Professional Documents

Culture Documents

Designs of All Digital Phase Locked Loop: A Review

Uploaded by

Soha HamedOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Designs of All Digital Phase Locked Loop: A Review

Uploaded by

Soha HamedCopyright:

Available Formats

Proceedings of 2014 RAECS UIET Panjab University Chandigarh, 06 08 March, 2014

Designs of All Digital Phase Locked Loop

A REVIEW

Aastha Singhal

Charu Madhu

Vijay Kumar

Department of Electronics and Communication

University Institute of Engineering and Technology, Panjab University

Chandigarh, India.

Abstract Phase Locked Loop (PLL) is a feedback system that is

configured as frequency multipliers, tracking generators,

demodulators and clock recovery circuits. Today the most

challenging requirement engineers face is design of fast locking

PLL with low jitter. Many analog techniques are proposed to

fulfill the demand but they result in increasing complexity of

design and long lock in time. In this paper, review of advantages

of an All-Digital phase locked loop (ADPLL) over an analog

phase locked loop (APLL) in terms of stability, programmability

is studied. Various approaches to design the blocks of ADPLL till

now adopted are presented in this paper.

Keywords- Phase Locked Loop (PLL); all digital phase locked loop

(ADPLL); analog phase locked loop (APLL)

I. INTRODUCTION

Phase Locked Loop (PLL) is a closed loop feedback system

that is capable to track the fixed phase relationship between

phase of output and the reference clock. It is widely used for

clock recovery, as a frequency synthesizer, jitter attenuator

and synchronization of chips in GPS receivers [1]. The

foundation of PLL was led in 1918 with the invention of super

heterodyne but it uses large number of tuned stages. In early

1930s attempt of comparing frequency of oscillator with

input of detector is carried out which results into introduction

of PLL in 1932 by de Belle size, French Engineer [2].Since

then the basic PLL block diagram has nearly remained same

but time to time lot of researches and advancements has been

done on various parameters of PLL such as the lock time, the

phase noise, jitter, loop bandwidth, output frequency and

acquisition time. When certain parameters are improved,

others factors may get worse.PLL can be configured in

following three ways- Analog PLL (all blocks are analog),

Hybrid PLL (combination of both analog and digital circuit)

and All Digital PLL (all blocks are implemented

digitally).The paper is organized as follows: Section II

presents Prior work using APLL. Section III gives Overview

of ADPLL architecture. Section IV presents mathematical

modelling of ADPLL and finally conclusion is drawn in

section V.

II. PRIOR WORK USING APLL

There are three building blocks of PLL - Phase Detector,

Loop filter and VCO (Voltage Controlled Oscillator) [1].

Phase detector compares the phase of each input, proportional

978-1-4799-2291-8/14/$31.00 2014 IEEE

to the phase difference between them generates an error signal

which alters the input of VCO to make its output frequency

equal to input frequency. PLL has three operating statesfrequency running, capture and lock state. In free running

feedback loop is open and VCO is oscillating in its natural

frequency. In capture mode, feedback loop is closed and VCO

vary the feedback frequency to make it equal to reference

frequency. In lock state, the phase error is zero i.e. both the

frequency are perfectly matched.

Traditionally, analog approaches were adopted to design

PLL.

In 2007, Greg Paul [3] had used ferroelectric capacitor in

VCO replacing linear capacitor as a storage element which

leads to reduction in cycle to cycle jitter because of its nonlinear dielectric constant behavior.

Interpolate compensation [4] method was used in which

compensator and interpolative loop were implemented

which detects the jitter during the sampling of reference

input signal.

Jitter reduction circuit was proposed [5] which was based

on autocorrelation of jittered signal.

In 2010, Jie Wu [6] introduces the usage of digital

circuitry to reduce noise from VCO which was difficult to

avoid using analog technique. This was the first time when

DDSC (Digital distributed synchronous clock) with

voltage controlled crystal oscillators (VCXO) was

implemented. This design shows jitter cleaning properties

but problem in this design was it was unable to compare

the reference clock with feedback clock completely due to

inaccuracy of DAC.

In analog PLL, many algorithms were designed and

modelled [7], [8] to generate mathematical relations to

check maximum noise level from various components of

PLL and deducing the transfer function for system.

In [9], [10] sub sampling PLL was used to lessen the

impact of jitter to a factor of 0.73 ps. In this no frequency

divider was used during the locked state. During locking

period PD/CP is not multiplied by N2 factor which leads to

low noise.

Above analog techniques were proposed to reduce jitter in

PLL but they result into higher switching and lock-in time,

complexity of circuit was also increased and PLL becomes

sensitive to process parameters so they need to restore for new

technology every time.

Because of the need of the circuit with small size, high

performance, low cost and immunity to noise there is a need to

digitalize various blocks of PLL which is implemented using

ADPLL.

Fig.1 Basic block diagram of ADPLL

III. OVERVIEW OF ADPLL ARCHITECTURE

An All Digital Phase Locked Loop (ADPLL) composed of

components purely in digital format. All the components of

ADPLL are analogous to analog PLL. The phase detector is

replaced by digital phase frequency detector or time to digital

convertor. The phase error is in digital representation. Digital

filter is used instead of analog filter where frequency is

controlled by a control word. The voltage controlled oscillator

(VCO) is replaced by digitally controlled oscillator

(DCO).General block diagram of ADPLL is shown in Fig.1

[13].Various techniques used to design these blocks are

describe as below.

A. PHASE-FREQUENCY DETECTOR (PFD)

A PFD detects phase/frequency error between reference

(V1) and feedback clock signal (V2) and generates a signed

binary code (Vd). In late nineties, EX-OR gate as shown in

Fig-2(a) was used for phase detection but it was level

triggered mechanism which results into lack of sensitivity to

edges. To eliminate this drawback the edge triggered JK

mechanism was employed as given in Fig-2(b). It was

sensitive to the edges and hence instantaneous corrective

action can be achieved. These were the basic means to design

the detector. In 2003, Digital pulse amplifier (DPA) [14], [16]

had been proposed to enlarge phase error when it is so small

that it is difficult to detect. DPA minimizes the dead zone and

make it more easily detectable by D-Flip Flop, these

amplifiers has AND gates connected in cascaded network to

increase width of pulse.

The design of DPA proposed was as shown in Fig-3 [16].

In 2006, chang-hong shan [15] introduce another method of

designing ADPLL which is based on Double edge triggered

flip flop. Takamoto Watanabe in [17] high speed with phase

lock at seventh reference cycle was intended in which a ring

delay line (RDL) with 32 inverters were assembled and taken

as a time base for designing the PFD. Martin kumm in 2010

designed [18] the Hilbert transform based PFD in which input

signal are firstly converted into analytic signals using Hilbert

transform and then phase error was obtained using Cartesian

to polar conversion. To build phase error, zero delay circuits

were employed. In [12], [19] PFD along with a time to digital

convertor (TDC) was used which together forms P2D (Phase

to Digital) convertor as shown below in Fig-4 [12]. The PFD

sense the difference of reference frequency and DCO divided

clock and then converts the phase error into off-time width

(t) and further TDC digitalize t into set of binary digits

with fixed resolution of TDC. Dynamic logic PFD was

adopted in [12] instead of static PFD as number of transistors

are decreased from 44 to 16 hence power and dead zone were

reduced. In reference [20] Nyquist- rate phase detector was

proposed and designed using HDL.

Fig.3 Proposed design of PFD with DPA

Fig.4 Phase to digital convertor

()

(a)

(b)

Fig.2 (a) XOR implementation (b) PD based on edge triggered JK

B. DIGITAL LOOP FILTER (DLF)

The code generated by phase frequency detector is

processed by loop filter so as to generate a control word for

digitally controlled oscillator. DLF may be designed using PI,

PD or PID controller i.e. loop filter consist of integral,

proportional, differential or delay elements [21]. Type of loop

filter is important property of PLL as type-1 is suitable for

lock time but it has low noise immunity [11]. In order to

remove glitches from PFD to reduce power consumption and

generating digital codes proportional to the output of PFD a

controller is designed in [16], two types of deglitching filter

circuit were proposed as shown in Fig-5(a) and 5(b).Second

method was suitable for every digital circuit but consumes

more power as compared to first method.

(a)

Fig.8 Logical configuration of Digital LPF

C. DIGITAL CONTROLLED OSCILLATOR (DCO)

(b)

Fig.5 (a) First deglitching filter circuit (b) Second deglitching filter circuit

Double edge triggered based DLF had been proposed [15]

to achieve low power. In this adder was designed by the

combination of DETDFF and a full adder as shown in Fig-6

[15]. After get modulated through PI controller it is passed to

adder which provides the control word of DCO. One of the

most important and simplest digital loop filters is the K

counter [13] shown in Fig 7[13]. This filter always works in

combination with EXOR or the JK-flip-flop phase detector. In

[19], [12],[22],[23] designed PI integral based loop filter as

shown in Fig 8 [12] which consist of proportional and integral

path from second order charge pump PLL using bilinear

transformation is proposed. Using this design phase margin is

calculated for stability analysis.

DCO is similar to analog VCO except for DCO frequency

is tuned digitally whereas VCO is tuned by analog signal from

charge pump. It is the heart of Phase locked loop which

changes its output frequency in accordance to the control word

from loop filter. Yu Ming Chung [12] and V. Kratyuk [19]

used ring oscillator for frequency tuning instead of LC

oscillator as later was more bulky and performs tuning

through switching on and off the tank capacitor which further

leads to power consumption. Fig-9 shows the proposed design

of DCO which consist of 5 delay cells, frequency was tuned

according to the current passes through these delay cell. One

of the typical methods to design DCO was using combination

of VCO and DAC (Digital to Analog convertor) [23]. From

the output of digital loop filter digital code was obtained

which was converted into control voltage (Vc) by DAC fed

into the VCO for controlling the frequency. In [13] basic

configuration of DCO is given by K.Lata which is incrementdecrement counter which works on the principle that if fref is

more than fdiv the counter will increment the frequency of fdiv

and vice versa. Logical block of the counter is shown in Fig

10.Bohan Wu, 2013[22] proposed two methods output

frequency detection and frequency averaging method to

achieve fast Locking and remove non-idealities such as DCO

estimation error.

Fig.6 Design of DLF based on DETDFF

Fig.9 DCO with delay cell decrement

Fig.7 K counter loop filter

Fig.10 Logical block of increment-counter

In 2012, S.Sreekumar uses NCO(Numerically Controlled

Oscillator) [20] in his design which will take error voltage

(Vn), and then shift its output frequency from its free-running

value closer to reference frequency so to make phase error

zero and thus keep the PLL in lock state. In reference [16] ring

oscillator based DCO is proposed consisting of 64 buffers

with different combinations of digital code having different

path corresponds to different clock period and clock

frequency. This was executed using binary frequency search

algorithm.

IV. MATHEMATICAL MODELLING OF ADPLL

Various properties of ADPLL such as working range,

stability, lock-in range [ 18],[26] , loop bandwidth and

variables based on noise sources [24] can be analyzed in either

phase domain or z-domain [11], [21].

A. PHASE DOMAIN MODEL OF LINEAR PLL

Block diagram of PLL as shown in Fig-11(a) [18], presents

three main components of PLL in phase domain and transfer

functions of all the blocks is given in Fig-11(b).

Phase Detector (PD): It detects the phase difference

(v (t)) between the input signal Vi (t) and the

feedback signal Vo (t).

Loop filter: It has transfer function of F(s) which

depends on type and order of filter used. It is used to

minimize the phase difference (t) by varying the

frequency of VCO. Here [18] type 1 PI controller

loop filter is used with gains of proportional and

integral path KI and KP respectively.

VCO: Voltage Controlled Oscillator is having

transfer function of Ko/s whose output frequency

oscillator is a function of the voltage of its input

signal.VCO acts like an integrator.

Fig.11 (a) General block diagram of PLL

Transfer function of loop filter:

F(s) = KP +

Gain of phase detector and VCO is considered as Kd and KO

respectively. The phase error can be given as:

E(s) =

K K F

Resulting value of phase error can be given as

E(s) =

K K K

K K K

When compared with general second order equation

E(s) =

Comparing both the above equations

Wn (natural frequency) =Ko Ki Kd

(damping ratio) =

K /

K K

K

Natural frequency varies the settling time so it is

responsible for fast locking. It is generally kept high but

should be low enough so to achieve

phase filtering

efficiently.Damping factor affects overshoot so to maintain

trade off between both = 0.707 (approx) [19].

B. Z-DOMAIN MODEL OF PLL

Phase or continuous time domain modeling of PLL is

applied to analog design of PLL, but for digital systems zdomain modeling is more accurate and proper description. So

far a lot of work has been done in analysis of ADPLL using Zdomain. Block diagram of z-domain model is as shown in Fig12 [21]. In this phase detector is represented by summing

node, gain block (Kd) and a delay block of z-1 as frequency of

DCO output is dependent on events a step earlier [21]. Loop

filter is implemented using first order PI elements where Ki

and Kp are gains of integral path and proportional path. All the

blocks of ADPLL can be analyzed by performing bilinear

transformation of s-domain analysis by replacing s by (1-z-1).

Z-domain transfer function of loop filter:

F (z) = KP +

Transfer function of DCO is

Fig.11 (b) Phase domain model of PLL

D (z) =

Open loop equation can be given as:

L (z) =Kd*Kf*Ko*z-1*F (z)*D (z)

Closed loop transfer function is given by:

H (z) =

L

L

Fig.12 Z-domain model of PLL

V. CONCLUSION

In this paper, a detailed analysis of various techniques for

designing the phase detector, digital loop filter and digital

controlled oscillator in ADPLL is provided. Among all the

methods to design detector, PFD with TDC is the best

approach as the amount of glitches using this method is less.

Digital loop filter is designed using bilinear transformation of

RC loop filter.DCO structure based on ring oscillator is

preferred for low power and low complex design. Finally, if

we use PFD, TDC and digital loop filter together in ADPLL,

various parameters such as lock-in time, power consumption

and stability can be evaluated and comparison with the results

of existing ADPLL structures can be carried out.

VI. REFERENCES

[1] Razavi, B.: Design of Analog CMOS Integrated Circuits, McGrawHILL, 2001.

[2] Roland E.Best: Phase locked loop: Design, simulation and applications,

4th ed., New York: McGraw-hill, 1999.

[3] Pauls, G. and Kalkur, T.S.: PLL jitter reduction by utilizing a

ferroelectric capacitor as a VCO timing element, IEEE transactions on

ultrasonics, ferroelectrics and frequency control, vol-54, No-6, June 2007, pp.

1096-1102.

[4] Nakanishi, Y., Kobayashi, F., and Kondoh, H.: Low jitter PLL by

interpolate compensation, IEEE Asia Pacific Conference on Circuits and

Systems, (APCCAS), Nov 2008, pp. 1078-1081.

[5] Venkatanayanan, H.V. and Bushnell, M.L.: A Jitter reduction circuit

using autocorrelation for phase locked loops and serializer deserializer

(SERDES) circuits, 21st international conference on VLSI design (VLSID),

Jan 2008, pp. 581-588.

[6] Wu, J., Ma, Y., Zhang, J. and Xie, M.: A Low-jitter synchronous clock

distribution scheme using a DAC based PLL, IEEE transactions on nuclear

science, vol-57, No-2, April 2010, pp. 589-594.

[7] Siwiec, K., Borejko, T. and Pleskacz, W.A.: CAD tool for PLL design,

IEEE 14th International Symposium on design and diagnostics of electronic

circuits and systems (DDECS), April 2011, pp.283-286.

[8] Telba, A.A.: Modelling and simulation of wideband low jitter frequency

synthesizer, IEEE International Conference on Multimedia, signal processing

and communication technologies, March 2009, pp.317-319.

[9] Sogo,K.,Toya,A. and Kikkawa,T.: A ring VCO-based Sub-sampling PLL

CMOS circuit with 0.73 ps jitter and 20.4 mW power consumption, Asia and

South pacific conference on design automation conference (ASP-DAC), Jan

2013, pp. 101-102.

[10] Xiang Gao, Klumperink,E. A.M., Bohsali,M. and Nauta,B.: A Low

Noise Sub-Sampling PLL in which divider noise is eliminated and PD/CP

noise is not multiplied by N2, IEEE Journal of solid state circuits, vol.44,

No.12, December 2009, pp. 3253-3263.

[11] Mendel, S., Vogel, C.: A z-domain model and analysis of phase-domain

All- Digital Phase Locked Loops, IEEE, 2007.

[12] Yu-Ming Chung and Chia-Ling Wei, An All-Digital Phase-Locked loop

for Digital power management integrated chips, IEEE International

Symposium on circuits and systems, May 2009, pp. 2413-2416.

[13] Lata, K. and Kumar, M.: ADPLL Design and Implementation on

FPGA, 2013 International Conference on Intelligent Systems and Signal

Processing (ISSP), March 2013, pp.272-277.

[14] Ching-Che Chung and Chen-Yi Lee: An All-Digital Phase-Locked loop

for High- Speed Clock generation, IEEE Journal of solid-state circuits, vol.

38, No.2, February 2003, pp.347-351.

[15] Chang-hong Shan, Zhong-ze Chen, Yan Wang: An All-Digital PhaseLocked loop based on Double Edge Triggered Flip-flop, IEEE, 2006.

[16] Watanabe, T. and Yamauchi, S.: An All-Digital PLL for Frequency

multiplication by 4 to 1022 with seven cycle lock time, IEEE Journal of

solid-state circuits, vol. 38, No.2, February 2003, pp.198-204.

[17] Abadian, A., Lotfizad, M., Majd, N.E., Ghoushchi, M.B.G and Mirzaie,

H.: A new low- power and low-complexity All Digital PLL (ADPLL) in 180

nm and 32 nm, IEEE International Conference on electronics, circuits and

systems, December 2010, pp.305-310.

[18] Kumm, M., Klingbeil, H. and Zipf, P.: An FPGA-based linear AllDigital Phase-Locked loop, IEEE Transactions on circuits and systems-I,

Regular papers, vol.57, No.9, September2010, PP.2487-2497.

[19] Kratyk,V., Hanumolu,P.K, Moon,U. and Mayaram,K.: A Design

Procedure for All-Digital Phase-Locked loops based on a charge pump phase

locked loop analogy, IEEE Transactions on circuits and systems-II, Express

Briefs,vol.54, No.3 March 2007.

[20] Sreekumar, S., Geetha and Snoop, M.K.: FPGA Implementation of

ADPLL, International journal of emerging technology and advanced

engineering, vol.2, issue 6, June, 2012.

[21] Xin Chen, Jun Yang and Xiao-ying Deng: A Contribution to the discrete

z-domain analysis of ADPLL, IEEE International Conference on ASIC,

October 2007, pp.185-188.

[22] Bohan Wu, Weixin Gai and Te Han: A Novel Frequency Search

Algorithm to achieve fast locking without phase tracking in ADPLL, IEEE

International Symposium on Circuits and systems (ISCAS), May 2013,

pp.2464-2467.

[23] Xin Chen, Ju Yang and Long- Xing shi: A fast-locking All-digital

Phase-Locked Loop via Feed- forward compensation technique, IEEE

Transactions on very large scale integration(VLSI) systems, vol.19, No.5,

May 2011,pp.857-868.

[24] Bo Jiang and Tian Xia: ADPLL Variables Determinations based on

phase-noise, spur and locking time, IEEE International SOC Conference,

September 2012, pp.39-44.

[25] Jiancheng Li, Tao Xu, Zhaowen Zhuang and Yongfeng Guan, High

performance All Digital Phase Locked Loop Mathematics Modelling and

Design, IEEE International Conference on Information and Automation,

June 2008, pp.1395-1399.

You might also like

- Designs of All Digital Phase Locked Loop: A ReviewDocument5 pagesDesigns of All Digital Phase Locked Loop: A ReviewKoldodeRostovNo ratings yet

- Cas2 Mar 07 DPLL 2Document5 pagesCas2 Mar 07 DPLL 2Fakhrul Risal DjuminginNo ratings yet

- All Digital Phase Locked Loop (ADPLL) Design and SimulationDocument27 pagesAll Digital Phase Locked Loop (ADPLL) Design and SimulationSuresh KumarNo ratings yet

- Delay Lock LoopDocument19 pagesDelay Lock LoopjameelahmadNo ratings yet

- ALL Digital Phase-Locked Loop (ADPLL) : A Survey: Kusum Lata and Manoj KumarDocument5 pagesALL Digital Phase-Locked Loop (ADPLL) : A Survey: Kusum Lata and Manoj KumargezahegnNo ratings yet

- All Digital Phase Locked Loop Design and ImplementationDocument4 pagesAll Digital Phase Locked Loop Design and ImplementationAnton SaitovNo ratings yet

- A Digitally Controlled PLL For Soc Applications: Thomas Olsson, Member, Ieee, and Peter Nilsson, Member, IeeeDocument10 pagesA Digitally Controlled PLL For Soc Applications: Thomas Olsson, Member, Ieee, and Peter Nilsson, Member, IeeeSathish KumarNo ratings yet

- Design of All Digital Phase Locked Loop For WireleDocument5 pagesDesign of All Digital Phase Locked Loop For WireleKiran SomayajiNo ratings yet

- A Phase-Locked Loop With Embedded Analog-to-Digital Converter For Digital ControlDocument7 pagesA Phase-Locked Loop With Embedded Analog-to-Digital Converter For Digital ControlAbhi BhatNo ratings yet

- An All-Digital PLL Clock Multiplier: M PD OSC FilterDocument4 pagesAn All-Digital PLL Clock Multiplier: M PD OSC FilterArun JyothiNo ratings yet

- ADPLL Design and Implementation On FPGADocument6 pagesADPLL Design and Implementation On FPGANavathej BangariNo ratings yet

- ADPLL Digital PhaseLocked Circuit ProjectDocument27 pagesADPLL Digital PhaseLocked Circuit ProjectSteven YuNo ratings yet

- A 2.6Ps - Period-Jitter 900Mhz All-Digital Fractional-N PLL Built With Standard CellsDocument4 pagesA 2.6Ps - Period-Jitter 900Mhz All-Digital Fractional-N PLL Built With Standard CellsRichard SuNo ratings yet

- A 0.6Ghz To 2Ghz Digital PLL With Wide Tracking RangeDocument4 pagesA 0.6Ghz To 2Ghz Digital PLL With Wide Tracking RangeStella SofiaNo ratings yet

- A Software-Based Frequency Locked Loop DC Motor Drive SystemDocument12 pagesA Software-Based Frequency Locked Loop DC Motor Drive SystemMoeed IqbalNo ratings yet

- Low Jitter Adpll Based Clock Generator For High Speed Soc ApplicationsDocument5 pagesLow Jitter Adpll Based Clock Generator For High Speed Soc ApplicationsjubidownNo ratings yet

- A Digitally Controlled Phase Locked Loop With A Digital Phase Frequency Detector For Fast AcquisitionDocument8 pagesA Digitally Controlled Phase Locked Loop With A Digital Phase Frequency Detector For Fast AcquisitionQuas GmallNo ratings yet

- Adaptive TD PLLDocument7 pagesAdaptive TD PLLdilrubaNo ratings yet

- A_Simulink_Model_for_All-Digital-Phase-Locked-LoopDocument4 pagesA_Simulink_Model_for_All-Digital-Phase-Locked-LoopManiNo ratings yet

- Synopsis of ADPLL Design and Implementation On FPGADocument4 pagesSynopsis of ADPLL Design and Implementation On FPGANavathej BangariNo ratings yet

- An575 Introduction To Fpga-Based AdpllsDocument8 pagesAn575 Introduction To Fpga-Based AdpllsDan HauerNo ratings yet

- ADPLL All Digital Phase Locked Loop CircuitsDocument27 pagesADPLL All Digital Phase Locked Loop Circuitsvinod kumarNo ratings yet

- FFT Analysis, Simulation of Computational Model and Netlist Model of Digital Phase Locked LoopDocument16 pagesFFT Analysis, Simulation of Computational Model and Netlist Model of Digital Phase Locked LoopIJSTENo ratings yet

- Design of All Digital Phase Locked LoopDocument4 pagesDesign of All Digital Phase Locked LoopInternational Journal of Research in Engineering and TechnologyNo ratings yet

- Design and Analysis of Phase Locked Loop in 90mm CmosDocument7 pagesDesign and Analysis of Phase Locked Loop in 90mm CmosabhishekNo ratings yet

- Ofc Lab Manual 2Document21 pagesOfc Lab Manual 2Shobhit JainNo ratings yet

- Design of Charge Pump PLLDocument5 pagesDesign of Charge Pump PLLSwati KashtNo ratings yet

- ADPLL PresentationDocument28 pagesADPLL PresentationSaiHarshithaNo ratings yet

- Roll of Engineer FINAL2!3!13Document6 pagesRoll of Engineer FINAL2!3!13Mahendra S. PatilNo ratings yet

- Paper 20Document4 pagesPaper 20Mohamed AhmiedNo ratings yet

- A 0.4-To-3 GHZ Digital PLL With PVT Insensitive Supply Noise Cancellation Using Deter Minis Tic Background CalibrationDocument13 pagesA 0.4-To-3 GHZ Digital PLL With PVT Insensitive Supply Noise Cancellation Using Deter Minis Tic Background CalibrationTeerachot SiriburanonNo ratings yet

- Pulse Triggered Flip Flop Design With Signal Feed Through Scheme Using Conditional Pulse Enhancement TechniqueDocument6 pagesPulse Triggered Flip Flop Design With Signal Feed Through Scheme Using Conditional Pulse Enhancement TechniqueIJSTENo ratings yet

- A 0.0021 mm2 1.82 MW 2.2 GHZ PLL Using Time-Based Integral Control in 65 NM CMOSDocument13 pagesA 0.0021 mm2 1.82 MW 2.2 GHZ PLL Using Time-Based Integral Control in 65 NM CMOSnayakadarsh2000No ratings yet

- ICCSP IEEE Published Paper - ManikanthDocument4 pagesICCSP IEEE Published Paper - ManikanthRamesh NairNo ratings yet

- Fast-Locking Digital DLL with Multiphase OutputsDocument8 pagesFast-Locking Digital DLL with Multiphase OutputsMeshcheryakov SlavaNo ratings yet

- Adpll JSSC 2007Document11 pagesAdpll JSSC 2007陳育楷No ratings yet

- Clear OnDocument6 pagesClear OnAbdalmoedAlaiashyNo ratings yet

- Dual Loop DLLDocument11 pagesDual Loop DLLKiran KNo ratings yet

- Sooho Cha, Chunseok Jeong, Changsik Yoo Joongsik Kih: Abstract - A Digitally Controlled Phase-Locked LoopDocument4 pagesSooho Cha, Chunseok Jeong, Changsik Yoo Joongsik Kih: Abstract - A Digitally Controlled Phase-Locked LoopNguyen Tien HaiNo ratings yet

- The Design of DDS ADPLL Using ARM Micro ControllerDocument15 pagesThe Design of DDS ADPLL Using ARM Micro ControllerIJRASETPublicationsNo ratings yet

- Vlsi Design: Paper Presentation ONDocument8 pagesVlsi Design: Paper Presentation ONYogesh YadavNo ratings yet

- 6.VLSI Architecture Design For Analysis of Fast Locking ADPLL Via Feed Forward Compensation Algorithm (33-38)Document6 pages6.VLSI Architecture Design For Analysis of Fast Locking ADPLL Via Feed Forward Compensation Algorithm (33-38)ijcctsNo ratings yet

- DatasheetDocument5 pagesDatasheetDeepak KumarNo ratings yet

- Implementation of Digital QPSK Modulator by Using VHDL / MatlabDocument5 pagesImplementation of Digital QPSK Modulator by Using VHDL / Matlabblesson123No ratings yet

- A 0.52/1 V Fast Lock-In ADPLL For Supporting Dynamic Voltage and Frequency ScalingDocument5 pagesA 0.52/1 V Fast Lock-In ADPLL For Supporting Dynamic Voltage and Frequency ScalingDeep SahaniNo ratings yet

- Frequency Modulation of System Clocks For EMI Reduction: by Cornelis D. HoekstraDocument7 pagesFrequency Modulation of System Clocks For EMI Reduction: by Cornelis D. HoekstraKesavant TkesavanNo ratings yet

- Fpga Implementation of A Phase Locked Loop Based On RandomDocument6 pagesFpga Implementation of A Phase Locked Loop Based On Random9638042No ratings yet

- PLL DividerDocument6 pagesPLL Divider081270No ratings yet

- Injection-Locked Clock andDocument12 pagesInjection-Locked Clock andAnonymous e4UpOQEPNo ratings yet

- A Loop Gain Optimization Technique For IntegerTDC-Based Phase-Locked LoopsDocument10 pagesA Loop Gain Optimization Technique For IntegerTDC-Based Phase-Locked Loops孫世洋No ratings yet

- Kundu Et Al - 2019 - A Fully Integrated Digital LDO With Built-In Adaptive Sampling and ActiveDocument12 pagesKundu Et Al - 2019 - A Fully Integrated Digital LDO With Built-In Adaptive Sampling and Active马晓飞No ratings yet

- Digital Phase Lock LoopsDocument17 pagesDigital Phase Lock LoopsArfaaNaseemNo ratings yet

- Design of Integer N Frequency Divider For High Performance PLL Using 180 NM CMOS TechnologyDocument8 pagesDesign of Integer N Frequency Divider For High Performance PLL Using 180 NM CMOS Technology123abhijeetNo ratings yet

- Design and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationDocument4 pagesDesign and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationMatthew CarterNo ratings yet

- An Efficient Differential Conditional Capturing Energy Recovery Flip-Flop DesignDocument6 pagesAn Efficient Differential Conditional Capturing Energy Recovery Flip-Flop DesignRaghul RamasamyNo ratings yet

- A Sub-Mw Fractional-N Adpll With Fom Of: 246 DB For Iot ApplicationsDocument13 pagesA Sub-Mw Fractional-N Adpll With Fom Of: 246 DB For Iot ApplicationsSAMNo ratings yet

- High Resolution Digital-To-Time Converter For Low Jitter Digital PllsDocument4 pagesHigh Resolution Digital-To-Time Converter For Low Jitter Digital PllsroomaNo ratings yet

- Digital Signal Processing: Instant AccessFrom EverandDigital Signal Processing: Instant AccessRating: 3.5 out of 5 stars3.5/5 (2)

- The Women's Health Fast-Track Tone-Up Plan: The Greatest Workout You'll Ever Get-Inside A Gym, or Out DirectionsDocument5 pagesThe Women's Health Fast-Track Tone-Up Plan: The Greatest Workout You'll Ever Get-Inside A Gym, or Out DirectionsSoha HamedNo ratings yet

- Weightloss Training Plan 1 4 PDFDocument1 pageWeightloss Training Plan 1 4 PDFSoha HamedNo ratings yet

- Run To Lose Program Training PlanDocument1 pageRun To Lose Program Training PlanSoha HamedNo ratings yet

- All Digital Phase Locked Loop Design and ImplementationDocument4 pagesAll Digital Phase Locked Loop Design and ImplementationAnton SaitovNo ratings yet

- Digital PLL Cicc Tutorial PerrottDocument118 pagesDigital PLL Cicc Tutorial PerrottSwethaVellankiNo ratings yet

- TSG Surge Reduction Filter, Three Phase - TSGSRF3630Document2 pagesTSG Surge Reduction Filter, Three Phase - TSGSRF3630Angela TienNo ratings yet

- St. Andrew's Junior College JC2 2015 Preliminary Exam Physics Paper 2Document24 pagesSt. Andrew's Junior College JC2 2015 Preliminary Exam Physics Paper 2VarshLokNo ratings yet

- N2006 PidDocument8 pagesN2006 PidSarah KempNo ratings yet

- 2090 CSWM1DF 14aa05 PDFDocument132 pages2090 CSWM1DF 14aa05 PDFsoayNo ratings yet

- Long Life 12V 100Ah Gel Battery for Telecom, UPS, and Emergency PowerDocument2 pagesLong Life 12V 100Ah Gel Battery for Telecom, UPS, and Emergency PowerIwhan KristantoNo ratings yet

- Root Category: # Free Space (1 Part(s) )Document1 pageRoot Category: # Free Space (1 Part(s) )MiguelNo ratings yet

- AD8232-EVALZ User Guide: Evaluating The Single-Lead Heart Rate Monitor Front EndDocument8 pagesAD8232-EVALZ User Guide: Evaluating The Single-Lead Heart Rate Monitor Front EndBorislav GanevNo ratings yet

- Government of Kerala public works department schedule of rates for electrical materials 2008Document106 pagesGovernment of Kerala public works department schedule of rates for electrical materials 2008Kamal ShaikNo ratings yet

- Design Optimazation and Simulation of PMSM Based On Maxwell and Twinbuilder For EvsDocument6 pagesDesign Optimazation and Simulation of PMSM Based On Maxwell and Twinbuilder For EvsMayur DeokarNo ratings yet

- Cylindrical Proximity Magnetic Sensors for Detection of Ferrous TargetsDocument2 pagesCylindrical Proximity Magnetic Sensors for Detection of Ferrous TargetsTenuka pereraNo ratings yet

- CDJ 100SDocument28 pagesCDJ 100SMarcos ZanelliNo ratings yet

- Accessory Cable GuideDocument9 pagesAccessory Cable GuideCarmelo BayonNo ratings yet

- Essay On Corrosion - Baimourne BournebeDocument4 pagesEssay On Corrosion - Baimourne BournebeBAIMOURNE BOURNEBENo ratings yet

- Maxwell Stress TensorDocument8 pagesMaxwell Stress Tensorkushaldave227No ratings yet

- Energies: Analysis and Design of High-Efficiency Bidirectional Gan-Based CLLC Resonant ConverterDocument13 pagesEnergies: Analysis and Design of High-Efficiency Bidirectional Gan-Based CLLC Resonant ConverterThien DinhNo ratings yet

- Apostila CLP Omrom BRDocument671 pagesApostila CLP Omrom BRreinaldopf2011No ratings yet

- Is 15652Document3 pagesIs 15652IshanNo ratings yet

- Error List For Mitsubishi HeavyDocument54 pagesError List For Mitsubishi HeavynovyNo ratings yet

- Extremely Inverse Time Overcurrent CDG14 PDFDocument6 pagesExtremely Inverse Time Overcurrent CDG14 PDFkarqu86No ratings yet

- XGN15 Ring Main Unit User's ManualDocument21 pagesXGN15 Ring Main Unit User's ManualFrancisco VeraNo ratings yet

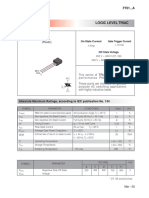

- LOGIC LEVEL TRIAC TECHNICAL SPECIFICATIONSDocument4 pagesLOGIC LEVEL TRIAC TECHNICAL SPECIFICATIONSAnatoly WolkoffNo ratings yet

- SW32V Operating Manual e ZIEHL 2017-05-03Document22 pagesSW32V Operating Manual e ZIEHL 2017-05-03Jatupol PongsirisartNo ratings yet

- MCQ LCR Circuits Master-1Document14 pagesMCQ LCR Circuits Master-1Deepak Choudhary DCNo ratings yet

- Final Earthing V3Document22 pagesFinal Earthing V3RewanEsamNo ratings yet

- UM Faculty of Science and Technology Lab Report: Measuring Efficiency and Waveforms of an Electric MachineDocument6 pagesUM Faculty of Science and Technology Lab Report: Measuring Efficiency and Waveforms of an Electric MachineJIayu ZhangNo ratings yet

- Design of EHV SubstationDocument66 pagesDesign of EHV SubstationMadanasekhar Tadimarri100% (1)

- Long Transmission LinesDocument11 pagesLong Transmission LinesPao Castillon50% (2)

- Electronic Instrument Handbook Third EditionDocument1,217 pagesElectronic Instrument Handbook Third Editionhashemowida100% (39)

- Eletric TractionDocument21 pagesEletric TractionGowri Sri Gowri75% (4)

- Electrical Vendor ListDocument11 pagesElectrical Vendor Listshantanu11181No ratings yet