Professional Documents

Culture Documents

Lab 6. Simulation of Feedback Analog - Digital Converters

Uploaded by

IoanaNicoletaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab 6. Simulation of Feedback Analog - Digital Converters

Uploaded by

IoanaNicoletaCopyright:

Available Formats

Lab 6.

SIMULATION OF FEEDBACK ANALOG - DIGITAL

CONVERTERS

The first step in designing an electronic circuit uses models for the

used electronic devices. Mathematical functions describe their behavior and

they allow global estimation of the whole circuit function. The used model

is closer to the real circuit behavior (but also more difficult to use) when the

used mathematical equations are more numerous (more parameters

considered) and complex (better approximation of real dependencies).

Obviously, simple models are used in first steps of the design

process. Subsequently, the design needs to be verified and validated,

making sure that it is close enough to the desired behavior. There are two

possible ways to check that:

Experimental model - is a real circuit built in lab conditions, but trying

to reflect as close as possible the real technology to use by final (series)

production process. The designer uses a set of components to build a small

number of products (sometimes a single one). The method is expensive,

time consuming and assumes some risk (malfunction can lead to component

damage or other unwanted effects).

On the other hand, the measured results represent the behavior of a

particular set of used components. The effect of parameter spreading (in the

range allowed by the component specifications) is hard to emphasize. For

example, the design includes an operational amplifier for which the data

book specifies an offset error in the range +/- 5mV. The particular used OA

exhibits +2mV offset. How would the circuit behave using a -4mV or +5mV

offset OA? To find that, such AO should be looked for and tested in the

experimental model.

Simulation of an electronic circuit computes the behavior functions

using mathematical models. As many as possible parameters are considered,

approximated by as close as possible mathematical functions. For complex

devices, the implied calculus is laborious requiring the computer speed and

power. The programming time could be large, but the method is much

cheaper. It reduces the component and assembly costs, allows simple

1

Data Conversion and Acquisition Systems - Lab Manual

changing the parameter values, to emphasize the effect of each one on the

overall circuit behavior. The risk is significantly reduced and theoretical

aspects can be easily studied.

On the other hand, even the best component models are not perfect.

Simulation is an efficient analysis method, but it doesnt replace the

experimental model at all.

THE LAB PURPOSE

The lab intends to help students in understanding the behavior basics

of several feedback analog-to-digital circuit types, previously discussed at

class: counter, tracking and Successive Approximation Register (SAR)

ones. All of them are studied in both voltage- and current-comparison

versions.

A dedicated program simulates the ADCs, emphasizing several nonideal parameters of the used components also (slew rate, setting time, etc.).

The parameter values can be set in specific ranges.

THE LAB FLOW

The students perform steps similar to building and testing of an

experimental model:

- choosing a converter type,

- designing it (setting values for devices parameters),

- setting supply voltage and clock frequency,

- applying the input analog signal,

- analyzing the circuit behavior based on simulated time diagrams,

- understanding the (dis)advantages of each studied conversion

principle,

- emphasizing the error sources, modifying the circuit to improve it.

CHOOSING A CONVERTER TYPE

Three command logic types are available:

2

Simulation of feedback analog-digital converters

G

tact

Counter ADC

As the name shows, the

V bit

Sta rt/Stop

command logic is build around a nonreversible binary counter. PP (main

AO

gate) allows the clock pulses to reach

Logica

R

Reset

the counter input when Vbit=1, meaning

the voltage drop across R is less than the

instantaneous value of Vin. Each active

R

Ck

slope of the clock signal increments the

CNA

counter content, increasing the voltage

Bipola r

Numarator

drop across R by VLSB (the voltage

corresponding to the least significant

...

bit) The process continues until bringing

Iref

a1 a2

an

the actual voltage drop across R slightly

Rref

{A }

greater than the instantaneous value of

Vin. At this moment, Vbit (comparators

V ref

Fig. 1 Counter ADC voltage output) falls to logical 0 and closes PP.

comparison. Block diagram.

The conversion is done; its result is the

current counter content. It is held a

G

R

tact

while to be read by subsequent

COMP

V in

+

circuits, then the counter is reset.

V bit

Sta rt/Sto p

The voltage drop across R is zero,

basically less than Vin, Vbit rises

Logica

to logical 1, pointing a new

Reset

conversion begin. The conversion

R

Ck

period is proportional to the

CNA

instantaneous value of Vin, i.e.

Bipola r

Numarator

changes from a conversion to

another. The worst case happens

...

when

Vin=VFS;

then

the

Iref

a1 a2

an

conversion takes 2n-1 tact periods.

COMP

V in

PP

Io

Io

...

Io

Io

...

Rref

{A }

V ref

Fig. 2 Counter ADC current

comparison. Block diagram.

3

Data Conversion and Acquisition Systems - Lab Manual

COMP

V in

G

tact

Tracking ADC

This time, the binary

counter is reversible. PPU (UP

AO

PPD

main gate) allows the clock

R

pulses to reach up-count input,

while Vbit=1 (voltage drop

across R less than instantaneous

CD

CU

value of Vin). PPD (DOWN main

CNA

gate) allows the clock pulses to

Bipola r

Numarator

reach down-count input, while

...

Vbit=0 (voltage drop across R

greater than instantaneous value

Iref

a1 a2

an

of Vin). The counter content

Rref

{A }

increases or decreases 1LSB at

each clock active slope, such a

V ref

Fig. 3 Tracking ADC voltage way to lead to a voltage drop

across R as close as possible to

comparison. Block diagram.

the current value of Vin

G

tact

(approximating it with either

R

COMP

PPU

positive or negative error).

V in

+

V bit

Anyhow, the approximation

error module is less than VLSB.

PPD

The

counter

content

represents at any time the

conversion result. To keep the

CD

CU

converter able to track Vin,

CNA

this one is not allowed to

Bipola r

Numarator

change faster then the R

...

voltage drop maximum speed:

Iref

a1 a2

an

|dVin/dt| < VLSB/Ttact

+

V bit

PPU

Io

Io

...

Io

Io

...

Rref

{A }

V ref

Fig. 4 Tracking ADC current comparison.

Block diagram.

4

Simulation of feedback analog-digital converters

COMP

V in

V bit

Io

Io

AO

R

...

CNA

Bipola r

RA S

...

Iref

an

G

tact

a1 a2

Rref

{A }

V ref

Fig. 5 SAR ADC voltage

comparison. Block diagram.

R

COMP

V in

V bit

Io

Io

...

CNA

+

Rref

RA S

...

a1 a2

Iref

Bipola r

an

{A }

V ref

Fig. 6 SAR ADC current

comparison. Block diagram.

G

tact

Successive Approximation Register ADC.

The command logic is now a SAR

(Successive Approximation Register) and

works based on halving principle. Prior

to a conversion begin, Vin is assumed to

belong to its definition range; for an

unipolar converter: Vin[0,VFS). That is

the initial search-range, which halves

each conversion step (at each active slope

of clock signal). To perform that, the

SAR delivers such a number to determine

(via DAC) a voltage drop on R to halve

the previous step search-range. The first

step considers the whole definition range,

halved by VFS/2. The SAR generated

number

is

{A}=1/2=0,100...02.,

a1=MSB=1, and ai=0,i=2...n

If Vbit=1, then Vin>VFS/2 belongs to

the upper half of its definition range:

Vin[VFS,VFS). This sub-range (current

search-range) is halved in the next step

by the VFS value. SAR generates the

number {A}=3/4=0,110...02, where the

final value of a1=1 is established (no

subsequent steps of same conversion

could change it).

Otherwise, Vbit=0 shows that

Vin[0, VFS). This sub-range (current

search-range) is halved in the next step

by the VFS value. SAR generates the

number {A}=1/4=0,010...02, where the

final value of a1=0 is established.

Similarly, the remaining bits are

determined step by step.

5

Data Conversion and Acquisition Systems - Lab Manual

SIMCAN PROGRAM PRESENTATION

The command menu includes the structure shown below:

C: Configuring

A: Supplies

- voltage supplies (0...+/-50V)

- clock frequency (0.001...10000kHz)

T: comparison Type 1 = voltage comparison

- slew rate AO (0.1...100V/s)

-open loop gain (1...1000000)

-resistance (0.1...100k)

2 = current comparison

- resistance (0.1...100K)

C: Converter

L: command Logic

- Bit number (2...14)

- Reference current (0.001...10mA)

- DAC setting time (0...1000ns)

1: Tracking

2: Counter

3: Successive Approximation Register

G: signal Generator:

- Frequency (0...10000KHz)

- Offset (-50...+50V)

- Amplitude (0...50V)

- Shape

1 = Sinus

2 = Triangle

3 = Rectangle

O: Oscilloscope

- Time base

S: Simulate

X: eXit

6

1 = 1/3 tact/div

2 = 1 tact/div

3 = 3 tact/div

4 = 10 tact/div

5 = 100 tact/div

6 = 1000 tact/div

Simulation of feedback analog-digital converters

The displayed signal set depends on the chosen time base (each time

the most relevant):

For time bases

1 and 2:

Vin, Vcmp, Vbit, Clk, {A}cmp

3 and 4:

Vin, Vcmp, Vbit, Clk, {A}

5 and 6:

Vin, V{A}

The above signal meaning is:

Vin input voltage (from signal generator).

Vcmp comparison voltage (feedback to the inverting compatator

input).

By voltage comparison, Vcmp is the operational amplifier output

voltage:

Vcmp Io R Iref {A}cmp R

(1)

where Iref is the reference current. Vcmp is proportional to the partial result

{A}cmp and is compared to Vin.

By current comparison, Vcmp is the voltage in the Io pin of DAC IC:

Vcmp Vin Io R Vin Iref {A}cmp R

(2)

It represents the difference between Vin and the voltage drop across

R and it is compared to zero. Obviously, the following comparisons are

logically equivalent:

Vcmp (7.1) Vin Vbit 1

(3)

Vcmp (7.1) Vin Vbit 0

Vcmp (7.2) 0 Vbit 1

(4)

Vcmp (7.2) 0 Vbit 0

Consequently, the command logic circuit behaves identically for the two

comparison types.

7

Data Conversion and Acquisition Systems - Lab Manual

Vbit the comparator output signal.

Clk clock signal. Any state change of the command state machine can

only occur on the active (rising) slope of the Clk signal. Correspondingly,

the value of the input signal Vbit is relevant for the circuit behavior only at

these moments. For correct behavior, the Clk period should be greater than

the sum of setting times for all the components in the feedback loop:

command logic, DAC, comparator and, eventually, operational amplifier.

{A}cmp - partial result for the current conversion step. In step i, bits

a1...ai-1 are already determined (they already have the values they will have

in the final result also), bit ai is logical 1 (halves the current search-range of

Vin) and bits ai+1...an are logical 0 yet.

{A} - final digital result of the conversion. It is updated at the end of

each conversion and keeps its value during the whole next conversion.

V{A} graphic representation of binary number {A}. Could be seen as

Vin signal re-build, trough an analog-to-digital-to-analog conversion.

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Chapter 6Document42 pagesChapter 6Henry MaedaNo ratings yet

- Analog To Digital ConverterDocument11 pagesAnalog To Digital ConverterFf Fr100% (1)

- Analog To Digital ConvertDocument20 pagesAnalog To Digital ConvertluxiaofengNo ratings yet

- Low Power 1.8V 0.18μm CMOS SAR ADCDocument5 pagesLow Power 1.8V 0.18μm CMOS SAR ADCMiguel BrunoNo ratings yet

- Application of MATLAB SIMULINK and PSPICE Simulation in Teaching Power Electronics and Electric Drive SystemDocument5 pagesApplication of MATLAB SIMULINK and PSPICE Simulation in Teaching Power Electronics and Electric Drive SystemRaghava KatreepalliNo ratings yet

- Paper Single Slope ADCDocument4 pagesPaper Single Slope ADCArdittoTrianggada100% (1)

- Design of An ADC Using High Precision Comparator With Time Domain Offset CancellationDocument4 pagesDesign of An ADC Using High Precision Comparator With Time Domain Offset CancellationijtetjournalNo ratings yet

- Unit Iv Data Converters: Types of Analog To Digital ConvertersDocument3 pagesUnit Iv Data Converters: Types of Analog To Digital ConvertersAshrith LadiNo ratings yet

- Central University of Punjab: BhatindaDocument14 pagesCentral University of Punjab: Bhatindaaayush tomarNo ratings yet

- Me 365 Experiment 2 Introduction To Digital Data Acquisition ObjectivesDocument13 pagesMe 365 Experiment 2 Introduction To Digital Data Acquisition ObjectivesSenthil KumarNo ratings yet

- Project Report On OPDocument13 pagesProject Report On OPVarun PathaniaNo ratings yet

- Flyback ConverterDocument19 pagesFlyback Convertergpalencia_1No ratings yet

- Chapter 1 IntroductionDocument39 pagesChapter 1 IntroductionNivedini KuttiNo ratings yet

- L4 EaDocument7 pagesL4 EaIoanaNicoletaNo ratings yet

- Tutorial Ultracapacitor Model 1Document8 pagesTutorial Ultracapacitor Model 1VinardoPriyadiRahmanNo ratings yet

- Bel - 16 - ADC and DACDocument26 pagesBel - 16 - ADC and DACBharavi K SNo ratings yet

- Oregon State OR 9733 I, USA: Jipeng Gil-Cho Ahn, Dong-Young Chang, and Un-Ku MoonDocument4 pagesOregon State OR 9733 I, USA: Jipeng Gil-Cho Ahn, Dong-Young Chang, and Un-Ku MoonAlex WongNo ratings yet

- Updated Simlab ManualDocument46 pagesUpdated Simlab ManualSumanthNo ratings yet

- Study of Various ADCs and Compare Their Performance and ParametersDocument12 pagesStudy of Various ADCs and Compare Their Performance and ParametersijaertNo ratings yet

- AnalogDocument16 pagesAnalogchandushar1604No ratings yet

- Analog-To-Digital Conversion Btech IIIDocument50 pagesAnalog-To-Digital Conversion Btech IIILisa BhagatNo ratings yet

- Analog To Digital ConverterDocument7 pagesAnalog To Digital Convertersaima alamNo ratings yet

- berkes_interfacing exp arrangementDocument20 pagesberkes_interfacing exp arrangementAditya K NNo ratings yet

- What Is The Advantages and Disadvantages of Analog and Digital InstrumentDocument22 pagesWhat Is The Advantages and Disadvantages of Analog and Digital Instrumentabishek_bhardwa866645% (20)

- Anna University Lab Manuals For Engineering Students - HALF WAVE RECTIFIERDocument13 pagesAnna University Lab Manuals For Engineering Students - HALF WAVE RECTIFIERDayanand Gowda KrNo ratings yet

- Cadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyDocument6 pagesCadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyUtsavNo ratings yet

- Analog To Digital ConvertersDocument11 pagesAnalog To Digital Convertersمحمد ماجدNo ratings yet

- Pipeline ADC TutorialDocument8 pagesPipeline ADC TutorialAlexandre KennedyNo ratings yet

- TI Data Converter GuideDocument16 pagesTI Data Converter GuideDavid PostonNo ratings yet

- Computer Modeling and Simulation of PWM Converter CircuitsDocument27 pagesComputer Modeling and Simulation of PWM Converter CircuitsskrtamilNo ratings yet

- Electric Circuits I: Laboratory Guide ForDocument67 pagesElectric Circuits I: Laboratory Guide ForMisa KurobaneNo ratings yet

- Inter Grating AdcDocument6 pagesInter Grating AdcthắngNo ratings yet

- Dual Slope ADC DesignDocument10 pagesDual Slope ADC DesignMoHaMMeD HaLaByNo ratings yet

- Analog Inputs and Outputs: Voltage LogicalDocument29 pagesAnalog Inputs and Outputs: Voltage LogicalmdkhandaveNo ratings yet

- MATLAB LAB ManualDocument36 pagesMATLAB LAB Manuals sivaNo ratings yet

- 5-10-12 - Analog To Digital ConverterDocument49 pages5-10-12 - Analog To Digital ConverterjagdaNo ratings yet

- ET 304A Laboratory Tutorial-Circuitmaker For Transient and Frequency AnalysisDocument7 pagesET 304A Laboratory Tutorial-Circuitmaker For Transient and Frequency AnalysisZhong XiangNo ratings yet

- Small-Signal Model of A 5kW High-Output Voltage Capacitive-Loaded Series-Parallel Resonant DC-DC ConverterDocument7 pagesSmall-Signal Model of A 5kW High-Output Voltage Capacitive-Loaded Series-Parallel Resonant DC-DC ConverterAshok KumarNo ratings yet

- PSpice Tutorial for Circuit SimulationDocument14 pagesPSpice Tutorial for Circuit SimulationHuỳnh Thanh DưNo ratings yet

- Experiment No: 1 Aim:: To Study Commands of PspiceDocument18 pagesExperiment No: 1 Aim:: To Study Commands of PspiceRudra Kumar MishraNo ratings yet

- Data ConversionDocument4 pagesData ConversionpauliNo ratings yet

- Digitally Removing A DC Offset: DSP Without Mathematics: WP279 (v1.0) July 18, 2008Document16 pagesDigitally Removing A DC Offset: DSP Without Mathematics: WP279 (v1.0) July 18, 2008santanu_sinha87No ratings yet

- Performing Worst-Case Circuit Analysis With LTspice - Technical ArticlesDocument10 pagesPerforming Worst-Case Circuit Analysis With LTspice - Technical ArticlesMichael MargoleseNo ratings yet

- Sar AdcDocument40 pagesSar AdcNivedini KuttiNo ratings yet

- Design of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTADocument22 pagesDesign of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTAZarion JacobsNo ratings yet

- Project 2 ElectronicDocument23 pagesProject 2 ElectronicOmar Eduardo Rios GuzmanNo ratings yet

- Digital Protective RelayDocument3 pagesDigital Protective RelayjannumitsNo ratings yet

- R - KZ I: A 12-Bit ADC Successive-Approximation-Type With Digital Error CorrectionDocument10 pagesR - KZ I: A 12-Bit ADC Successive-Approximation-Type With Digital Error CorrectionMiguel BrunoNo ratings yet

- Fast Ac Electric Drive Development Process Using Simulink Code Generation PossibilitiesDocument9 pagesFast Ac Electric Drive Development Process Using Simulink Code Generation Possibilitiesmechernene_aek9037No ratings yet

- Student Name Ali Abdullah Mohammed Ameen: Class 3 BDocument13 pagesStudent Name Ali Abdullah Mohammed Ameen: Class 3 Bالزهور لخدمات الانترنيتNo ratings yet

- SRMSCET Bareilly Electrical Simulation Lab ExperimentsDocument28 pagesSRMSCET Bareilly Electrical Simulation Lab Experimentssachin10dulkarNo ratings yet

- Half Wave Rectifier Circuit SimulationDocument33 pagesHalf Wave Rectifier Circuit SimulationHomoudAlsohaibi100% (2)

- Computer Modeling and Simulation of PWM Converter CircuitsDocument27 pagesComputer Modeling and Simulation of PWM Converter CircuitsAshok KumarNo ratings yet

- Analog To Digital ConverterDocument4 pagesAnalog To Digital Convertermuzamiru Kahise sayumweNo ratings yet

- Understanding Integrating ADC AN1041Document7 pagesUnderstanding Integrating ADC AN1041dileepank14No ratings yet

- Analog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and EngineeringDocument61 pagesAnalog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and Engineeringvadla77No ratings yet

- Practical No6Document5 pagesPractical No6NidhiNo ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Lab 5 Identifying The Digital-Analog Converter Parameters, Using The Signal ShapesDocument4 pagesLab 5 Identifying The Digital-Analog Converter Parameters, Using The Signal ShapesIoanaNicoletaNo ratings yet

- L4 EaDocument7 pagesL4 EaIoanaNicoletaNo ratings yet

- Lab 2. Binary Integer Representation. Normal ValuesDocument6 pagesLab 2. Binary Integer Representation. Normal ValuesIoanaNicoletaNo ratings yet

- The GNU General Public LicenseDocument7 pagesThe GNU General Public LicenseIoanaNicoletaNo ratings yet

- L1 EaDocument15 pagesL1 EaIoanaNicoletaNo ratings yet

- An 931 Appnote Ad7689Document4 pagesAn 931 Appnote Ad7689Gunta AkhiriNo ratings yet

- Solar Turbines Taurus 65 Data SheetDocument2 pagesSolar Turbines Taurus 65 Data SheetLuis SanguinettiNo ratings yet

- John Deere Diesel GensetDocument2 pagesJohn Deere Diesel Gensetnanocycle0% (1)

- Modeling of Three-Phase Induction Motor Inverter Fault Using SimulinkDocument13 pagesModeling of Three-Phase Induction Motor Inverter Fault Using SimulinkAmir RasyadanNo ratings yet

- Design of Starters and Their TypesDocument20 pagesDesign of Starters and Their TypesSai Pranahita KulithalaiNo ratings yet

- ACKTS Unit 3 Subjective QuestionsDocument3 pagesACKTS Unit 3 Subjective QuestionsRaviNo ratings yet

- 55 - B - 5 - Physics For VI CandidatesDocument27 pages55 - B - 5 - Physics For VI CandidatesOm TripathiNo ratings yet

- ZTX689B ZTX689B: NPN Silicon Planar Medium Power High Gain TransistorDocument3 pagesZTX689B ZTX689B: NPN Silicon Planar Medium Power High Gain TransistorAdrian NaeNo ratings yet

- SPB Power Supply Fuente de Poder Sistema Contra IncendiosDocument4 pagesSPB Power Supply Fuente de Poder Sistema Contra IncendiosEduard MachadoNo ratings yet

- Converting Watts & Amps To 12V Run TimesDocument2 pagesConverting Watts & Amps To 12V Run TimesWaqar AhmedNo ratings yet

- Earthing & Lightning Protection System TrainingDocument25 pagesEarthing & Lightning Protection System TrainingNaushad Haider100% (1)

- Arsenic For High Capacity Lithium and Sodium-Ion BatteriesDocument11 pagesArsenic For High Capacity Lithium and Sodium-Ion BatteriesLIZANA QUISPE ELMER ARSENIONo ratings yet

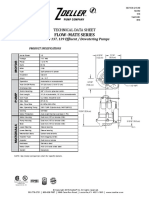

- Flow-Mate Series: Technical Data SheetDocument2 pagesFlow-Mate Series: Technical Data SheetDavid LucioNo ratings yet

- Nathan Stubblefield Earth BatteryDocument5 pagesNathan Stubblefield Earth Batteryanakin68100% (3)

- Clipper and ClamperDocument35 pagesClipper and ClamperRahul YadavNo ratings yet

- SIMCO FMX003 Field Meter UsersDocument11 pagesSIMCO FMX003 Field Meter UsersZE ARRUELANo ratings yet

- JBL Manual - Northridge E150PDocument8 pagesJBL Manual - Northridge E150PionelflorinelNo ratings yet

- The Spin Force - A Collection of Articles & Experiments 2nd EditionDocument187 pagesThe Spin Force - A Collection of Articles & Experiments 2nd EditionJorge Casalini100% (3)

- A-1.JSA-Service Panel & U.P.SDocument1 pageA-1.JSA-Service Panel & U.P.SVivek SinghNo ratings yet

- LCD Thermostat 2Document27 pagesLCD Thermostat 2Mauro MarafonNo ratings yet

- Ohms Law and ResistanceDocument9 pagesOhms Law and ResistanceMarco Ramos JacobNo ratings yet

- Helion Invictus 10 MT: Owner's ManualDocument36 pagesHelion Invictus 10 MT: Owner's ManualalexgkkNo ratings yet

- EAMCET 2015 - EngineeringDocument26 pagesEAMCET 2015 - EngineeringNeepur Garg100% (1)

- RF FiltersDocument10 pagesRF Filtersec academicNo ratings yet

- English MCCBDocument81 pagesEnglish MCCBLeed ENNo ratings yet

- High Speed Can Bus Transceiver: DescriptionDocument9 pagesHigh Speed Can Bus Transceiver: Descriptionsweety987No ratings yet

- Aiwa - 4ZG - 1A, 1B e 1Z-MecanicaDocument70 pagesAiwa - 4ZG - 1A, 1B e 1Z-MecanicaSergioNo ratings yet

- Ford Pin DVDocument17 pagesFord Pin DVjtfjtf100% (1)

- W005F.... W10F: 1.5 A 50 V To 1000 VDocument4 pagesW005F.... W10F: 1.5 A 50 V To 1000 VBraulio Manuel Trejo PerezNo ratings yet

- NASA GEVS Standard Provides Environmental Testing RequirementsDocument203 pagesNASA GEVS Standard Provides Environmental Testing RequirementsAGonzalezNo ratings yet