Professional Documents

Culture Documents

Chapitre 4 Archi - Etudiants

Uploaded by

Mariem RouissiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapitre 4 Archi - Etudiants

Uploaded by

Mariem RouissiCopyright:

Available Formats

Chapitre 4 :

Programmation du microprocesseur Intel 8086

I.

Prsentation du processeur Intel 8086

LIntel 8086, dvelopp en 1978, est le premier microprocesseur de la famille des intel x86.

Il est bas sur des registres 16 bits, et dispose d'un bus externe de donnes de 16 bits et d'un bus

d'adresse de 20 bits.

Sa puissance de calcul varie de 0,33 MIPS (lorsqu'il est cadenc 4.77 MHz) jusqu' 0,75 MIPS

pour la version 10 MHz.

I.1. Architecture interne du microprocesseur 8086

Le 8086 est constitu de deux units fonctionnant en parallle et dun ensemble de registres :

Lunit dinterface avec le bus (BIU : Bus Interface Unit) : elle calcule des adresses relles

(sur 20 bits) recherche les instructions en mmoire et les range dans une file dattente de 6

octets.

Lunit dexcution (EU : Execution Unit) : elle dcode et excute les instructions ranges

dans la file dattente

Figure 1 : Architecture interne du microprocesseur Intel 8086

1

Les registres

- Les registres gnraux :

Le 8086 fournit 4 registres gnraux (AX, BX, CX et DX) de 16 bits

Chacun de ces registres peut tre dcompos en deux registres de 8 bits. L et H dsignent

respectivement loctet bas (LOW) et loctet Haut (High)

AX = (AH, AL)

BX = (BH, BL)

Nom

AX (Accumulateur)

Fonction

Utilis pour les oprations arithmtiques telles que MUL (multiplication) ou

DIV (Division) + oprations dE/S

Utilis lors de laccs une zone sous forme de tableau ; il reprsente

lindice du tableau. Il peut aussi tre utilis pour ladressage

Utilis lors de lappel dinstructions comme REP (rpter) ou LOOP

(Boucle) comme compteur

Utilis gnralement pour stocker des donnes provisoires. Il peut servir

comme extension au registre AX + contenir le port dentre sortie

BX (Base)

CX (Compteur)

DX (Donnes)

CX = (CH, CL)

DX = (DH, DL)

- Registres de pointeurs et dindex : 4 registres de 16 bits

Nom

Fonction

Registre dindexe utilis lors doprations sur les chanes de caractres, il

SI (Source Index)

dsigne la variable source --> data

DI (Destination Index) Registre dindexe utilis lors doprations sur les chanes de caractres, il

dsigne la variable destination --> extra

BP (Base Pointer)

Registre de base utilis pour contenir ladresse de base dune structure de

donnes en mmoire (tableau,..) --> pile

SP (Stack Pointer)

Pointeur de pile, il indique le dernier lment de la pile point --> pile

- le registre pointeur dinstruction :

IP (Instruction Pointer) : registre sur 16 bits qui indique la prochaine instruction excuter.

- Les registres segment :

Ils sont utiliss pour identifier les 4 segments de code, de donnes de pile et le segment extra.

Nom

CS (Code Segment)

DS (Data Segment)

SS (Stack Segment)

ES (Extra Segment)

Fonction

Mmorise le segment o se trouve le code en cours dexcution

Mmorise le segment o se trouve les donnes du programme

Mmorise le segment o se trouve la pile de donnes du programme

Mmorise le segment supplmentaire pour les donnes

- Le registre dtat : (Voir dtails en annexe)

O D I T S Z

CF: Indicateur de retenue

PF : Indicateur de Parit

AF : Indicateur de retenue auxiliaire

ZF : Indicateur Zro

SF : Indicateur de signe

TF : Indicateur dexcution pas pas (trap)

IF : Indicateur dautorisation dinterruption

DF : Indicateur de dcrmentation

OF: Indicateur de dpassement

I.2. Gestion de la mmoire par le 8086

I.2.1. Organisation de la mmoire

Lespace mmoire adressable par le 8086 est de 220 = 1 048 576 octets = 1 Mo (20 bits dadresses).

Cet espace est divis en segments. Un segment est une zone mmoire de 64 Ko (65 536 octets)

dfinie par son adresse de dpart qui doit tre un multiple de 16.

Figure 2 : Organisation de la mmoire

Chacun des 4 registres de segment pointe sur lorigine de lun des 4 segments :

Le segment de code : CS : Il contient le code du programme courant. Lorigine de ce

segment est plac dans le registre de segment CS, CS et IP pointent toujours sur linstruction

suivante excuter (CS :IP).

Le segment de donnes : DS : Il contient les donnes courantes du programme : cest le

segment source lors dune opration de traitement dune chane de caractres. Origine : DS :SI

Le segment de donnes Extra : ES : Il contient les donnes en dehors du programme

courant, cest le le segment de destination lors dune opration sur une chane de caractres.

Origine : ES : DI

Le segment de pile : SS : Il contient toutes les informations stockes dans la pile. SS : SP

pointe sur le dernier lment empil.

Figure 3 : Organisation des diffrents segments dans la mmoire

Remarque : Les segments ne sont pas ncessairement distincts les uns des autres, ils peuvent se

chevaucher ou se recouvrir compltement.

I.2.2.Adressage du 8086

Les adresses relles du 8086 scrivent sur 20 bits, or tous les registres du 8086 sont de 16 bits, une

case mmoire est repre au moyen de 2 champs de 16 bits :

Ladresse dun segment

Le dplacement ou offset (appel aussi adresse effective) dans ce segment.

La donne du couple (segment, offset) not segment :offset dfinit une adresse logique.

Ladresse dune case donne sur 20 bits (5 digits hexa) est appele adresse relle ou adresse

physique car elle correspond la valeur relle envoye sur le bus dadresses.

Correspondance entre adresse logique et adresse physique :

Adresse physique = 16 * adresse segment + offset

Adresse relle est obtenue en dcalant le registre segment de 4 positions binaires vers la gauche et

en lui ajoutant loffset

Exemple : (4055 : 3192) = 40550 + 3192 = 436E2

II. Structure dun programme assembleur

II.1. Directives

Les directives sont des dclarations lintention de lassembleur (FASM, NASM, TASM,

MASM) pour le guider. A la diffrence des instructions, elles ne gnrent pas de code machine.

Exemples de directives FASM (Flat ASM) :

use 16 : indique quon souhaite compiler du code 16 bits

org : Origine du programme en mmoire : Exemple : org 100h le programme est charg en

mmoire partir de ladresse 100h

II.2. Squelette dun programme

Un programme assembleur comprend gnralement les parties suivantes :

Dfinition des donnes dclares par des directives

Cur du programme form par les instructions

Exemple : Structure dun programme FASM

org 100 h

4

; Le code

II.3. Dfinition des donnes

II.3.1. Dfinition des constantes

Syntaxe: NOM EQU valeur

Exemples :

escape EQU 1bh

Dix EQU 10

II.3.2. Dfinition des variables

Syntaxe: NOM Directive_de_donnes valeur[, val2, val3,]

Exemples :

Val DB 2Fh (Define Byte): Val rfrence une donne code sur 1 octet dont la valeur initiale

est 47

Char DB B ; 1 octet initialis B : cest son code ASCII (66) qui va tre mmoris

Entree DW 10 (Define Word): 2 octets initialiss 10 (00000000 00001010)

DVAR DD 12345678h (Define Double Word) 4 octets initialiss la valeur hexadcimale

12345678

0001 0010 0011 0100 0101 0110 0111 1000

Message DB Salem ; dfinit une chane de caractres : quivalent : Message DB S,

a,l,e,m

Tab DB 10, 20 ; Tableau de deux cases initialises respectivement 10 et 20.

Exemple illustratif :

machin DB 10, 0FH

chose DB -2, ALORS

Lorsquon veut dclarer un tableau de n cases, toutes initialises la mme valeur, on utilise la

directive dup

Tab DB 10 dup (0) : Tableau de 10 octets initialises chacune la valeur 0

Tab DW 5 dup (?) : Tableau de 5 mots de 16 bits non initialiss

Remarque :

Pour rserver des octets (variables non initialises), il est possible dutiliser les directives rb

(reserve byte), rw (reserve word),

Val rb 1 est quivalent Val DB ?

5

III. Instructions du 8086

III.1. Principales instructions

Voir annexe

Exemple 1 : Ecrire un programme en assembleur qui calcule la somme et la moyenne des

valeurs 30 et 40. La somme sera place dans la variable SOM et la moyenne dans la variable

MOY. Donnez 2 solutions en utilisant une fois ladressage immdiat et une fois ladressage

direct (en dclarant 2 variables A = 30 et B = 40)

III.2. Les structures conditionnelles

Les structures conditionnelles font appel aux instructions de sauts conditionnels et

inconditionnels.

Instruction de saut inconditionnel

Syntaxe : JMP label

Cette instruction permet deffectuer un saut (jump) vers le label spcifi.

; Instructions prcdant le saut conditionnel

JMP label ; Instruction de saut

; Instructions ne seront pas excutes

label :

. ; Instructions excutes aprs le saut

Exemple :

MOV AX, 2

Et : INC AX ; Boucle infinie

JMP Et

Instructions de sauts conditionnels

Syntaxe : Jcondition label

Un saut conditionnel nest excut que si une condition (qui porte sur un ou plusieurs flags)

est vrifie.

; Instructions prcdant le saut conditionnel

Jcondition label

; Condition de saut

; Instructions excutes si la condition nest pas vrifie

label :

. ; Instructions excutes si la condition est vrifie

Remarque : Les indicateurs dtat sont positionns en fonction du rsultat de la dernire

instruction.

Exemples : JZ, JNZ, JZ, JB, Voir polycope

Structure conditionnelle simple

Algorithmique

Assembleur

Si (condition) Alors Jcondition Etiquette

Traitement 1

Sinon

Traitement 2

JMP Suite

Traitement 2

Etiquette :

Finsi

Traitement 1

Suite

Suite :

Exemple 2 : Ecrire un programme en assembleur qui place dans une variable Max, le maximum de

deux valeurs 70 et 80.

Structure conditionnelle multiple

Algorithmique

Si (condition 1) Alors

Traitement 1

Assembleur

Jcondition1 Etiquette1

Jcondition2 Etiquette2

Sinon Si (condition 2) Alors

Traitement 3

Traitement 2

Sinon

JMP Suite

Etiquette2 :

Traitement 3

Traitement 2

Finsi

JMP Suite

Suite

Etiquette1 :

Traitement 1

Suite :

Exemple 3 : Ecrire un programme en assembleur qui fait la soustraction de deux nombres qui

valent respectivement 30 et 50 et qui placent dans une variable res le caractre p si (a-b) > 0, le

caractre n si (a-b) < 0 et le caractre e si (a-b) = 0

III.3. Les structures rptitives

Algorithmique

Assembleur

Pour compteur de 1 ValFin MOV CX, ValFin

faire

Pour :

{

{

Traitement

Traitement

}

}

FinPour

LOOP Pour

; LOOP dcrmente

MOV CX, ValFin

Pour :

{

Traitement

DEC CX

}

JNZ Pour

Rpter

REPETER:

{

Traitement

Traitement

; code pour positionner les flags selon la condition

}

Jusqu (ConditionSortie)

JXX REPETER

; JXX dsigne la condition de rptition

Tant

faire

que

(ConditionVrifie) TANTQUE :

; code pour positionner les flags

Traitement

JXX Suite ; JXX dsigne la condition de non excution de la

boucle

Traitement

FTQ

Suite

JMP TANTQUE

Suite :

Exemple 4 : Soit un tableau de 10 octets initialis aux valeurs suivantes : 1, 2, 3, 4, 5, 6, 7, 8, 9, 10.

En utilisant la structure rptitive POUR, donnez la somme de ces valeurs. Le rsultat sera plac

dans la variable SOM. Donnez les 2 variantes avec linstruction LOOP et JNZ.

III.4. Les entres sorties

Les entres sorties se font par lintermdiaire des interruptions BIOS et DOS.

Linstruction INT n permet dappeler la nime fonction de la table des vecteurs dinterruptions (n

est compris entre 0 et 255)

Les fonctions du DOS sappellent laide du vecteur 21h, la valeur du registre AH permet

dindiquer quelle est la fonction que lon appelle

Syntaxe : MOV AH, nfonction

Int 21h

Numro

01 H

02 H

09H

0AH

Fonction

Lecture du caractre: Met dans AL le code ASCII du caractre saisi

Affichage du caractre dont le code ASCII est plac dans le registre DL

Affichage dune chane de caractres dont ladresse de dbut est place dans DX

Lecture dune chane de caractres place dans DX o la premire case rfrence la taille

maximale de la chane et la 2me case rfrence le nombre de caractres rellement saisis

Tableau 7 : Principales interruptions dentre/ sortie

Remarque :

La saisie sarrte quand on tape sur le retour la ligne (Code ASCII 13), ce dernier est

comptabilis.

DX : adresse du tampon T o sera stocke la chane saisie

[T] doit tre initialis la taille maximale de la chane saisir

Exemple 5 : Ecrire un programme en assembleur qui permet dafficher les lettres de lalphabet en

majuscule

ANNEXE 1 : Registre dtat

Le registre dtats comprend un ensemble de flags comme suit:

OD I T S Z

CF : Bit de retenue qui indique quune retenue sest propage partir du bit le plus significatif

dune oprande 8 ou 16 bits la suite dune opration arithmtique.

PF : Indicateur de parit qui prend la valeur 1 si le rsultat dune opration contient un nombre pair

de 1.

AF : Indicateur de retenue auxiliaire prend la valeur 1 pour indiquer quune retenue sest propage

du bit 3 (utilis en BCD).

ZF : Bit de zro prend la valeur 1 si le rsultat dune opration est nul.

SF : Bit de signe prend la valeur 1 si le bit le plus significatif du rsultat est 1.

TF : Bit de pas pas (Trap flag), positionn 1, impose au processeur le mode dexcution pas

pas dans le but daider la mise au point des programmes. La commande trace de debug utilise

cette particularit pour afficher le contenu des registres.

IF : Bit de validation des interruptions, positionn 1, les interruptions externes sont autorises.

DF : Bit de direction : contrle le sens dvolution dans une chane de donnes, si DF = 1, il y a

auto dcrmentation des registres SI et DI et auto incrmentation si DF = 0.

OF : Bit de dbordement de capacit utilis e arithmtique signe qui indique que lopration

arithmtique est sortie de la gamme du systme de numration.

ANNEXE 2 : Principales instructions du microprocesseur Intel 8086

Instructions de transfert de donnes

Instruction

MOV d,s

PUSH s

POP d

IN d, adr

OUT adr, s

Rle

Copie de la source dans la destination (dun octet ou dun mot)

Empilement de s dans la pile

Dpilement du sommet de la pile dans d

Lecture dun port dE/S ladresse adr

Ecriture dans un port dE/S

Instructions arithmtiques

Instruction

Rle

ADD opd, ops Addition de opd et ops, le rsultat est plac dans opd

SUB opd, ops Soustraction de opd et ops, le rsultat est plac dans opd

MUL op

Multiplication de AL par op (8 bits), le rsultat (16 bits) est plac dans AX

Multiplication de AX par op (16 bits), le rsultat est plac dans DX :AX

DIV op

Division de AX par op8, le rsultat est plac dans AL et le reste dans AH

Division de DX :AX par op16, le rsultat est mis dans AX et le reste dans DX

INC op

Incrmentation de op

DEC op

Dcrmentation de op

NEG op

Remplace op par son ngatif (complment 2)

CMP op, val Comparaison de op la valeur val (les drapeaux sont positionns)

CBW

Covert Byte to Word : Extension de AL dans AH

CWD

Convert Word to Double Word: Extension de AX dans DX

Instructions logiques

Instruction

Rle

NOT op

Complment 1 de op (les 0 deviennent des 1 et inversement)

AND opd, ops ET logique de deux octets ou de deux mots

OR opd, ops OU logique de deux octets ou de deux mots

Instructions de branchement conditionnel

Instruction

JE adr / JNE adr

JZ adr/ JNZ adr

JB adr /JNB adr

JC adr /JNC adr

LOOP adr

LOOPZ adr

Rle

Saut ladresse adr si galit / si non galit

Saut ladresse adr si Z= 1 / si Z = 0

Saut ladresse adr si infrieur (Bellow) cd si CF = 1 / si CF = 0

Saut ladresse adr sil y a retenue cd si CF = 1 / si CF = 0

Dcrmentation automatique de CX + saut ladresse adr si CX non nul

Bouclage tant que CX <> 0 et Z = 1

Instructions de branchement inconditionnel

Instruction

JMP adr

CALL adr

RET

Int n

Rle

Saut vers ladresse adr

Appel dun sous programme

Retour dune procdure

Appel linterruption logicielle n n

You might also like

- Poteau Recommandations ProfDocument8 pagesPoteau Recommandations ProfAbderahim KasmiNo ratings yet

- Codes Erreur LG Multi InvertersDocument21 pagesCodes Erreur LG Multi Invertersnovy80% (20)

- La Fabrication Du ProjetDocument19 pagesLa Fabrication Du Projetأحمد أمين العلويNo ratings yet

- Spec Des PylônesDocument2 pagesSpec Des PylônesToto DjadjameNo ratings yet

- Kit de Traversée-Écran Universel - VDEFDocument2 pagesKit de Traversée-Écran Universel - VDEFpaulNo ratings yet

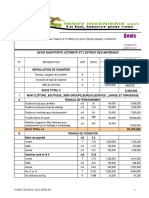

- Devis 2 SS+R+1Document3 pagesDevis 2 SS+R+1nanfack100% (6)

- Ens Ens Ens STD Opt Dig Gie 002 A3Document262 pagesEns Ens Ens STD Opt Dig Gie 002 A3JonathanNo ratings yet

- Exemple de Devis de StationDocument35 pagesExemple de Devis de StationFode Bangaly Keita87% (15)

- DocumentDocument10 pagesDocumentDavid HoffmanNo ratings yet

- DP La Fabrique Du Vivant WebDocument43 pagesDP La Fabrique Du Vivant Webm.cNo ratings yet

- CH04-Analyse 2014 PDFDocument53 pagesCH04-Analyse 2014 PDFEtienne LechasseurNo ratings yet

- Installation de Réseaux Et Traitement de DonnéesDocument8 pagesInstallation de Réseaux Et Traitement de DonnéesNounou BenelzineNo ratings yet

- Presse A InjectionDocument10 pagesPresse A Injectiontreda100% (1)

- Comment Mettre Un Fichier Odt en PDFDocument2 pagesComment Mettre Un Fichier Odt en PDFSamanthaNo ratings yet

- Dallage - Les Différents Types de Dalles Et Leur PrixDocument11 pagesDallage - Les Différents Types de Dalles Et Leur PrixIrénée SorghoNo ratings yet

- CV Ibra Gueye Com-2Document1 pageCV Ibra Gueye Com-2Mamadou GueyeNo ratings yet

- Syllabus OA PDFDocument60 pagesSyllabus OA PDFHidlerNo ratings yet

- Avancement Des TravauxDocument7 pagesAvancement Des Travauxmaryem LaaorfNo ratings yet

- TP Routage OspfDocument2 pagesTP Routage OspfMahiout Rymane50% (2)

- Devis Quantitatif Et Estimatif Gros OeuvresDocument3 pagesDevis Quantitatif Et Estimatif Gros OeuvresLe Kamben100% (1)

- Artzimut 4 Promenades D'art À PerpignanDocument2 pagesArtzimut 4 Promenades D'art À Perpignanantou74No ratings yet

- PROXM Formation Proxmox Ve PDFDocument2 pagesPROXM Formation Proxmox Ve PDFCertyouFormationNo ratings yet

- Notes de Cours WindowsDocument3 pagesNotes de Cours WindowsOmar Oughzal100% (1)

- Convention de Dessin (Ok+)Document26 pagesConvention de Dessin (Ok+)mpmariusNo ratings yet

- Creation de Reseaux Locaux Virtuels Et Affectation de PortsDocument4 pagesCreation de Reseaux Locaux Virtuels Et Affectation de PortsradouaneNo ratings yet

- Dimensionnement Des Ponts Par Précontrainte AdditionnelleDocument186 pagesDimensionnement Des Ponts Par Précontrainte AdditionnelleRedallah50% (2)

- Metre Main D'ouvreDocument8 pagesMetre Main D'ouvreyassineharfideNo ratings yet

- F. Choay Allegorie Du PatrimoineDocument10 pagesF. Choay Allegorie Du PatrimoineAndreea Larisa RadionNo ratings yet

- Notice 51434#04Document38 pagesNotice 51434#04AdrienNo ratings yet

- Sujets ExercicesDocument150 pagesSujets Exercicesbrayam11No ratings yet