Professional Documents

Culture Documents

Architecture and Design of Generic IEEE-754 Based Floating Point Adder, Subtractor and Multiplier

Uploaded by

Editor IJRITCCCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Architecture and Design of Generic IEEE-754 Based Floating Point Adder, Subtractor and Multiplier

Uploaded by

Editor IJRITCCCopyright:

Available Formats

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 5

ISSN: 2321-8169

2690 - 2694

_______________________________________________________________________________________________

Architecture and Design of Generic IEEE-754 Based Floating Point Adder,

Subtractor and Multiplier

Sahdev D. Kanjariya

Rutarth Patel

VLSI & Embedded Systems Design

Gujarat Technological University PG School

Ahmedabad, India

sahdev.kanjariya@gmail.com

VLSI & Embedded Systems Design

Gujarat Technological University PG School

Ahmedabad, India

rutarth91@gmail.com

Abstract The Floating point numbers are being widely used in various fields because of their great dynamic range, high precision and easy

operation rules. In this paper, architecture of generic floating point unit is proposed and discussed. This generic unit is compatible with all three

IEEE-754 binary formats. Further based on this architecture, floating point adder, subtractor and multiplier modules are designed and

functionally verified for Virtex-4 FPGA. The design is working properly and giving accurate result up to the last point.

Keywords- Floating point; IEEE-754; FPGA; Generic; Verilog HDL

__________________________________________________*****_________________________________________________

I.

INTRODUCTION

In terms of computing, Floating point is the method of

representing an approximation to real number with the help of

fixed number of bits. With the increase in digital devices, the

need of having floating point capable hardware on the same

device is also increasing. Applications working with DSP

(Digital Signal Processing), 3D graphics, Image processing etc

can get benefited by including a floating point unit along with

the main processor on the device. Now in these days, Field

Programmable Gate Arrays (FPGAs) are becoming one of the

major platforms to implement and check any complex digital

design because of their high integration density, comparatively

low price, high performance, flexibility and many more others.

This paper mainly focuses on obtaining a basic architecture

which can be used to design a FPU (Floating Point Unit),

which is IEEE-754 standard compliant. A generic architecture

for such FPU is discussed. This architecture can be used to

design any of the three binary formats of floating point

representations, which are: 32-bit (Single Precision), 64-bit

(Double Precision) and 128-bit (Quadruple precision). Based

on this design, generic code for the Adder, Subtractor and

Multiplier is written in Verilog HDL (Hardware Description

Language). The code is written such that just by changing

parameters in the code, designs for any of the available format

are obtained. Furthermore these sub modules are obtained and

each module is functionally verified separately. This FPU is

designed for Virtex-4 FPGA platform. Implementation part of

the whole design is still remaining and will be done in future.

The rest of the paper is organized as follows: Section II

describes all the literature surveyed for this paper. These

include some research papers as well as standards and manuals.

Section III gives understanding about the floating point

numbers and operation on them. Section IV provides overview

of the designed Generic units: Adder, Subtractor and

Multiplier. Section V is for discussion on simulations and

results

of

the

all

designed

units.

Furthermore

acknowledgements and conclusion, followed by the references

ends up the paper.

II.

LITERATURE

The IEEE has standardized the binary and decimal floating

point computer representation and rules about them in their

standard IEEE-754. Current version of the standard is IEEE

754-2008[1]. For understanding floating point numbers

properly, this standard is studied in detail.

Many researchers have worked with the fraction or real

numbers. Many of them have also implemented their designs

on different platforms. Some of them have used single

precision format, some of them have used other options to

represent real numbers like fixed point numbers. The key factor

driving many of the researchers to use floating point numbers

are because of their many advantages over fixed point.

In [2] P. Karlstrom, A. Ehliar and D. Liu designed floating

point adder/subtractor and multiplier units. They have

implemented their design on Virtex-4. However their design is

capable of doing single precision operations only. Also their

design is not fully IEEE-754 standard compatible. It does not

handle infinities, Not-a-Numbers (NaNs) and denormalized

numbers. Getao Liang, JunKyu Lee and Gregory D. Peterson

proposed a dynamic precision supporting architecture for real

number operations in [3]. Their proposed architecture is target

for both, fixed point as well as floating point devices. Their

architecture can work on different precision without need of

changing hardware. They have implemented this architecture

for some fixed point adders and multipliers only. Addanki

Puma Ramesh, A. V. N. Tilak and A. M. Prasad designed and

implemented double precision floating point multiplier in [4].

They have used DSP slices of Virtex-6 FPGA for the

multiplication operation to make best use of the available

resources. Their design handled overflow, underflow and round

to zero (truncation) rounding mode. In [5], Manisha Sangwan

and A Anita Angeline designed and compared different

arithmetic modules and after that they implemented these

modules together. They used single precision format for

floating point numbers. They have not specified anything about

rounding mode as well as different exceptions.

2690

IJRITCC | May 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 5

ISSN: 2321-8169

2690 - 2694

_______________________________________________________________________________________________

III.

FLOATING POINT NUMBERS AND ARITHMETIC

A. Floating point numbers

In floating point format, exponent is used to scale up or

down a number, represented by mantissa. Floating point

format is shown below.

sign(s)

MSB

exponent(e)

mantissa(f)

LSB

Sign field represent sign of the number. Exponent field

represent exponent by which the fraction part will be scaled up

or scaled down. Mantissa field represent fraction part of the

real number. Most of the time, this mantissa or fraction part is

used along with the implicit hidden bit 1 before the mantissa.

This bit is used along with the mantissa to provide precision of

the format. These combinations also represent some special

values[6][7].

IEEE has defined three binary formats for floating point

numbers which are:

i. 32-bit

ii. 64-bit

iii. 128-bit

Multiplication is comparatively easy task for floating point

numbers than the addition and subtraction. The basic steps of

the multiplications are:

Add exponents of two operands to obtain resultant

exponent

Multiply mantissas of the two operands to obtain

resultant significand

Signs of these operands are XORed to obtain resultant

sign

For the final result, still some approximations and round up

need to be done. The resultant significand after multiplying two

mantissas are of double length then the original operands. So

some adjustments needs to be done on this intermediate result

so that significand can be fitted into desired width. Also one

should need to take of overflow or underflow and also make

sure that normalization on resulting significand is done

properly.

IV.

ARCHITECTURE

An architecture for Floating point unit which can perform

arithmetic operations like addition, subtraction or

multiplication at a time is discussed in this paper. This

architecture is shown below.

They have also defined four rounding modes:

i. Round to nearest (even)

ii. Round up

iii. Round down

iv. Round towards zero

Five types of exceptions:

i. Invalid

ii. Division by zero

iii. Underflow

iv. Overflow

v. Inexact

B. Arithmetic

This section gives overview about the arithmetic operation

on the floating point numbers. William Stallings has discussed

about floating point formats and arithmetic operations on these

numbers very well in his book [8].

Addition and subtraction of the two floating point numbers

are done as follows:

In order to add/subtract two mantissas, the exponents of

both the numbers should be made equal.

This is done by calculating difference between two

mantissas and then right shifting the mantissa of the

number with smaller exponent by the same amount as

of difference.

Then both significands are added/subtracted

accordingly to obtain result significand, the result

exponent is the same as the bigger one from both

exponents.

If there is an overflow/underflow during

addition/subtraction of the significands, then it should

be handled by adjusting result exponent accordingly.

Multiplication of two floating point numbers requires

different approach than the previous one.

Figure 1. Basic Architecture of the FPU

This floating point unit shown here is designed to operate

IEEE standard numbers. This architecture is having all

rounding modes and can handle exceptions whichever occurs

during these operations. Input operands and different

controlling signals as well as result and some other signals as

output are shown in architecture.

Descriptions of different blocks of the architecture are

given in the following section.

A. Controller

It will generate and propagate controlling signals for

other modules

Store incoming data (operands) into two registers

Make sure that if operation is addition and either of the

operand is negative, data will be routed towards

subtractor module

Likewise, if the operation is subtraction and either of

the operand in negative, data will be routed towards

adder module, also sign will be adjusted accordingly

The block diagram of the controller is shown in the figure

2.

2691

IJRITCC | May 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 5

ISSN: 2321-8169

2690 - 2694

_______________________________________________________________________________________________

C. Subtractor

Figure 2. Block diagram of Controller

Performs subtraction of the two input operands

Input operands are first separated into their exponent

and mantissa parts

Difference between the two exponents is calculated

Then according to this value, the mantissa of the

smaller operand is shifted right by that value.

After that normal subtraction between two mantissas is

performed to obtain resulting mantissa

The working of the subtractor is almost similar to that of

adder. The only difference is that we have to subtract shifted

mantissa from the other one and also during normalizing, we

have to take care of underflow, if there occurs any opposite to

the overflow in case of addition.

The block diagram of the generic subtractor is shown in the

figure below.

B. Adder

Adds two operands without considering the signs of

the numbers

The input operands are first separated into their

mantissa and exponent parts

The larger operand goes into larger field, smaller

operand into smaller field because of the controlling

from controller module

Then exponents of both operands are made equal by

shifting the significand of the operand with the

smallest exponent (intB) to the right, such that both

exponents become equal

Then significands are added to obtain result

significand

The block diagram of the generic adder module is shown

below.

Figure 4. Block diagram of Subtractor

Figure 3. Block diagram of Adder

D. Multiplier

This unit multiplies two floating point numbers and

provides result which is also a floating point number.

At first, the input operands are separated into their

mantissa and exponent parts.

The mantissa of first operand and the leading 1 (for

normalized numbers) are stored in to one register.

The mantissa of the other operand and the leading 1

(for normalized numbers) are stored in the other

register.

The sign bit of the result is obtained by performing an

XOR on the sign bit of both the operands.

The exponent is obtained by adding the exponent of

first operand with the exponent of the other operand

and then by subtracting bias from this sum.

Result mantissa is obtained by multiplying mantissas

of both operands. Some extra bits are used along with

these bits for further rounding and exception

handlings.

2692

IJRITCC | May 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 5

ISSN: 2321-8169

2690 - 2694

_______________________________________________________________________________________________

The block diagram of the Multiplier unit is shown in the

figure below.

Figure 7. Simulated waveform of 64-bit Adder

Figure 8. Simulated waveform of 32-bit Subtractor

Figure 5. Block diagram of Multiplier

E. Rounding

This module is used to get approximate number from

obtained intermediate results. The mode of rounding can be

decided by the user by providing external output to the unit.

This unit supports all the rounding modes described in the

IEEE standard. Rounding is done to make sure that result after

any arithmetic operation be fitted into the available bits for

final output.

F. Exceptions

In the exceptions module, all of the special cases are

checked for, and if they are found, the appropriate output is

created, and the individual output signals of underflow,

overflow, inexact and invalid will be asserted if the conditions

for each case exist.

V.

Figure 9. Simulated waveform of 64-bit Subtractor

Figure 10. Simulated waveform of 32-bit Multiplier

IMPLEMENTATION AND RESULTS

The above described modules are designed for Virtex-4

FPGA board and simulated to check if the results are

functionally correct or not. Simulation results are shown in the

figures below.

Figure 11. Simulated waveform of 64-bit Multiplier

VI.

CONCLUSION

This paper discussed and designed architecture for floating

point unit, which supports IEEE standard and the architecture

itself can be used to implement any binary floating point format

numbers. Furthermore some basic modules of this FPU is

designed as well as functionally tested for their correctness, and

they are giving very accurate results.

Figure 6. Simulated waveform of 32-bit Adder

2693

IJRITCC | May 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 5

ISSN: 2321-8169

2690 - 2694

_______________________________________________________________________________________________

ACKNOWLEDGMENT

We would like to express our deepest appreciations to all

those who helped us and gave us opportunity to complete this

paper. Special thanks I give to my guide Mr. Rohit Khanna for

helping me throughout my work. Their suggestions and

encouragement helped me in writing this paper.

REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

IEEE Standard for Floating-Point Arithmetic, IEEE Standard

754-2008, 2008

Karlstrom P. et al., High-performance, low-latency fieldprogrammable gate array-based floating-point adder and

multiplier units in a Virtex 4, in Computers & Digital

Techniques, IET, (Volume: 2, Issue: 4), July 2008, pp. 305-313

Getao Liang et al., ALU Architecture with Dynamic Precision

Support, in Application Accelerators in High Performance

Computing (SAAHPC), 2012 Symposium on, Chicago IL, 2012,

pp. 26-33

Ramesh A. P. et al., An FPGA based high speed IEEE-754

double precision floating point multiplier using Verilog, in

Emerging Trends in VLSI, Embedded System, Nano Electronics

and Telecommunication System (ICEVENT), 2013 International

Conference on, Tiruvannamalai, 2013, pp. 1-5

Sangwan M. and Angeline A. A., Design and implementation

of single precision pipelined floating point co-processor, in

Advanced Electronic Systems (ICAES), 2013 International

Conference on, Pilani, 2013, pp. 79-82

Intel 64 and IA-32 Architectures Software Developers

Manual, Volume 1: Basic Architecture; 2014

Numerical Computation Guide; Sun Microsystems, Inc.; Palo

Alto, CA; 2001

William Stallings; Computer Arithmetic; in Computer

Organization and Architecture Designing For Performance;

8/E; Pearson Education, Upper Saddle River, New Jersey; 2009;

pp. 334-344

2694

IJRITCC | May 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

You might also like

- DS TUTORIAL 2 Forecasting Regression AnalysisDocument6 pagesDS TUTORIAL 2 Forecasting Regression AnalysisDebbie Debz0% (1)

- Ed Periodic TableDocument1 pageEd Periodic Tablechrissy_chinNo ratings yet

- Windows 10 - Getting Started With Windows 10Document6 pagesWindows 10 - Getting Started With Windows 10Edina Zulcic Ex MandraNo ratings yet

- Solution Processed Metal Oxide Thin Films for Electronic ApplicationsFrom EverandSolution Processed Metal Oxide Thin Films for Electronic ApplicationsNo ratings yet

- Design and Implementation of Costas Loop For BPSK DemodulatorDocument5 pagesDesign and Implementation of Costas Loop For BPSK DemodulatorBushra AnsariNo ratings yet

- Design and Implementation of Fast Floating Point Multiplier UnitDocument5 pagesDesign and Implementation of Fast Floating Point Multiplier UnitSanthoshReddyNo ratings yet

- Synthesis of Area Optimized 64 Bit Double Precision Floating Point Multiplier Using VHDLDocument4 pagesSynthesis of Area Optimized 64 Bit Double Precision Floating Point Multiplier Using VHDLerpublicationNo ratings yet

- DSPDocument190 pagesDSPMallikarjun AralimaradNo ratings yet

- Introduction To Verilog HDLDocument38 pagesIntroduction To Verilog HDLYeshoda MallikarjunaNo ratings yet

- Single Precision Floating Point ALU: Prof. Vidya Dahake, Prof. Mithilesh MahendraDocument4 pagesSingle Precision Floating Point ALU: Prof. Vidya Dahake, Prof. Mithilesh MahendraLê Xuân HiếuNo ratings yet

- Implementing PID Controllers on Motorola DSP56000/DSP56001Document84 pagesImplementing PID Controllers on Motorola DSP56000/DSP56001vydeoNo ratings yet

- AsmDocument156 pagesAsmSaulencoNo ratings yet

- The K FactorDocument11 pagesThe K FactorSOURAV PRASADNo ratings yet

- Chris Basso APEC Seminar 2021Document128 pagesChris Basso APEC Seminar 2021sabinebachNo ratings yet

- RS232 Communication With PIC MicrocontrollerDocument5 pagesRS232 Communication With PIC Microcontrollerhidad56195No ratings yet

- Factor KDocument10 pagesFactor Kmeaaa770822No ratings yet

- Power Amplifier Linearization Using Singular Value Decomposition AlgorithmDocument4 pagesPower Amplifier Linearization Using Singular Value Decomposition AlgorithmEditor IJRITCCNo ratings yet

- Xyce Reference GuideDocument634 pagesXyce Reference GuideVojislav MedićNo ratings yet

- Using The Mid-Range Enhanced Core PIC16 Devices' MSSP Module For Slave I C CommunicationDocument14 pagesUsing The Mid-Range Enhanced Core PIC16 Devices' MSSP Module For Slave I C CommunicationDario Darius100% (2)

- Micro InterfacingDocument15 pagesMicro InterfacingDeepesh KhanejaNo ratings yet

- I2C Protocol Design For ReusabilityDocument8 pagesI2C Protocol Design For ReusabilityAkshay KashyapNo ratings yet

- I2C Bus Specifications for CMS Tracker 2S & PS ModulesDocument13 pagesI2C Bus Specifications for CMS Tracker 2S & PS ModulesGasthim KiranNo ratings yet

- M68 HC 05Document332 pagesM68 HC 05rullitoNo ratings yet

- Fix Point Implementation of Elementry FunctionsDocument134 pagesFix Point Implementation of Elementry FunctionsmukulkabraNo ratings yet

- AS3842Document10 pagesAS3842kik020No ratings yet

- Loop Gain MeasurementDocument7 pagesLoop Gain MeasurementgubiliNo ratings yet

- DC-DC Converters Feedback and ControlDocument220 pagesDC-DC Converters Feedback and ControlNguyên NghĩaNo ratings yet

- An Improved SEPIC Converter TopologyDocument35 pagesAn Improved SEPIC Converter TopologyDileep GNo ratings yet

- An920 Rev2Document38 pagesAn920 Rev2glamuraNo ratings yet

- Three Stage Battery Charge SLA PDFDocument18 pagesThree Stage Battery Charge SLA PDFzigoto_2n0% (1)

- Diodes Inc - Library - Components - List PDFDocument5 pagesDiodes Inc - Library - Components - List PDFLuciaNo ratings yet

- Steber An LMS Impedance BridgeDocument7 pagesSteber An LMS Impedance BridgebigpriapNo ratings yet

- Free CADDocument19 pagesFree CADKent PawarNo ratings yet

- 1 BJTDiffPairLabDocument11 pages1 BJTDiffPairLaburim11No ratings yet

- Instruction Manual: Digital MultimeterDocument269 pagesInstruction Manual: Digital MultimeterAntonio CarlosNo ratings yet

- 3.1.1.1 Video Demonstration - BIOS - UEFI MenusDocument2 pages3.1.1.1 Video Demonstration - BIOS - UEFI Menusillus fitriyahNo ratings yet

- Order and Rate Constant of a ReactionDocument4 pagesOrder and Rate Constant of a ReactionAbdul RehmanNo ratings yet

- A Beginner's Guide To TIG WeldingDocument5 pagesA Beginner's Guide To TIG WeldingKalaimugilan ArunNo ratings yet

- I2c ProgramDocument2 pagesI2c Programarunan55No ratings yet

- Characterization of Au (OH) 3Document6 pagesCharacterization of Au (OH) 3Nguyen TrangNo ratings yet

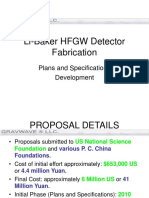

- Li-Baker DetectorDocument32 pagesLi-Baker Detectorapi-397061932No ratings yet

- A Low-Cost Impedance Meter Using a PC Sound CardDocument4 pagesA Low-Cost Impedance Meter Using a PC Sound Carddavorko_tNo ratings yet

- ENGR 451 Lab 2 BJT Differential PairDocument9 pagesENGR 451 Lab 2 BJT Differential PairdgretchenNo ratings yet

- Introduction To VerilogDocument88 pagesIntroduction To Verilogmaster vijayNo ratings yet

- What is UEFI? How to Determine if Your PC Uses UEFI or BIOS (39Document2 pagesWhat is UEFI? How to Determine if Your PC Uses UEFI or BIOS (39Vineeth NandanamNo ratings yet

- An Implementation of I2C Slave Interface Using Verilog HDL: JournalDocument6 pagesAn Implementation of I2C Slave Interface Using Verilog HDL: Journalvisu100% (1)

- IEEE 754 Floating Point NotesDocument4 pagesIEEE 754 Floating Point NotesNathaniel R. ReindlNo ratings yet

- Micro Controller Lab Manual (06ESL47)Document67 pagesMicro Controller Lab Manual (06ESL47)aamreen818No ratings yet

- I2C Bus Overview - The Inter-Integrated Circuit Communication ProtocolDocument19 pagesI2C Bus Overview - The Inter-Integrated Circuit Communication ProtocolMohamed Ali100% (3)

- I2C TutorialDocument4 pagesI2C TutorialDeepak Reddy100% (2)

- IEEE 754 ConverterDocument2 pagesIEEE 754 ConverterAnggara KusumaNo ratings yet

- Getting Started Free CadDocument13 pagesGetting Started Free CadproftononNo ratings yet

- PIC Assembly Language For The Complete BeginnerDocument35 pagesPIC Assembly Language For The Complete BeginnerVlad Ioan Cirlogea100% (2)

- I2c Serial ProtocolDocument9 pagesI2c Serial ProtocolShardul Deolankar100% (2)

- The Best of Bob PeaseDocument338 pagesThe Best of Bob PeaseCARROUCHO62No ratings yet

- I C-Master Core Specification: Author: Richard HerveilleDocument18 pagesI C-Master Core Specification: Author: Richard Herveillegeorge guoNo ratings yet

- The I2C Bus SpecificationsDocument46 pagesThe I2C Bus Specificationsshrivastav.ajay100% (14)

- Discrete Numerical Methods in Physics and EngineeringFrom EverandDiscrete Numerical Methods in Physics and EngineeringRating: 4 out of 5 stars4/5 (2)

- Floating Point Arithmetic Unit Using VerilogDocument6 pagesFloating Point Arithmetic Unit Using Verilognamdt10% (1)

- Importance of Similarity Measures in Effective Web Information RetrievalDocument5 pagesImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCNo ratings yet

- A Review of Wearable Antenna For Body Area Network ApplicationDocument4 pagesA Review of Wearable Antenna For Body Area Network ApplicationEditor IJRITCCNo ratings yet

- Channel Estimation Techniques Over MIMO-OFDM SystemDocument4 pagesChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCNo ratings yet

- Regression Based Comparative Study For Continuous BP Measurement Using Pulse Transit TimeDocument7 pagesRegression Based Comparative Study For Continuous BP Measurement Using Pulse Transit TimeEditor IJRITCCNo ratings yet

- A Review of 2D &3D Image Steganography TechniquesDocument5 pagesA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCNo ratings yet

- Channel Estimation Techniques Over MIMO-OFDM SystemDocument4 pagesChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCNo ratings yet

- Comparative Analysis of Hybrid Algorithms in Information HidingDocument5 pagesComparative Analysis of Hybrid Algorithms in Information HidingEditor IJRITCCNo ratings yet

- IJRITCC Call For Papers (October 2016 Issue) Citation in Google Scholar Impact Factor 5.837 DOI (CrossRef USA) For Each Paper, IC Value 5.075Document3 pagesIJRITCC Call For Papers (October 2016 Issue) Citation in Google Scholar Impact Factor 5.837 DOI (CrossRef USA) For Each Paper, IC Value 5.075Editor IJRITCCNo ratings yet

- Performance Analysis of Image Restoration Techniques at Different NoisesDocument4 pagesPerformance Analysis of Image Restoration Techniques at Different NoisesEditor IJRITCCNo ratings yet

- A Study of Focused Web Crawling TechniquesDocument4 pagesA Study of Focused Web Crawling TechniquesEditor IJRITCCNo ratings yet

- A Review of 2D &3D Image Steganography TechniquesDocument5 pagesA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCNo ratings yet

- A Review of Wearable Antenna For Body Area Network ApplicationDocument4 pagesA Review of Wearable Antenna For Body Area Network ApplicationEditor IJRITCCNo ratings yet

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmDocument5 pagesDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCNo ratings yet

- Modeling Heterogeneous Vehicle Routing Problem With Strict Time ScheduleDocument4 pagesModeling Heterogeneous Vehicle Routing Problem With Strict Time ScheduleEditor IJRITCCNo ratings yet

- Network Approach Based Hindi Numeral RecognitionDocument4 pagesNetwork Approach Based Hindi Numeral RecognitionEditor IJRITCCNo ratings yet

- Fuzzy Logic A Soft Computing Approach For E-Learning: A Qualitative ReviewDocument4 pagesFuzzy Logic A Soft Computing Approach For E-Learning: A Qualitative ReviewEditor IJRITCCNo ratings yet

- Efficient Techniques For Image CompressionDocument4 pagesEfficient Techniques For Image CompressionEditor IJRITCCNo ratings yet

- 41 1530347319 - 30-06-2018 PDFDocument9 pages41 1530347319 - 30-06-2018 PDFrahul sharmaNo ratings yet

- Prediction of Crop Yield Using LS-SVMDocument3 pagesPrediction of Crop Yield Using LS-SVMEditor IJRITCCNo ratings yet

- Itimer: Count On Your TimeDocument4 pagesItimer: Count On Your Timerahul sharmaNo ratings yet

- 45 1530697786 - 04-07-2018 PDFDocument5 pages45 1530697786 - 04-07-2018 PDFrahul sharmaNo ratings yet

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianDocument3 pagesPredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaNo ratings yet

- 44 1530697679 - 04-07-2018 PDFDocument3 pages44 1530697679 - 04-07-2018 PDFrahul sharmaNo ratings yet

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionDocument5 pagesHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaNo ratings yet

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsDocument3 pagesSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaNo ratings yet

- A Clustering and Associativity Analysis Based Probabilistic Method For Web Page PredictionDocument5 pagesA Clustering and Associativity Analysis Based Probabilistic Method For Web Page Predictionrahul sharmaNo ratings yet

- Vehicular Ad-Hoc Network, Its Security and Issues: A ReviewDocument4 pagesVehicular Ad-Hoc Network, Its Security and Issues: A Reviewrahul sharmaNo ratings yet

- Image Restoration Techniques Using Fusion To Remove Motion BlurDocument5 pagesImage Restoration Techniques Using Fusion To Remove Motion Blurrahul sharmaNo ratings yet

- A Content Based Region Separation and Analysis Approach For Sar Image ClassificationDocument7 pagesA Content Based Region Separation and Analysis Approach For Sar Image Classificationrahul sharmaNo ratings yet

- Space Complexity Analysis of Rsa and Ecc Based Security Algorithms in Cloud DataDocument12 pagesSpace Complexity Analysis of Rsa and Ecc Based Security Algorithms in Cloud Datarahul sharmaNo ratings yet

- Internet of Things Applications: Opportunities and ThreatsDocument26 pagesInternet of Things Applications: Opportunities and ThreatsMEnrique ForocaNo ratings yet

- Connecting Excel To ControlLogix - PLCdevDocument9 pagesConnecting Excel To ControlLogix - PLCdevAhmed OUADAHINo ratings yet

- Lab ManualDocument24 pagesLab ManualA.Ruba COMPUTER SCIENCE AND ENGINEERINGNo ratings yet

- Testing ProcessDocument6 pagesTesting ProcessKabilan Ponmudi100% (1)

- Class 12 Computer Notes by Binod RijalDocument31 pagesClass 12 Computer Notes by Binod Rijalसन्दिप तिम्ल्सिना100% (1)

- Math 3 - Factors and MultiplesDocument23 pagesMath 3 - Factors and MultiplesTrixy RodriguezNo ratings yet

- ABB - Controller Comander 200 Operating GuideDocument28 pagesABB - Controller Comander 200 Operating GuideAdrianus AjaNo ratings yet

- Real Numbers: Project Work-Submitted To - Mr. Amit Pandey Submitted by - Srishti Dubey Class - 10 BDocument10 pagesReal Numbers: Project Work-Submitted To - Mr. Amit Pandey Submitted by - Srishti Dubey Class - 10 BSrishti Dubey100% (2)

- Data AnalysisDocument32 pagesData AnalysisDiksha chaudharyNo ratings yet

- Pres5 - Single Instance ArchitectureDocument13 pagesPres5 - Single Instance ArchitectureAbdul WaheedNo ratings yet

- Help Ge Lunar ProdigyDocument96 pagesHelp Ge Lunar ProdigyMohammad El ArabNo ratings yet

- Error Message Reference: Oracle® Hyperion Tax GovernanceDocument6 pagesError Message Reference: Oracle® Hyperion Tax GovernanceAbayneh AssefaNo ratings yet

- Loan Management System For HESFB (Uganda)Document42 pagesLoan Management System For HESFB (Uganda)Peter LubegaNo ratings yet

- MIS in NASSIT Sierra Leone.Document20 pagesMIS in NASSIT Sierra Leone.Alie BanguraNo ratings yet

- V1600D-MINI Series Software Release Notes SummaryDocument7 pagesV1600D-MINI Series Software Release Notes SummaryrchiriviNo ratings yet

- Fanuc Alarm 12 Troubleshooting GuideDocument20 pagesFanuc Alarm 12 Troubleshooting GuidePhong HuynhNo ratings yet

- 5c713810f3f1f-Canon Ir400i PLDocument4 pages5c713810f3f1f-Canon Ir400i PLvon arvin gregorioNo ratings yet

- Sales Letter - To Promote A Product or ServiceDocument2 pagesSales Letter - To Promote A Product or Serviceapi-3797608100% (2)

- SRSDOC1Document17 pagesSRSDOC1Bts ArmyNo ratings yet

- Xerox Workcentre 7425 / 7428 / 7435 Multifunction Device: Colorful InnovationDocument8 pagesXerox Workcentre 7425 / 7428 / 7435 Multifunction Device: Colorful InnovationChenna VijayNo ratings yet

- SC600Y - Hardware Design DataSheetDocument131 pagesSC600Y - Hardware Design DataSheetEduardo Solana LopezNo ratings yet

- Available BusyBox CommandsDocument45 pagesAvailable BusyBox CommandsSlyfester KurniawanNo ratings yet

- QB CP06 EngDocument19 pagesQB CP06 EngPoon Yin KwongNo ratings yet

- SEO Score: 17 FailedDocument12 pagesSEO Score: 17 FailedlinkedNo ratings yet

- Eg8141a5 Datasheet PDFDocument4 pagesEg8141a5 Datasheet PDFcraytusNo ratings yet

- Quảng Nam THPT Chuyên English ExamDocument12 pagesQuảng Nam THPT Chuyên English ExamTún PhạmNo ratings yet

- SAP Ariba IntroductionDocument3 pagesSAP Ariba Introductiondivya zawarNo ratings yet

- IITM AppDev QUIZ 3Document127 pagesIITM AppDev QUIZ 3ShreyaNo ratings yet