Professional Documents

Culture Documents

Cours Ato Lpgi - 2

Uploaded by

Cricri AduOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cours Ato Lpgi - 2

Uploaded by

Cricri AduCopyright:

Available Formats

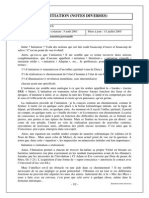

Architecture des ordinateurs

Anne acadmique 2012-2013

Sommaire

INTRODUCTION.................................................................................................................................. 3

CHAPITRE 1 : GENERALITES ............................................................................................................ 4

1.1 Introduction ....................................................................................................................................... 4

1.2 Quentend-t-on par architecture ?............................................................................................................ 4

1.3 Quest ce quun microprocesseur ? ........................................................................................................... 4

1.4 Rappels............................................................................................................................................. 5

1.5 O trouve-t-on des systmes microprocesseur ? ......................................................................................... 5

CHAPITRE 2 : ARCHITECTURE DE BASE ........................................................................................ 7

2.1 Modle de Von Neumann .................................................................................................................... 7

2.2 Lunit centrale................................................................................................................................... 7

2.3 La mmoire principale.......................................................................................................................... 7

2.4 Les interfaces dentres/sorties ............................................................................................................... 8

2.5 Les bus ............................................................................................................................................. 8

2.6 Dcodage dadresses ............................................................................................................................. 8

CHAPITRE 3 : LES MEMOIRES ......................................................................................................... 10

3.1 Organisation dune mmoire ................................................................................................................ 10

3.2 Caractristiques dune mmoire ............................................................................................................ 11

3.3 Diffrents types de mmoire ................................................................................................................. 12

3.3.1 Les mmoires vives (RAM) .................................................................................................... 12

3.3.2 Les mmoires mortes (ROM)........................................................................................................ 15

3.4 Critres de choix dune mmoire ........................................................................................................... 18

3.5 Notion de hirarchie mmoire............................................................................................................... 19

CHAPITRE 4 : LE MICROPROCESSEUR .......................................................................................... 21

4.1 Architecture de base dun microprocesseur............................................................................................... 21

4.1.1 Lunit de commande............................................................................................................. 22

4.1.2 Lunit de traitement .............................................................................................................. 22

4.1.3 Schma fonctionnel................................................................................................................ 23

4.3 Jeu dinstructions............................................................................................................................... 25

4.3.1 Dfinition............................................................................................................................... 25

4.3.2 Type dinstructions................................................................................................................. 25

4.3.3 Codage ................................................................................................................................... 25

4.3.4 Mode dadressage ................................................................................................................... 25

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 1

Architecture des ordinateurs

Anne acadmique 2012-2013

4.3.5 Temps dexcution ................................................................................................................. 26

4.4 Langage de programmation ................................................................................................................. 26

4.5 Performances dun microprocesseur ........................................................................................................ 26

4.6 Notion darchitecture RISC et CISC.................................................................................................... 27

4.6.1 Larchitecture CISC................................................................................................................ 27

4.6.2 Larchitecture RISC ................................................................................................................ 27

4.6.3 Comparaison.......................................................................................................................... 28

4.7 Amliorations de larchitecture de base................................................................................................... 28

4.7.1 Architecture pipeline .............................................................................................................. 28

4.7.2 Notion de cache mmoire ...................................................................................................... 30

4.7.3 Architecture superscalaire....................................................................................................... 31

4.7.4 Architecture pipeline et superscalaire...................................................................................... 32

4.8 Processeurs spciaux .......................................................................................................................... 32

4.8.1 Le microcontrleur................................................................................................................. 32

4.8.2 Le processeur de signal........................................................................................................... 32

CHAPITRE 5 : LES ECHANGES DE DONNEES ............................................................................. 34

5.1 Linterface dentre/sortie ................................................................................................................... 34

5.1.1 Rle ....................................................................................................................................... 34

5.1.2 Constitution ........................................................................................................................... 34

5.2 Techniques dchange de donnes........................................................................................................... 35

5.2.1 Echange programm .............................................................................................................. 35

5.2.2 Echange direct avec la mmoire ............................................................................................. 36

5.3 Types de liaisons ............................................................................................................................... 36

5.3.1 Liaison parallle...................................................................................................................... 37

5.3.2 Liaison srie ........................................................................................................................... 37

CHAPITRE 6 UN EXEMPLE - LE PC ................................................................................................ 39

6.1 Lunit centrale................................................................................................................................. 39

6.1.1 La carte mre.......................................................................................................................... 39

6.1.2 Le microprocesseur ................................................................................................................ 43

6.1.3 La mmoire ............................................................................................................................ 43

6.1.4 La carte vido......................................................................................................................... 43

6.1.5 Les priphriques internes de stockage ....................................................................................... 45

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 2

Architecture des ordinateurs

Anne acadmique 2012-2013

INTRODUCTION

Larchitecture des ordinateurs constitue un vaste sujet en constante volution. En

20 ans, la vitesse dun processeur standard a t multiplie par un facteur 1 000 et le cot

par unit de performance a plong dun facteur 100 000. Pour ces raisons, tout livre bas

sur une architecture particulire risque dtre obsolte six mois aprs sa sortie.

Ce document nest pas destin aux concepteurs de processeurs de demain, mais

aux informaticiens actuels et futurs. Ce nest pas le rle dun informaticien de concevoir

des architectures. Les dtails dune architecture particulire, ou mme de larchitecture en

gnral, ne sont pas forcment utiles. Linformaticien a plutt besoin dun modle de

fonctionnement de lordinateur qui lui donne une bonne ide de la performance de son

programme et de limpact de modifications donnes du programme sur sa performance.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 3

Architecture des ordinateurs

Anne acadmique 2012-2013

CHAPITRE 1 : GENERALITES

1.1 Introduction

L'informatique, contraction des mots information et automatique, est la science du

traitement de l'information. Apparue au milieu du 20me sicle, elle a connu une

volution extrmement rapide. A sa motivation initiale qui tait de faciliter et d'acclrer le

calcul, se sont ajoutes de nombreuses fonctionnalits, comme l'automatisation, le

contrle et la commande de processus, la communication ou le partage de l'information.

Le cours darchitecture des systmes microprocesseurs expose les principes de base du

traitement programm de linformation. La mise en uvre de ces systmes sappuie sur

deux modes de ralisation distincts, le matriel et le logiciel. Le matriel (hardware)

correspond laspect concret du systme : unit centrale, mmoire, organes dentressorties, etc Le logiciel (software) correspond un ensemble dinstructions, appel

programme, qui sont contenues dans les diffrentes mmoires du systme et qui

dfinissent les actions effectues par le matriel.

1.2 Quentend-t-on par architecture ?

L'architecture d'un systme microprocesseur reprsente lorganisation de ses

diffrentes units et de leurs interconnexions. Le choix d'une architecture est toujours le

rsultat d'un compromis :

- entre performances et cots

- entre efficacit et facilit de construction

- entre performances d'ensemble et facilit de programmation

- etc

1.3 Quest ce quun microprocesseur ?

Un microprocesseur est un circuit intgr complexe. Il rsulte de lintgration sur

une puce de fonctions logiques combinatoires (logiques et/ou arithmtique) et

squentielles (registres, compteur, etc). Il est capable d'interprter et d'excuter les

instructions d'un programme. Son domaine dutilisation est donc presque illimit.

Le concept de microprocesseur a t cr par la Socit Intel. Cette Socit, cre

en 1968, tait spcialise dans la conception et la fabrication de puces mmoire. la

demande de deux de ses clients fabricants de calculatrices et de terminaux Intel

tudia une unit de calcul implmente sur une seule puce. Ceci donna naissance, en 1971,

au premier microprocesseur, le 4004, qui tait une unit de calcul 4 bits fonctionnant

108 kHz. Il rsultait de lintgration denviron 2300 transistors.

Remarque :

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 4

Architecture des ordinateurs

Anne acadmique 2012-2013

La ralisation de circuits intgrs de plus en plus complexe a t rendue possible

par lapparition du transistor en 1947. Il a fallu attendre 1958 pour voir apparatre le 1ier

circuit intgr ralis par Texas Instrument.

1.4 Rappels

Les informations traites par un microprocesseur sont de diffrents types

(nombres, instructions, images, vido, etc) mais elles sont toujours reprsentes sous

un format binaire. Seul le codage changera suivant les diffrents types de donnes

traiter. Elles sont reprsentes physiquement par 2 niveaux de tensions diffrents.

En binaire, une information lmentaire est appel bit et ne peut prendre que deux

valeurs diffrentes : 0 ou 1.

Une information plus complexe sera code sur plusieurs bits. On appelle cet

ensemble un mot.

Un mot de 8 bits est appel un octet.

Reprsentation dun nombre entier en binaire :

Les nombres sont exprims par des chiffres pouvant prendre deux valeurs 0 ou 1.

A chaque chiffre est affect un poids exprim en puissance de 2.

Ex : ( 101 )2 <> 1x 2 + 0x21 + 1x20 = ( 5 )10

Reprsentation dun nombre entier en hexadcimal :

Lorsquune donne est reprsente sur plus de 4 bits, on prfre souvent

lexprimer en hexadcimal. Les nombres sont exprims par des chiffres et des lettres

pouvant prendre 16 valeurs :

0123456789ABCDEF

A chaque chiffre est affect un poids exprim en puissance de 16.

Ex : ( 9A )16 <> 9x161+ Ax160 = 9x161 + 10x160 = (154)10

Attention !! :

1 kilobit = 210 bit = 1024 bit

1 mgabit = 210 kbit = 1024 kbit

1 gigabit = 210 Mbit = 1024 Mbit

1.5 O trouve-t-on des systmes microprocesseur ?

Les applications des systmes microprocesseurs sont multiples et varies :

- Ordinateur, PDA

- console de jeux

- calculatrice

- tlvision

- tlphone portable

- distributeur automatique dargent

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 5

Architecture des ordinateurs

Anne acadmique 2012-2013

- robotique

- lecteur carte puce, code barre

- automobile

- instrumentation

- etc.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 6

Architecture des ordinateurs

Anne acadmique 2012-2013

CHAPITRE 2 : STRUCTURE ET FONCTIONNEMENT DE

BASE DUN ORDINATEUR

2.1 LE Modle de Von Neumann

Pour traiter une information, un microprocesseur seul ne suffit pas, il faut linsrer

au sein dun systme minimum de traitement programm de linformation. John Von

Neumann est l'origine d'un modle de machine universelle de traitement programm de

linformation (1946). Cette architecture sert de base la plupart des systmes

microprocesseur actuel. Elle est compose des lments suivants :

une unit centrale

une mmoire principale

des interfaces dentres/sorties

Les diffrents organes du systme sont relis par des voies de communication appeles

bus.

2.2 Lunit centrale

Elle est compose par le microprocesseur qui est charg dinterprter et dexcuter

les instructions dun programme, de lire ou de sauvegarder les rsultats dans la mmoire et

de communiquer avec les units dchange. Toutes les activits du microprocesseur sont

cadences par une horloge.

On caractrise le microprocesseur par :

sa frquence dhorloge : en MHz ou GHz

le nombre dinstructions par secondes quil est capable dexcuter : en MIPS

la taille des donnes quil est capable de traiter : en bits

2.3 La mmoire principale

Elle contient les instructions du ou des programmes en cours dexcution et les

donnes associes ce programme. Physiquement, elle se dcompose souvent en :

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 7

Architecture des ordinateurs

Anne acadmique 2012-2013

une mmoire morte (ROM = Read Only Memory ) charge de stocker le programme.

Cest une mmoire lecture seule.

une mmoire vive (RAM = Random Access Memory) charge de stocker les donnes

intermdiaires ou les rsultats de calculs. On peut y lire ou crire des donnes, ces

donnes sont perdues la mise hors tension.

Remarque :

Les disques durs, disquettes, CDROM, etc sont des priphriques de stockage et sont

considrs comme des mmoires secondaires.

2.4 Les interfaces dentres/sorties

Elles permettent dassurer la communication entre le microprocesseur et les

priphriques. (Capteur, clavier, moniteur ou afficheur, imprimante, modem, etc).

2.5 Les bus

Un bus est un ensemble de fils qui assure la transmission du mme type

dinformation. On retrouve trois types de bus vhiculant des informations en parallle

dans un systme de traitement programm de linformation :

un bus de donnes : bidirectionnel qui assure le transfert des informations entre le

microprocesseur et son environnement, et inversement. Son nombre de lignes est

gal la capacit de traitement du microprocesseur.

un bus d'adresses: unidirectionnel qui permet la slection des informations traiter

dans un espace mmoire (ou espace adressable) qui peut avoir 2n emplacements,

avec n = nombre de conducteurs du bus d'adresses.

un bus de commande: constitu par quelques conducteurs qui assurent la

synchronisation des flux d'informations sur les bus des donnes et des adresses.

2.6 Dcodage dadresses

La multiplication des priphriques autour du microprocesseur oblige la prsence

dun dcodeur dadresse charg daiguiller les donnes prsentes sur le bus de donnes.

En effet, le microprocesseur peut communiquer avec les diffrentes mmoires et

les diffrents botiers dinterface. Ceux-ci sont tous relis sur le mme bus de donnes et

afin dviter des conflits, un seul composant doit tre slectionn la fois.

Lorsquon ralise un systme microprogramm, on attribue donc chaque

priphrique une zone dadresse et une fonction dcodage dadresse est donc

ncessaire afin de fournir les signaux de slection de chacun des composants.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 8

Architecture des ordinateurs

Anne acadmique 2012-2013

Remarque : lorsquun composant nest pas slectionn, ses sorties sont mises

ltat haute impdance afin de ne pas perturber les donnes circulant sur le bus (elle

prsente une impdance de sortie trs leve = circuit ouvert).

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 9

Architecture des ordinateurs

Anne acadmique 2012-2013

CHAPITRE 3 : ORGANISATION ET GESTION DE LA

MEMOIRES

Une mmoire est un circuit semi-conducteur permettant denregistrer, de

conserver et de restituer des informations (instructions et variables). Cest cette capacit

de mmorisation qui explique la polyvalence des systmes numriques et leur adaptabilit

de nombreuses situations. Les informations peuvent tre crites ou lues. Il y a criture

lorsqu'on enregistre des informations en mmoire, lecture lorsqu'on rcupre des

informations prcdemment enregistres.

3.1 Organisation dune mmoire

Une mmoire peut tre reprsente comme une armoire de rangement constitue

de diffrents tiroirs. Chaque tiroir reprsente alors une case mmoire qui peut contenir un

seul lment : des donnes. Le nombre de cases mmoires pouvant tre trs lev, il est

alors ncessaire de pouvoir les identifier par un numro. Ce numro est appel adresse.

Chaque donne devient alors accessible grce son adresse.

Avec une adresse de n bits il est possible de rfrencer au plus 2n cases mmoire.

Chaque case est remplie par un mot de donnes (sa longueur m est toujours une puissance

de 2). Le nombre de fils dadresses dun botier mmoire dfinit donc le nombre de cases

mmoire que comprend le botier. Le nombre de fils de donnes dfinit la taille des

donnes que lon peut sauvegarder dans chaque case mmoire.

En plus du bus dadresses et du bus de donnes, un botier mmoire comprend une

entre de commande qui permet de dfinir le type daction que lon effectue avec la

mmoire (lecture/criture) et une entre de slection qui permet de mettre les

entres/sorties du botier en haute impdance.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 10

Architecture des ordinateurs

Anne acadmique 2012-2013

On peut donc schmatiser un circuit mmoire par la figure suivante o lon peut

distinguer :

les entres dadresses

les entres de donnes

les sorties de donnes

les entres de commandes :

- une entre de slection de lecture ou dcriture. (R/W)

- une entre de slection du circuit. (CS)

Une opration de lecture ou dcriture de la mmoire suit toujours le mme cycle :

1. slection de ladresse

2. choix de lopration effectuer (R/W)

3. slection de la mmoire (CS = 0)

4. lecture ou criture la donne

Remarque :

Les entres et sorties de donnes sont trs souvent regroupes sur des bornes

bidirectionnelles.

3.2 Caractristiques dune mmoire

La capacit : cest le nombre total de bits que contient la mmoire. Elle sexprime

aussi souvent en octet.

Le format des donnes : cest le nombre de bits que lon peut mmoriser par

case mmoire. On dit aussi que cest la largeur du mot mmorisable.

Le temps daccs : cest le temps qui s'coule entre l'instant o a t lance une

opration de lecture/criture en mmoire et l'instant o la premire information

est disponible sur le bus de donnes.

Le temps de cycle : il reprsente l'intervalle minimum qui doit sparer deux

demandes successives de lecture ou d'criture.

Le dbit : cest le nombre maximum d'informations lues ou crites par seconde.

Volatilit : elle caractrise la permanence des informations dans la mmoire.

L'information stocke est volatile si elle risque d'tre altre par un dfaut

d'alimentation lectrique et non volatile dans le cas contraire.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 11

Architecture des ordinateurs

Anne acadmique 2012-2013

Exemple : Chronogramme dun cycle de lecture

Remarque :

Les mmoires utilises pour raliser la mmoire principale dun systme

microprocesseur sont des mmoires semi-conducteur. On a vu que dans ce type de

mmoire, on accde directement n'importe quelle information dont on connat l'adresse

et que le temps mis pour obtenir cette information ne dpend pas de l'adresse. On dira

que l'accs une telle mmoire est alatoire ou direct.

A l'inverse, pour accder une information sur bande magntique, il faut drouler la

bande en reprant tous les enregistrements jusqu' ce que l'on trouve celui que l'on dsire.

On dit alors que l'accs l'information est squentiel. Le temps d'accs est variable selon

la position de l'information recherche. L'accs peut encore tre semi-squentiel :

combinaison des accs direct et squentiel.

Pour un disque magntique par exemple l'accs la piste est direct, puis l'accs au secteur

est squentiel.

3.3 Diffrents types de mmoire

3.3.1 Les mmoires vives (RAM)

Une mmoire vive sert au stockage temporaire de donnes. Elle doit avoir un

temps de cycle trs court pour ne pas ralentir le microprocesseur. Les mmoires vives

sont en gnral volatiles : elles perdent leurs informations en cas de coupure

d'alimentation. Certaines d'entre elles, ayant une faible consommation, peuvent tre

rendues non volatiles par l'adjonction d'une batterie. Il existe deux grandes familles de

mmoires RAM (Random Acces Memory : mmoire accs alatoire) :

Les RAM statiques

Les RAM dynamiques

3.3.1.1 Les RAM statiques

Le bit mmoire d'une RAM statique (SRAM) est compos d'une bascule. Chaque bascule

contient entre 4 et 6 transistors.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 12

Architecture des ordinateurs

Anne acadmique 2012-2013

3.3.1.2 Les RAM dynamiques

Dans les RAM dynamiques (DRAM), l'information est mmorise sous la forme d'une

charge lectrique stocke dans un condensateur (capacit grille substrat d'un transistor

MOS).

Avantages :

Cette technique permet une plus grande densit d'intgration, car un point

mmoire ncessite environ quatre fois moins de transistors que dans une mmoire

statique. Sa consommation sen retrouve donc aussi trs rduite.

Inconvnients :

La prsence de courants de fuite dans le condensateur contribue sa dcharge.

Ainsi, linformation est perdue si on ne la rgnre pas priodiquement (charge du

condensateur). Les RAM dynamiques doivent donc tre rafrachies rgulirement pour

entretenir la mmorisation : il s'agit de lire l'information et de la recharger. Ce

rafrachissement indispensable a plusieurs consquences :

il complique la gestion des mmoires dynamiques car il faut tenir compte des

actions de rafrachissement qui sont prioritaires.

la dure de ces actions augmente le temps d'accs aux informations.

Dautre part, la lecture de linformation est destructive. En effet, elle se fait

par dcharge de la capacit du point mmoire lorsque celle-ci est charge. Donc

toute lecture doit tre suivie dune rcriture.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 13

Architecture des ordinateurs

Anne acadmique 2012-2013

3.3.1.3 Conclusions

En gnral les mmoires dynamiques, qui offrent une plus grande densit

d'information et un cot par bit plus faible, sont utilises pour la mmoire centrale, alors

que les mmoires statiques, plus rapides, sont utilises lorsque le facteur vitesse est

critique, notamment pour des mmoires de petite taille comme les caches et les registres.

Remarques :

Voici un historique de quelques DRAM qui ont ou sont utilises dans les PC :

La DRAM FPM (Fast Page Mode, 1987) : Elle permet d'accder plus rapidement

des donnes en introduisant la notion de page mmoire. (33 50 Mhz)

La DRAM EDO (Extended Data Out, 1995) : Les composants de cette mmoire

permettent de conserver plus longtemps l'information, on peut donc ainsi espacer

les cycles de rafrachissement. Elle apporte aussi la possibilit danticiper sur le

prochain cycle mmoire. (33 50 Mhz)

La DRAM BEDO (Bursted EDO) : On n'adresse plus chaque unit de mmoire

individuellement lorsqu'il faut y lire ou y crire des donnes. On se contente de

transmettre l'adresse de dpart du processus de lecture/criture et la longueur du

bloc de donnes ( Burst). Ce procd permet de gagner beaucoup de temps,

notamment avec les grands paquets de donnes tels qu'on en manipule avec les

applications modernes (66 Mhz).

La Synchronous DRAM (SDRAM, 1997) : La mmoire SDRAM a pour

particularit de se synchroniser sur une horloge. Les mmoires FPM, EDO taient

des mmoires asynchrones et elles induisaient des temps d'attentes lors de la

synchronisation. Elle se compose en interne de deux bancs de mmoire et des

donnes peuvent tre lues alternativement sur l'un puis sur l'autre de ces bancs

grce un procd d'entrelacement spcial. Le protocole d'attente devient donc

tout fait inutile. Cela lui permet de supporter des frquences plus leves

quavant (100 Mhz).

La DDR-I ou DDR-SDRAM (Double Data Rate Synchronous DRAM, 2000) :

La DDR-SDRAM permet de recevoir ou d'envoyer des donnes lors du front

montant et du front descendant de

lhorloge. (133 200 MHz)

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 14

Architecture des ordinateurs

Anne acadmique 2012-2013

3.3.2 Les mmoires mortes (ROM)

Pour certaines applications, il est ncessaire de pouvoir conserver des informations

de faon permanente mme lorsque l'alimentation lectrique est interrompue. On utilise

alors des mmoires mortes ou mmoires lecture seule (ROM : Read Only Memory). Ces

mmoires sont non volatiles.

Ces mmoires, contrairement aux RAM, ne peuvent tre que lue. Linscription en

mmoire des donnes reste possible mais est appele programmation. Suivant le type de

ROM, la mthode de programmation changera. Il existe donc plusieurs types de ROM :

ROM

PROM

EPROM

EEPROM

FLASH EPROM.

3.3.2.1 LA ROM

Elle est programme par le fabricant et son contenu ne peut plus tre ni modifi., ni

effac par l'utilisateur.

Structure :

Cette mmoire est compose d'une matrice dont la programmation seffectue en

reliant les lignes aux colonnes par des diodes. L'adresse permet de slectionner une ligne

de la matrice et les donnes sont alors reues sur les colonnes (le nombre de colonnes

fixant la taille des mots mmoire).

Programmation :

L'utilisateur doit fournir au

constructeur un masque indiquant les

emplacements des diodes dans

matrice.

Avantages :

Densit leve

Non volatile

Mmoire rapide

Inconvnients :

criture impossible

Modification

impossible

(toute

erreur est fatale).

Dlai de fabrication

( 3 6 semaines)

Obligation de grandes

quantits en raison du

cot lev qu'entrane la production du masque et le processus de

fabrication.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 15

Architecture des ordinateurs

Anne acadmique 2012-2013

3.3.2.2 La PROM

Cest une ROM qui peut tre programme une seule fois par l'utilisateur

(Programmable ROM). La programmation est ralise partir dun programmateur

spcifique.

Structure :

Les liaisons diodes de la ROM sont remplaces par des fusibles pouvant tre

dtruits ou des jonctions pouvant tre court-circuites.

Programmation :

Les PROM fusible sont livres avec toutes les lignes connectes aux colonnes (0 en

chaque point mmoire). Le processus de programmation consiste donc programmer les

emplacements des 1 en gnrant des impulsions de courants par lintermdiaire du

programmateur ; les fusibles situs aux points mmoires slectionns se retrouvant donc

dtruits.

Le principe est identique dans les PROM jonctions sauf que les lignes et les colonnes

sont dconnectes (1 en chaque point mmoire). Le processus de programmation consiste

donc programmer les emplacements des 0 en gnrant des impulsions de courants par

lintermdiaire du programmateur ; les jonctions situes aux points mmoires slectionns

se retrouvant court-circuites par effet davalanche.

Avantages :

Idem ROM

Claquage en quelques minutes

Cot relativement faible

Inconvnients :

Modification impossible (toute erreur est fatale).

3.3.2.3 LEPROM ou UV-EPROM

Pour faciliter la mise au point d'un programme ou tout simplement permettre une

erreur de programmation, il est intressant de pouvoir reprogrammer une PROM. La

technique de claquage utilise dans celles-ci ne le permet videmment pas. L'EPROM

(Erasable Programmable ROM) est une PROM qui peut tre efface.

Structure

Dans une EPROM, le point mmoire est ralis partir dun transistor FAMOS

(Floating gate Avalanche injection Metal Oxyde Silicium). Ce transistor MOS a t

introduit par Intel en 1971 et a la particularit de possder une grille flottante.

Programmation

La programmation consiste piger des charges dans la grille flottante. Pour cela, il

faut tout dabord appliquer une trs forte tension entre Grille et Source. Si lon applique

ensuite une tension entre D et S, la canal devient conducteur. Mais comme la tension

Grille-Source est trs importante, les lectrons sont dvis du canal vers la grille flottante

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 16

Architecture des ordinateurs

Anne acadmique 2012-2013

et capturs par celle-ci. Cette charge se maintient une dizaine d'annes en condition

normale.

Lexposition dune vingtaine de minutes un rayonnement ultraviolet permet

dannuler la charge stocke dans la grille flottante. Cet effacement est reproductible plus

dun millier de fois. Les botiers des EPROM se caractrisent donc par la prsence dune

petite fentre transparente en quartz qui assure le passage des UV. Afin dviter toute

perte accidentelle de linformation, il faut obturer la fentre deffacement lors de

lutilisation.

Avantages :

Reprogrammable et non Volatile

Inconvnients :

Impossible de slectionner une seule cellule effacer

Impossible deffacer la mmoire in-situ.

lcriture est beaucoup plus lente que sur une RAM. (environ 1000x)

3.3.2.4 LEEPROM

LEEPROM (Electically EPROM) est une mmoire programmable et effaable

lectriquement.

Elle rpond ainsi linconvnient principal de lEPROM.

Structure

Dans une EEPROM, le point mmoire est ralis partir dun transistor SAMOS

reprenant le mme principe que le FAMOS sauf que lpaisseur entre les deux grilles est

beaucoup plus faible.

Programmation

Une forte tension lectrique applique entre grille et source conduit la

programmation de la mmoire. Une forte tension inverse provoquera la libration des

lectrons et donc leffacement de la mmoire.

Avantages :

Comportement d'une RAM non Volatile.

Programmation et effacement mot par mot possible.

Inconvnients :

Trs lente pour une utilisation en RAM.

Cot de ralisation.

3.3.2.5 La FLASH EPROM

La mmoire Flash s'apparente la technologie de lEEPROM. Elle est

programmable et effaable lectriquement comme les EEPROM.

Structure

Il existe deux technologie diffrentes qui se diffrencient par lorganisation de leurs

rseaux mmoire : larchitecture NOR et NAND. Larchitecture NOR propose un

assemblage des cellules lmentaires de mmorisation en parallle avec les lignes de

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 17

Architecture des ordinateurs

Anne acadmique 2012-2013

slection comme dans une EEPROM classique. Larchitecture NAND propose un

assemblage en srie de ces mmes cellules avec les lignes de slection. Dun point de vue

pratique, la diffrence majeure entre NOR et NAND tient leurs interfaces. Alors quune

NOR dispose de bus dadresses et de donnes ddis, la NAND est dote dune interface

dE/S indirecte. . Par contre, la structure NAND autorise une implantation plus dense

grce une taille de cellule approximativement 40 % plus petite que la structure NOR.

Programmation

Si NOR et NAND exploitent toutes deux le mme principe de stockage de charges

dans la grille flottante dun transistor, lorganisation de leur rseau mmoire noffre pas la

mme souplesse dutilisation. Les Flash NOR autorise un adressage alatoire qui permet

de la programmer octet par octet alors que la Flash NAND autorise un accs squentiel

aux donnes et permettra seulement une programmation par secteur comme sur un

disque dur.

Avantages

Flash NOR :

Comportement d'une RAM non Volatile.

Programmation et effacement mot par mot possible.

Temps daccs faible.

Flash NAND :

Comportement d'une RAM non Volatile.

Forte densit dintgration cot rduit.

Rapidit de lcriture/lecture par paquet

Consommation rduite.

Inconvnients

Flash NOR :

Lenteur de lcriture/lecture par paquet.

cot.

Flash NAND :

Ecriture/lecture par octet impossible.

Interface E/S indirecte

La Flash EPROM a connu un essor trs important ces dernires annes avec le boom

de la tlphonie portable et des appareils multimdia (PDA, appareil photo numrique,

lecteur MP3, etc...).

3.4 Critres de choix dune mmoire

Les principaux critres retenir sont :

Capacit

Vitesse

Consommation

Cot

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 18

Architecture des ordinateurs

Anne acadmique 2012-2013

3.5 Notion de hirarchie mmoire

Une mmoire idale serait une mmoire de grande capacit, capable de stocker un

maximum dinformations et possdant un temps daccs trs faible afin de pouvoir

travailler rapidement sur ces informations. Mais il se trouve que les mmoires de grande

capacit sont souvent trs lente et que les mmoires rapides sont trs chres. Et pourtant,

la vitesse daccs la mmoire conditionne dans une large mesure les performances dun

systme. En effet, cest l que se trouve le goulot dtranglement entre un microprocesseur

capable de traiter des informations trs rapidement et une mmoire beaucoup plus lente

(ex : processeur actuel 3Ghz et mmoire 400MHz). Or, on na jamais besoin de toutes

les informations au mme moment. Afin dobtenir le meilleur compromis cotperformance, on dfinie donc une hirarchie mmoire. On utilise des mmoires de faible

capacit mais trs rapide pour stocker les informations dont le microprocesseur se sert le

plus et on utilise des mmoires de capacit importante mais beaucoup plus lente pour

stocker les informations dont le microprocesseur se sert le moins. Ainsi, plus on sloigne

du microprocesseur et plus la capacit et le temps daccs des mmoires vont augmenter.

Les registres sont les lments de mmoire les plus rapides. Ils sont situs au

niveau du processeur et servent au stockage des oprandes et des rsultats

intermdiaires.

La mmoire cache est une mmoire rapide de faible capacit destine acclrer

laccs la mmoire centrale en stockant les donnes les plus utilises.

La mmoire principale est lorgane principal de rangement des informations.

Elle contient les programmes (instructions et donnes) et est plus lente que les

deux mmoires prcdentes.

La mmoire dappui sert de mmoire intermdiaire entre la mmoire centrale et

les mmoires de masse. Elle joue le mme rle que la mmoire cache.

La mmoire de masse est une mmoire priphrique de grande capacit utilise

pour le stockage permanent ou la sauvegarde des informations. Elle utilise pour

cela des supports magntiques (disque dur, ZIP) ou optiques (CDROM,

DVDROM).

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 19

Architecture des ordinateurs

Anne acadmique 2012-2013

Exercices

Exercice1. Soit la table dtats de la figure suivante.

Dessiner le circuit dcrit par celle-ci.

Table dtats

Exercice 2. Soit le circuit squentiel de la figure suivante. Ce circuit est ralis avec trois

bistables D; il a une entre x et trois sorties y2, y1 et y0.

Circuit squentiel pour

lexercice

(1) Soient y2, y1 et y0 les valeurs des sorties au cours dun cycle.

Exprimer y2, y1 et y0, les valeurs des sorties au cycle suivant en fonction de x, y2, y1 et y0.

(2) Donner la table dtats correspondant ce circuit.

(3) Expliquer en une phrase ce que fait le circuit.

(4) Comment pourrait-on simplifier ce circuit ?

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 20

Architecture des ordinateurs

Anne acadmique 2012-2013

CHAPITRE 4 : SRTUCTURE ET FONCTIONNEMENT DU

MICROPROCESSEUR

Un microprocesseur est un circuit intgr complexe caractris par une trs grande

intgration et dot des facults d'interprtation et d'excution des instructions d'un

programme.

Il est charg dorganiser les tches prcises par le programme et dassurer leur excution.

Il doit aussi prendre en compte les informations extrieures au systme et assurer leur

traitement. Cest le cerveau du systme.

A lheure actuelle, un microprocesseur regroupe sur quelques millimtres carrs des

fonctionnalits toujours plus complexes. Leur puissance continue de saccrotre et leur

encombrement diminue rgulirement respectant toujours, pour le moment, la fameuse loi

de Moore (Moore (un des co-fondateurs de la socit Intel) a mis l'hypothse que les capacits technologiques

permettraient de multiplier par 2 tous les 18 mois le nombre de transistors intgrs sur les circuits.).

4.1 Architecture de base dun microprocesseur

Un microprocesseur est construit autour de deux lments principaux :

Une unit de commande

Une unit de traitement associ des registres charges de stocker les diffrentes

informations traiter. Ces trois lments sont relis entre eux par des bus interne

permettant les changes dinformations.

Remarques :

Il existe deux types de registres :

Les registres d'usage gnral permettent l'unit de traitement de manipuler des

donnes vitesse leve. Ils sont connects au bus donnes interne au

microprocesseur.

Les registres d'adresses (pointeurs) connects sur le bus adresses.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 21

Architecture des ordinateurs

Anne acadmique 2012-2013

4.1.1 Lunit de commande

Elle permet de squencer le droulement des instructions. Elle effectue la

recherche en mmoire de l'instruction. Comme chaque instruction est code sous forme

binaire, elle en assure le dcodage pour enfin raliser son excution puis effectue la

prparation de l'instruction suivante. Pour cela, elle est compose par :

le compteur de programme constitu par un registre dont le contenu est

initialis avec l'adresse de la premire instruction du programme. Il contient

toujours ladresse de linstruction excuter.

le registre d'instruction et le dcodeur d'instruction : chacune des instructions

excuter est range dans le registre instruction puis est dcode par le dcodeur

dinstruction.

Bloc logique de commande (ou squenceur) : Il organise l'excution des

instructions au rythme dune horloge. Il labore tous les signaux de

synchronisation internes ou externes (bus de commande) du microprocesseur en

fonction des divers signaux de commande provenant du dcodeur dinstruction ou

du registre dtat par exemple. Il s'agit d'un automate ralis soit de faon cble

(obsolte), soit de faon micro-programme, on parle alors de microprocesseur.

4.1.2 Lunit de traitement

Cest le coeur du microprocesseur. Elle regroupe les circuits qui assurent les

traitements ncessaires l'excution des instructions :

LUnit Arithmtique et Logique (UAL) est un circuit complexe qui assure les

fonctions logiques (ET, OU, Comparaison, Dcalage , etc) ou arithmtique

(Addition, soustraction).

Le registre d'tat est gnralement compos de 8 bits considrer

individuellement. Chacun de ces bits est un indicateur dont l'tat dpend du

rsultat de la dernire opration effectue par lUAL. On les appelle indicateur dtat

ou flag ou drapeaux. Dans un programme le rsultat du test de leur tat conditionne

souvent le droulement de la suite du programme. On peut citer par exemple les

indicateurs de :

retenue (carry : C)

retenue intermdiaire (Auxiliary-Carry : AC)

signe (Sign : S)

dbordement (overflow : OV ou V)

zro (Z)

parit (Parity : P)

Les accumulateurs sont des registres de travail qui servent stocker une

oprande au dbut d'une opration arithmtique et le rsultat la fin de

l'opration.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 22

Architecture des ordinateurs

Anne acadmique 2012-2013

4.1.3 Schma fonctionnel

4.2 Cycle dexcution dune instruction

Le microprocesseur ne comprend quun certain nombre dinstructions qui sont

codes en binaire. Le traitement dune instruction peut tre dcompos en trois phases.

Phase 1: Recherche de l'instruction traiter

1. Le PC contient l'adresse de l'instruction suivante du programme. Cette valeur est place

sur le bus d'adresses par l'unit de commande qui met un ordre de lecture.

2. Au bout d'un certain temps (temps d'accs la mmoire), le contenu de la case

mmoire slectionne est disponible sur le bus des donnes.

3. L'instruction est stocke dans le registre instruction du processeur.

Phase 2 : Dcodage de linstruction et recherche de l'oprande

Le registre d'instruction contient maintenant le premier mot de l'instruction qui peut

tre code sur plusieurs mots. Ce premier mot contient le code opratoire qui dfinit

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 23

Architecture des ordinateurs

Anne acadmique 2012-2013

la nature de l'opration effectuer (addition, rotation,...) et le nombre de mots de

l'instruction.

1. L'unit de commande transforme l'instruction en une suite de commandes lmentaires

ncessaires au traitement de l'instruction.

2. Si l'instruction ncessite une donne en provenance de la mmoire, l'unit de

commande rcupre sa valeur sur le bus de donnes.

3. Loprande est stocke dans un registre.

Phase 3 : Excution de l'instruction

1. Le microprogramme ralisant l'instruction est excut.

2. Les drapeaux sont positionns (registre d'tat).

3. L'unit de commande positionne le PC pour l'instruction suivante.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 24

Architecture des ordinateurs

Anne acadmique 2012-2013

4.3 Jeu dinstructions

4.3.1 Dfinition

La premire tape de la conception dun microprocesseur est la dfinition de son

jeu dinstructions. Le jeu dinstructions dcrit lensemble des oprations lmentaires que

le microprocesseur pourra excuter. Il va donc en partie dterminer larchitecture du

microprocesseur raliser et notamment celle du squenceur. A un mme jeu

dinstructions peut correspondre un grand nombre dimplmentations diffrentes du

microprocesseur.

4.3.2 Type dinstructions

Les instructions que lon retrouve dans chaque microprocesseur peuvent tre classes en 4

groupes :

Transfert de donnes pour charger ou sauver en mmoire, effectuer des

transferts de registre registre, etc

Oprations arithmtiques : addition, soustraction, division, multiplication

Oprations logiques : ET, OU, NON, NAND, comparaison, test, etc

Contrle de squence : branchement, test, etc

4.3.3 Codage

Les instructions et leurs oprandes (paramtres) sont stocks en mmoire

principale. La taille totale dune instruction (nombre de bits ncessaires pour la

reprsenter en mmoire) dpend du type dinstruction et aussi du type doprande.

Chaque instruction est toujours code sur un nombre entier doctets afin de faciliter son

dcodage par le processeur. Une instruction est compose de deux champs :

le code instruction, qui indique au processeur quelle instruction raliser

le champ oprande qui contient la donne, ou la rfrence une donne en

mmoire (son adresse).

Le nombre d'instructions du jeu d'instructions est directement li au format du code

instruction.

Ainsi un octet permet de distinguer au maximum 256 instructions diffrentes.

4.3.4 Mode dadressage

Un mode d'adressage dfinit la manire dont le microprocesseur va accder

loprande. Les diffrents modes d'adressage dpendent des microprocesseurs mais on

retrouve en gnral :

Ladressage de registre o lon traite la donne contenue dans un registre

Ladressage immdiat o lon dfinit immdiatement la valeur de la donne

Ladressage direct o lon traite une donne en mmoire

Selon le mode dadressage de la donne, une instruction sera code par 1 ou plusieurs

octets.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 25

Architecture des ordinateurs

Anne acadmique 2012-2013

4.3.5 Temps dexcution

Chaque instruction ncessite un certain nombre de cycles dhorloges pour

seffectuer. Le nombre de cycles dpend de la complexit de linstruction et aussi du mode

dadressage. Il est plus long daccder la mmoire principale qu un registre du

processeur. La dure dun cycle dpend de la frquence dhorloge du squenceur.

4.4 Langage de programmation

Le langage machine est le langage compris par le microprocesseur. Ce langage est

difficile matriser puisque chaque instruction est code par une squence propre de bits.

Afin de faciliter la tche du programmeur, on a cr diffrents langages plus ou moins

volus.

Le langage assembleur est le langage le plus proche du langage machine. Il est

compos par des instructions en gnral assez rudimentaires que lon appelle des

mnmoniques. Ce sont essentiellement des oprations de transfert de donnes entre les

registres et l'extrieur du microprocesseur (mmoire ou priphrique), ou des oprations

arithmtiques ou logiques. Chaque instruction reprsente un code machine diffrent.

Chaque microprocesseur peut possder un assembleur diffrent.

La difficult de mise en uvre de ce type de langage, et leur forte dpendance avec la

machine a ncessit la conception de langages de haut niveau, plus adapts l'homme, et

aux applications qu'il cherchait dvelopper. Faisant abstraction de toute architecture de

machine, ces langages permettent l'expression d'algorithmes sous une forme plus facile

apprendre, et dominer (C, Pascal,

Java, etc). Chaque instruction en langage de haut niveau correspondra une succession

dinstructions en langage assembleur. Une fois dvelopp, le programme en langage de

haut niveau nest donc pas comprhensible par le microprocesseur. Il faut le compiler

pour le traduire en assembleur puis lassembler pour le convertir en code machine

comprhensible par le microprocesseur. Ces oprations sont ralises partir de logiciels

spcialiss appels compilateur et assembleur.

4.5 Performances dun microprocesseur

On peut caractriser la puissance dun microprocesseur par le nombre dinstructions quil

est capable de traiter par seconde. Pour cela, on dfinit :

Le CPI (Cycle Par Instruction) qui reprsente le nombre moyen de cycles dhorloge

ncessaire pour lexcution dune instruction pour un microprocesseur donn.

Le MIPS (Millions d'Instructions Par Seconde) qui reprsente la puissance de

traitement du microprocesseur.

Code machine

FH

Avec FH en MHz

MIPS =

CPI

Pour augmenter les performances dun microprocesseur, on peut donc soit augmenter la

frquence d'horloge (limitation matrielle), soit diminuer le CPI (choix d'un jeu

d'instruction adapt).

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 26

Architecture des ordinateurs

Anne acadmique 2012-2013

4.6 Notion darchitecture RISC et CISC

Actuellement larchitecture des microprocesseurs se composent de deux grandes

familles :

Larchitecture CISC (Complex Instruction Set Computer)

Larchitecture RISC (Reduced Instruction Set Computer)

4.6.1 Larchitecture CISC

4.6.1.1 Pourquoi

Par le pass la conception de machines CISC tait la seule envisageable. En effet,

vue que la mmoire travaillait trs lentement par rapport au processeur, on pensait quil

tait plus intressant de soumettre au microprocesseur des instructions complexes. Ainsi,

plutt que de coder une opration complexe par plusieurs instructions plus petites (qui

demanderaient autant daccs mmoire trs lent), il semblait prfrable dajouter au jeu

dinstructions du microprocesseur une instruction complexe qui se chargerait de raliser

cette opration. De plus, le dveloppement des langages de haut niveau posa de

nombreux problmes quant la conception de compilateurs. On a donc eu tendance

incorporer au niveau processeur des instructions plus proches de la structure de ces

langages.

4.6.1.2 Comment

Cest donc une architecture avec un grand nombre dinstructions o le

microprocesseur doit excuter des tches complexes par instruction unique. Pour une

tche donne, une machine CISC excute ainsi un petit nombre dinstructions mais

chacune ncessite un plus grand nombre de cycles dhorloge. Le code machine de ces

instructions varie dune instruction lautre et ncessite donc un dcodeur complexe

(microcode)

4.6.2 Larchitecture RISC

4.6.2.1 Pourquoi

Des tudes statistiques menes au cours des annes 70 ont clairement montr que

les programmes gnrs par les compilateurs se contentaient le plus souvent

d'affectations, d'additions et de multiplications par des constantes. Ainsi, 80% des

traitements des langages de haut niveau faisaient appel seulement 20% des instructions

du microprocesseur. Do lide de rduire le jeu dinstructions celles le plus

couramment utilises et den amliorer la vitesse de traitement.

4.6.2.2 Comment

Cest donc une architecture dans laquelle les instructions sont en nombre rduit

(chargement, branchement, appel sous-programme). Les architectures RISC peuvent donc

tre ralises partir de squenceur cbl. Leur ralisation libre de la surface permettant

daugmenter le nombre de registres ou dunits de traitement par exemple. Chacune de

ces instructions sexcutent ainsi en un cycle dhorloge. Bien souvent, ces instructions ne

disposent que dun seul mode dadressage. Les accs la mmoire seffectuent seulement

partir de deux instructions (Load et Store). Par contre, les instructions complexes

doivent tre ralises partir de squences bases sur les instructions lmentaires, ce qui

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 27

Architecture des ordinateurs

Anne acadmique 2012-2013

ncessite un compilateur trs volu dans le cas de programmation en langage de haut

niveau.

4.6.3 Comparaison

Le choix dpendra des applications vises. En effet, si on diminue le nombre

d'instructions, on cre des instructions complexes (CISC) qui ncessitent plus de cycles

pour tre dcodes et si on diminue le nombre de cycles par instruction, on cre des

instructions simples (RISC) mais on augmente alors le nombre d'instructions ncessaires

pour raliser le mme traitement.

Architecture RISC

instructions simples ne prenant

quun seul cycle

instructions au format fixe

dcodeur simple (cbl)

beaucoup de registres

seules les instructions LOAD et

STORE ont accs la mmoire

peu de modes dadressage

compilateur complexe

Architecture CISC

instructions complexes prenant

plusieurs cycles

instructions au format variable

dcodeur complexe (microcode)

peu de registres

toutes les instructions sont

susceptibles daccder la mmoire

beaucoup de modes dadressage

compilateur simple

4.7 Amliorations de larchitecture de base

L'ensemble des amliorations des microprocesseurs visent diminuer le temps

d'excution du programme.

La premire ide qui vient lesprit est daugmenter tout simplement la frquence de

lhorloge du microprocesseur. Mais lacclration des frquences provoque un surcrot de

consommation ce qui entrane une lvation de temprature. On est alors amen

quiper les processeurs de systmes de refroidissement ou diminuer la tension

dalimentation.

Une autre possibilit daugmenter la puissance de traitement dun microprocesseur est de

diminuer le nombre moyen de cycles dhorloge ncessaire lexcution dune instruction.

Dans le cas dune programmation en langage de haut niveau, cette amlioration peut se

faire en optimisant le compilateur. Il faut quil soit capable de slectionner les squences

dinstructions minimisant le nombre moyen de cycles par instructions. Une autre solution

est dutiliser une architecture de microprocesseur qui rduise le nombre de cycles par

instruction.

4.7.1 Architecture pipeline

4.7.1.1 Principe

Lexcution dune instruction est dcompose en une succession dtapes et

chaque tape correspond lutilisation dune des fonctions du microprocesseur.

Lorsquune instruction se trouve dans lune des tapes, les composants associs aux autres

tapes ne sont pas utiliss. Le fonctionnement dun microprocesseur simple nest donc

pas efficace.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 28

Architecture des ordinateurs

Anne acadmique 2012-2013

Larchitecture pipeline permet damliorer lefficacit du microprocesseur. En effet,

lorsque la premire tape de lexcution dune instruction est acheve, linstruction entre

dans la seconde tape de son excution et la premire phase de lexcution de linstruction

suivante dbute. Il peut donc y avoir une instruction en cours dexcution dans chacune

des tapes et chacun des composants du microprocesseur peut tre utilis chaque cycle

dhorloge. Lefficacit est maximale. Le temps dexcution dune instruction nest pas

rduit mais le dbit dexcution des instructions est considrablement augment. Une

machine pipeline se caractrise par le nombre dtapes utilises pour lexcution dune

instruction, on appelle aussi ce nombre dtapes le nombre dtages du pipeline.

4.7.1.2 Gain de performance

Dans cette structure, la machine dbute lexcution dune instruction chaque

cycle et le pipeline est pleinement occup partir du quatrime cycle. Le gain obtenu

dpend donc du nombre dtages du pipeline. En effet, pour excuter n instructions, en

supposant que chaque instruction sexcute en k cycles dhorloge, il faut :

n.k cycles dhorloge pour une excution squentielle.

k cycles dhorloge pour excuter la premire instruction puis n-1 cycles pour les n1 instructions suivantes si on utilise un pipeline de k tages

Le gain obtenu est donc de :

n.k

G=

k+n-1

Donc lorsque le nombre n dinstructions excuter est grand par rapport k, on

peut admettre quon divise le temps dexcution par k.

Remarque :

Le temps de traitement dans chaque unit doit tre peu prs gal sinon les units rapides

doivent attendre les units lentes.

Exemples :

LAthlon dAMD comprend un pipeline de 11 tages.

Les Pentium 2, 3 et 4 dIntel comprennent respectivement un pipeline de 12, 10 et 20

tages.

4.7.1.3 Problmes

La mise en place dun pipeline pose plusieurs problmes. En fait, plus le pipeline

est long, plus le nombre de cas o il nest pas possible datteindre la performance

maximale est leve. Il existe 3 principaux cas o la performance dun processeur pipelin

peut tre dgrade ; ces cas de dgradations de performances sont appels des alas :

ala structurel qui correspond au cas o deux instructions ont besoin dutiliser la

mme ressource du processeur (conflit de dpendance),

ala de donnes qui intervient lorsquune instruction produit un rsultat et que

linstruction suivante utilise ce rsultat avant quil nait pu tre crit dans un

registre,

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 29

Architecture des ordinateurs

Anne acadmique 2012-2013

ala de contrle qui se produit chaque fois quune instruction de branchement est

excute. Lorsquune instruction de branchement est charge, il faut normalement

attendre de connatre ladresse de destination du branchement pour pouvoir

charger linstruction suivante. Les instructions qui suivent le saut et qui sont en

train dtre traites dans les tages infrieurs le sont en gnral pour rien, il faudra

alors vider le pipeline. Pour attnuer leffet des branchements, on peut spcifier

aprs le branchement des instructions qui seront toujours excutes. On fait aussi

appel la prdiction de branchement qui a pour but de recenser lors de

branchements le comportement le plus probable. Les mcanismes de prdiction de

branchement permettent d'atteindre une fiabilit de prdiction de l'ordre de 90

95 %.

Lorsquun ala se produit, cela signifie quune instruction ne peut continuer

progresse dans le pipeline. Pendant un ou plusieurs cycles, linstruction va rester bloque

dans un tage du pipeline, mais les instructions situes plus en avant pourront continuer

sexcuter jusqu ce que lala ait disparu. Plus le pipeline possde dtages, plus la

pnalit est grande. Les compilateurs sefforcent dengendrer des squences dinstructions

permettant de maximiser le remplissage du pipeline. Les tages vacants du pipeline sont

appels des bulles de pipeline, en pratique une bulle correspond en fait une

instruction NOP (No OPeration) mise la place de linstruction bloque.

4.7.2 Notion de cache mmoire

4.7.2.1 Problme pos

Lcart de performance entre le microprocesseur et la mmoire ne cesse de

saccrotre. En effet, les composants mmoire bnficient des mmes progrs

technologique que les microprocesseurs mais le dcodage des adresses et la

lecture/criture dune donnes sont des tapes difficiles acclrer. Ainsi, le temps de

cycle processeur dcrot plus vite que le temps daccs mmoire entranant un goulot

dtranglement. La mmoire n'est plus en mesure de dlivrer des informations aussi

rapidement que le processeur est capable de les traiter. Il existe donc une latence daccs

entre ces deux organes.

4.7.2.2 Principe

Depuis le dbut des annes 80, une des solutions utilises pour masquer cette

latence est de disposer une mmoire trs rapide entre le microprocesseur et la mmoire.

Elle est appele cache mmoire. On compense ainsi la faible vitesse relative de la

mmoire en permettant au microprocesseur dacqurir les donnes sa vitesse propre. On

la ralise partir de cellule SRAM de taille rduite ( cause du cot). Sa capacit mmoire

est donc trs infrieure celle de la mmoire principale et sa fonction est de stocker les

informations les plus rcentes ou les plus souvent utilises par le microprocesseur. Au

dpart cette mmoire tait intgre en dehors du microprocesseur mais elle fait

maintenant partie intgrante du microprocesseur et se dcline mme sur plusieurs

niveaux.

Le principe de cache est trs simple : le microprocesseur na pas conscience de sa

prsence et lui envoie toutes ses requtes comme sil agissait de la mmoire principale :

Soit la donne ou linstruction requise est prsente dans le cache et elle est alors

envoye directement au microprocesseur. On parle de succs de cache. (a)

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 30

Architecture des ordinateurs

Anne acadmique 2012-2013

soit la donne ou linstruction nest pas dans le cache, et le contrleur de cache

envoie alors une requte la mmoire principale. Une fois linformation rcupre,

il la renvoie au microprocesseur tout en la stockant dans le cache. On parle de

dfaut de cache. (b)

a)

b)

Bien entendu, le cache mmoire napporte un gain de performance que dans le

premier cas. Sa performance est donc entirement lie son taux de succs. Il est courant

de rencontrer des taux de succs moyen de lordre de 80 90%.

Remarque :

Un cache utilisera une carte pour savoir quels sont les mots de la mmoire

principale dont il possde une copie. Cette carte devra avoir une structure simple.

Il existe dans le systme deux copies de la mme information : loriginale dans la

mmoire principale et la copie dans le cache. Si le microprocesseur modifie la

donne prsente dans le cache, il faudra prvoir une mise jour de la mmoire

principale.

Lorsque le cache doit stocker une donne, il est amen en effacer une autre. Il

existe donc un contrleur permettant de savoir quand les donnes ont t utilises

pour la dernire fois. La plus ancienne non utilise est alors remplace par la

nouvelle.

A noter que lon peut reprendre le mme principe pour les disques durs et

CD/DVD.

4.7.3 Architecture superscalaire

Une autre faon de gagner en performance est dexcuter plusieurs instructions en

mme temps. L'approche superscalaire consiste doter le microprocesseur de plusieurs

units de traitement travaillant en parallle. Les instructions sont alors rparties entre les

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 31

Architecture des ordinateurs

Anne acadmique 2012-2013

diffrentes units d'excution. Il faut donc pouvoir soutenir un flot important

dinstructions et pour cela disposer dun cache performant.

4.7.4 Architecture pipeline et superscalaire

Le principe est de dexcuter les instructions de faon pipeline dans chacune des units

de traitement travaillant en parallle.

4.8 Processeurs spciaux

4.8.1 Le microcontrleur

Ce sont des systmes minimum sur une seule puce. Ils contiennent un CPU, de la

RAM, de la ROM et des ports dEntre/Sorties (parallles, sries, I2C, etc..). Ils

comportent aussi des fonctions spcifiques comme des compteurs programmables pour

effectuer des mesures de dures, des CAN voir des CNA pour sinsrer au sein de chanes

dacquisition, des interfaces pour rseaux de terrain, etc ...

Il est adapt pour rpondre au mieux aux besoins des applications embarques

(appareil lectromnagers, chane dacquisition, lecteur carte puce, etc...). Il est par

contre gnralement moins puissant en terme de rapidit, de taille de donnes traitables

ou de taille de mmoire adressable quun microprocesseur.

4.8.2 Le processeur de signal

Le processeur de signal est beaucoup plus spcialis. Alors qu'un microprocesseur

n'est pas conu pour une application spcifique, le processeur DSP (Digital Signal

Processor) est optimis pour effectuer du traitement numrique du signal (calcul de FFT,

convolution, filtrage numrique, etc...).

Les domaines dapplication des D.S.P taient lorigine les tlcommunications et

le secteur militaire. Aujourdhui, les applications se sont diversifies vers le multimdia

(lecteur CD, MP3, etc..) llectronique grand public (tlvision numrique, tlphone

portable, etc), lautomatique, linstrumentation, llectronique automobile, etc

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 32

Architecture des ordinateurs

Anne acadmique 2012-2013

EXERCICES

Exercice .1. On considre des blocs de 2 mots (8 octets). Soit un cache direct de 16

blocs.

(1) Quelle est la taille du cache ?

(2) En supposant que la mmoire une taille de 232 octets, schmatiser la dcomposition

dune adresse mmoire en zone, ligne, octet.

(3) Quelle est la taille totale occupe par le cache ?

(4) Voici une suite de rfrences des adresses de mots (4 octets) :

1, 6, 8, 32, 7, 33, 1, 39, 27, 59, 58, 64, 97, 1.

On suppose que le cache est initialement vide. Dterminer pour chaque rfrence de la

suite si elle conduit un succs ou un dfaut. Donner le contenu final du cache.

Exercice .2. Soit un cache associatif de 16 blocs. Rpondre aux questions de lexercice

prcdent.

Exercice .3. Soit un cache dassociativit 2 de 16 blocs. Rpondre aux questions de

lexercice prcdent.

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 33

Architecture des ordinateurs

Anne acadmique 2012-2013

CHAPITRE 5 : LES ECHANGES DE DONNEES

La fonction dun systme microprocesseurs, quel quil soit, est le traitement de

linformation. Il est donc vident quil doit acqurir linformation fournie par son

environnement et restituer les rsultats de ses traitements. Chaque systme est donc

quip dune ou plusieurs interfaces dentres/sorties permettant dassurer la

communication entre le microprocesseur et le monde extrieur.

Les techniques dentres/sorties sont trs importantes pour les performances du

systme.

Rien ne sert davoir un microprocesseur calculant trs rapidement sil doit souvent

perdre son temps pour lire des donnes ou crire ses rsultats. Durant une opration

dentre/sortie, linformation est change entre la mmoire principale et un priphrique

reli au systme. Cet change ncessite une interface (ou contrleur) pour grer la connexion.

Plusieurs techniques sont employes pour effectuer ces changes.

5.1 Linterface dentre/sortie

5.1.1 Rle

Chaque priphrique sera reli au systme par lintermdiaire dune interface (ou

contrleur) dont le rle est de :

Connecter le priphrique au bus de donnes

Grer les changes entre le microprocesseur et le priphrique

5.1.2 Constitution

Pour cela, linterface est constitue par :

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 34

Architecture des ordinateurs

Anne acadmique 2012-2013

Un registre de commande dans lequel le processeur dcrit le travail effectuer

(sens de transfert, mode de transfert).

Un ou plusieurs registres de donnes qui contiennent les mots changer entre

le priphrique et la mmoire

Un registre dtat qui indique si lunit dchange est prte, si lchange sest bien

droul, etc

On accde aux donnes de linterface par le biais dun espace dadresses dentres/sorties.

5.2 Techniques dchange de donnes

Avant denvoyer ou de recevoir des informations, le microprocesseur doit

connatre ltat du priphrique. En effet, le microprocesseur doit savoir si un

priphrique est prt recevoir ou transmettre une information pour que la

transmission se fasse correctement. Il existe 2 modes dchange dinformation :

Le mode programm par scrutation ou interruption o le microprocesseur sert

dintermdiaire entre la mmoire et le priphrique

Le mode en accs direct la mmoire (DMA) o le microprocesseur ne se charge

pas de lchange de donnes.

5.2.1 Echange programm

5.2.1.1 Scrutation

Dans la version la plus rudimentaire, le microprocesseur interroge linterface pour

savoir si des transferts sont prts. Tant que des transferts ne sont pas prts, le

microprocesseur attend.

Linconvnient majeur est que le microprocesseur se retrouve souvent en phase dattente.

Il est compltement occup par linterface dentre/sortie. De plus, linitiative de

lchange de donnes est dpendante du programme excut par le microprocesseur. Il

peut donc arriver que des requtes dchange ne soient pas traites immdiatement car le

microprocesseur ne se trouve pas encore dans la boucle de scrutation.

Ce type dchange est trs lent.

5.2.1.2 Interruption

Une interruption est un signal, gnralement asynchrone au programme en cours,

pouvant tre mis par tout dispositif externe au microprocesseur. Le microprocesseur

possde une ou plusieurs entres rserves cet effet. Sous rserve de certaines

conditions, elle peut interrompre le travail courant du microprocesseur pour forcer

lexcution dun programme traitant la cause de linterruption.

Dans un change de donnes par interruption, le microprocesseur excute donc son

programme principal jusqu ce quil reoive un signal sur sa ligne de requte

dinterruption. Il se charge alors deffectuer le transfert de donnes entre linterface et la

mmoire.

Principe de fonctionnement dune interruption :

Avant chaque excution dinstructions, le microprocesseur examine sil y a eu une

requte sur sa ligne dinterruption. Si cest le cas, il interrompt toutes ces activits et

sauvegarde ltat prsent (registres, PC, accumulateurs, registre dtat) dans un registre

particulier appel pile. Les donnes y sont entasses comme on empile des livres (la

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 35

Architecture des ordinateurs

Anne acadmique 2012-2013

premire donne sauvegarde sera donc la dernire tre restitue). Ensuite, il excute le

programme dinterruption puis restitue ltat sauvegard avant de reprendre le programme

principal.

5.2.2 Echange direct avec la mmoire

Ce mode permet le transfert de blocs de donnes entre la mmoire et un

priphrique sans passer par le microprocesseur. Pour cela, un circuit appel contrleur

de DMA (Direct Memory Access) prend en charge les diffrentes oprations.

Le DMA se charge entirement du transfert dun bloc de donnes. Le microprocesseur

doit tout de mme :

initialiser lchange en donnant au DMA lidentification du priphrique concern

donner le sens du transfert

fournir ladresse du premier et du dernier mot concerns par le transfert

Un contrleur de DMA est dot dun registre dadresse, dun registre de donne, dun

compteur et dun dispositif de commande (logique cble). Pour chaque mot change, le

DMA demande au microprocesseur le contrle du bus, effectue la lecture ou l'criture

mmoire l'adresse contenue dans son registre et libre le bus. Il incrmente ensuite cette

adresse et dcrmente son compteur. Lorsque le compteur atteint zro, le dispositif

informe le processeur de la fin du transfert par une ligne d'interruption.

Le principal avantage est que pendant toute la dure du transfert, le processeur est libre

d'effectuer un traitement quelconque. La seule contrainte est une limitation de ses propres

accs mmoire pendant toute la dure de l'opration, puisqu'il doit parfois retarder

certains de ses accs pour permettre au dispositif d'accs direct la mmoire d'effectuer

les siens : il y a apparition de vols de cycle.

5.3 Types de liaisons

Les systmes microprocesseur utilisent deux types de liaison diffrentes pour se

connecter des priphriques :

liaison parallle

liaison srie

On caractrise un type de liaison par sa vitesse de transmission ou dbit (en bit/s).

Ralis par M. NZI consultant en informatique dcisionnelle

Mail : ingkouak@yahoo.fr/22506165394

Page 36

Architecture des ordinateurs

Anne acadmique 2012-2013

5.3.1 Liaison parallle

Dans ce type de liaison, tous les bits dun mot sont transmis simultanment. Ce

type de transmission permet des transferts rapides mais reste limite de faibles distances

de transmission cause du nombre important de lignes ncessaires (cot et

encombrement) et des problmes dinterfrence lectromagntique entre chaque ligne

(fiabilit). La transmission est cadence par une horloge

Exemple : Bus PCI, AGP dans un PC.

5.3.2 Liaison srie

Dans ce type de liaison, les bits constitutifs dun mot sont transmis les uns aprs

les autres sur un seul fil. Les distances de transmission peuvent donc tre plus beaucoup

plus importantes mais la vitesse de transmission est plus faible. Sur des distance

suprieures quelques dizaines de mtres, on utilisera des modems aux extrmits de la

liaison.

La transmission de donnes en srie peut se concevoir de deux faons diffrentes :

en mode synchrone, lmetteur et le rcepteur possde une horloge synchronise

qui cadence la transmission. Le flot de donnes peut tre ininterrompu.

en mode asynchrone, la transmission seffectue au rythme de la prsence des

donnes.

Les caractres envoys sont encadrs par un signal start et un signal stop.

Principe de base dune liaison srie asynchrone :

Afin que les lments communicants puissent se comprendre, il est ncessaire dtablir un

protocole de transmission. Ce protocole devra tre le mme pour chaque lment.