Professional Documents

Culture Documents

AN4105 Power Switching IC

Uploaded by

atomo33Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

AN4105 Power Switching IC

Uploaded by

atomo33Copyright:

Available Formats

www.fairchildsemi.

com

Application Note AN4105

Design Considerations for Switched Mode Power

Supplies Using A Fairchild Power Switch (FPS) in a

Flyback Converter

Introduction

power MOSFET (SenseFET) and pulse width modulation

(PWM) based control IC in one package. Moreover, they

provide enhanced IC functionality, thereby minimizing the

number of additional components needed in an SMPS.

Fairchild Power Switch (SPS) ICs are widely used in the

power circuits of a variety of equipment, such as color TVs,

printers, PCs, monitors, battery chargers and ac adapters.

They typically incorporate a variety of enhanced protection

functions and they permit a much reduced power

consumption in standby modes.

Flyback switched mode power supplies (SMPS) are among

the most frequently used power circuits in household and

consumer electronics. The basic function of an SMPS is to

supply regulated power to the load on the secondary, or

output side. An SMPS typically incorporates a power

transformer, secondary-side rectifier diodes, a switching

semiconductor device with control IC, and peripheral

circuitry. If the level of integration of the switching and

control circuitry is not high enough, then additional, separate

circuits will be required to accommodate all functions. Such

additional components raise the overall SMPS cost and not

uncommonly reduce reliability.

This application note considers the three major functional

blocks of an SMPS: Fairchild Power Switch (SPS) , flyback

converter, and transformer. It discusses a variety of issues

important to their design and use in the overall SMPS.

Fairchild Power Switches are highly-integrated ICs for

power supply applications. They combine a high-voltage

#3 Vcc

6.3V

2uA

32V

Sync.

Voltage

Ref.

UVLO

Vck

1mA

#4

Feedback

OSC.

#1

Drain

2.5R

#5

Soft Start

& Sync.

S

R

Q

LEB

Voffset

#2

Source

GND

Sense

5V

Rsense

Reset

Sense

FET

S

7.5V

Reset

Q

Thermal

Protection

OVP

Control IC

Figure1. Internal block diagram of a Fairchild Power Switch(FPS).

Rev. 1.0.2

2002 Fairchild Semiconductor Corporation

AN4105

APPLICATION NOTE

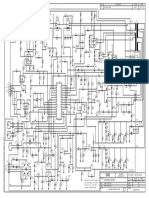

1. Block Diagram and Basic Operation

of a Fairchild Power Switch(FPS)

1.1 Block Diagram

Figure 1 presents a block diagram of a Fairchild Power

Switch (FPS). It can be divided into several large, functional

sections: under voltage lockout circuitry (UVLO); reference

voltage; oscillator (OSC); pulse width modulation (PWM)

block; protection circuits; and gate driving circuits.

IC current is less than 300A. IC operation starts when CCC

(Figure 2) charges to 15V. Because only a small current (<1

mA) is allowed to flow in through the resistor during normal

operation this technique reduces the current dissipation in

the SMPS start up resistor.

DC

L INK

Rg

Ccc

V cc

3

1.2 Under Voltage Lockout (UVLO)

In te rn al Bia s

A Fairchild Power Switch (FPS) under voltage lockout

(UVLO) circuitry (Figure 2) guarantees stable operation of

the ICs control circuit by stopping and starting it as a

function of the value of VCC (Figure 3). The tur off and turn

on voltage thresholds are fixed internally at 10V and 15V,

respectively. Therefore the UVLO circuitry turns off the

control circuit when VCC is lower than 10V and starts it

when VCC is higher than 15V. Once the control circuit starts

operating, VCC must drop below the 10V level for the

UVLO to stop the circuit again. Before switching starts, the

P o we r O n

Re se t

L a tch

Co mp a ra to r

Fairchild Power

Switch(FPS)

SPS

5V

V re f

1 5V /1 0 V

-

UV L

Vz

6V

Good Logic

Figure 2. Detail of the undervoltage lockout (UVLO)

circuitry in a Fairchild Power Switch. The gate

operating circuit holds in a low state during UVLO,

thereby maintaining the SenseFET at turnoff.

Icc

[mA]

20

Power On

Reset Range

0.3

6V

10V

15V

Vz

Vc

[V]

[V]

c

Figure 3. Fairchild Power Switch(FPS) control circuit status vs. Vcc.

1.3 Feedback Control Circuit

The Fairchild Power Switch(FPS) control IC uses a current

mode PWM and operates such that MOSFET current is

proportional to the feedback voltage Vfb. This limits the

MOSFET current at every cycle. It also offers other

advantages, such as a well regulated SMPS output voltage

with input voltage changes. This method of control also

works successfully in SMPSs used for monitors, which may

have a broad range of synchronizing frequencies to deal

with. As shown in Figure 4, the Fairchild Power Switch

(FPS) oscillator turns on the MOSFET. The feedback

comparator operates to turn it off again, when the MOSFET

current reaches a set value proportional to Vfb. The

MOSFET turn off operation is as follows:(1) the internal

(R+2.5R) voltage divider sets the voltage fed back to one

input of the feedback comparator at Vfb /3.5; (2) a current

proportional to the drain current flows to the MOSFET sense

terminal making Vsense proportional to the drain current;

and, (3) when Vsense becomes greater than Vfb, the output of

the feedback comparator goes high, turning off the

MOSFET. Figure 4 also shows that the circuit is designed to

use an opto isolator in the feedback loop. This is appropriate

for an off line design where input to output

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4105

isolation is required. Cfb improves the noise characteristics.

If the control IC incorporates an error amp however, as in

Fairchilds KA3842B/3B/4B/5B current mode PWM

controller ICs for SMPSs then a resistor and capacitor are

required to provide the feedback to the error amp. This

would provided the same functions as those provided by the

circuit of Figure 4, e.g., fine control of the output voltage

through Vfb. Similarly, other appropriate devices here are

Fairchilds LM431/TL431/KA431 series of three terminal

shunt regulators. These have a very sharp turn on

characteristic much like a Zener diode and are widely used in

SMPS secondary side error amplifiers.

Fairchild Power Switch(FPS)

SPS

Precision

Current Source

2uA

Vck

1mA

Idrain

OSC.

Vfb

#4

#1

5V

2.5R

On

Cfb

Vfb*

Vss

#2

Sense

Off

Ioffset

#5

Css

Reset

Rsense

Vsense

Isense

Figure 4. Fairchild Power Switch(FPS) feedback circuit appropriate for off line SMPS use (current mode PWM).

1.4 Example Fairchild Power Switch (FPS)

Control Circuit

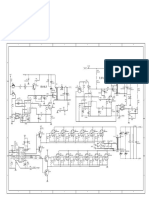

Figure 5 shows two approaches to control feedback with a

Fairchild Power Switch (FPS). The design in Figure 5a uses

the LM431 regulator, and that of Figure 5b uses a Zener diode.

Even though zenor diode approach is cost effective, the output

regulation is relatively poor.

In Figure 5a, C1 together with R1 produce high frequency

pole formed by the internal 3.5k resistor and Cfb in the

compensation networrk. R4 limits the maximum current of the

photodiode to 2.3mA [(12V - 2.5V - 2V) /3.3K, where 2.5V

is the LM431's saturation voltage and 2 V is the photodiode's

voltage drop]. Cfb should be determined by considering the

shutdown delay time (see Section 2.1). In Figure 5b, R3 sets a

fixed current to the Zener diode to stabilize its voltage.

2002 Fairchild Semiconductor Corporation

AN4105

APPLICATION NOTE

2uA

Vo, 80V

12V

PC817

Vck

1mA

Vfb

Fairchild Power Switch(FPS)

SPS

OSC.

#4

C1

33n

R3

1k

R1

33k

Cfb

33n

2k

2R

Vfb*

R4

3.3k

1k

Ioffset

10n

R2

1k

KA431

C2

Sense

Rsense

LM431

Control IC

(a) Control

ControlCircuit

circuitusing

thatKA431(LM431)

used KA431(LM431)

Fairchild Power Switch(FPS)

2uA

Vo, 80V

R1

33k

12V

PC817

Vfb

2k

2R

Vfb*

1k

2.2k

C1

0.1u

OSC.

#4

Cfb

33n

R3

1k

SPS

Vck

1mA

Ioffset

Rsense

Sense

R2

Vz

Zener the

Diode

Control

IC

(b) Control

ControlCircuit

circuitusing

thata used

zener

diode

Figure 5. Fairchild Power Switch(FPS) feedback control circuit.

1.5 Soft Start Operation

Normally, the SMPS output voltage increases from start up

with a fixed time constant. This is due to the capacitive

component of the load. At start up, therefore, the feedback

signal applied to the PWM comparator's inverting input

reaches its maximum value (1V), This is because the

feedback loop is effectively open. Also at this time, the drain

current is at its peak value (Ipeak) and maximum allowable

power is being delivered to the secondary load. With that

said, note that when the SMPS pushes maximum power to

the secondary side for this initial fixed time, the entire circuit

is seriously stressed. Use of a soft start function avoids such

stresses. Figure 6 shows how to implement a soft start for a

Fairchild Power Switch(FPS). At turn on, the soft start

capacitor CS on pin 5 of the Fairchild Power Switch(FPS)

starts to charge through the 1mA current source. When the

4

voltage across CS reaches 3V, diode DS turns off. No more

current flows to it from the 1mA current source. Cs then

continues to charge to 5V through the 50k resistor.

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4105

Fa ircPower

hild Switch(FPS)

Pow e r

Fairchild

1 0V

2

Fairchild Power Switch(FPS)

SPS

Sw itc h (SPS)

PW M

Co mp a ra to r

5V

Ds

5 0k

#4

Figure 6. Soft start circuit.

Note that when the voltage across CS exceeds 3V, The voltage

at the comparators inverting terminal no longer follows the

voltage across CS. Instead, it follows the output voltage

feedback signal. In shutdown or protection circuit operation,

capacitor CS is discharged, in order to enable it to charge from

0V at restart.

1.6 Synchronization

In an SMPS intended for use with monitors, synchronization

is handled differently than in a general purpose SMPS. For

monitor use, it is necessary to prevent noise from appearing on

the monitor display. To accomplish this, it is necessary to

synchronize the SMPS switching frequency with the

monitors horizontal sync frequency. The monitors horizontal

scan flyback signal is commonly used as the external sync

signal for the SMPS. By synchronizing the switching with the

horizontal scans flyback, the switching noise is positioned at

the far left of the monitor display where it cannot be seen.

Figure 7 shows how to implement the external circuit for

synchronization. The external sync signal, applied across

resistor Rs, cannot drop below 0.6V because of diode Dsync.

After the conclusion of the initial soft start, the voltage across

Cs remains at 5V until the external sync signal is applied, at

which point it looks like VRs of Figure 8. The sync comparator

compares VCs against a 6.3V level and produces the

comparator output waveform, Vcomp of Figure 8.

A Fairchild Power Switch (FPS) has an internal timing

capacitor, Ct. Figure 8 shows that when the voltage on Ct, VCt,

reaches an upper threshold, it begins to discharge; then, when

it reaches a lower threshold, it again starts to charge. This

operation is controlled by the internal oscillator. The oscillator

output signal, VCk in Figure 8, which goes low.

2002 Fairchild Semiconductor Corporation

V C O MP

V RS

Rs

Dsyn c

6 .3V

OSC .

S yn c

c o m p a ra t o r

S eries

#5

Cs

K A5XX Series

Exte rna l

Syn c In p ut

KA2SXX

Rs K

A 5S X X

KA3SXX

K

A 5Q X X

V CS

E x t e rn a l

S yn c

I n p ut

#5

Cs

PW M

c o m p a ra to r

5V

Figure 7. Synchronization circuit.

when Ct recharges and high when it discharges, is applied to

the Fairchild Power Switch (FPS) S/R Latch Set terminal. In

the absence of an external sync signal, the voltage across Ct

oscillates at the basic frequency of 20kHz. In the presence of

a sync signal, however, the Set signal goes high because VCt

charges to the high threshold following the external sync

signal, and, ultimately, the Set signal, which determines the

switching frequency, synchronizes to the external sync

signal. It is necessary to limit the Set signal's high duration to

5% or less of the full cycle. As the Set signal drops low the

gate turns on. If the device were not synchronized to the

horizontal scan of the monitor, noise would appear on the

screen. When the Set signal goes high, the sync is synchronized with the horizontal scan flyback. Because the high

duration is 5% (maximum) of the full cycle, the start of the

horizontal scan (as the Set signal goes low) turns on the

switch. The switch turn on noise, therefore, is hidden in the

horizontal blanking period at the far left of the monitor

display.

V RS

2V

0V

V CS

5V

0V

V C O MP

0V

V ThH

V CT

0V

V ThL

V ck

0V

Figure 8. Synchronization circuit operation.

AN4105

APPLICATION NOTE

2. Fairchild Power Switch(FPS) Built

In Protection Circuits

When the Fairchild Power Switch (FPS) senses an overload,

it waits for a specified time. If the overload is still present

after this, it is considered a true overload and the device

shuts down.

The Fairchild Power Switch (FPS) has a current control that

prohibits current flow above a set maximum, which means

the maximum input power is limited at any given voltage.

Therefore, if the output load tries to draw more than this

level, Vo (Figure 9) drops below the set voltage and LM431

can draw only a given minimum current. As a result, the opto

coupler secondary current drops to almost zero. Almost the

entire current flow at the node is from the Fairchild Power

Switch (FPS) 1mA current source. Hence, the internal 3k

resistor (2.5R + R = 3K) moves Vfb to 3V. From this point

on, however, the 5A current source starts to charge Cfb,

and, because the opto coupler secondary current is almost

zero, Vfb continues to increase. When Vfb reaches 7.5V, the

Fairchild Power Switch (FPS) shuts down.

Since a Fairchild Power Switch (FPS)s built in protection

circuits do not require additional, external components,

reliability is increased without increasing cost. Note that the

protective circuitry can completely stop the SMPS operation

(latch mode protection) until the power is turned off and on

again, and can make the control voltage restart above the

ULVO level should the latch be released below ULVO

(Auto Restart Mode protection).

2.1 Output Overload Protection

An overload is any load greater than the load defined as

normal for operation. This is not a short circuit. The

Fairchild Power Switch (FPS) overload protection

determines whether the overload is true or merely transient.

Only a true overload will trigger the overload protection.

2uA

Vck

1mA

Vfb

Vo

Fairchild Power Switch(FPS)

SPS

OSC.

#4

D1

Cfb

D2

2.5R

2R

Vfb*

Ioffset

LM431

KA431

Sense

Rsense

Reset

7.5V

R

Q

Thermal

Shutdown

Shutdown

Figure 9. Fairchild Power Switch(FPS) overload protection circuit.

The shutdown delay interval is therefore determined by Cfb.

When Cfb is 10nF, the shutdown delay t2 (see Figure 10b) is

about 9mS. With Cfb at 0.1F, t2 is about 90ms. Such delay

intervals do not allow the typical transients observed to shut

down the Fairchild Power Switch (FPS). Note that, if a

longer delay is needed, Cfb cannot be made arbitrarily large

because it is important in determining the dynamic response

of the SMPS.

When a large value of Cfb is necessary, a series connected

capacitor and Zener diode can be connected across Cfb as

shown in Figure 10a. The combination works in this way:

When Vfb is below 3V, the low valued Cfb allows the SMPS

to have a good dynamic response. When Vfb is above 3.9V,

the high valued Cd extends the delay time to the desired

6

shutdown point. Of course, where transients are insignificant

and good dynamic response is not required, then eliminate

Cd and the Zener, thereby eliminating their added costs.

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4105

Fairchild Power Switch(FPS) V

SPS

2uA 1mA

7.5V

Vfb

Vo

#

Cd

Cf

D1

D2

Vfb*

Vz=3.9V

3.9V

3V

0

t

LM431

KA431

t1

7.5V

Tim e Constant

= 3.5R*Cfb

(a)

t3

t2

2uA = Cfb*0.9V/t2

Shutdown

2uA = Cd*3.6V/t3

< SPS

Delayed

Shutdown

>

<Fairchild

Powerlong

Switch

(FPS) long

Delayed Shutdown>

(b)

Figure 10. Long delay shutdown.

2.2 Output Short Circuit Protection

When the SMPSs output terminal is short circuited the input

current is at maximum. The output power however, is not a

maximum. This is because there can be no load voltage since

the load is a short circuit. Under such conditions the output

short circuit protection operates as follows.

When the output load short circuits a relatively large

transformer winding in the SMPS, the Fairchild Power

Switch(FPS)s MOSFET current becomes much greater than

Ipeak because the inductors magnetic core is unable to reset.

This is due to low transformer coil voltage at turn off. This

occurs because the current remaining in the inductor during

the Fairchild Power Switch(FPS)s minimum turn on time

cannot decrease by that amount during the remaining turn off

time. Even though it is a large current, it does not unduly

stress the MOSFET but does greatly stress the transformers

secondary coils and the secondary side rectifiers.

In most flyback or forward converters the controller gets its

power from a small secondary bias winding in the

transformer. Furthermore, this controller voltage is proportional to the output voltage (see circuit of Figure 11a). This

is fairly straightforward because, for a flyback converter, the

coil voltage when the switch turns off is proportional to the

output voltage.

For a forward converter, the transformer average voltage at

turn off is proportional to the output voltage. For a flyback

converter SMPS, the output short circuit protection circuit

can be operated in either latch mode or auto restart mode.

The change in Vcc as a function of Rsd is shown in Figure

11b. Rsd is shown in Figure 11a. When Rsd is zero, Vcc

reaches the maximum value of Vtx (see lower primary

winding, Figure 11a), i.e., n'Vsn/n, which is proportional to

the maximum transformer current. For this case, if the output

short circuits, Vcc increases and, after a specified delay, the

2002 Fairchild Semiconductor Corporation

protection circuit operates, entering the latch mode.

However, when Rsd is made sufficiently large, Vcc can

become smaller than n'Vo. Therefore, if the output short

circuits, Vcc drops, but, if Ccc (see Figure 11a) is sufficiently

large, Vcc stays at a level higher than the UVLO's lower

threshold voltage (10V) until Vfb reaches 7.5V (Figure 11c2) and latch mode protection starts. In contrast, if Ccc is

small enough Vcc approaches the UVLO's low threshold

before Vfb reaches 7.5V (Figure 11c-3), and the UVLO

operates instead of the protection circuit, stopping the device

switching. In such a case, if Vcc exceeds the ULVO's upper

threshold voltage (15V), auto restart operates again. Rsd,

Ccc, and Cfb have affects even at start up and power down, so

their values must be decided upon carefully. Our

experiments have indicated that 10-20W is most appropriate

for Rsd.

AN4105

APPLICATION NOTE

Vo

n :1

Vin

V sn

V in

Fairchild Power Switch(FPS)

SPS

LM431

C o n t ro l

IC

K A 4 31

2

3

V fb

V cc

Rsd

C fb

n *: 1

V tx

Ccc

(a ) F ly b a ck c o n v e rt e r

V tx

No Rsd

n *V s n / n

n *V o

L ow Rsd

L a rg e R s d

0

n * V in / n

The voltage Vtx waveform of NB and VCC(the rectified VNB) depending on Rsd

(b ) F la yb a c k co n v e rt e r c o n t ro lle r v o lt a g e a n d R s d d e p e n d e n t V c c

(1 )

V cc

S h u t do w n

(2 )

(3 )

UVLO

S h u t do w n

1 0V

7 . 5V

3V

V fb

Cvcc

t

0V

O u t p ut s h o rt

UVLO

S h u t do w n

(C ) V c c a n d V f b w a v e f o rm s d e p e n d in g o n t h e re la t iv e s iz e o f C v c c a t o u t p u t sh o rt

Figure 11. Operation of the SMPS flyback converters output short circuit protection (latch mode ).

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4105

2.3 Fast Protection Without Delay

can be made to operate sufficiently fast. In such a case, when

the transistor is turned off, the protection shifts to auto restart

mode for normal operation. It is also possible to use this

circuit as an output enable circuit. Fast latch mode protection

can be implemented by adding a photocoupler. Thus, when

the output terminal latch mode transistor turns on, a large

current flows through the photodiode PC2. A large current

therefore flows through the primary phototransistor, which

increases Vfb rapidly. This executes fast latch mode

protection with no time delay.

It was mentioned above that the Fairchild Power

Switch(FPS) shutdown capability is associated with a delay,

to allow normal transients to occur without shutting down

the system. In effect, this restricts the protection range. If

fast protection is required, then additional circuitry is called

for. Figure 12 shows how its done. A transistor is used to

force the feedback photodiode current to increase causing

the primary side Vfb to be forced below 0.3V. Therefore the

Fairchild Power Switch (FPS) stops switching. Depending

on the magnitude of the photodiode current, the protection

n:1

Vin

Vo

V sn

Vin

P C1

Fairchild Power Switch(FPS)

SPS

1

Co n tro l

IC

2

KA4 31

LM431

B urst Mo de

S hu t Do wn

V fb

Vcc

Rsd

Ccc

PC1

Vo

PC2

n *:1

Vtx

P C2

L atch Mod e

Cfb

Sh u t Do wn

Figure 12. A fast protection circuit without a shutdown delay.

2.4 Overvoltage Protection

The Fairchild Power Switch (FPS) has a self protection

feature that operates even when faults exist in the feedback

path. These could include an open or short circuit. On the

primary side, if the feedback terminal is short circuited, then

the voltage on it is zero and hence the Fairchild Power

Switch (FPS) is unable to start switching.

If the feedback path open circuits, the protection circuit

operates as though a secondary overload is present. Further,

if the feedback terminal looks open due say, to some fault in

the primary feedback circuit, the primary side could switch

at the set maximum current level until the protection circuit

operates. This causes the secondary voltage to become much

greater than the rated voltage. Note that in such a case if

there were no protection circuit, the fuse could blow or, more

serious, a fire could start.

It is possible that, without a regulator, devices directly

connected to the secondary output could be destroyed.

Instead, however, the Fairchild Power Switch (FPS) over

2002 Fairchild Semiconductor Corporation

voltage protection circuit operates. Since VCC is proportional to the output, in an over voltage situation it will also

increase. In the Fairchild Power Switch (FPS), the protection

circuit operates when Vcc exceeds 25V. Therefore in normal

operation Vcc must be set below 25V.

AN4105

APPLICATION NOTE

3. Noise Considerations at switch Turn On

3.1 SMPS Current Sensing

(1) Reverse recovery current is generated when the SMPS

operates in continuous conduction mode (CCM; see Section

4.1). If the MOSFET is turned on while the rectifier diode is

conducting, the diode, during its reverse recovery time will

act like a short circuit. Therefore a large current spike will

flow in the MOSFET. There are three ways to reduce the

magnitude of this (reverse recovery) current: use a fast

recovery diode; reduce the MOSFETs gate operating

current at turn on; or, increase the transformer leakage

inductance.

(2) The total capacitance on the MOSFETs drain side

includes the parasitic capacitor Cds between the drain and the

source terminals, the junction capacitance of the snubber

diode, and the capacitance of the transformer windings. At

turn on, the total equivalent capacitor discharges through the

MOSFET.

(3) As shown in the diagram, the MOSFET gate operating

current also flows through the current sensing resistor.

Whether an SMPS is current mode or voltage mode

controlled, or uses some form of non linear control, it

requires the protection afforded by current sensing

capabilities. Even though most current sensing is done using

a sensing resistor or a current transformer, there are

instances where a MOSFET is used by the SMPS to further

reduce current sensing losses. The Fairchild Power Switch

(FPS) switching element is a SenseFET. This minimises any

power losses in the sense resistor, which is integrated onto

the controller chip.

3.2 Current Sensing Waveform Noise After

Turn On

A leading edge spike is present on the current sense line

when the SMPS switching device turns on. It arises from

three causes, as shown in Figure 13: (1) reverse recovery

current; (2) charge/discharge current of the MOSFET shunt

capacitance; and (3) MOSFET gate operating current.

Vo

Vin

Vo

Vin

Rg

Rg

Control

IC

Vo

Vin

Control

IC

Rf

Rs

Rg

Cf

Cf

Control

IC

Rf

Rf

Rs

Cf

Reverse Recovery Current

Charge/Discharge Current of

the equvalent capacitor

MOSFET Gate Operating

Current

Figure 13. Current sensing waveform noise after turn on.

10

2002 Fairchild Semiconductor Corporation

AN4105

APPLICATION NOTE

3.3 Dealing With Leading Edge Noise

3.3.1 Burst Mode Operation

Among the measures taken to reduce leading edge noise, the

most commonly used technique is the RC filter. As shown in

Figure 14a the RC filter is effective against the noise, but it

has the disadvantage that it distorts the current sensing signal

so that accurate current sensing becomes difficult.

Furthermore, a large RC value may be difficult to implement

on an IC and may even require a bigger chip. The technique

of leading edge blanking, as presented in Figure 14b and

14c, overcomes the distortion disadvantage of the RC

technique and works as follows. Since the problem noise

arises just after turn on, if a circuit is inserted that ignores the

current sensing line for a fixed time just after turn on,

operation can continue normally regardless of the noise.

Whatever the details of the location and type of circuit used,

the basic idea is to maintain a minimum turn on time i.e.,

touse the shortest turn on time that cannot be terminated

once turn on starts. Duty ratio control with a minimum turn

on time is implemented through a non linear control method

having a very wide control range relative to a linear control.

The non linear control operates such that if load conditions

require a turn on time of 400ns when the minimum turn on

time is set at 500ns, then one switching cycle will turn on at

800ns. The next cycle will be missed, ensuring that the

average turn on time is 400ns. In this case every other cycle

is missed. This is pulse skipping. In this case the switching

frequency will be half that of a linearly controlled system,

thereby improving SMPS efficiency at light loads. The input

power is therefore minimised. The Fairchild KA34063 dc/dc

converter is an example of a non linear control IC.

The aforementioned method can be viewed as an example of

burst mode operation. Burst mode operation, by reducing the

switching frequency, is one of the most useful ways to

improve SMPS efficiency at light loads and to reduce the

standby input power of household appliances, etc. Note that

burst mode operation is not a burst oscillation (as in ringing

choke conversion circuits), which can bring about reliability

problems. There are mainly two types of true burst mode

operation: one type lowers the switching frequency equally.

The other switches at normal frequency for a fixed time and

stops the control IC operation for a large number of cycles.

Even though in the first method the control IC continues to

consume power, the output voltage ripple is minimized.

The second method can be a useful way to reduce the

minimum input power at standby (since obviously the

standby power is greatly reduced when the IC is stopped).

Indeed, it is often used in cell phones to reduce the dc/dc

converters power consumption in standby mode. However,

it has the disadvantage of a larger output voltage ripple.

Currently, Europe restricts a household appliances standby

input power to less than 5W, and in time it will be required

to be less than 3W. For such needs, burst mode operation

will be a powerful method to satisfy the requirement for

reduced standby input power.

11

2002 Fairchild Semiconductor Corporation

AN4105

APPLICATION NOTE

Rg

PW M

IC

MO S FE T

Rf

C u rre n t

S e n s in g

Cf

Rs

(a)

< N o ise elim inat ion u sing R C f ilter >

V ck

Vi

OSC

Vo

LEB

Ifb

V fb

Va

Vq

C fb

Vb

Ifb

V is

F e e d ba c k

C ir cu it

(b)

< In te rn al blo ck d iag ra m f or no ise elim inat ion u sing L E B >

V ck

Va

0

V fb

V is

0

Vb

Vq

0

0

(c) Noise elimination and waveforms in LEB

< N oise e lim ina tio n a nd w an efo rm s in LE B >

Figure 14. Leading edge blanking.

12

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4105

4. Flyback Converter Operation

4.1 Operation In Continuous Conduction Mode

(CCM)

Figure 15 shows a typical flyback converter. When the current

through the converters inductor is always greater than zero

within a switching cycle, the converter is said to operating in

the continuous conduction mode (CCM). Figure 16 shows the

waveforms of CCM operation, which operates as follows.

V i TON = nV O T OFF

nV O

T ON

D

------------ = --------------- = ------------Vi

T OFF

D1

The input and output currents become:

I i = DI Lm, AVG

I O = n ( 1 D )I Lm, AVG

4.1.1 For t0 ~ t1 = TON

At t0 the MOSFET turns on. Immediately before t0, the

inductor current was flowing through diode D, but when the

MOSFET turns on, D turns off thereby isolating the output

terminal from the input terminal. At MOSFET turn on, its

VDS goes to zero, hence VD becomes (Vo + Vi/n). During the

interval after MOSFET turn on (i.e., from t0 on), Vi is

applied to Lm, so ILm increases linearly with a slope as

shown by the following equation:

V

Slope = ------iLm

Hence the input and output powers are equal. An ideal

waveform is shown here because the effect of leakage

inductance has been ignored. In reality leakage inductance

will cause ringing.

ID

IO

IL m

IC

VD

VL m

Lm

V in

n:1

ID S

When the energy flow is examined, it is seen that the input

power source supplies energy to Lm while the MOSFET is on.

However, since the energy in Lm continues to increase while

the output terminal is isolated from the input terminal, it is Co

that has to supply the output current during this interval.

RO

VO

CO

V DS

Figure 15. A typical flyback converter.

V GS

ON

4.1.2 For t1 ~ t2 = TOFF

At t1 the MOSFET turns off. At the instant of turn off, the

inductor current that had been flowing through the MOSFET

starts to flow through diode D. When D turns on, VDS

becomes (Vi +nVo). During this interval the voltage nVo is

applied to Lm so that ILm decreases in a straight line with the

following slope:

nV O

Slope = ----------Lm

When the energy flow during this interval is examined, it is

seen that the inductor energy is delivered to the output. The

energy in Lm is reduced by the amount of energy it delivers

to the output. When the MOSFET turns on again, at t2, one

switching cycle will end.

OFF

T ON

T O FF

VDS

V i+ n V O

0

V Lm

Vi

0

B

nV 0

VD

V 0+ V i/ n

0

S lo p e = V i/ L m

S lp o e = n V O /L m

IL m

0

ID S

4.1.3 Relationship Between Input And Output

As shown in Figure 16, the colored areas A and B of the

waveform VLm (the voltage applied to the inductor) must be

equal because the average voltage of the inductor or

transformer in steady state is always zero. Therefore:

2002 Fairchild Semiconductor Corporation

IC

ID

IO

0

t0

t1

t2

t3

Figure 16. Flyback converter operating waveforms in

continuous current mode (CCM).

13

AN4105

APPLICATION NOTE

4.2 Discontinuous Conduction Mode (DCM)

The appearance of an interval in which the inductor current

becomes zero during a switching cycle marks flyback

converter operation as discontinuous conduction mode

(DCM). As shown in Figure 17, the voltage waveform

applied to the inductor, VLm, becomes more complex in

DCM. Hence, to avoid difficulties in computation TOFF is

not used. Instead, three input and output relationships of a

converter are derived by using TOFF * , the time when the

output rectifier diode is actually conducting.

V GS

ON

OFF

VT

= nV T*

i ON

O OFF

VO

T ON

D*

-------- = ------------------ = ---------------Vi

T* OFF

1 D*

Deriving the above equation again, using Io and the fact that

the input and output powers are equal, Vo is obtained as:

2

( V i T ON )

V O = ----------------------------------------------------------------IO

2 ----- L m ( T ON + T OFF ) + V i

n

The following equation represents the input power:

2

1

P IN = --- L m I Lm,(peak) fsw

2

VDS

V i+nV O

where fsw is the switching frequency.

Vi

0

VLm

Vi

4.3 Flyback Converter Design

V i+nV O

0

B

nV 0

4.3.1 Turns Ratio Considerations

VD

V O +V i/n

0

T OFF *

TON

Slope

Slpoe=V i/Lm

IL m

The turns ratio of an SMPSs flyback converter transformer

is an important variable. It affects the voltage and current

levels associated with the primary side switching device and

the secondary side rectifier, as well as the number of turns on

the transformer and the current through it. A frequently

discussed design concept suggests operating at maximum

duty ratio when the input voltage is a minimum. For

simplified calculations, here it is assumed that operating

conditions change as listed immediately below.

- Vac input: 85 ~ 265Vac

VO

T OFF

Slope=nV O /L m

0

ID S

- Vdc (rectified voltage): 100 ~ 400Vdc

ID

IC

0

IO

0

t0

t1

t2

t3

Figure 17. Flyback converter operating waveforms in

discontinuous current mode (DCM).

The boundary condition between DCM and CCM is:

Vi

Ii + I O = ---------- T ON

2Lm

The following input output relationship in DCM is derived

by using the fact that the colored areas A and B of VLm in

Figure 17 must always be equal because, in steady state, the

average inductor (or transformer) voltage is always zero.

14

- Output voltage: 50Vdc

- Inductor current: Continuous conduction mode (CCM)

operation assumed.

The input power taken by the dc source is the product of the

dc voltage and average input current. Using a wide duty

cycle to deliver equal average current reduces efficiency.

A narrow duty cycle increases the effective current on the

primary side, increasing the operating temperature of the

primary winding and the MOSFET. Also, it is best to decide

on a turns ratio, n, based on the device used. If the voltage on

the primary side MOSFET is relatively low (e.g., 600V),

make n small; if it is on the high side (e.g., 800V), make n

large. As the value of n increases, the primary side switching

device current and the secondary side rectifier diode voltage

decreases Hence, with high output voltage and multiple

secondary side outputs, it is advantageous to increase n.

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4105

4.3.2 Deciding On The Operating Current Mode

As discussed in Sections 4.1 and 4.2, there are two different

operating current modes possible in a flyback converter: the

continuous conduction mode (CCM); and the discontinuous

conduction mode (DCM). Here the advantages and

disadvantages of each are reviewed, to help the designer

make a proper choice between them.

4.3.2.1 Characteristics Of The Discontinuous

Conduction Mode

In a flyback converter design, if discontinuous conduction

occurs just at minimum input voltage and maximum output

power, then discontinuous conduction must be considered to

be the case for all input conditions. The flyback converters

input power in discontinuous conduction mode can be

expressed as:

2

1

P I = --- L m I P fsw

2

Regardless of any changes in input voltage, the power

equation indicates that the input current is limited by the

peak value of the current flowing through the MOSFET in

the transformer primary. A Fairchild Power Switch (FPS)

has an integrated overcurrent protection feature (see Section

2.1, above). This feature does not require external

components and operates across the range of input current.

However, the fixed operating current of DCM, tends

somewhat to offset the effect of the larger effective primary

2002 Fairchild Semiconductor Corporation

side current. The gain is at the low frequency end where core

loss is not a problem since only a minimum number of turns

need be wound. Also, turn on loss is not a serious problem

due to the low input current. Other losses such as eddy

current, skin effect, proximity effect, etc., are not significant.

A more clearly defined advantage of DCM operation is that

it permits the use of a slow and hence, low cost secondary

rectifier diode. In contrast to the continuous conduction

mode, in the discontinuous conduction mode the effective

current is higher, requiring the use of heavier wire and hence

thicker coils. Therefore DCM does not bring an advantage

insofar as transformer construction is concerned. Moreover,

DCM causes the MOSFET operating temperature to increase

because of the large effective primary side current, as was

described above (Section 4.3.1).

4.3.2.2 Characteristics Of The

Continuous Conduction Mode

Since the coils effective current is decreased CCM brings

the advantage of lighter wire. The smaller effective current

also reduces MOSFET heating. This is a definite advantage

for average input current. On the other hand, CCM operation

brings with it a need to consider the rectifier diodes reverse

recovery current. Depending on the diodes reverse recovery

time (trr), the reverse recovery current may stress the diode

and increase the loss at its end terminals. It is therefore

necessary to use a diode with the minimum trr possible

within the allowable cost range.

15

AN4105

APPLICATION NOTE

V i =10 0V

V i= 400 V

V DS

M e ri t s & de m e ri ts

n V O =6 7 V

V DS

n V O =6 7 V

- V o ltag e

V i=1 0 0V

0

V i=4 0 0V

VD

VD

V i/n =7 5 V

V O= 50 V

V i/n =2 6 7 V

V D S=1 67V

V D =1 25 V

V O= 50 V

ap p li e d to sw itch d ev ic e is

lo w

-E ffect iv e cu rren t in sw itc h i n g d ev ice

an d p rim ary w in d in g is lo w

-V o ltag e ap p li ed to rect ifi er d io d e is

h ig h

-O u tp u t v o lta g e rip p l e is sm al l

-C o n tro l m u st b e d o n e th ro u g h sh o rt

tu rn - o n tim e

V D S =46 7V

V D =31 7V

V DS

n V O =1 0 0 V

n:1

V DS

n V O =1 0 0 V

VLm

V i=1 0 0V

V i=4 0 0V

VD

Vi

VDS

0

VD

2

VD

- Int e rm e di a te D e si gn M e t hod

V i/n =5 0 V

V i/n =2 0 0 V

V O= 50 V

V D S=2 00V

V O= 50 V

0

V D =1 00 V

V D S =50 0V

V D =25 0V

V DS

V DS

n V O =1 5 0 V

n V O =1 5 0 V

V i=1 0 0V

V i=4 0 0V

VD

VD

V i/n =3 3 V

V i/n =1 3 3 V

V O= 50 V

V D S=2 50V

V D = 83V

V O= 50 V

V D S =55 0V

- V o ltag e

ap p li e d to sw itch d ev ic e is

h ig h

-E ffect iv e cu rren t in sw itc h i n g d ev ice

an d p rim ary w in d in g is h ig h

-V o ltag e ap p li ed to rect ifi er d io d e is

lo w

-O u tp u t v o lta g e rip p l e is larg e l

-C o n tro l m u st

tu rn - o n tim e

be

done

th ro u g h

lo n g

V D =18 3V

Figure 18. The current and voltage ratings required on the primary side switching device and the secondary side

rectifier diode depend on the turns ratio (n) selected.

4.3.2.3 Designers Choice

As is clear from the above discussion, DCM operation can

be advantageous, in terms of cost and efficiency, if the input

is small and it is required to precisely control the input power

through the primary side switch (MOSFET) current.

On the other hand, for large inputs and where switching turn

16

on loss could be a major problem, a CCM design would be

more advantageous. In conclusion, therefore, the system

designer must decide between the two modes according to

which mode best fits the characteristics of the system being

designed.

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4105

5. The Transformer

5.1 Why a Transformer Is Needed

There are three reasons for needing a transformer in a power

conversion circuit. The first reason is safety. A transformer

affords electrical isolation between the primary and

secondary sides, as shown in Figure 19a. In addition, a true

ground on the output side helps prevent electric shock. The

second reason is for voltage conversion. For example, if a

dc/dc converter (such as the buck converter shown in Figure

19b) switching at 50kHz is used to obtain 5V from 100V.

The duty cycle would only be 5%. Using a 50kHz switching

frequency, the control circuit may have only about 1s to

act, which is not an easy task. Even if this were possible, the

internal voltage and current for each element would be very

large reducing efficiency. The problem is aggravated at high

output current. In the above example, using a transformer to

AC220V

DC

& Rectifier

Output

lower the voltage to 10V would then allowing an on time of

about 10s. This is an advantageous strategy for lowering

cost and raising efficiency. The third reason to use a

transformer has to do with high voltages and voltage fluctuations. For example, even though all control for a 1000V

supply is done at the 5V power source on the GND side, a

transformer is necessary if power is needed for current

sensing at the 1000V output terminal or for other control. If

the isolation voltage between the transformer windings is

sufficient, a 1000V potential difference can be safely

maintained between the primary and secondary windings

and power can be delivered. Further, a transformer is also

required when the power GND has a sudden potential

fluctuation as in a half bridge converter, gate drive power

source.

GND

Vin=100V

100V

Vo=5V

---->

Electric Shock

short when touched Safe to touch

Duty 5%

---->

5V

50kHz --> Ton=1uS

(a) For safty

Safety

5V

Vo=5V

Vin=100V

10:1

1000V

5V

100V

--> 10V

-->

Duty 50%

-->

5V

50kHz -> Ton=10uS

(b) For voltage change

(c) For potential fluctuation

Figure 19. Why a transformer is needed.

5.2 The Ideal Transformer

The transformer is a device that uses inductive coupling

between its windings to deliver power or signals from one

winding to the another. This is usually from the primary

winding to the secondary winding. The voltages across the

windings can be raised or lowered with respect to each other,

and, if necessary, the primary and secondary sides can be

isolated from each other. Figure 20 shows an ideal

transformer, a simplistic model useful in describing the

transformer concept. An ideal transformer which is actually

a fictional concept must satisfy the following three

2002 Fairchild Semiconductor Corporation

conditions:

1.The coupling coefficient between the windings

is unity (i.e., the leakage flux is zero);

2.The coil loss is zero (the device has no losses).

3.The inductance of each coil is infinite.

17

AN4105

APPLICATION NOTE

IP

IS

I d e a l T ra n sfo rm e r

VP

VS

NP : N

VP : VS =N

VP

I P*

IP

: N

IS

Lm

VS

IP : IS = N S : N P

Figure 20. Ideal transformer.

The input to output voltage ratio of an ideal transformer is

directly proportional to the turns ratio. This is the ratio of the

number of turns on the primary winding to the number of

turns on the secondary. The polarity is represented schematically by the placement of a dot on each winding. Since n =

Vp/Vs, and an ideal transformer has no loss, the current ratio

is inversely proportional to the turns ratio. The current direction is such that it enters on one side and leaves at another.

Thus the sum of all the nI that flow into the dot is zero. The

dot, indicating the winding polarity, is placed to make the

flux direction in the transformer core uniform when current

flows into the dot. Furthermore, in the case of an ideal transformer, if the path on the secondary side windings is opened,

there is no secondary current flow, and the current on the primary side also goes to zero.

5.3 The Real Transformer

Significant differences exist between an ideal transformer

and a real one. In a real transformer:

1. The coupling coefficient between each coil is finite, and

when a gap is placed in the core as is done in many power

transformers, the coupling coefficient becomes still smaller

(i.e., there is leakage flux);

2. There are losses, such as iron (hysteresis) loss, eddy current

loss, coil resistance loss, etc.; and,

3. The inductance of each coil is finite. When a gap is

placed in the core the inductance becomes still smaller.

NP : N S

V P : V S =N P : N S

IP * : I S = N S : N P

Figure 21. A model of an actual transformer showing the

magnetizing inductance Lm, which accounts for energy

storage.

Rp

Llp

Ideal Transformer

Rm

Lm

Lls

Rs

- Rp:Primary side winding resistance

- Rs:Secondary side winding resistance

- Llp:Primary side leakage inductance

- Lls:Secondary side leakage inductance

- Lm:Magnetizing inductance

- Rm:Transform er core loss resistance

Figure 22. A more complete equivalent circuit of an

actual transformer, showing inductances and loss

resistances.

In a real transformer, should the secondary side be opened

current would continue to flow in the primary (as in 3,

above). So, while energy cannot be stored in the ideal

transformer, it is stored in a real transformer. The so-called

magnetizing inductance accounts for this energy storage

phenomenon. The circuit of Figure 21 is a simplistic view of

an actual transformer and shows the magnetizing inductance.

Figure 22 presents a more complete equivalent circuit of a

real transformer, showing inductances and loss resistances

18

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4105

6. Transformer Design

6.1 Core Selection

The maximum power that a transformer core can deliver and

the maximum energy a transformer inductor can store

depends on the shape and size of the core. In general, as the

effective cross sectional area (Ae) increases, more power can

be delivered. Also, as the window area (Aw) on which the

coils are wound increases, more and thicker windings can be

used, allowing a further increase in the power that can be

delivered. The product of Aw and Ae is called the area

product, AP, and the maximum power a transformer can

deliver is proportional to an exponential power of AP.

Indeed, recent transformer theory shows designs depending

almost entirely on AP. In the broader view, a flyback

converter transformer can be viewed as a coupled inductor,

so it's common to design a flyback transformer using

inductor design methods. The two equations below, (a) and

(b), represent two ways to calculate AP. Equation (a) below,

is a method based on whether or not the core is saturated, is

appropriate at low operating frequencies. Equation (b),

limited by core loss, is appropriate at high frequencies. For

any given design, it is necessary to calculate AP using both

equations, and the equation that gives the higher value is the

one that must be considered correct. Equation (a) assumes

that all losses are wire losses and ignores the core (iron) loss.

4 1.31

LIP I RMS 10

AP = -------------------------------

420KB MAX

[ cm ]

a)

L = Inductance of Transformer

Ip = Operating peak current

Bmax = MAximum operating flux density

Irms = RMS current

L and BMAX are in Henries and Tesla units, respectively, and

K is listed in Table 1, below. From the above equation the

current density (J) per unit area of wire is obtained from the

current by the relationship below, which assumes that the

temperature of the inductors hot spot is 30C above

ambient.

J 30 = 420 AP

0.24

[ A cm ]

At any operating frequency high enough so that the core

losses become large, the following equation should be used.

Specifically, it assumes that the total transformer losses are

split equally (50/50) between the wire and the core.

2002 Fairchild Semiconductor Corporation

4 1.58

LI I

0.66

2

m RMS 10

(K f

+ K ( f )2 )

[ cm ]

AP = ------------------------------------------

H SW

E sw

130K

b)

L = Inductance of Transformer

Ip = Operating peak current

Irms = RMS current

In equation (b), KH is the hysteresis coefficient (typically 4 x

10-5 for ferrite cores) and KE is the eddy current coefficient

(typically 4 x 10-10 for ferrite cores).

The current density relationship here, represented by the

equation for J30, below, assumes a hot spot temperature of

15C above ambient, with the iron loss adding on an

additional 15C (again, a total of 30C above ambient).

J 30 = 297AP

0.24

[ A cm ]

The parameter K in equation (a) is the product of the window

utilization factor KU with the primary area factor KP.

(See Table 1.) KU is the ratio of the cross sectional area of

the windings copper to the entire window area, and it is

significant in setting the isolation between the primary and

secondary sides. Because it is related to the transformer

shape and winding method, the designer should know the

value of KU for the transformer usually used.

The value of KU can vary greatly, depending particularly on

how closely the isolation safety standards (re isolation) are

followed; the KU of Table 1 assumes a general bobbin is

used. KP is the ratio of the area of the primary winding to

that of the total winding. In Table 1, it is unity for the

inductors because a buck boost inductor has no secondary

windings. For the flyback transformer coupled inductor, KP

is usually 0.5, as Table 1 shows; such an inductor has the

highest efficiency when the primary and secondary winding

areas are equal. When there are more secondary windings,

however, the KP for a flyback transformer coupled inductor

can be lower than 0.5. Note that the ease and speed of

obtaining an accurate AP from equations (a) and (b) depends

on the designer's experience. A reasonably good knowledge

of the probable values of the three parameters KU, KP, and J

for the flyback transformer being designed will reduce the

number of trial and error attempts necessary.

19

AN4105

APPLICATION NOTE

Table 1. KU, KP, and K

KU

KP

K = KU KP

CCM Buck, Boost Inductor

0.7

1.0

0.7

DCM Buck, Boost Inductor

0.7

1.0

0.7

CCM Flyback Transformer

0.4

0.5

0.2

DCM Flyback Transformer

0.4

0.5

0.2

6.2 Determining The Number of Turns

6.4 Determining The Gap

Although the equation for the minimum number of flyback

transformer turns can be determined using applied voltage

and maximum turn on time, the equations used here are

derived from the relationship between L and IP.

For an AP determined from equation (a), above, calculate

NMIN using the following equations:

It is not easy to precisely calculate the required gap.

However, the gap can be calculated from the following

equation. It is based on the fringing effect of the surrounding

flux. Note that the calculated value of L is usually larger than

required.

LI P

4

N MIN = ---------------------- 10

B MAX A C

L = Inductance of Transformer

Ip = Operating peak current

Bmax = Maximum operating flux density

Ae = Effective cross-sectional area of core

For an AP determined from equation (b), above, calculate

NMIN using the following equations:

LI m

4

N MIN = ------------------- 10

B m AC

L = Inductance of Transformer

Ip = Operating peak current

Bmax = Maximum operating flux density

Ae = Effective cross-sectional area of core

6.3 The Windings

The cross sectional area of the winding must be obtained

from the calculated effective current and the current density

(from the appropriate equation above), factoring in the

number of turns (as determined from a calculation of

NMIN). If eddy current loss is not a serious problem simply

divide the effective current by the current density, thereby

determining the coil cross sectional area.

Be aware, however, that as the coil becomes thicker, the

problem of eddy current loss will arise. Using twisted thin

coil strands (Litz wire), instead of a single heavy wire, can

reduce the eddy current loss, but KU will become smaller.

20

uO ur N AC 2

- 10 [ cm ]

I g = --------------------------L

Uo = Permeability of free space

Ur = Relative permeability

Therefore, the gap must be changed to obtain the required

value of L.

References

1. Transformer and Inductor Design Handbook. 2nd ed.

Col. Wm. T. McLyman. Marcel Dekker, Inc., 1988.

2. Switch Mode Power Supply Handbook. Keith H.

Billings. McGraw-Hill, Inc., 1989.

KA1H0280RB, KA1M0280RB, KA1H0380RB, KA1M0380RB,

KA1L0380RB, KA1L0380B, KA1H0680B, KA1M0680B,

KA1H0680RFB, KA1M0680RB, KA1M0880B, KA1L0880B,

KA1M0880BF, KA1M0880D, KA2S0680B, KA2S0880B,

KA3S0680RB, KA3S0680RFB, KA3S0880RB, KA3S0880RFB,

KA1H0165RN, KA1H0165R, KA1H0265R, KA1M0265R,

KA1H0365R, KA1M0365R, KA1L0365R, KA1H0565R,

KA1M0565R, KA1M0765RC, KA1M0765R, KA1M0965R,

KA2S0765, KA2S0965, KA2S09655, KA2S1265, KA3S0765R,

KA3S0765RF, KA3S0965R, KA3S0965RF, KA3S1265R,

KA3S1265RF, KA5H0280R, KA5M0280R, KA5H0380R,

KA5M0380R, KA5L0380R, KA5P0680C, KA5H0165R,

KA5M0165R, KA5L0165R, KA5H0165RV, KA5M0165RV,

KA5L0165RV, KA5M0165RI, KA5L0165RI, KA5H0165RN,

KA5M0165RN, KA5L0165RN, KA5H0165RVN,

KA5M0165RVN, KA5L0165RVN, KA5H02659RN,

KA5M02659RN, KA5H0265RC, KA5M0265R, KA5L0265R,

KA5M0365RN, KA5L0365RN, KA5H0365R, KA5M0365R,

KA5L0365R, KA5M0765RQC, KA5M0965Q, KA5S0765C,

KA5S09654QT, KA5S0965, KA5S12656, KA5S1265,

KA5Q0740RT, KA5Q0945RT, KA5Q0765RT, KA5Q12656RT,

KA5Q1265RF, KA5Q1565RF, FSDH0165, FSDH565,

FS6M07652RTC, FS6M12653RTC, FS6S0765RCB,

FS6S0965RT, FS6S0965RC, FS6S1265RB, FS6S1565RB,

FS7M0880, FS8S0765RC

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

2002 Fairchild Semiconductor Corporation

AN4105

21

AN4105

APPLICATION NOTE

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER

DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICODUCTOR

CORPORATION. As used herein:

1. Life support devices or systems are devices or systems

2. A critical component is any component of a life support

which (a) are intended for surgical implant into the body, or

device or system whose failure to perform can be

(b) support or sustain life, or (c) whose failure to per-form

reasonably expected to cause the failure of the life support

when properly used in accordance with instructions for use

device or system, or to affect its safety or effectiveness.

provided in the labeling can be reasonably expected to

result in significant injury to the user.

www.fairchildsemi.com

3/19/04 0.0m 002

2002 Fairchild Semiconductor Corporation

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

You might also like

- Inside The Power SupplyDocument41 pagesInside The Power SupplyBright UzzalNo ratings yet

- Texas Instruments. Testing A Form of SMPSDocument7 pagesTexas Instruments. Testing A Form of SMPSRoger FairchildNo ratings yet

- Electrodes/ADS1298 Interface: ResolvedDocument10 pagesElectrodes/ADS1298 Interface: ResolvedSummer MamunNo ratings yet

- HGLRC F4 V5PRO Manual - High-Performance All-in-One Racing Drone FCDocument12 pagesHGLRC F4 V5PRO Manual - High-Performance All-in-One Racing Drone FCGobardhan Pudasaini100% (1)

- Elecs 1 - Diode CircuitsDocument103 pagesElecs 1 - Diode CircuitsAnthony CortezNo ratings yet

- Switch Mode Power Supply Basics TutorialDocument16 pagesSwitch Mode Power Supply Basics TutorialDavidNo ratings yet

- Gazi Üniversitesi Mühendislik Fakültesi Elektrik Elektronik Mühendisliği'nde Resonant KonvertörlerDocument41 pagesGazi Üniversitesi Mühendislik Fakültesi Elektrik Elektronik Mühendisliği'nde Resonant Konvertörlerkazemy_gNo ratings yet

- SMPS Test SeduleDocument6 pagesSMPS Test SeduledeeruNo ratings yet

- Crius AIOP V2 0 Guide For MegaPirateNG Ver 1 0Document43 pagesCrius AIOP V2 0 Guide For MegaPirateNG Ver 1 0FlyeerNo ratings yet

- H2 Production Detailed ReviewDocument6 pagesH2 Production Detailed ReviewJaydeep PatelNo ratings yet

- Multiwii Software GUIDEDocument10 pagesMultiwii Software GUIDEHiroshi TakeshiNo ratings yet

- The Quad Copter ControllerDocument11 pagesThe Quad Copter ControllerAdam MahmoodNo ratings yet

- Simple Distillation of Cyclohexane and Toluene MixtureDocument18 pagesSimple Distillation of Cyclohexane and Toluene MixtureAnonymous xfzNyyi4No ratings yet

- Testing The PIC Microcontroller (Pic 16F877A)Document6 pagesTesting The PIC Microcontroller (Pic 16F877A)Matt ImriNo ratings yet

- Switch-Mode Power Supplies - SPICE Simulations and Practical Designs - EE Times3 PDFDocument7 pagesSwitch-Mode Power Supplies - SPICE Simulations and Practical Designs - EE Times3 PDFVIJAYPUTRA0% (1)

- Flasher 5: Programming Tool For Serial in Circuit Programming of Microcontrollers With On-Chip FlashDocument16 pagesFlasher 5: Programming Tool For Serial in Circuit Programming of Microcontrollers With On-Chip FlashAjay AroraNo ratings yet

- 12 Steps Design SMPS TransformersDocument11 pages12 Steps Design SMPS TransformersRnDES1 CMLNo ratings yet

- ZVS Full BridgeDocument20 pagesZVS Full Bridgejameschall1No ratings yet

- Syngas Preparation: CH4 + H2 O CO + 3H2Document4 pagesSyngas Preparation: CH4 + H2 O CO + 3H2Gopal AgarwalNo ratings yet

- Physics Grade 10 Physics Ch3 Motion in One DimensionDocument68 pagesPhysics Grade 10 Physics Ch3 Motion in One DimensionozasviNo ratings yet

- Led CircuitsDocument18 pagesLed CircuitsDedan Kimathi100% (1)

- WWW Mikroe Com Chapters View 69 Chapter 6 ExamplesDocument67 pagesWWW Mikroe Com Chapters View 69 Chapter 6 Examplesramnag4100% (1)

- PIC+l293d DocumentDocument5 pagesPIC+l293d Documentmadduanil100% (1)

- LED ChaserDocument7 pagesLED ChaserMegan Skinner100% (1)

- Open Source Frequency Counter DIY Kit 10Hz-250MHzDocument10 pagesOpen Source Frequency Counter DIY Kit 10Hz-250MHzBruno Santos de Miranda100% (1)

- Aerosemi: Features ApplicationsDocument9 pagesAerosemi: Features Applicationsttnaing100% (1)

- How A Power Supply WorksDocument3 pagesHow A Power Supply Worksperkinsc305No ratings yet

- Basic Connecting Microcontroller Power Clock ResetDocument6 pagesBasic Connecting Microcontroller Power Clock ResetJuan CarlOs Culqui Melendez100% (1)

- 12v To 18v ConverterDocument7 pages12v To 18v ConverterLuis Paulo100% (1)

- ANCRCT-4 Precision Rectifier CircuitDocument1 pageANCRCT-4 Precision Rectifier Circuitramesh_br85100% (1)

- Generate PWM Signals Using a PIC 16F84 MicrocontrollerDocument5 pagesGenerate PWM Signals Using a PIC 16F84 Microcontrollersaadettin100% (2)

- The 8051 Microcontroller and Embedded Systems: Motor Control: Relay, PWM, DC and Stepper MotorsDocument51 pagesThe 8051 Microcontroller and Embedded Systems: Motor Control: Relay, PWM, DC and Stepper MotorsAmAnDeepSingh100% (1)

- DIY Short Circuit Overcurrent Protection PDFDocument6 pagesDIY Short Circuit Overcurrent Protection PDFsarath39438No ratings yet

- Intelligent Street Light Control While Obstacle PassingDocument32 pagesIntelligent Street Light Control While Obstacle Passingprashanthi_komatireddyNo ratings yet

- Practical PIC ProjectsDocument14 pagesPractical PIC ProjectsArdhika Dhennis Putra Ananda100% (1)

- Micro Smart ManualDocument455 pagesMicro Smart ManualJuan Carlos100% (1)

- So Do On AP LiOa (Nen)Document1 pageSo Do On AP LiOa (Nen)Anhtu Pham100% (1)

- What Is A Switched-Mode Power Supply (SMPS) - Definition From Techopedia PDFDocument1 pageWhat Is A Switched-Mode Power Supply (SMPS) - Definition From Techopedia PDFBright Tendai ChingwenaNo ratings yet

- SCRDocument4 pagesSCRJoshua Amiel javines100% (1)

- Understanding Modern ElectronicsDocument3 pagesUnderstanding Modern ElectronicsNarayana Mugalur100% (1)

- Osd Oscilloscope SchematicDocument1 pageOsd Oscilloscope SchematicSebastian Costa100% (1)

- Guia Basica de Ejercicios-ProtonDocument59 pagesGuia Basica de Ejercicios-ProtonFatality Joseph100% (1)

- DC Motor Bidirectional Speed Control Using PWM PDFDocument5 pagesDC Motor Bidirectional Speed Control Using PWM PDFM Rameez Ur Rehman100% (1)

- P27-Smoke Alarm CircuitDocument2 pagesP27-Smoke Alarm CircuitDenis Pt100% (1)

- PWMDocument1 pagePWMSharungomesNo ratings yet

- Review of a simple adjustable power supply using linear and switching componentsDocument4 pagesReview of a simple adjustable power supply using linear and switching componentsramesh ranjitNo ratings yet

- Report On Power SupplyDocument16 pagesReport On Power SupplyKshitij GuptaNo ratings yet

- Application Note AN-6026: Design of Power Factor Correction Circuit Using FAN7529Document23 pagesApplication Note AN-6026: Design of Power Factor Correction Circuit Using FAN7529miloud1911No ratings yet

- Wireless World 1948 06Document102 pagesWireless World 1948 06Jan Pran100% (1)

- DIY Electronics (HK) LTD PO Box 88458, Sham Shui Po, Hong KongDocument17 pagesDIY Electronics (HK) LTD PO Box 88458, Sham Shui Po, Hong Kongrajudp100% (1)

- Fonte SEMP LE4050Document4 pagesFonte SEMP LE4050Rafael MarquesNo ratings yet

- Introduction To The PIC32 - The Basics, Getting Started, IO Ports and The First ProgramDocument17 pagesIntroduction To The PIC32 - The Basics, Getting Started, IO Ports and The First Programtahmidmc100% (1)

- Design Strategy For A 3-Phase Variable Frequency Drive (VFD) PDFDocument37 pagesDesign Strategy For A 3-Phase Variable Frequency Drive (VFD) PDFSamuel Mushaka100% (1)

- Application Note AN4105Document23 pagesApplication Note AN4105Fady HachemNo ratings yet

- AN-4102: Colour TV Receiver SMPSDocument16 pagesAN-4102: Colour TV Receiver SMPSshri.bhairavkar6977No ratings yet

- KA3525 IC UpdatedDocument10 pagesKA3525 IC UpdatedKarthik DmNo ratings yet

- AN4102 (Uso 3S0680RF)Document20 pagesAN4102 (Uso 3S0680RF)Cintya CardozoNo ratings yet

- Application Note AN-6027: Design of Power Factor Correction Circuit Using FAN7530Document16 pagesApplication Note AN-6027: Design of Power Factor Correction Circuit Using FAN7530Malanie Sriya De SilvaNo ratings yet

- An 6026Document23 pagesAn 6026Иван АлексиевNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- En 1996 08Document116 pagesEn 1996 08atomo33No ratings yet

- WWW - Jdwx.info: PSIV840C01B HANARO3 - 26HDDocument2 pagesWWW - Jdwx.info: PSIV840C01B HANARO3 - 26HDatomo33100% (1)

- D26W931 D32W931 LC32W053 LC42H053+service+manualDocument188 pagesD26W931 D32W931 LC32W053 LC42H053+service+manualNilton NevesNo ratings yet

- 715G5193P01000002HDocument2 pages715G5193P01000002Hatomo33100% (2)

- Hisense FA y LED DriveDocument2 pagesHisense FA y LED Driveatomo33No ratings yet

- Basic Electronic & Transistor Circuits PDFDocument54 pagesBasic Electronic & Transistor Circuits PDFSandeep GoyalNo ratings yet

- 12V Power Supply SchematicDocument1 page12V Power Supply Schematicatomo33100% (2)

- Boston Soudware Xs2.1 Ice3b0365j Ir2153Document21 pagesBoston Soudware Xs2.1 Ice3b0365j Ir2153atomo33No ratings yet

- Genesis b200 Stealth SCH (Audio-home-Theater)Document17 pagesGenesis b200 Stealth SCH (Audio-home-Theater)atomo33No ratings yet

- Safety and Operation Manual for Side-by-Side RefrigeratorDocument71 pagesSafety and Operation Manual for Side-by-Side Refrigeratoratomo33No ratings yet

- Aoc 2436saDocument45 pagesAoc 2436saatomo33100% (1)

- 13101715433434Document1 page13101715433434atomo33100% (3)

- Service Guide: Colour TelevisionDocument43 pagesService Guide: Colour TelevisiontiganiadaNo ratings yet

- Proview Monitor LCDDocument87 pagesProview Monitor LCDatomo33No ratings yet

- WP TransformerlessUPS PDFDocument12 pagesWP TransformerlessUPS PDFatomo33No ratings yet

- w2253v PFVDocument24 pagesw2253v PFVatomo33No ratings yet

- Elenberg ltv-2602Document36 pagesElenberg ltv-2602danielradu27No ratings yet

- Schematics for a PCI Power Supply (LE3252iDocument1 pageSchematics for a PCI Power Supply (LE3252iatomo33100% (1)

- Esq Power Vision T0403701Document1 pageEsq Power Vision T0403701atomo33No ratings yet

- KA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)Document10 pagesKA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)vetchboyNo ratings yet

- Comprehensible Background On Progessive VideoDocument6 pagesComprehensible Background On Progessive Videoatomo33No ratings yet

- 1162858918Document1 page1162858918atomo33100% (1)

- Plecs Tl431Document11 pagesPlecs Tl431khsniper100% (1)

- Схема Ups Powercom Eaton Bnt 600apDocument1 pageСхема Ups Powercom Eaton Bnt 600apatomo33100% (4)

- Computer-Generated Circuit DiagramDocument1 pageComputer-Generated Circuit Diagramatomo33No ratings yet

- Dca55t PDFDocument3 pagesDca55t PDFatomo33No ratings yet

- 666 1 PDFDocument1 page666 1 PDFatomo33100% (1)

- Delta Adp-90sb BBDocument1 pageDelta Adp-90sb BBatomo33100% (1)

- Tg0003en Ed01 ErmaDocument16 pagesTg0003en Ed01 ErmaEduardo Pereira da SilvaNo ratings yet

- Technical Assessment - Sample Questions: Correct Answer: 1Document5 pagesTechnical Assessment - Sample Questions: Correct Answer: 1Shruti PNo ratings yet

- Air Liquide BS 50-3-2,5Document1 pageAir Liquide BS 50-3-2,5kuraimundNo ratings yet

- NorsokDocument133 pagesNorsokNuzuliana EnuzNo ratings yet

- 3 28 19 NtapDocument199 pages3 28 19 Ntapfikri fikriNo ratings yet

- GHS - Liquid (KOH Liquid)Document12 pagesGHS - Liquid (KOH Liquid)Yeniffer Geraldine guerra quispeNo ratings yet

- Mixers Towable Concrete Essick EC42S Rev 8 Manual DataId 18822 Version 1Document84 pagesMixers Towable Concrete Essick EC42S Rev 8 Manual DataId 18822 Version 1Masayu MYusoffNo ratings yet

- FS120-FS200-FS300-FS350-FS400-FS450-FR350-FR450 Service ManualDocument63 pagesFS120-FS200-FS300-FS350-FS400-FS450-FR350-FR450 Service Manualnik_nicholson_189% (18)

- D. Marriot - The Development of High-Performance Post-Tensioned Rocking Systems For The Seismic Design of StructuresDocument556 pagesD. Marriot - The Development of High-Performance Post-Tensioned Rocking Systems For The Seismic Design of Structuresedicson1aNo ratings yet

- Breathing Air System Performance QualificationDocument11 pagesBreathing Air System Performance QualificationCHALLA ANITHA100% (1)

- Pattern MatchingDocument58 pagesPattern Matchingamitavaghosh1No ratings yet

- Civil Engineering Laboratory Uitm Pahang, Kampus Jengka Highway Engineering ECG344 Open-Ended Lab OCTOBER 2020 - JANUARY 2021Document3 pagesCivil Engineering Laboratory Uitm Pahang, Kampus Jengka Highway Engineering ECG344 Open-Ended Lab OCTOBER 2020 - JANUARY 2021Adli Amin AmzukiNo ratings yet

- LucentDocument14 pagesLucentDaniel ManoleNo ratings yet

- Microsoft Word - Dangerous Goods Declaration PDFDocument1 pageMicrosoft Word - Dangerous Goods Declaration PDFAlfian AnasNo ratings yet

- Inspected by QCP Approval 1-APC 1 - APC 2 - DAR 2 - DAR Al-Handeseh 3 - Negemco 4 - Vendor 5 - Third PartyDocument4 pagesInspected by QCP Approval 1-APC 1 - APC 2 - DAR 2 - DAR Al-Handeseh 3 - Negemco 4 - Vendor 5 - Third PartyAhmad DagamsehNo ratings yet

- Felsic 105 Tfrs v4Document12 pagesFelsic 105 Tfrs v4mohammad reza aghatiNo ratings yet

- Telsinex Installation Guide Ver2.0Document46 pagesTelsinex Installation Guide Ver2.0Ludgério PedroNo ratings yet

- UM4730 Integration GuideDocument0 pagesUM4730 Integration Guidenarse8488No ratings yet

- Vectron+1-6 300713 en 1.6Document24 pagesVectron+1-6 300713 en 1.6kikokadolaNo ratings yet

- Kick Off Meeting: Post Tensioned I-BeamDocument29 pagesKick Off Meeting: Post Tensioned I-BeamSaddam TamimiNo ratings yet

- Power System Harmonics Causes and Effects PDFDocument8 pagesPower System Harmonics Causes and Effects PDFRamon DrakeNo ratings yet

- A) Flickering B) Interleaving C) Clipping D) InterlacingDocument45 pagesA) Flickering B) Interleaving C) Clipping D) InterlacingJass GillNo ratings yet

- OS X ShortcutsDocument19 pagesOS X Shortcutsia_moheetNo ratings yet

- ARM Processor CoreDocument34 pagesARM Processor CorevarshaksNo ratings yet

- FEMA 440 equivalent linearization pushover analysisDocument2 pagesFEMA 440 equivalent linearization pushover analysisAdam JrNo ratings yet

- Charles Correa 1Document21 pagesCharles Correa 1NupurAgrawalNo ratings yet

- Study of Tig WeldingDocument11 pagesStudy of Tig WeldingChandan Srivastava100% (1)

- Concrete Caissons For 2BMA - Large Scale Test of Design and Material 2019Document154 pagesConcrete Caissons For 2BMA - Large Scale Test of Design and Material 2019hjdNo ratings yet

- SolaMAXSERIES REV5 PDFDocument2 pagesSolaMAXSERIES REV5 PDFxander1982No ratings yet

- Top Plate - Qad-28 Sample Inspection ReportDocument3 pagesTop Plate - Qad-28 Sample Inspection ReportazadNo ratings yet