Professional Documents

Culture Documents

Adc 0809

Uploaded by

Carbon Nano TubeOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Adc 0809

Uploaded by

Carbon Nano TubeCopyright:

Available Formats

ADC0808/ADC0809

8-Bit P Compatible A/D Converters with 8-Channel

Multiplexer

General Description

Features

The ADC0808, ADC0809 data acquisition component is a

monolithic CMOS device with an 8-bit analog-to-digital converter, 8-channel multiplexer and microprocessor compatible

control logic. The 8-bit A/D converter uses successive approximation as the conversion technique. The converter features a high impedance chopper stabilized comparator, a

256R voltage divider with analog switch tree and a successive approximation register. The 8-channel multiplexer can

directly access any of 8-single-ended analog signals.

The device eliminates the need for external zero and

full-scale adjustments. Easy interfacing to microprocessors

is provided by the latched and decoded multiplexer address

inputs and latched TTL TRI-STATE outputs.

The design of the ADC0808, ADC0809 has been optimized

by incorporating the most desirable aspects of several A/D

conversion techniques. The ADC0808, ADC0809 offers high

speed, high accuracy, minimal temperature dependence, excellent long-term accuracy and repeatability, and consumes

minimal power. These features make this device ideally

suited to applications from process and machine control to

consumer and automotive applications. For 16-channel multiplexer with common output (sample/hold port) see

ADC0816 data sheet. (See AN-247 for more information.)

n Easy interface to all microprocessors

n Operates ratiometrically or with 5 VDC or analog span

adjusted voltage reference

n No zero or full-scale adjust required

n 8-channel multiplexer with address logic

n 0V to 5V input range with single 5V power supply

n Outputs meet TTL voltage level specifications

n Standard hermetic or molded 28-pin DIP package

n 28-pin molded chip carrier package

n ADC0808 equivalent to MM74C949

n ADC0809 equivalent to MM74C949-1

Key Specifications

n

n

n

n

n

Resolution

Total Unadjusted Error

Single Supply

Low Power

Conversion Time

8 Bits

12 LSB and 1 LSB

5 VDC

15 mW

100 s

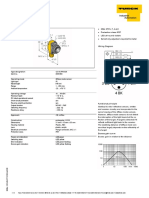

Block Diagram

DS005672-1

See Ordering

Information

TRI-STATE is a registered trademark of National Semiconductor Corp.

1999 National Semiconductor Corporation

DS005672

www.national.com

ADC0808/ADC0809 8-Bit P Compatible A/D Converters with 8-Channel Multiplexer

October 1999

ADC0808/ADC0809

Connection Diagrams

Molded Chip Carrier Package

Dual-In-Line Package

DS005672-12

Order Number ADC0808CCV or ADC0809CCV

See NS Package V28A

DS005672-11

Order Number ADC0808CCN or ADC0809CCN

See NS Package J28A or N28A

Ordering Information

TEMPERATURE RANGE

Error

12 LSB Unadjusted

1 LSB Unadjusted

Package Outline

www.national.com

40C to +85C

ADC0808CCN

ADC0808CCV

ADC0809CCN

ADC0809CCV

N28A Molded DIP

V28A Molded Chip Carrier

55C to +125C

ADC0808CCJ

ADC0808CJ

J28A Ceramic DIP

J28A Ceramic DIP

Dual-In-Line Package (ceramic)

Molded Chip Carrier Package

Vapor Phase (60 seconds)

Infrared (15 seconds)

ESD Susceptibility (Note 8)

Supply Voltage (VCC) (Note 3)

6.5V

Voltage at Any Pin

0.3V to (VCC+0.3V)

Except Control Inputs

Voltage at Control Inputs

0.3V to +15V

(START, OE, CLOCK, ALE, ADD A, ADD B, ADD C)

Storage Temperature Range

65C to +150C

875 mW

Package Dissipation at TA = 25C

Lead Temp. (Soldering, 10 seconds)

Dual-In-Line Package (plastic)

260C

Operating Conditions

300C

215C

220C

400V

(Notes 1, 2)

TMINTATMAX

40CTA+85C

40C TA +85C

4.5 VDC to 6.0 VDC

Temperature Range (Note 1)

ADC0808CCN,ADC0809CCN

ADC0808CCV, ADC0809CCV

Range of VCC (Note 1)

Electrical Characteristics

Converter Specifications: VCC = 5 VDC = VREF+, VREF() = GND, TMINTATMAX and fCLK = 640 kHz unless otherwise stated.

Symbol

Parameter

Conditions

Min

Typ

Max

Units

12

34

LSB

1

114

LSB

VCC+0.10

VDC

ADC0808

Total Unadjusted Error

25C

(Note 5)

TMIN to TMAX

LSB

ADC0809

VREF(+)

Total Unadjusted Error

0C to 70C

(Note 5)

TMIN to TMAX

Input Resistance

From Ref(+) to Ref()

1.0

Analog Input Voltage Range

(Note 4) V(+) or V()

GND0.10

Voltage, Top of Ladder

Measured at Ref(+)

Voltage, Center of Ladder

VREF()

Voltage, Bottom of Ladder

IIN

Comparator Input Current

VCC/2-0.1

Measured at Ref()

fc = 640 kHz, (Note 6)

LSB

2.5

VCC

VCC+0.1

VCC/2

VCC/2+0.1

0.1

0.5

Electrical Characteristics

Digital Levels and DC Specifications: ADC0808CCN, ADC0808CCV, ADC0809CCN and ADC0809CCV, 4.75VCC5.25V,

40CTA+85C unless otherwise noted

Symbol

Parameter

Conditions

Min

Typ

Max

Units

10

200

nA

1.0

ANALOG MULTIPLEXER

IOFF(+)

OFF Channel Leakage Current

VCC = 5V, VIN = 5V,

TA = 25C

IOFF()

OFF Channel Leakage Current

TMIN to TMAX

VCC = 5V, VIN = 0,

TA = 25C

200

TMIN to TMAX

1.0

10

nA

A

CONTROL INPUTS

VIN(1)

Logical 1 Input Voltage

VIN(0)

Logical 0 Input Voltage

IIN(1)

Logical 1 Input Current

VCC1.5

VIN = 15V

1.5

1.0

(The Control Inputs)

IIN(0)

Logical 0 Input Current

VIN = 0

1.0

(The Control Inputs)

ICC

Supply Current

fCLK = 640 kHz

0.3

3.0

mA

www.national.com

ADC0808/ADC0809

Absolute Maximum Ratings (Notes 2, 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

ADC0808/ADC0809

Electrical Characteristics

(Continued)

Digital Levels and DC Specifications: ADC0808CCN, ADC0808CCV, ADC0809CCN and ADC0809CCV, 4.75VCC5.25V,

40CTA+85C unless otherwise noted

Symbol

Parameter

Conditions

Min

Typ

Max

Units

DATA OUTPUTS AND EOC (INTERRUPT)

VOUT(1)

Logical 1 Output Voltage

VOUT(0)

Logical 0 Output Voltage

VOUT(0)

Logical 0 Output Voltage EOC

IOUT

TRI-STATE Output Current

VCC = 4.75V

IOUT = 360A

IOUT = 10A

IO = 1.6 mA

2.4

4.5

V(min)

V(min)

0.45

IO = 1.2 mA

VO = 5V

VO = 0

0.45

Electrical Characteristics

Timing Specifications VCC = VREF(+) = 5V, VREF() = GND, tr = tf = 20 ns and TA = 25C unless otherwise noted.

Typ

Max

Units

tWS

Symbol

Minimum Start Pulse Width

Parameter

(Figure 5)

Conditions

MIn

100

200

ns

tWALE

Minimum ALE Pulse Width

(Figure 5)

100

200

ns

ts

Minimum Address Set-Up Time

(Figure 5)

25

50

ns

tH

Minimum Address Hold Time

25

50

ns

tD

Analog MUX Delay Time

(Figure 5)

RS = 0 (Figure 5)

2.5

CL = 50 pF, RL = 10k (Figure 8)

CL = 10 pF, RL = 10k (Figure 8)

fc = 640 kHz, (Figure 5) (Note 7)

125

250

ns

125

250

ns

90

100

116

10

640

1280

kHz

From ALE

tH1, tH0

OE Control to Q Logic State

t1H, t0H

OE Control to Hi-Z

tc

Conversion Time

fc

Clock Frequency

tEOC

EOC Delay Time

(Figure 5)

8+2 S

Clock

Periods

CIN

Input Capacitance

At Control Inputs

10

15

pF

COUT

TRI-STATE Output

At TRI-STATE Outputs

10

15

pF

Capacitance

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to GND, unless othewise specified.

Note 3: A zener diode exists, internally, from VCC to GND and has a typical breakdown voltage of 7 VDC.

Note 4: Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater

than the VCCn supply. The spec allows 100 mV forward bias of either diode. This means that as long as the analog VIN does not exceed the supply voltage by more

than 100 mV, the output code will be correct. To achieve an absolute 0VDC to 5VDC input voltage range will therefore require a minimum supply voltage of 4.900 VDC

over temperature variations, initial tolerance and loading.

Note 5: Total unadjusted error includes offset, full-scale, linearity, and multiplexer errors. See Figure 3. None of these A/Ds requires a zero or full-scale adjust. However, if an all zero code is desired for an analog input other than 0.0V, or if a narrow full-scale span exists (for example: 0.5V to 4.5V full-scale) the reference voltages

can be adjusted to achieve this. See Figure 13.

Note 6: Comparator input current is a bias current into or out of the chopper stabilized comparator. The bias current varies directly with clock frequency and has little

temperature dependence (Figure 6). See paragraph 4.0.

Note 7: The outputs of the data register are updated one clock cycle before the rising edge of EOC.

Note 8: Human body model, 100 pF discharged through a 1.5 k resistor.

www.national.com

Multiplexer. The device contains an 8-channel single-ended

analog signal multiplexer. A particular input channel is selected by using the address decoder. Table 1 shows the input

states for the address lines to select any channel. The address is latched into the decoder on the low-to-high transition

of the address latch enable signal.

The successive approximation register (SAR) performs 8 iterations to approximate the input voltage. For any SAR type

converter, n-iterations are required for an n-bit converter.

Figure 2 shows a typical example of a 3-bit converter. In the

ADC0808, ADC0809, the approximation technique is extended to 8 bits using the 256R network.

TABLE 1.

SELECTED

ADDRESS LINE

ANALOG

CHANNEL

IN0

IN1

IN2

IN3

IN4

IN5

IN6

IN7

The A/D converters successive approximation register

(SAR) is reset on the positive edge of the start conversion

(SC) pulse. The conversion is begun on the falling edge of

the start conversion pulse. A conversion in process will be interrupted by receipt of a new start conversion pulse. Continuous conversion may be accomplished by tying the

end-of-conversion (EOC) output to the SC input. If used in

this mode, an external start conversion pulse should be applied after power up. End-of-conversion will go low between

0 and 8 clock pulses after the rising edge of start conversion.

The most important section of the A/D converter is the comparator. It is this section which is responsible for the ultimate

accuracy of the entire converter. It is also the comparator

drift which has the greatest influence on the repeatability of

the device. A chopper-stabilized comparator provides the

most effective method of satisfying all the converter requirements.

CONVERTER CHARACTERISTICS

The Converter

The heart of this single chip data acquisition system is its

8-bit analog-to-digital converter. The converter is designed to

give fast, accurate, and repeatable conversions over a wide

range of temperatures. The converter is partitioned into 3

major sections: the 256R ladder network, the successive approximation register, and the comparator. The converters

digital outputs are positive true.

The 256R ladder network approach (Figure 1) was chosen

over the conventional R/2R ladder because of its inherent

monotonicity, which guarantees no missing digital codes.

Monotonicity is particularly important in closed loop feedback

control systems. A non-monotonic relationship can cause oscillations that will be catastrophic for the system. Additionally,

the 256R network does not cause load variations on the reference voltage.

The chopper-stabilized comparator converts the DC input

signal into an AC signal. This signal is then fed through a

high gain AC amplifier and has the DC level restored. This

technique limits the drift component of the amplifier since the

drift is a DC component which is not passed by the AC amplifier. This makes the entire A/D converter extremely insensitive to temperature, long term drift and input offset errors.

Figure 4 shows a typical error curve for the ADC0808 as

measured using the procedures outlined in AN-179.

www.national.com

ADC0808/ADC0809

The bottom resistor and the top resistor of the ladder network in Figure 1 are not the same value as the remainder of

the network. The difference in these resistors causes the

output characteristic to be symmetrical with the zero and

full-scale points of the transfer curve. The first output transition occurs when the analog signal has reached +12 LSB

and succeeding output transitions occur every 1 LSB later up

to full-scale.

Functional Description

ADC0808/ADC0809

Functional Description

(Continued)

DS005672-2

FIGURE 1. Resistor Ladder and Switch Tree

DS005672-13

DS005672-14

FIGURE 2. 3-Bit A/D Transfer Curve

FIGURE 3. 3-Bit A/D Absolute Accuracy Curve

DS005672-15

FIGURE 4. Typical Error Curve

www.national.com

ADC0808/ADC0809

Timing Diagram

DS005672-4

FIGURE 5.

www.national.com

ADC0808/ADC0809

Typical Performance Characteristics

DS005672-16

FIGURE 6. Comparator IIN vs VIN

(VCC = VREF = 5V)

DS005672-17

FIGURE 7. Multiplexer RON vs VIN

(VCC = VREF = 5V)

TRI-STATE Test Circuits and Timing Diagrams

t1H, CL = 10 pF

t1H, tH1

DS005672-18

tH1, CL = 50 pF

DS005672-19

t0H, CL = 10 pF

t0H, tH0

DS005672-22

DS005672-21

DS005672-20

tH0, CL = 50 pF

DS005672-23

FIGURE 8.

DX = Data point being measured

DMAX = Maximum data limit

DMIN = Minimum data limit

A good example of a ratiometric transducer is a potentiometer used as a position sensor. The position of the wiper is directly proportional to the output voltage which is a ratio of the

full-scale voltage across it. Since the data is represented as

a proportion of full-scale, reference requirements are greatly

reduced, eliminating a large source of error and cost for

many applications. A major advantage of the ADC0808,

ADC0809 is that the input voltage range is equal to the supply range so the transducers can be connected directly

across the supply and their outputs connected directly into

the multiplexer inputs, (Figure 9).

Ratiometric transducers such as potentiometers, strain

gauges, thermistor bridges, pressure transducers, etc., are

suitable for measuring proportional relationships; however,

many types of measurements must be referred to an absolute standard such as voltage or current. This means a sys-

Applications Information

OPERATION

1.0 RATIOMETRIC CONVERSION

The ADC0808, ADC0809 is designed as a complete Data

Acquisition System (DAS) for ratiometric conversion systems. In ratiometric systems, the physical variable being

measured is expressed as a percentage of full-scale which is

not necessarily related to an absolute standard. The voltage

input to the ADC0808 is expressed by the equation

(1)

VIN = Input voltage into the ADC0808

Vfs = Full-scale voltage

VZ = Zero voltage

www.national.com

The top of the ladder, Ref(+), should not be more positive

than the supply, and the bottom of the ladder, Ref(), should

not be more negative than ground. The center of the ladder

voltage must also be near the center of the supply because

the analog switch tree changes from N-channel switches to

P-channel switches. These limitations are automatically satisfied in ratiometric systems and can be easily met in ground

referenced systems.

(Continued)

tem reference must be used which relates the full-scale voltage to the standard volt. For example, if VCC = VREF = 5.12V,

then the full-scale range is divided into 256 standard steps.

The smallest standard step is 1 LSB which is then 20 mV.

2.0 RESISTOR LADDER LIMITATIONS

The voltages from the resistor ladder are compared to the

selected into 8 times in a conversion. These voltages are

coupled to the comparator via an analog switch tree which is

referenced to the supply. The voltages at the top, center and

bottom of the ladder must be controlled to maintain proper

operation.

Figure 10 shows a ground referenced system with a separate supply and reference. In this system, the supply must be

trimmed to match the reference voltage. For instance, if a

5.12V is used, the supply should be adjusted to the same

voltage within 0.1V.

DS005672-7

FIGURE 9. Ratiometric Conversion System

The top and bottom ladder voltages cannot exceed VCC and

ground, respectively, but they can be symmetrically less than

VCC and greater than ground. The center of the ladder voltage should always be near the center of the supply. The sensitivity of the converter can be increased, (i.e., size of the

LSB steps decreased) by using a symmetrical reference system. In Figure 13, a 2.5V reference is symmetrically centered about VCC/2 since the same current flows in identical

resistors. This system with a 2.5V reference allows the LSB

bit to be half the size of a 5V reference system.

The ADC0808 needs less than a milliamp of supply current

so developing the supply from the reference is readily accomplished. In Figure 11 a ground referenced system is

shown which generates the supply from the reference. The

buffer shown can be an op amp of sufficient drive to supply

the milliamp of supply current and the desired bus drive, or if

a capacitive bus is driven by the outputs a large capacitor will

supply the transient supply current as seen in Figure 12. The

LM301 is overcompensated to insure stability when loaded

by the 10 F output capacitor.

www.national.com

ADC0808/ADC0809

Applications Information

ADC0808/ADC0809

Applications Information

(Continued)

DS005672-24

FIGURE 10. Ground Referenced

Conversion System Using Trimmed Supply

DS005672-25

FIGURE 11. Ground Referenced Conversion System with

Reference Generating VCC Supply

www.national.com

10

ADC0808/ADC0809

Applications Information

(Continued)

DS005672-26

FIGURE 12. Typical Reference and Supply Circuit

DS005672-27

RA = RB

*Ratiometric transducers

FIGURE 13. Symmetrically Centered Reference

The output code N for an arbitrary input are the integers

within the range:

3.0 CONVERTER EQUATIONS

The transition between adjacent codes N and N+1 is given

by:

(4)

Where: VIN = Voltage at comparator input

VREF(+) = Voltage at Ref(+)

VREF() = Voltage at Ref()

VTUE = Total unadjusted error voltage (typically

VREF(+)512)

(2)

The center of an output code N is given by:

(3)

11

www.national.com

ADC0808/ADC0809

Applications Information

If no filter capacitors are used at the analog inputs and the

signal source impedances are low, the comparator input current should not introduce converter errors, as the transient

created by the capacitance discharge will die out before the

comparator output is strobed.

If input filter capacitors are desired for noise reduction and

signal conditioning they will tend to average out the dynamic

comparator input current. It will then take on the characteristics of a DC bias current whose effect can be predicted conventionally.

(Continued)

4.0 ANALOG COMPARATOR INPUTS

The dynamic comparator input current is caused by the periodic switching of on-chip stray capacitances. These are

connected alternately to the output of the resistor ladder/

switch tree network and to the comparator input as part of

the operation of the chopper stabilized comparator.

The average value of the comparator input current varies directly with clock frequency and with VIN as shown in

Figure 6.

Typical Application

DS005672-10

*Address latches needed for 8085 and SC/MP interfacing the ADC0808 to a microprocessor

TABLE 2. Microprocessor Interface Table

PROCESSOR

www.national.com

READ

WRITE

INTERRUPT (COMMENT)

8080

MEMR

MEMW

INTR (Thru RST Circuit)

8085

RD

WR

INTR (Thru RST Circuit)

Z-80

RD

WR

INT (Thru RST Circuit, Mode 0)

SC/MP

NRDS

NWDS

SA (Thru Sense A)

6800

VMA 2 R/W

VMA R/W

IRQA or IRQB (Thru PIA)

12

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- LCD TutorialDocument44 pagesLCD TutorialSahil Khan100% (1)

- Otis Software Basic Data PDFDocument23 pagesOtis Software Basic Data PDFReynold Suarez100% (1)

- List of 7400 Series Integrated Circuits PDFDocument22 pagesList of 7400 Series Integrated Circuits PDFduriiNo ratings yet

- D D D D: Description/ordering InformationDocument24 pagesD D D D: Description/ordering InformationOmnhickNo ratings yet

- 60MHz LCD Frequency CounterDocument3 pages60MHz LCD Frequency CounterHector Ledesma IIINo ratings yet

- hd44780 1602A LCDDocument74 pageshd44780 1602A LCDJoão Paulo Versiani LadeiaNo ratings yet

- Hello WorlvvvvvdDocument8 pagesHello WorlvvvvvdbrodryuNo ratings yet

- Manual TB6560Document16 pagesManual TB6560erickmoraesNo ratings yet

- 4000 Series CMOS Logic ICsDocument10 pages4000 Series CMOS Logic ICsjaganmohanrs100% (1)

- ADC 0808 and 0809Document8 pagesADC 0808 and 0809Edwin YesaNo ratings yet

- Led Display DriversDocument4 pagesLed Display DriverscybertechnicoNo ratings yet

- Stepper Motor PDFDocument9 pagesStepper Motor PDFΓιώργος ΔήμαςNo ratings yet

- 16x2 LCD Display Module GuideDocument5 pages16x2 LCD Display Module GuidesalmanNo ratings yet

- Measurements & Electronic Instruments Laboratory Experiment ManualDocument3 pagesMeasurements & Electronic Instruments Laboratory Experiment Manualfirst lastNo ratings yet

- How To Control HD44780 DisplayDocument5 pagesHow To Control HD44780 DisplayUngureanu BiankaNo ratings yet

- Noritake Display 7k A-Apn200 E21Document52 pagesNoritake Display 7k A-Apn200 E21Muhammad ArslanNo ratings yet

- Current Mode PWM Controller: Features DescriptionDocument9 pagesCurrent Mode PWM Controller: Features DescriptionJozo ĆurčićNo ratings yet

- SCADA-Networking Protocol For Data ExchangeDocument83 pagesSCADA-Networking Protocol For Data ExchangeRaja RamNo ratings yet

- ADC - Sound Shaper Tree - Manul ServicioDocument41 pagesADC - Sound Shaper Tree - Manul ServicioCarol Eduardo Apitz DíazNo ratings yet

- LCD 16X2 para PicsDocument21 pagesLCD 16X2 para Picsjuarez100% (1)

- LCD (Liquid Crystal Display)Document24 pagesLCD (Liquid Crystal Display)Giani Kumar100% (3)

- Datasheet 4017Document8 pagesDatasheet 4017rathalengNo ratings yet

- Aplicacion Uc3842Document15 pagesAplicacion Uc3842Gian Mejia100% (1)

- Application For Blanket-Licensed Earth Stations in Motion: VerviewDocument10 pagesApplication For Blanket-Licensed Earth Stations in Motion: VerviewSimon AlvarezNo ratings yet

- PSRR and Measurement of PSRR in Class-D Audio Amplifiers and LDOs - An-135Document7 pagesPSRR and Measurement of PSRR in Class-D Audio Amplifiers and LDOs - An-135absalomlootNo ratings yet

- Ed Laboratory Dsa8400Document2 pagesEd Laboratory Dsa8400Jose Cesar Souza GebaraNo ratings yet

- Uc 3842Document56 pagesUc 3842Miguel TorresNo ratings yet

- Kh56qm SeriesDocument2 pagesKh56qm SeriesPhan AnNo ratings yet

- Datasheet - 74LS283 - Somador Binário Completo de 4 BitsDocument7 pagesDatasheet - 74LS283 - Somador Binário Completo de 4 BitsLucas CarvalhoNo ratings yet

- The Ansoff Model PDFDocument4 pagesThe Ansoff Model PDFCarbon Nano Tube0% (1)

- The Ansoff Model PDFDocument4 pagesThe Ansoff Model PDFCarbon Nano Tube0% (1)

- HD44780 CommandsDocument3 pagesHD44780 CommandsPhani ChakravarthiNo ratings yet

- LS7290 Stepper Motor ControlDocument12 pagesLS7290 Stepper Motor ControlOlger NavarroNo ratings yet

- Datasheet Sensor FotoelectricoDocument3 pagesDatasheet Sensor FotoelectricoFederico CalcopietroNo ratings yet

- Analog To Digital Convertor Interface With 8051 MicrocontrollerDocument28 pagesAnalog To Digital Convertor Interface With 8051 MicrocontrollerbbbbgcbgbeNo ratings yet

- ATmega328P - Instruction Set ManualDocument166 pagesATmega328P - Instruction Set ManualJesús Pérez MorenoNo ratings yet

- LCD Interfacing With Micro ControllersDocument4 pagesLCD Interfacing With Micro ControllersMijie Hj Hassan100% (1)

- HD44780 LCD Datasheet ExplainedDocument1 pageHD44780 LCD Datasheet ExplainedAnkit Daftery100% (4)

- 555 TimerDocument26 pages555 TimerEngr Wahab MarwatNo ratings yet

- Stepper ArduinoDocument6 pagesStepper ArduinoShahrim MohdNo ratings yet

- TEX100 - EN (Vol 1)Document48 pagesTEX100 - EN (Vol 1)Harris RahmanaNo ratings yet

- CD 4538Document10 pagesCD 4538Geraldo PereiraNo ratings yet

- Ecs Lecture5 Adc AhDocument45 pagesEcs Lecture5 Adc AhJai GaizinNo ratings yet

- List of 74xxx and 4xxx ICDocument15 pagesList of 74xxx and 4xxx ICTanvir Hussain92% (12)

- Kenwood AG 203 Service ManualDocument18 pagesKenwood AG 203 Service ManualJose PimentaNo ratings yet

- EEE Digital Assignment: Lamp Dimmer Circuit (Darlington Pair)Document6 pagesEEE Digital Assignment: Lamp Dimmer Circuit (Darlington Pair)bolbo naNo ratings yet

- Handson Technology: I2C To LCD Interface BoardDocument6 pagesHandson Technology: I2C To LCD Interface BoardAlan Robson100% (1)

- Fender Passport PD 250 SM (ET)Document36 pagesFender Passport PD 250 SM (ET)iceman55555No ratings yet

- SP431 Adjustable Precision RegulatorsDocument11 pagesSP431 Adjustable Precision Regulatorsagmnm1962No ratings yet

- 6ZG 1Document23 pages6ZG 1Sergio Daniel BarretoNo ratings yet

- The Transistor Tester User Manual (Newly)Document7 pagesThe Transistor Tester User Manual (Newly)Tanel Laanemägi100% (1)

- AN2450-L6599 Application Note PDFDocument32 pagesAN2450-L6599 Application Note PDF양영주No ratings yet

- BCD to 7-Segment Display Decoder ExplainedDocument3 pagesBCD to 7-Segment Display Decoder ExplainedMuhammad Aamir100% (1)

- List of 7400 Series Integrated Circuits - Wikipedia, The Free EncyclopediaDocument11 pagesList of 7400 Series Integrated Circuits - Wikipedia, The Free EncyclopediaHermes Heli Retiz AlvarezNo ratings yet

- Resistor Transistor LogicDocument3 pagesResistor Transistor LogicRAJESHKUMAR SNo ratings yet

- T6963C LCD Device Driver LinuxDocument10 pagesT6963C LCD Device Driver LinuxAnonymous NZrcrgNo ratings yet

- Adc 0808Document14 pagesAdc 0808Vikas PatelNo ratings yet

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocument16 pagesμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKasi ChinnaNo ratings yet

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocument16 pagesμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKudo ShinichiNo ratings yet

- ADC0809CCNDocument16 pagesADC0809CCNFrancesca Castelar BenalcazarNo ratings yet

- ADC0808Document15 pagesADC0808Ketan SalviNo ratings yet

- Adc 0804Document41 pagesAdc 0804AndySilvandNo ratings yet

- ADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer OptionsDocument20 pagesADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer Optionsrazali1982No ratings yet

- Product Life CycleDocument5 pagesProduct Life CycleCarbon Nano TubeNo ratings yet

- Ael1046 Universal Lab TrainerDocument2 pagesAel1046 Universal Lab TrainerCarbon Nano TubeNo ratings yet

- SGP10xxS Series DDS Signal Generator User's ManualDocument7 pagesSGP10xxS Series DDS Signal Generator User's ManualCarbon Nano TubeNo ratings yet

- OWON XDM3041 Bench-Type Digital Multimeter Technical Spec.sDocument2 pagesOWON XDM3041 Bench-Type Digital Multimeter Technical Spec.sAndres LaiNo ratings yet

- Item 5 FG-2002 Function Generator and Power Supply Mar 2021Document14 pagesItem 5 FG-2002 Function Generator and Power Supply Mar 2021Carbon Nano TubeNo ratings yet

- Product Life Cycle CostingDocument3 pagesProduct Life Cycle CostingCarbon Nano TubeNo ratings yet

- Item 3 Ac DC Power Supply MPS350-6 Mar 2021Document14 pagesItem 3 Ac DC Power Supply MPS350-6 Mar 2021Carbon Nano TubeNo ratings yet

- High-Performance XDG2000 Waveform GeneratorDocument20 pagesHigh-Performance XDG2000 Waveform GeneratorCarbon Nano TubeNo ratings yet

- Electrical MeasurementDocument12 pagesElectrical MeasurementCarbon Nano TubeNo ratings yet

- Global Enterprise & Leadership-LUC Dec2019Document41 pagesGlobal Enterprise & Leadership-LUC Dec2019Carbon Nano TubeNo ratings yet

- DS1000E DatasheetDocument7 pagesDS1000E DatasheetunknownipNo ratings yet

- Anivys New Product CatalogDocument5 pagesAnivys New Product CatalogCarbon Nano TubeNo ratings yet

- Ael1037b-I Power Electronics Trainer v1.2014Document2 pagesAel1037b-I Power Electronics Trainer v1.2014Carbon Nano TubeNo ratings yet

- Grandway Fhs2q01f Light SourceDocument2 pagesGrandway Fhs2q01f Light SourceCarbon Nano TubeNo ratings yet

- Satellite Communication Trainer: TechnologiesDocument1 pageSatellite Communication Trainer: TechnologiesCarbon Nano TubeNo ratings yet

- Analog Circuit Design Courseware: Designed To Impart Knowledge inDocument4 pagesAnalog Circuit Design Courseware: Designed To Impart Knowledge inCarbon Nano TubeNo ratings yet

- Power Electronic Devices TrainerDocument67 pagesPower Electronic Devices TrainerCarbon Nano TubeNo ratings yet

- CTC Domestic Circuit Board ModelDocument1 pageCTC Domestic Circuit Board ModelCarbon Nano TubeNo ratings yet

- 02 Basic Optics System Manual OS 8515CDocument58 pages02 Basic Optics System Manual OS 8515CCarbon Nano TubeNo ratings yet

- 16 PowerElectronics Lab 09Document1 page16 PowerElectronics Lab 09Carbon Nano TubeNo ratings yet

- Jabatan Kejuruteraan Elektrik Politeknik Port Dickson KM 14 Jalan Pantai, 71050 SIRUSA, Negeri SembilanDocument6 pagesJabatan Kejuruteraan Elektrik Politeknik Port Dickson KM 14 Jalan Pantai, 71050 SIRUSA, Negeri SembilanCarbon Nano TubeNo ratings yet

- CTC Fluorescent Lamp SeriesDocument1 pageCTC Fluorescent Lamp SeriesCarbon Nano TubeNo ratings yet

- Motor Fault Simulator L Low Voltage Fault Simulation Trainer (XPO - MFS)Document1 pageMotor Fault Simulator L Low Voltage Fault Simulation Trainer (XPO - MFS)Carbon Nano TubeNo ratings yet

- Scientech 2801 Guide to PAM, PPM, PWM & Line CodingDocument2 pagesScientech 2801 Guide to PAM, PPM, PWM & Line CodingCarbon Nano TubeNo ratings yet

- Spreading Science & Technology: Home Electrical Wiring Training SystemDocument1 pageSpreading Science & Technology: Home Electrical Wiring Training SystemCarbon Nano TubeNo ratings yet

- Reasoning New 1Document28 pagesReasoning New 1Redemptah Mutheu MutuaNo ratings yet

- Proxxon - MF 70Document4 pagesProxxon - MF 70Carbon Nano TubeNo ratings yet

- Cp1e P061-E1 16 2 csm2118Document54 pagesCp1e P061-E1 16 2 csm2118Carbon Nano TubeNo ratings yet

- InTech-Equivalent Circuit and Calculation of Its Parameters of Magnetic Coupled Resonant Wireless Power Transfer PDFDocument17 pagesInTech-Equivalent Circuit and Calculation of Its Parameters of Magnetic Coupled Resonant Wireless Power Transfer PDFMaria Lavinia IordacheNo ratings yet

- GC9403 Application Notes Ver04 - 20141206Document24 pagesGC9403 Application Notes Ver04 - 20141206SpecShareNo ratings yet

- Accurately measure long distances with the NTS-660LCl660RC total stationDocument2 pagesAccurately measure long distances with the NTS-660LCl660RC total stationabdulNo ratings yet

- ElectronicsDocument3 pagesElectronicsashishkumar218No ratings yet

- Modicon TSX Micro Automation Platform: Presentation, Description, SelectionDocument14 pagesModicon TSX Micro Automation Platform: Presentation, Description, SelectionsebadolzNo ratings yet

- Genius SW Flat2.1 1250 - Ver1.0Document17 pagesGenius SW Flat2.1 1250 - Ver1.0Vyacheslav Disco 80No ratings yet

- ADC and Power Optimization With tinyAVR® 0 - and 1 - Series, and megaAVR® 0-SeriesDocument62 pagesADC and Power Optimization With tinyAVR® 0 - and 1 - Series, and megaAVR® 0-SeriessaifulkohNo ratings yet

- How Computers Work & Their Daily UseDocument3 pagesHow Computers Work & Their Daily UserezaNo ratings yet

- Load Test of Single Phase TransformerDocument6 pagesLoad Test of Single Phase TransformerKevin DanyNo ratings yet

- WLAN NetworkingDocument247 pagesWLAN NetworkingNazar AzizNo ratings yet

- 74 3441Document104 pages74 3441GUZMANNo ratings yet

- 2nd Order Band Pass Chebyshev 0.5 DB Active Filter Design Assignment 2 KHZ - 4 KHZDocument7 pages2nd Order Band Pass Chebyshev 0.5 DB Active Filter Design Assignment 2 KHZ - 4 KHZBuddhiNo ratings yet

- Sn74als245a PDFDocument21 pagesSn74als245a PDFRodriguezJoseCarlosNo ratings yet

- Module 3:the Memory System: Courtesy: Text Book: Carl Hamacher 5 EditionDocument73 pagesModule 3:the Memory System: Courtesy: Text Book: Carl Hamacher 5 EditionRajkumarNo ratings yet

- Service Manual: CSD-TD51 CSD-TD52 CSD-TD53Document30 pagesService Manual: CSD-TD51 CSD-TD52 CSD-TD53parascoliNo ratings yet

- 1606-XLERED: Power Supply Ess Redundancy Module 24-60Vdc 20A Catalogue NoDocument3 pages1606-XLERED: Power Supply Ess Redundancy Module 24-60Vdc 20A Catalogue NoA. Muhsin PamungkasNo ratings yet

- Design and Implementation of Audio Transceiver Using Infrared Laser For Audio Signal DetectionDocument4 pagesDesign and Implementation of Audio Transceiver Using Infrared Laser For Audio Signal DetectionGoitom HaileNo ratings yet

- Digital Analog Heterodyne Microwave Radio SystemDocument4 pagesDigital Analog Heterodyne Microwave Radio SystemEduardo CudiaNo ratings yet

- DC To AC InvertersDocument41 pagesDC To AC Invertersarefiqrc100% (1)

- GeiDocument2 pagesGeisansureNo ratings yet

- Marble Rush Ultimate Set 542300-002 IM0 BILDocument19 pagesMarble Rush Ultimate Set 542300-002 IM0 BILJordan BélangerNo ratings yet

- Driving transistors and thyristorsDocument11 pagesDriving transistors and thyristorsEduard KeynesNo ratings yet

- Savk 61 DgsDocument156 pagesSavk 61 Dgsall schematicNo ratings yet

- Hardware Maintainance ManualDocument104 pagesHardware Maintainance ManualchanduNo ratings yet

- MADYA COMPUTER SERVICE CENTER OFFERS LAPTOPS, PCs AND MOREDocument2 pagesMADYA COMPUTER SERVICE CENTER OFFERS LAPTOPS, PCs AND MOREcl3o.frNo ratings yet

- EE453 Power System Protection and Stability Assignment 5Document2 pagesEE453 Power System Protection and Stability Assignment 5umar khanNo ratings yet

- Infinity-Reference5760 5761 CarampDocument33 pagesInfinity-Reference5760 5761 CarampJeff ReikenNo ratings yet