Professional Documents

Culture Documents

Guide Active HDL 83 V 09

Uploaded by

Wilfried KamgaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Guide Active HDL 83 V 09

Uploaded by

Wilfried KamgaCopyright:

Available Formats

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.

9, 13 janvier 2014)

Guide pratique dutilisation dActive-HDL 8.3

1 Introduction

1.1 Survol

Active-HDL, de la compagnie Aldec, est un environnement intgr de dveloppement de systmes numriques dcrits :

avec un langage de description matrielle (comme VHDL, Verilog et SystemC);

par schmas;

par diagrammes d'tats; ou,

avec une combinaison des trois.

Active-HDL inclut entre autres :

des outils de description de designs;

des compilateurs pour plusieurs langages de description matrielle;

un simulateur;

des outils de dbogage; et,

des outils de profilage et de vrification.

Le logiciel intgre de plus des outils de synthse et d'implmentation d'autres compagnies, permettant

ainsi de travailler avec diffrentes technologies dans un environnement unifi. Dans ce guide, on suppose

que la suite d'outils ISE de Xilinx est installe en conjonction avec Active-HDL.

Au dpartement de gnie informatique et de gnie logiciel, une version complte dActive-HDL est installe dans les laboratoires Windows. Une version tudiante peut tre tlcharge du site web de la

compagnie (www.aldec.com).

1.2 Objectif de ce guide

L'objectif de ce guide est d'numrer et de dcrire les tapes pour :

crer un espace de travail dans Active-HDL;

crer un projet et l'ajouter un espace de travail;

dcrire un circuit numrique l'aide de code VHDL;

simuler le circuit numrique en lui appliquant des signaux d'entre dsirs et en observant sa sortie;

et,

dcrire un circuit numrique laide dune description hirarchique, base sur un schma, et contenant plusieurs modules dcrits en VHDL dans des fichiers spars.

cole Polytechnique de Montral

page 1 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

1.2.1 Lancement de Active-HDL

Lancez Active-HDL en choisissant la commande

correspondante dans le menu Dmarrer.

Si une fentre License Configuration souvre,

cliquez simplement sur Next.

2 Cration dun espace de travail (workspace)

Un espace de travail (workspace) peut regrouper plusieurs projets (designs) logiquement relis entre eux.

Par exemple, dans le contexte d'un programme universitaire, on pourrait avoir un espace de travail pour

chaque cours, et un projet pour chaque laboratoire de ce cours. Un espace de travail diffrent pourrait

regrouper les laboratoires d'un cours diffrent, d'un projet intgrateur, ou de projets personnels.

La premire fois que vous lancez le programme,

une fentre apparat. Choisissez OK pour crer

un nouvel espace de travail. Sinon, choisissez

File > New > Workspace.

Choisissez un nom reprsentatif pour un premier

espace de travail.

Il faut aussi spcifier un rpertoire dans lequel

l'espace de travail sera sauvegard. Il est important que le chemin de ce rpertoire ne contienne

pas d'espaces, parce que certains outils invoqus

par Active-HDL ne les supportent pas bien.

Dans les laboratoires du GIGL, il est donc recommand de travailler dans un rpertoire

personnel sur C:\temp\votrenom. Une fois le travail termin, il est important d'archiver ce

rpertoire et d'en emporter une copie avec vous.

Le rpertoire C:\temp\ des ordinateurs des laboratoires est rgulirement effac.

cole Polytechnique de Montral

page 2 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

3 Cration dun projet (design)

Un projet permet de regrouper plusieurs fichiers-sources pour un laboratoire ou un module en particulier.

Lors de la cration du premier espace de travail,

l'outil vous propose immdiatement de crer un

nouveau projet.

Pour les projets suivant, il suffit de choisir File >

New > Design.

Cliquez sur Next pour invoquer l'assistant.

Vrifiez que les bons outils ont t pralablement

choisis. Si ce n'est pas le cas, informez votre charg

de laboratoire ou cliquez sur Flow Settings pour

faire les bons choix.

Pour la case Default Family, le choix devrait correspondre la famille du type de FPGA utilis dans

votre laboratoire. Le choix indiqu ici correspond

au cours INF3500. Vrifiez avec votre charg de

laboratoire dans le cas contraire.

Cliquez sur Next.

cole Polytechnique de Montral

page 3 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

Choisissez un nom reprsentatif pour votre projet.

Cliquez sur Next, puis sur Finish.

4 Description dun circuit numrique en VHDL

4.1 Circuit en exemple

Dans les instructions qui suivent, on construit un circuit arithmtique de base : un additionneur 3 bits.

Ce circuit accepte 3 bits en entre et les additionne. Il a deux sorties : une retenue ainsi quune somme.

Les sorties possibles sont donc (retenue, sortie) {(0, 0), (0, 1), (1, 0), (1, 1)}, correspondant respectivement aux cas o les trois bits dentre sont 0, un seul bit est 1, deux bits sont 1, et trois bits sont 1. Ce

circuit indique donc le nombre de bits dentre qui valent 1.

Le tableau de vrit de ce circuit est donn ici :

cole Polytechnique de Montral

bit0

bit1

bit2

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

retenue somme

page 4 de 20

0

0

0

1

0

1

1

1

0

1

1

0

1

0

0

1

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

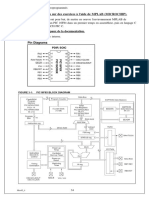

On peut driver les quations pour les sorties retenue et somme grce un tableau de Karnaugh. Un

schma dun circuit ralisant ces deux fonctions est donn ici :

Le circuit est compos des composantes suivantes :

deux portes OU-exclusif deux entres;

deux portes ET deux entres;

une porte OU deux entres; et,

trois terminaux dentre et deux terminaux de sortie.

4.2 Procdure

Lancez Active-HDL. Ouvrez lespace de travail dans lequel se trouve le design sur lequel vous voulez

travailler. Si votre espace de travail comporte plus dun design, cliquer sur celui sur lequel vous voulez

travailler avec le bouton de droite, et choisissez Set as Active Design.

Suivez les instructions suivantes:

Dans lexplorateur de projets (Design Browser), cliquez sur le + gauche de votre

projet, puis deux fois sur Add New File.

cole Polytechnique de Montral

page 5 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

Choisissez licne VHDL Source Code de

longlet Empty Files. Donnez un nom reprsentatif au fichier (ici add3bits).

Cliquez sur OK.

Dans lditeur de texte, entrez le code VHDL

suivant, et sauvegarder le (soit avec Ctrl+S ou

dans File > Save).

------------------------------------- add3bits.vhd

-- additioneur 3 bits

-----------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity add3bits is

port (

bit0 : in std_logic;

bit1 : in std_logic;

bit2 : in std_logic;

retenue : out std_logic;

somme : out std_logic

);

end add3bits;

architecture flotdonnees of add3bits is

signal T1 : std_logic;

signal T2 : std_logic;

signal T3 : std_logic;

begin

somme <= T1 xor bit0;

retenue <= T3 or T2;

T1 <= bit1 xor bit2;

T2 <= bit1 and bit2;

T3 <= bit0 and T1;

end flotdonnees;

5 Compilation du projet

Lors de la compilation, le projet est vrifi de faon confirmer que toutes les rgles de syntaxe du langage sont respectes.

Une compilation correcte ne signifie pas que le circuit fonctionne, mais plutt que sa description est

conforme des rgles prcises.

Choisissez Design > Compile, ou pesez sur la touche F11.

Corrigez toutes les erreurs (si ncessaire).

cole Polytechnique de Montral

page 6 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

6 Simulation du projet

La simulation du projet permet de vrifier quil fonctionne de la faon prvue par les spcifications.

Tout d'abord, choisissez Tools > Preferences

et vrifiez pour la catgorie Waveform Viewer/Editor que Standard Waveform

Viewer/Editor est bien l'affichage de chronogramme par dfaut.

Choisissez Simulation > Initialize Simulation.

Choisissez File > New > List.

Choisissez File > New > Waveform.

Cliquez sur le symbole de lentit simuler

(add3bits ici) de la fentre de lexplorateur de

design gauche.

Dans la fentre des signaux, choisissez, en

pesant sur la touche Shift, les signaux bit0,

bit1, bit2, retenue et somme. Tranez ces signaux dans la fentre Waveform.

Rptez pour la fentre List.

cole Polytechnique de Montral

page 7 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

laide de la souris et de la touche Shift, slectionnez les signaux bit0, bit1 et bit2 dans la

fentre Waveform.

Cliquez sur le bouton de droite et choisissez

Stimulators.

Choisissez le signal bit0, puis le type Clock,

puis fixez la frquence 10 MHz. Cliquez sur

Apply.

Rptez pour les signaux bit1 et bit2, en fixant

leurs frquences 20 MHz et 40 MHz, respectivement.

Avec un temps de simulation de 100 ns, cliquez

sur le bouton Run For.

Vrifiez le fonctionnement correct de votre

additionneur 3 bits laide de la fentre Waveform.

cole Polytechnique de Montral

page 8 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

et de la fentre List. Affichez le menu

contextuel (clic-droit) et activez sur Collapse

Deltas.

cole Polytechnique de Montral

page 9 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

7 Trois outils pratiques pour crire du code VHDL

Active-HDL contient trois outils particulirement pratiques pour crire du code VHDL.

Lassistant du langage (Language Assistant) est

invoqu en cliquant sur lampoule lectrique.

Lassistant comporte plusieurs catgories

dlments VHDL et il est facile de copiercoller du code dans un module.

Du menu Help > Online Documentation, on

lance laide de Active-HDL. Dans la section

References, on trouve un guide du langage

VHDL qui est trs complet.

Du menu Help > Interactive VHDL Tutorial,

on lance le programme Evita qui est un tutorial

trs convivial pour lapprentissage de VHDL.

cole Polytechnique de Montral

page 10 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

8 Synthse et implmentation du projet

8.1 Description

La synthse dun circuit consiste traduire la description du circuit en blocs disponibles dans la technologie utilise. Par exemple, pour un circuit dcrit avec un schma et qui doit tre ralis sur un FPGA, le

processus de synthse convertit et regroupe les portes logiques du schma en composantes ralisables sur

le FPGA choisi.

Limplmentation du circuit est divise en quatre sous tapes:

la transformation (mapping) : regrouper les composantes obtenues lors de la synthse dans des blocs

spcifiques du FPGA;

la disposition (placement) : choisir des endroits spcifiques sur le FPGA o disposer les blocs utiliss,

et choisir les pattes du FPGA correspondant aux ports dentre et de sortie;

le routage (routing) : tablir des connexions lectriques entre les blocs utiliss; et,

la configuration (configuration) : convertir toute cette information en un fichier pouvant tre tlcharg sur le FPGA pour le programmer.

8.2 Ports dentre et de sortie

Pendant ltape de disposition de limplmentation, il faut assigner des pattes spcifiques du FPGA des

ports dentre et de sortie de son design. Pour le design prsent, les ports dentre sont bit0, bit1 et

bit2, et les ports des sortie sont retenue et somme.

Lassignation des ports se fait par lentremise dun fichier de contraintes avec lextension .ucf (pour

user constraints file).

Ouvrez un diteur de texte (comme Notepad++ ou lditeur de texte dActive-HDL) et copiez-y les lignes

suivantes. On suppose que vous utilisez la planchette Digilent Genesys.

# add3bits.ucf

# pour planchette Digilent Genesys

# LEDs

NET "retenue" LOC = "AH8"; # LD1

NET "somme" LOC = "AG8"; # LD0

# commutateurs

NET "bit0" LOC = "J19"; # SW0

NET "bit1" LOC = "L18"; # SW1

NET "bit2" LOC = "K18"; # SW2

On note que chaque port est list dans le fichier, exactement comme il apparat dans le code. Le symbole

du dise (#) indique que le reste de la ligne est un commentaire (ne sapplique pas dans un fichier vhdl).

Sauvegardez le fichier dans le mme rpertoire que les autres fichiers source de votre design, sous le nom

de add3bits.ucf.

Consultez le manuel de l'utilisateur de votre planchette de dveloppement pour plus de dtails.

cole Polytechnique de Montral

page 11 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

8.3 Procdure

Activez la fentre design flow. Si elle nest pas

visible, choisissez View > Flow.

Double-cliquez sur le bouton options gauche de

licne synthesis.

Pour Top-Level Unit choisissez le nom de votre

entit du plus haut niveau, ici add3bits.

Pour Family et Device, pour la planchette Genesys,

il faut choisir Xilinx13x VIRTEX5 et

5vlx50tff1136. Pour Speed Grade, choisir -1.

Pour les autres options, on peut prendre les valeurs

par dfaut.

Cliquez sur OK.

Cliquez sur licne synthesis.

Une nouvelle fentre devrait apparatre, et, aprs un

certain temps, le message Synthesis finished successfully devrait apparatre. Sinon, consultez les

messages derreur et apportez les corrections ncessaires vos fichiers.

En cas de doute, consultez votre charg de laboratoire.

Cliquez sur Close.

Cliquez sur le bouton options gauche de licne

implementation.

cole Polytechnique de Montral

page 12 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

Sous longlet Main, la ligne Constraint File

(UCF) Support, choisissez Custom constraint

file.

Cliquez sur Browse, et choisissez votre fichier

add3bits.ucf.

Sous longlet Post-Map STR, choisissez Do Not

Run Post-Map STR.

STR signifie Static Timing Report, ou rapport des

dlais statiques. Enlever cette option acclre le

processus.

Sous longlet Post-PAR STR, choisissez Do Not

Run Post-PAR STR.

cole Polytechnique de Montral

page 13 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

Sous longlet BitStream, dslectionnez Do Not

Run Bitgen slectionnez Create Bit File.

Cliquez sur OK.

Cliquez sur licne implementation.

Une nouvelle fentre devrait apparatre, et, aprs

un certain temps, le message Implementation

completed successfully devrait apparatre.

Sinon, consultez les messages derreur et apportez les corrections ncessaires votre diagramme.

En cas de doute, consultez le charg de laboratoire.

Cliquez sur Close.

9 Programmation du FPGA et vrification

Mise en garde :

Les instructions suivantes sont particularises pour la planchette Digilent Genesys.

Voir le lien web suivant pour travailler avec la carte :

http://digilentinc.com/Products/Detail.cfm?NavPath=2,400,819&Prod=GENESYS

Si tout sest bien pass ltape prcdente, un fichier add3bits.bit est maintenant plac dans votre rpertoire \espaceDeTravail\design1\implement\ver1\rev1 et est prt tre tlcharg dans le FPGA de la

planchette de dveloppement.

cole Polytechnique de Montral

page 14 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

Au laboratoire, la planchette devrait tre dj

allume et relie au poste de travail par le cble

USB2. Dans ce cas, passez ltape suivante. Si

la planchette nest pas allume, informez le charg de laboratoire.

Dans Active-HDL, activez la fentre design

flow. Si elle nest pas visible, choisissez View >

Flow.

Cliquez sur le bouton Analysis, en bas droite,

puis sur licne de loutil iMPACT.

Si la fentre Automatically create and save a

project saffiche, cliquez sur No. Choisissez

create a new project, cliquez sur OK, puis assurez-vous de mettre loption de branchement

automatique avant de cliquer de nouveau sur OK.

Cliquez sur Yes si la fentre Auto Assign

Configuration Files Query Dialog saffiche.

Choisissez le fichier add3bits.bit que vous trouverez dans le dossier implement/ver1/rev1 et

cliquez sur Open. Si le logiciel vous demande

dattacher un SPI ou un BPI PROM, rpondez

par No. Cette option sert charger la mmoire

PROM de la planchette.

cole Polytechnique de Montral

page 15 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

Cliquez sur le symbole reprsentant le FPGA,

puis sur le bouton de droite de la souris. Choisissez Program

Cliquez sur OK dans la fentre Device Programming Properties (si elle saffiche), sans

rien changer.

Voil! Vous pouvez maintenant vrifier votre

design sur le FPGA.

Essayez toutes les combinaisons possibles

dentres et confirmez que les sorties sont bien

conformes au tableau de vrit de la section 4.1.

Note : Si lespace est blanc, cliquez sur le bouton

de droite de la souris et choisissez Initialize

Chain. Vous pourrez ensuite suivre les instructions pour y ajouter votre fichier .bit.

cole Polytechnique de Montral

page 16 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

10 Description hirarchique dun projet comportant plusieurs modules

10.1 Principes de base et circuit en exemple

Les circuits numriques ne sont jamais dcrits laide dun seul fichier contenant du code VHDL. La

plupart regroupent plusieurs modules indpendants qui sont tirs de bibliothques existantes ou bien qui

sont dvelopps sur mesure pour un projet en particulier. Quand un projet regroupe un grand nombre de

modules dcrits dans autant de fichiers, il peut devenir difficile de sy retrouver. De plus, il est ncessaire

de dcrire les interconnexions entre les diffrents modules, et encore l il peut devenir difficile de sy

retrouver. Une description hirarchique utilisant des schmas permet de grer la fois la complexit du

projet et de dcrire les interconnexions de faon efficace.

Dans cette section, vous allez crer un projet et y ajouter des fichiers VHDL existants. Vous allez ensuite

relier les modules dcrits dans ces fichiers laide dun schma. Vous allez aussi effectuer toutes les

connexions ncessaires pour une implmentation sur la planchette de dveloppement. Les instructions

suivantes illustrent la description hirarchique dun projet avec Active-HDL laide dun exemple.

10.2 Procdure suivre

Crez un nouveau projet en suivant les instructions de la section 3, et donnez-lui le nom tutoriel .

Copiez du site web du cours INF3500 dans le dossier src de votre projet les fichiers :

addsub.vhd

hd44780_8chars_1line.vhd

hd44780_simple.vhd

equal_ascii.vhd

signed_to_lcd.vhd

addsub_to_lcd.vhd

addsub.ucf

Dans lexplorateur de projets (Design Browser), cliquez sur le + gauche de votre projet, puis deux fois

sur Add New File. Cliquez sur Add Existing File et ajoutez les fichiers que vous venez de copier.

Inspectez les fichiers que vous avez copis. Le fichier addsub.vhd dcrit un module qui peut additionner

ou soustraire deux nombres A et B selon la valeur dun signal de slection choix. Il a une sortie F reprsentant le rsultat et V indiquant si un dbordement a lieu. Le paramtre W indique la largeur des

oprandes et du rsultat.

Dans lexplorateur de projets (Design Browser),

cliquez sur le + gauche de votre projet, puis deux

fois sur Add New File. Sous longlet Empty File,

choisissez Block Diagram. Donnez le nom addsub_top au diagramme.

cole Polytechnique de Montral

page 17 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

En cliquant sur licne des ports ou en choisissant

Diagram > Terminal, ajoutez les terminaux suivants au diagramme.

Ports dentre : clk, reset, choix, A(3:0) et B(3:0).

Ports de sortie : lcd_db(7:0), lcd_rw, lcd_rs, lcd_en

et V.

Les ports avec des indices entre parenthses sont des

bus, les autres sont des fils. Assurez-vous que les

ports A et B sont de type signed

Choisissez Diagram > Code Generation Settings

...

Sous longlet Design Unit, complter la fentre

Design Unit Header.

Dans cette fentre, il faut ajouter les librairies utiliss par les diffrents modules du circuit.

Sous longlet Conversion Functions, dslectionnez toutes les options. Cliquez sur OK.

cole Polytechnique de Montral

page 18 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

Choisissez Design > Compile All.

Cliquez sur licne Show Symbol Toolbox (petite porte ET dans la barre doutil). Dans la

libraire tutoriel, cliquez sur le module addsub, puis

tranez le symbole dans le diagramme.

Rptez pour les modules signed_to_lcd, addsub_to_lcd, equal_ascii et hd44780_8char_1line.

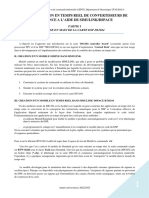

Reliez les modules et les terminaux tels que montr limage suivante. Il faut instancier trois copies du

module signed_to_lcd.

Le module addsub est dfini avec une largeur par

dfaut de 8 bits. Il faut spcifier une valeur de 4 ici.

laide du bouton de droite, cliquez sur le symbole

addsub et choisissez Properties. Sous longlet Generics, entrez la valeur 4 pour le paramtre W.

Par dfaut, les bus et les fils reliant les modules sont des types std_logic_vector et std_logic,

respectivement. Les bus ont une largeur de 8 bits par dfaut.

Il faut donc effectuer des conversions explicites de type dans certains cas. Pour ce faire, il faut inspecter

les dfinitions des diffrents modules dans leurs fichiers pour voir o cest ncessaire. Dans les prochains

cole Polytechnique de Montral

page 19 de 20

Dpartement de gnie informatique et de gnie logiciel

Guide pratique ActiveHDL 8.3 sp1 update 3 (v. 0.9, 13 janvier 2014)

laboratoires, il vous faudra jouer avec ces paramtres pour que la synthse russisse.

Par exemple, la sortie F du symbole addsub a le type

signed. Il faut donc changer le type et la largeur

du bus qui y est connect. Cliquez deux fois sur ce

bus, puis ajustez ses proprits comme montr ici

Dans certains cas, un bus (qui est de type

std_logic_vector) est connect une entre de module de type signed. Pour faire la conversion de

std_logic_vector vers signed au niveau de lentre

comme tel, il faut faire un clique-droit sur le bloc,

puis Properties Dans longlet Port Mapping, on

choisit le mode Function, et on indique le type signed. Pour plus de renseignements, voir le

supplment de ce guide disponible sur le site moodle

du cours INF3500.

10.3 Simulation dun circuit hirarchique

La simulation dun circuit hirarchique peut parfois tre lourde. Par exemple, le module ssdDriver ne sert

ici qu dcoder les signaux pour laffichage, et linterprtation de ses sorties est difficile faire.

Au minimum, chaque module devrait tre vrifi indpendamment. Dans un laboratoire, il est essentiel de

vrifier compltement chaque nouveau module dvelopp. La vrification complte du circuit devrait tre

faite par simulation quand cest possible, ou par implmentation sur la planchette dans le cas o un affichage est effectu.

10.4 Implmentation du circuit et programmation du FPGA

Suivez les instructions des sections 8.3 pour faire limplmentation du circuit, puis de la section 9 pour en

faire limplmentation sur la planchette.

Il se peut que vous voyiez des avertissements (warnings) lors de la synthse. Assurez-vous simplement

que ces avertissements ne concernent que le bloc hd44780_8chars_1line.vhd (hd44780_simple).

Notez que pour limplmentation vous devez utiliser le fichier addsub.ucf qui est particularis pour les

noms de terminaux montrs sur le diagramme de la section 10.2.

Pour obtenir le fichier VHDL de votre .bde, ouvrez votre projet ActiveHDL ainsi que votre .bde. Cliquez

ensuite, dans la barre de menu suprieure, sur Diagram > Generate HDL Code. Un code VHDL qui

instancie tous vos blocs selon vos connexions est gnr. Vous pouvez alors le rcuprer (dans le dossier

compile de votre dossier de projet ActiveHDL).

cole Polytechnique de Montral

page 20 de 20

Dpartement de gnie informatique et de gnie logiciel

You might also like

- TP1 4 Me27Document17 pagesTP1 4 Me27Mohamed NarumohNo ratings yet

- Guide Pratique Vivado v11 PDFDocument13 pagesGuide Pratique Vivado v11 PDFraniaNo ratings yet

- Fascicule de TP FpgaDocument32 pagesFascicule de TP FpgaHichem HamdiNo ratings yet

- TP3 3elnaDocument4 pagesTP3 3elnaAbdelhamid SaighiNo ratings yet

- ReadmeDocument15 pagesReadmeMed MadridNo ratings yet

- tp1 SystemcDocument3 pagestp1 SystemcAdil AbouelhassanNo ratings yet

- SOPC BuilderDocument17 pagesSOPC BuilderSimoKasNo ratings yet

- Travaux Pratiques: Electronique Numérique Avancée: Fpga - VHDLDocument39 pagesTravaux Pratiques: Electronique Numérique Avancée: Fpga - VHDLMį Ņā ŘěťNo ratings yet

- TP2 CoddesignDocument10 pagesTP2 Coddesigntalel haninNo ratings yet

- Elen0037 Labo1Document39 pagesElen0037 Labo1DominiqueNo ratings yet

- TP C54 PDFDocument18 pagesTP C54 PDFSanou BougharriouNo ratings yet

- Carte Numerique QuartusDocument26 pagesCarte Numerique QuartusAdiouma DiopNo ratings yet

- And GateDocument7 pagesAnd GateBehij ben amorNo ratings yet

- ++utilisation Du SOPC Builder - 1Document19 pages++utilisation Du SOPC Builder - 1Salima AZIZINo ratings yet

- TP Sin 2018 2017 PDFDocument21 pagesTP Sin 2018 2017 PDFyapNo ratings yet

- TP VHDL ModelSim20016 2017Document12 pagesTP VHDL ModelSim20016 2017Ayoub RahmouniNo ratings yet

- Manipulation Synthese VHDL TP en XILINXDocument17 pagesManipulation Synthese VHDL TP en XILINXdrissi kaitouni zinebNo ratings yet

- TD PSoC 1Document5 pagesTD PSoC 1Môham MedNo ratings yet

- Travaux PratiquesDocument18 pagesTravaux PratiquesSolomane KanéNo ratings yet

- TP4 Simulation Microcontroleur PICDocument6 pagesTP4 Simulation Microcontroleur PICSalah Dahouathi100% (1)

- TP1 - C1 - Prise en MainDocument17 pagesTP1 - C1 - Prise en MainAkram Del RioNo ratings yet

- VHDL LearningDocument9 pagesVHDL LearningAZEDDINENo ratings yet

- TP N1-Prise en Main de QuartusDocument22 pagesTP N1-Prise en Main de QuartusIlham KinichNo ratings yet

- Notice QuartusDocument16 pagesNotice QuartusSamra MrabetNo ratings yet

- TP Khamlich Niosii1Document9 pagesTP Khamlich Niosii1Bilal ChNo ratings yet

- TIA PortalDocument10 pagesTIA PortalAyoub AyayNo ratings yet

- TP 1 Basys 2Document12 pagesTP 1 Basys 2Lena OgbiNo ratings yet

- Compte Rendu TP1 VHDLDocument8 pagesCompte Rendu TP1 VHDLboussaoud.oualidNo ratings yet

- Micro 3Document8 pagesMicro 3Kiadam KitouNo ratings yet

- TP1 VHDLDocument6 pagesTP1 VHDLmoussaNo ratings yet

- C4 GestionProjetDocument204 pagesC4 GestionProjetpipilaNo ratings yet

- Rapport TP VHDLDocument16 pagesRapport TP VHDLAbdessamad ChbichebNo ratings yet

- TP1 FpgaDocument6 pagesTP1 Fpgasaid100% (1)

- TP Api1-1 MicroLogix1200Document6 pagesTP Api1-1 MicroLogix1200Mohamed RgnNo ratings yet

- Rapport Mplab PDFDocument12 pagesRapport Mplab PDFSimo AbkariNo ratings yet

- Rapport DSPDocument11 pagesRapport DSPEnnayri100% (1)

- TP VHDL FpgaDocument13 pagesTP VHDL FpgaJoel Minkeu100% (1)

- Compte RenduDocument7 pagesCompte RenduMezni RanyaNo ratings yet

- Syst' Emes Num Eriques V4Document19 pagesSyst' Emes Num Eriques V4ثانوية مولاي سليمانNo ratings yet

- TP Dspace Buck Boost InverseurDocument5 pagesTP Dspace Buck Boost Inverseursami debbacheNo ratings yet

- Cours Step7Document49 pagesCours Step7Dawn Light0% (1)

- Materiel TP Processeurs de SignauxDocument10 pagesMateriel TP Processeurs de SignauxTonprince Knight AdNo ratings yet

- TP VHDL 2024Document15 pagesTP VHDL 2024aminefoura6No ratings yet

- TP1 Dsp-Fpga S2 2021Document6 pagesTP1 Dsp-Fpga S2 2021yousraNo ratings yet

- Carte Numerique QuartusDocument26 pagesCarte Numerique QuartusalarichcharlesekNo ratings yet

- Tuto VivadoDocument7 pagesTuto Vivadoجميلة جميلةNo ratings yet

- Codesign Etape Nios2Document8 pagesCodesign Etape Nios2rejeb wissalNo ratings yet

- TP1 - Réseaux Et Télécmmunications - UEM 122 PDFDocument26 pagesTP1 - Réseaux Et Télécmmunications - UEM 122 PDFHermosaNo ratings yet

- Cours Labview 09Document55 pagesCours Labview 09Mohamed BerririNo ratings yet

- La Simulation VHDL - ModelSimDocument16 pagesLa Simulation VHDL - ModelSimMouad DarifNo ratings yet

- TP4 Application Pratique Des Files D'attente Avec Les Périphériques Du PIC24FDocument15 pagesTP4 Application Pratique Des Files D'attente Avec Les Périphériques Du PIC24FABDESSAMAD EL YOUSFYNo ratings yet

- Lab 1Document7 pagesLab 1Mamadou Korka KantéNo ratings yet

- Fassicule TP FODocument23 pagesFassicule TP FOJbir DoniaNo ratings yet

- Polycope TP DSPDocument24 pagesPolycope TP DSPSmirnov Artaéév67% (6)

- 2021 Tps 6Document19 pages2021 Tps 6Moujahed GassoumiNo ratings yet

- 82 Ena tp1 Tutorial Xilinx SchematicDocument9 pages82 Ena tp1 Tutorial Xilinx SchematicSmart ClasseNo ratings yet

- Travaux Pratiques - Microprocesseurs Microcontrôleurs PDFDocument13 pagesTravaux Pratiques - Microprocesseurs Microcontrôleurs PDFGoufi Aouf0% (1)

- LabviewDocument19 pagesLabviewtortorouNo ratings yet

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasFrom EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasNo ratings yet

- VHDL PDFDocument17 pagesVHDL PDFAbdelhamid DaribNo ratings yet

- Correction TD N 1 VHDL 2020 Envoi2Document16 pagesCorrection TD N 1 VHDL 2020 Envoi2nour sinNo ratings yet

- M ElectriqueDocument20 pagesM ElectriqueAdnane BechriNo ratings yet

- Compte Rendu Counter DecounterDocument18 pagesCompte Rendu Counter DecounterGuergour WalidNo ratings yet

- Formation VHDL FPGA Cours 5Document103 pagesFormation VHDL FPGA Cours 5Bouhafs AbdelkaderNo ratings yet

- 43 Telecom Systs TelecomDocument63 pages43 Telecom Systs TelecomcikguaiyadNo ratings yet

- CR 13 Les Memoires en VHDLDocument14 pagesCR 13 Les Memoires en VHDLMohammed BelkheiriNo ratings yet

- Laboratoire IDocument15 pagesLaboratoire IKhadidjaNo ratings yet

- Suite Cours Fpga Ikram MaaouiDocument26 pagesSuite Cours Fpga Ikram MaaouiFeriel GHOUILANo ratings yet

- Logprog TPVHDLDocument20 pagesLogprog TPVHDLWalid AmriNo ratings yet

- TD VHDLPPDocument23 pagesTD VHDLPPMël DjäNo ratings yet

- QCM VHDLDocument7 pagesQCM VHDLBELKACEMNo ratings yet

- 46 Telecom Systs TelecomFDocument59 pages46 Telecom Systs TelecomFtoto19800No ratings yet

- Tuto VivadoDocument7 pagesTuto Vivadoجميلة جميلةNo ratings yet

- Corrigé Partiel VHDL FPGA M1 ELN SE 2020Document6 pagesCorrigé Partiel VHDL FPGA M1 ELN SE 2020yasmine hmnNo ratings yet

- VHDL Machine A EtatDocument19 pagesVHDL Machine A EtathamissouNo ratings yet

- Livret Pédagogique Licence SPI 2022-2023 PDFDocument208 pagesLivret Pédagogique Licence SPI 2022-2023 PDFPrince BountsenguiNo ratings yet

- And GateDocument7 pagesAnd GateBehij ben amorNo ratings yet

- Elen0037 Labo1Document39 pagesElen0037 Labo1DominiqueNo ratings yet

- Cours SoC 2011Document72 pagesCours SoC 2011cointoinNo ratings yet

- CoursPolyLE2012011 2012Document221 pagesCoursPolyLE2012011 2012aymendabNo ratings yet

- Capteurs de MesureDocument9 pagesCapteurs de MesureDhafer MezghaniNo ratings yet

- FSM VHDL Code - 2021Document46 pagesFSM VHDL Code - 2021Souad ElhammoualiNo ratings yet

- Chap3 Circuitscombinatoires M1 2023Document14 pagesChap3 Circuitscombinatoires M1 2023Sãhãzà RandriamaharavoNo ratings yet

- TD RevisionDocument2 pagesTD RevisionMãrÿ ŌûmåNo ratings yet

- Eln-Electronique Desn Systemes EmbarquesfDocument23 pagesEln-Electronique Desn Systemes EmbarquesfMarquiz DitchiNo ratings yet

- TD1 VHDLDocument3 pagesTD1 VHDLbejaoui yosrNo ratings yet

- Cours Algebre de BoolDocument242 pagesCours Algebre de BoolCabrel TchoffoNo ratings yet

- Sc0 IntroductionDocument1 pageSc0 IntroductionNeifar AmelNo ratings yet

- Émetteur-Récepteur ManchesterDocument14 pagesÉmetteur-Récepteur ManchesterSiham MajidNo ratings yet