Professional Documents

Culture Documents

BS2F7VZ0164 Sharp Tuner

Uploaded by

Hasan AKOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BS2F7VZ0164 Sharp Tuner

Uploaded by

Hasan AKCopyright:

Available Formats

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.

net

MODEL

No.

SPEC No.

BS2F7VZ0164

DOC.

RECORDS OF

DATE

REVISION

REF. PAGE

PARAGRAPH

DRAWING No.

REVISED

No.

FIRST

IDENT.

DATA

ISSUE

EC-06X02

PAGE

2 / 19

11.OCT.2006

No.

SUMMARY

CHECK

APPROVAL

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

3/19

DESCRIPTION:

This specification covers DBS tuner intended for use in Digital Broadcasting Satellites. This

tuner incorporates "LINK" section that is composed of 8bit ADC, multistandard DVB-S/DVB-S2

demodulator and multistandard FEC. This tuner has DVB common interface compliant transport

stream output.

[1] GENERAL SPECIFICATIONS

1-1. Receiving frequency range

950MHz to 2150MHz

1-2. Input level

-65dBm to -25dBm

1-3. Input structure

F type Female

1-4. Nominal input impedance

75 ohm

1-5. Channel selection system

PLL synthesizer built in tuner IC IX2470VA

(Address:C0h)

(Reference clock: Internal 4.0MHz crystal oscillation)

1-6. Tuning step frequency

1MHz

1-7. Cutoff frequency

of Baseband(=I/Q out) LPF

Variable from 10MHz to 34MHz by 2MHz step

1-8. LINK IC

STB0899 (Address: D0h)

(Reference clock: 4MHz supplied from IX2470VA)

1-9. System clock specification

Fsampling=FM_CLK=99MHz

1-10. Multistandard demodulation

and decoding

[DVB-S]

>Channel symbol rate up to QPSK 45MSps

>Inner Viterbi and Outer Reed-solomon decoding

>Punctured rates 1/2, 2/3, 3/4, 5/6, 6/7, 7/8

[DVB-S2]

>Channel symbol rates up to QPSK 36MSps,

and 8PSK 30MSps

>Inner LDPC and outer BCH decoding

>Punctured rates 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9, 9/10

1-11. Operating voltage

(B2, B3 and B4) 3.3V +/- 0.165V DC

(VDD)

1.8V +/- 0.090V DC

1-12. Storage condition

Temperature

Humidity

Period

1-13. Environmental characteristics

RoHS compliant

(RoHS refers to the "DIRECTIVE 2002/95/EC OF THE

EUROPEAN PARLIAMENT AND OF THE COUNCIL of

27 January 2003 on the restriction of the use of certain

hazardous substances in electrical and electronic

equipment.")

15 deg.C to 35 deg.C

25 %RH to 75 %RH

6 months

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

4/19

1-14. Attention items:

1) This unit contains components that can be damaged by electro-static discharge.

Before handling this unit, ground your hands, tools, working desks and equipment to protect

the unit from Electronic Static Destroy.

2) Avoid following actions;

a) to store this unit in the place of the high temperature and humidity.

b) to expose this unit to corrosive gases.

[2] MECHANICAL SPECIFICATION

2-1. Dimension and mounting details

see section [14]

2-2. Mass

44g (typical)

2-3. Strength of F-connector

No severe transform or distortion at bending moment,

0.98Nm. To be connected electrically.

2-4. Clamp Torque of F-connector

No severe transform or distortion on the connection with

F-connector at bending moment, 0.98Nm.

To be connected electrically.

[3] ENVIRONMENTAL SPECIFICATION

(ELECTRICAL FUNCTIONAL OPERATION GUARANTEE)

3-1. Operating

Temperature

0deg.C to +50deg.C

Humidity

Less than 85

No condensation

3-2. Storage

Temperature

Humidity

-20deg.C to +85deg.C

Less than 95

Water vapor pressure 6643Pa max, without condensation

<Notice>

Please be careful that sudden temperature changes may cause condensation during storage,

and such condensation may cause corrosion.

[4] ABSOLUTE MAXIMUM VOLTAGE

Pin name

Pin No.

B1B

1

B1A

2

B4

3

B2

4

B3

11

VDD

13

SDA, SCL, RESETB

8, 9, 26

MIN.

-0.3

-0.3

-0.25

-0.1

-0.3

MAX

25

25

3.63

4.0

3.63

2.0

B3+0.3

UNIT

V

V

V

V

V

V

V

Note

400mA max.

400mA max.

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

[5] TESTING CONDITION

5-1. Supply voltage

Pin name

Pin No.

B4

3

B2

4

B3

11

VDD

13

MIN.

3.25

3.25

3.25

1.77

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

TYP.

3.30

3.30

3.30

1.80

MAX.

3.35

3.35

3.35

1.83

5-2. Ambient temperature

25deg.C +/- 5deg.C

5-3. Ambient humidity

65%

[6] ELECTRICAL SPECIFICATION

No.

6-4

6-5

6-6

6-7

6-8

6-9

6-10

RF input VSWR

Noise figure(at max. gain)

rd

3 order Intermodulation

Undesired signal (2 signals)

(FD+29.5MHz, FD+59MHz) or

(FD -29.5MHz, FD -59MHz)

L.O. leak at input terminal

PLL synthesizer tuning time

PLL phase noise

PLL reference leak

RF output VSWR

RF output gain

Current

B2

consumption B3

B4

VDD

[7] ERROR RATE PERFORMANCE

Es/No performance at Quasi Error Free

Mode

ETSI Ideal

QPSK 1/2

QPSK 3/5

QPSK 2/3

QPSK 3/4

QPSK 4/5

QPSK 5/6

QPSK 8/9

QPSK 9/10

8PSK 3/5

8PSK 2/3

8PSK 3/4

8PSK 5/6

8PSK 8/9

8PSK 9/10

1.00

2.23

3.10

4.03

4.68

5.18

6.20

6.42

5.50

6.62

7.91

9.35

10.69

10.98

PAGE

5/19

Note

+/- 10%

Unless otherwise stated testing condition 5-15-3.

Item

MIN.

6-1

6-2

6-3

UNIT

V

V

V

V

No.

40

-5

Specification

TYP.

MAX.

UNIT

2.0

2.5

8

12 dB

60

dB

-68

10

-80

-91

-40

2.0

0

90

70

25

1200

Performance

(Typical)

1.2

2.4

3.2

4.2

4.8

5.3

6.4

6.6

5.8

6.8

8.1

9.6

10.9

11.3

-63

50

-70

-86

-30

2.5

+5

135

130

40

1800

Unit

dBm

ms

dBc/Hz

dBc/Hz

dBc

dB

mA

mA

mA

mA

Condition

950MHz to 2150MHz

950MHz to 2150MHz

Input level: -25dBm

I/Q amplitude: 0.6VP-P

BBLPF Fc=30MHz

950MHz to 2150MHz

limited to IX2470VA

10kHz offset

100kHz offset

1MHz

950MHz to 2150MHz

measured at RF out

3.3V

3.3V

3.3V

1.8V

Note

>DVB-S2

>Pilot: ON

>BW = Synbol_rate

>BERTester: SFU

dB

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

6/19

[8] I2C INTERFACE

8-1. Internal circuits

The interface of this tuner is as following figure. It is using the I2C private repeater of STB0899 for

tuner isolation.

8-2. I2C bus characteristic (conforms to the specification of STB0899)

Item

Input high voltage

Input low voltage

SCL clock rate

Bus free time between a stop

and start condition

Hold time (repeated) start

condition

Low period of the SCL

High period of the SCL

Rise time for SDA and SCL

Fall time for SDA and SCL

Setup time for a repeated start

condition

Setup time for stop condition

Data setup time

Pulse width of spikes to be

suppressed by input filter

Synbol

vih

vil

fscl

tbuf

MIN.

2.0

-0.5

MAX.

3.6

0.8

400

1.3

Unit

V

V

kHz

us

thd, sta

0.6

us

tlow

thigh

tr

tf

tsu, sta

1.3

0.6

us

us

ns

ns

us

tsu, sto

tsu, dat

tsp

0.6

100

300

300

0.6

50

us

ns

ns

Note

Normal mode

After this period, the first

clock pulse is generated.

Fast mode

Fast mode

Fast mode

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

7/19

[9] IX2470VA FUNCTIONAL DESCRIPTION

PLL and VCO are promptly set up without fail when the user correctly program the data with the

prompt I2C access sequence as long as the following are also applied;

a) Follow the I2C standard specification

b) Leave RTS to 0

9-1. I2C-BUS DATA FORMATS

Table 1 ; Write data format (MSB is transmitted first)

MSB

LSB

0(MA1)

0(MA0)

Byte1

1(BG1)

0(BG0)

N8

N7

N6

N5

N4

Byte2

N3

N2

N1

A5

A4

A3

A2

A1

Byte3

1(C1)

1(C0)

PD5

PD4

TM

0(RTS)

REF

Byte4

BA2

BA1

BA0

PSC

PD3

PD2/TS2

DIV/TS1

PD0/TS0

Byte5

*A

* N8 to N1

* A5 to A1

* REF

* PSC

* MA1, MA0

* PD0

* BA2, BA1, BA0

* DIV

* PD5 to PD2

* RTS

* TS2, TS1, TS0

* C1, C0

* BG1, BG0

* TM

; Acknowledge bit

; Programmable division ratio control bits

; Swallow division ratio setting bits

; Reference division ratio setting bits

; Prescaler division ratio setting bits

; Address setting bits

; PO control bit

; Local oscillator select

; Local oscillator divided ratio setting

; BB LPF cut-off frequency setting

; Test mode control bit

; Test mode setting bits (when RTS = '1')

; Charge pump current setting bits

; BB AMP gain setting bits

; VCO/LPF adjustment mode setting bits

(see Table 3)

(see Table 4)

(see Table 5)

(see Table 6)

(see Table 7)

(see Table 8)

(see Table 9)

(see Table 10)

(see Table 11)

(see Table 12)

(see Table 13)

(see section 9-3)

Write PLL register data to set one among the following I C access sequence as #a) to h).

It is available to skip the bytes which does not require for renewal or change the sequence of the bytes to

choose one of the following.

2

st

nd

rd

th

th

I C start->1 byte->2 byte->3 byte->4 byte->5 byte

2

2

a)

I C start -> byte1 -> byte2 -> byte3 -> byte4 -> byte5 *

byte1: I C address byte

2

b)

I C start -> byte1 -> byte4 -> byte5 -> byte2 -> byte3 *

2

2

c)

I C start -> byte1 -> byte2 -> byte3 -> byte4 -> either I C stop or (another) start

2

2

d)

I C start -> byte1 -> byte4 -> byte5 -> byte2 -> either I C stop or (another) start

2

2

e)

I C start -> byte1 -> byte2 -> byte3 -> either I C stop or (another) start

2

2

f)

I C start -> byte1 -> byte4 -> byte5 -> either I C stop or (another) start

2

2

g)

I C start -> byte1 -> byte2 -> either I C stop or (another) start

2

2

h)

I C start -> byte1 -> byte4 -> either I C stop or (another) start

2

th

*: Either I C stop or (another) start is available to follow after the 5 byte, but not mandatory

2

CAUTION: During receiving signals, dont access I C bus to satisfy the phase noise character

specification.

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

8/19

NOTE: PLL set up rules

2

The following conditions are required to program the I C access sequence.

According to a required renewal data on each byte, one of the access sequence shown above as

a) to h) should be chosen.

st

1) Write byte1 on the 1 byte after I C start.

nd

2) Write either byte2 or byte4 on the 2 byte.

nd

nd

When the MSB header is 0 on the 2 byte, the 2 byte is recognized as byte2.

nd

nd

When the MSB header is 1 on the 2 byte, the 2 byte is recognized as byte4.

3) The following byte after byte2 or byte4 should be the sequent # of the last byte as;

The byte3 should be followed after byte2.

The byte5 should be followed after byte4.

4) The number of byte to write in one access sequence as from a start to a stop (or another start)

state should be two bytes at least. Review #g) and #h). Maximum bytes are five as write all byte1

to byte5 data in one access sequence. Review #a) and #b)

2

5) The renewal of the register data is only available when it becomes an I C stop or another start

state after all the bytes to write in case of #c) to h). Only in the case when the renewal of the

register data all from byte2 to byte5 in one access sequence as #a) and #b), a stop state or

another start state is not mandatory required for data renewal.

6) The data already registered and not to write for renewal has kept as it is as the last state.

7) Every time when the power is on, write all the register data on byte2 to byte5 in one sequence for

the purpose of the initial default set up to follow either #a) or #b). Because the initial values on

byte2 to byte5 are not fixed before the initialization.

8) As for POR (POWER ON RESET) of this tuner, the rise of the power-supply voltage might not

operate normally when it is not linear, and the noise enters while the power-supply voltage is rising.

For this case, the tuner might not accept the data input (Ack is not returned). Please input data

again (re-try) for this case.

Table 2; Read data format

MSB

1

POR

1

FL

0

RD2

0

RD1

0

RD1

MA1

X

MA0

X

LSB

1

X

A

A

Byte1

Byte2

* POR

; Power on reset indicator

(see table 14)

* FL

; Phase lock detect flag

(see table 15)

* RD2 RD0 ; Reserved (These bit values change under the condition of ICs.)

*X

; dont care

* All data of byte2 will be H, when Power on reset operates under the condition of a pulled up SDA.

* Read mode will change to Write mode after completing to output the byte2.

9-2. PROGRAMING

9-2-1 Programmable divider bits data

Please set P, N, A, R as follows.

fvco = [(P * N) + A] * fosc / R

fvco : Receiving frequency

P : Dividing factor of prescaler (16 or 32)

N : Programmable division ratio (5 to 255)

A : Swallow division ratio (0 to 31 and A < N)

fosc : Reference oscillation frequency (4 MHz)

R : Reference division ratio (see table 5)

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

9/19

9-2-2 Data setting

Table 3; Programmable division ratio control

(Binary: 8 bits)

Table 4; Swallow division ratio setting

(Binary: 5 bits)

Bit data

Bit data

Dividing

Dividing

factor (N) N8 N7 N6 N5 N4 N3 N2 N1

factor (A) A5 A4 A3 A2 A1

5

0

0

0

0

0

1

0

1

0

0

0

0

0

0

6

0

0

0

0

0

1

1

0

1

0

0

0

0

1

255

1

1

1

1

1

1

1

1

31

1

1

1

1

1

* The using of 4 or smaller dividing factors is inhibited.

2

* The dividing factor is set by the data of N8 to N1 and A5 to A1 in byte2, 3 on I C write data. (table 1)

Table 5; Reference division ratio setting (Binary: 1 bit)

REF

Dividing factor (R)

Compare frequency

fvco(MHz)

Caution:

0

4

1 MHz

1024 2150 MHz*

Only use REF=0

1

8

500 KHz

950 2150 MHz

* When the reference division ratio set to 4(REF = '0'), the fvco's minimum frequency must be higher

than 1024 MHz (including 1024 MHz). If the frequency is lower than 1023 MHz, the condition

mentioned in section 6-2-1 "A < N" is not satisfied. But all receiving ranges can be covered with

combination with PSC setting. (see Table 6)

Table 6; Prescaler division ratio setting (Binary: 1 bit)

The dividing factor is set by t

PSC

Dividing factor (P)

fvco

2

PSC in byte 4 on I C write data.

0

32

950 2150 MHz

1

16

950 1375 MHz*

* When the prescaler division ratio of the prescaler is set to 16(PSC = '1'), the fvco's maximum

frequency must be lower than 1375 MHz (including 1375 MHz). This fvco's maximum frequency

limitation is depended on the operation frequency of the internal programmable counter. Refer to Table

9 about PSC detailed setting.

Table 7; Address selection (Binary: 2 bits)

Bit

Table 8; PO control (Binary: 1 bit)

Bit

MA1

MA0

0V 0.1VCC

open

0.4VCC 0.6VCC

0.9VCC VCC

ADR input voltage

Output of PO

PD0

Normal

Power on

Power on

Hi-Z

Hi-Z

0

Hi-Z

* Hi-Z : High impedance

Hi-Z

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

10/19

Table 9; Local oscillator select (Binary: 4 bits)

Byte 4

Byte 5

BAND

PSC

div.ratio

DIV

BA2

BA1

BA0

div.ratio

Local frequency

(Receiving frequency)

1/16

1/4

950 ~ 986 MHz

1/16

1/4

986 ~ 1073 MHz

1/32

1/4

1073 ~ 1154 MHz

1/32

1/2

1154 ~ 1291 MHz

1/32

1/2

1291 ~ 1447 MHz

1/32

1/2

1447 ~ 1615 MHz

1/32

1/2

1615 ~ 1791 MHz

1/32

1/2

1791 ~ 1972 MHz

1/32

1/2

1972 ~ 2150 MHz

1/32

0/1

VCO disable

PSC

VCO

Table 10; Baseband LPF cut-off frequency setting

Register Bit

PD2

PD3

PD4

PD5

LPF cut-off

Frequency

10 MHz

12 MHz

14 MHz

16 MHz

18 MHz

20 MHz

22 MHz

24 MHz

26 MHz

28 MHz

30 MHz

32 MHz

34 MHz

Table 11; Test mode setting

RTS

0

Register Bit

TS2

TS1

X

TS0

X

Test mode

Normal operation

X: dont care

1

Don't use

Reserved (Test Mode)

2

* When RTS=1 on I C write data (table 1), it changes to test mode.

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

11/19

Table 12; Charge pump output current selection

Bit

Charge pump output current [A]

min

typ

max

C1

C0

78

120

150

169

260

325

360

555

694

780

1200

1500

Table 13; Baseband AMP gain control (Depend on PLL register setting)

BG1

BG0

ATTENUATION (Typ.)

0/1

2 dB

4 dB

* Set BG1,BG0 as 1,0.

Table 14; POR bit polarity

VCC > 2.2V

POR bit

L

* SDA has to be pulled up.

Table 15; FL bit polarity

VCC < 2.2V

H

FL bit

lock

H

unlock

L

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

12/19

9-3. Tuner control procedure

VCO and LPF adjustment mode setting sequence after power on

START

2

I C Start

Byte1

Set the MA1, MA0 bits

(Slave address setting)

Wait for 10msec

Hardware adjustment

mode running

Byte2

Set MSB header bit to '0'

(Byte2 header bit data)

Set BG1, BG0 bit

(BB AMP gain setting)

Set the N8-N4 bits

(Programmable division ratio control)

I C Start

Byte1

Set the MA1, MA0 bits

(Slave address setting)

Byte4

Byte3

Set MSB header bit to '1'

(Byte4 header bit data)

Set the PD5 and PD4 bits

(BB LPF cut-off frequency setting)

Leave the TM bit to '1'

(VCO/LPF adjustment mode setting)

Leave the latest data

(C1, C0, RTS, REF)

Set the N3-N1 bits

(Programmable division ratio control)

Set the A5-A1 bits

(Swallow division ratio setting)

Byte4

Set MSB header bit to '1'

(Byte4 header bit data)

Set the PD5 and PD4 bits to '0'

(BB LPF cut-off frequency setting)

Set the TM bit to '0'

(VCO/LPF adjustment mode clear)

Leave the latest data

(C1, C0, RTS, REF)

Byte5

Set the BA2-BA0 bits

(Local oscillator select)

Byte5

Set the PD3 and PD2 bits

(BB LPF cut-off frequency setting)

Leave the latest data

(BA2-BA0, PSC, DIV, PD0)

2

I C Stop

END

Set the PD3 and PD2 bits to '0'

(BB LPF cut-off frequency setting)

Set the DIV bit

(Local oscillator divided ratio setting)

Leave the latest data

(PSC, PD0)

2

(I C Stop)

2

I C Start

Byte1

Set the MA1, MA0 bits

(Slave address setting)

Byte4

Set MSB header bit to '1'

(Byte4 header bit data)

Set the TM bit to '1'

(VCO/LPF adjustment mode setting)

Leave the latest data

(C1, C0, PD5, PD4, RTS, REF)

2

I C Stop

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

13/19

[10] Reliability

10-1. High temperature high humidity load (40deg.C, 90% RH, 500h)

1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial

value.

2) After cycling DUT in the constant chamber at 40deg.C/90-95% RH in on state, for total 500h,

leave the DUT at room temperature and humidity for 2h and then measure value after test.

3) Must meet the specifications of Table 17.

4) The contact resistance of F-connector must be less than 0.02 ohm. (*)

10-2. High temperature load (70deg.C, 40% RH, 500h)

1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial

value.

2) After leaving DUT in the constant chamber at 70+/-2deg.C/40% RH for total 500h, leave the

DUT at room temperature and humidity for 2h and then measure value after test.

3) Must meet the specifications of Table 17.

10-3. Cold test (-25deg.C, 500h)

1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial

value.

2) After leaving DUT in the constant temperature chamber at -25deg.C for 500h, leave the DUT

at room temperature and humidity for 2h and then measure the values after test.

3) Must meet the specifications of Table 17.

10-4. Shock (686 m/s2, 6 planes, 3 times)

1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial

values.

2) Using the shock tester, apply shock of 686 m/s2 three times to each of 6 planes and then

measure the values.

3) Must meet the specifications of Table 17.

4) This test is to be conducted using a single tuner.

10-5. Vibration (10-55 Hz, 1.5 mm, in each of three mutually perpendicular directions, each 2 times)

1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial

values.

2) Using the vibration tester, apply motion having an amplitude of 1.5 mm (constant), the

frequency being varied uniformly between 10 and 55 Hz, to DUT, for 2h in each of three

mutually perpendicular directions (X, Y and Z, total of 6h). After the test, measure the values.

3) Must meet the specifications of Table 17.

4) This test is to be conducted using a single tuner.

10-6. Heat shock test (1 cycle=1h (-20deg.C; 0.5h, 70deg.C;0.5h), 50 cycles))

1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial value.

2) Using the heat shock tester, apply heat shock to DUT. After the test, measure the values.

3) Must meet the specifications of Table 17.

4) The contact resistance of F-connector must be less than 0.02 ohm. (*)

10-7. Solderability of terminal

Pretreatment of heating terminal at 150deg.C for 1h is performed and leave it at room

temperature for 2h or longer. Immerse 1.9 mm length of terminal (from the tip) to be soldered into

rosin (JIS-K-5902), isopropyl alcohol (JIS-K-8839 or JIS-K-1522, rosin concentration (10-35%

range) approx. 25% by weight unless otherwise specified) or equivalent solution for 35s, and then

immerse the length of the terminal into a pool of molten solder (Sn/3.0Ag/0.5Cu, or equivalent) at

240 +/-2deg.C for 3s.Dipped terminal portion shall be wetted by more than 95%. (Excluding the

cutting plane of the chassis)

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

14/19

10-8. Soldering heat resistance

Immerse the terminal mounted on a PCB (1.6t thick) into solder at 3505deg.C for 3.0-3.5

seconds or at 260 +/-5deg.C for 10 +/-1 seconds. Remove the PCB from the solder and leave it for

1 hour at room temperature. The test sample shall show no degradation in appearance and

electrical characteristics.

10-9. ESD protection

Table 16; ESD Test Condition (IEC61000-4-2 Compliant)

Terminal

Limits

Condition

RF_IN

+/-6kV DC

150pF/330ohm

(coaxial center)

each 5 times

Others

+/-200V DC

150pF/330ohm

each 5 times

Table 17

No.

Item

10-1 Noise figure(at max. gain)

10-2 PLL phase noise

10-3

10-4

Current

B2

consumption B3

B4

VDD

Es/No at QEF

8PSK 3/4

Spec.

< 12

< -70

< -86

< 135

< 130

< 40

< 1800

< 8.2

UNIT

dB

dBc/Hz

dBc/Hz

mA

mA

mA

mA

dB

Condition

950MHz to 2150MHz

10kHz offset

100kHz offset

3.3V

3.3V

3.3V

1.8V

DVB-S2, Pilot: ON

(*)Method of measuring contact resistance

Center-contact

Insert the gauge pin(0.8mm) to F-connector.

Measure the resistance between the gauge and the center-contact of F-connector.

Outer-shell

Connect the plug(3/8-32 UNEF-2B) to F-connector at 29.4Ncm of the clamping torque.

Measure the resistance between the plug and chassis.

(Measuring device: Milliohm meter)

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

15/19

2.5V

Reg.

4MHz

SDA

LPF

RF OUT

RF IN

HPF

B1A

B1B

B4

(LNB A)(LNB B) 3.3V

B2

3.3V

AGC

CONTROL

AGC Amp.

90deg

SHIFTER

(DIVIDER)

VCO

IX2470VA

PLL

2

IC

LPF

SCL

B3

3.3V

STB0899

Reg.

1.2V

LPF

VDD

1.8V

SCL

SDA

DISEQC_OUT

RESETB

ERROR

DO-D7

CLK_OUT

D/PN

STROUT

[11] BLOCK DIAGRAM

Fig 1. BLOCK DIAGRAM

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

16/19

[12] PIN LIST

No.

1

NAME

B1B

B1A

3

4

B4

B2

5,6,7,10

8

9

11

12

NC

SDA

SCL

B3

DISEQC_

OUT

VDD

D0,...,D7

CLK_OUT

D/PN

STROUT

ERROR

RESETB

13

14,...,21

22

23

24

25

26

LOGIC

3.3V

PIN DESCRIPTION

Voltage supply of LNB B. Please ground it with a 1000pF ceramic

capacitor.

Voltage supply of LNB A. Please ground it with a 1000pF ceramic

capacitor.

3.3V supply for RF Booster Amp of tuner.

3.3V supply for the Front-end section. Please keep a ripple at the Power

Supply less than 10mVp-p.

It is not connected inside the unit. We advice to ground it.

2

I C Bus. Please connect a pull-up resistor which is more than 2k ohm

outside of the tuner.

3.3V supply for demodulator IC. It is internally converted into 2.5V.

Digital satellite equipment control output.

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

1.8V digital core supply. It is internally converted into 1.2V.

Transport stream parallel data.

Transport stream byte or bit clock.

Transport stream data valid signal.

Transport stream sync bit.

Transport stream packet error signal.

Reset signal active low.

3.3V

3.3V

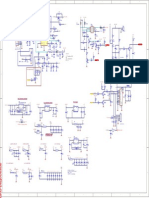

[13] CONECTION DIAGRAM

Fig 2. CONNECTION DIAGRAM

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

17/19

[14] DIMENSION DIAGRAM

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

18/19

[15] MOUNTING DETALIS

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

MODEL No.

SPEC

BS2F7VZ0164

EC-06X02

No.

PAGE

19/19

[16] PACKAGEING DETAILS

pad 3

partition_B x12

partition_C x12

partition_A x42

frame x2

outer_box x1

1948

antistatic_sheet x1

41

0

45

Unitmm

Quantity200pcs

SHARP PROPRIETARY

DEMA Electronic AG | Phone: +49 (0)89 28 69 41 0 | Fax: +49 (0)89 28 35 09 | Email: info@dema.net | Web: http://www.dema.net

You might also like

- PHILIPS LCD Ch-10.1L LLA-32PFL3605D-40PFL3605D PDFDocument71 pagesPHILIPS LCD Ch-10.1L LLA-32PFL3605D-40PFL3605D PDFAlecsandro BatistaNo ratings yet

- Philips Chassis Tpm9.1e LaDocument91 pagesPhilips Chassis Tpm9.1e LaDejan Miladinovic100% (2)

- Philips 32pfl5605 LC9.3LDocument85 pagesPhilips 32pfl5605 LC9.3Ldivubi20040% (1)

- Digital Signal Processing Using the ARM Cortex M4From EverandDigital Signal Processing Using the ARM Cortex M4Rating: 1 out of 5 stars1/5 (1)

- Smoke Alarm - PresentationDocument17 pagesSmoke Alarm - Presentationrenuka dixaNo ratings yet

- c264 en Ad c42Document34 pagesc264 en Ad c42ovucuzidoNo ratings yet

- Furuno Ais Fa100 Service ManualDocument307 pagesFuruno Ais Fa100 Service ManualRumi Amir92% (13)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Cell Phone DetectorDocument51 pagesCell Phone DetectorAnonymous L9fB0XU0% (1)

- SMD MarkcodesDocument308 pagesSMD Markcodestraianbasescuromania72% (32)

- Test Bank For Modern Electronic Communication 9th Edition Jeff Beasley DownloadDocument36 pagesTest Bank For Modern Electronic Communication 9th Edition Jeff Beasley Downloadpainting.hoggeryt759t100% (38)

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- IT Office Relocation PlanningDocument8 pagesIT Office Relocation PlanningsssjNo ratings yet

- Navtex NCR333Document80 pagesNavtex NCR333Sang Aji Jaya Suseno100% (2)

- LG 42LH50 SchematicDocument18 pagesLG 42LH50 SchematicHasan AKNo ratings yet

- ATCA MGW DescriptionDocument21 pagesATCA MGW DescriptionAmitesh AnandNo ratings yet

- Esprimo M9400 - Inventec M11D - Rev AX1Document44 pagesEsprimo M9400 - Inventec M11D - Rev AX1nikola1660No ratings yet

- XBT Xk700eDocument92 pagesXBT Xk700evalentincaciorNo ratings yet

- 32HFL4441D27Document126 pages32HFL4441D27Jim HarmkeNo ratings yet

- Data SheetDocument6 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- SDH QuickDocument8 pagesSDH Quickvosyok1111No ratings yet

- Base Processor Terminal CommandsDocument66 pagesBase Processor Terminal CommandssharadsirohiNo ratings yet

- 42" Plasma PDP Monitor Chassis: Sp-120: MODEL: PDS4250Document62 pages42" Plasma PDP Monitor Chassis: Sp-120: MODEL: PDS4250Vic DiNo ratings yet

- System Controllers: A Navya Vishnu 1210410304Document33 pagesSystem Controllers: A Navya Vishnu 1210410304Ananda KrishnaNo ratings yet

- DLA001Document36 pagesDLA001Rogerio GuimarãesNo ratings yet

- NHD C160100diz FSW FBWDocument15 pagesNHD C160100diz FSW FBWabelincoln1234No ratings yet

- Connecting Ethernet Interface With LPC2000: Rev. 01 - 7 February 2007 Application NoteDocument21 pagesConnecting Ethernet Interface With LPC2000: Rev. 01 - 7 February 2007 Application NoteJorBS57No ratings yet

- MC44BC380Document10 pagesMC44BC380judas_priest_12345No ratings yet

- 04da SDocument2 pages04da SasyfingNo ratings yet

- Manual de Service para TV LED PhilipsDocument108 pagesManual de Service para TV LED Philipstavillo1980No ratings yet

- Cisco 3662 InstallationDocument45 pagesCisco 3662 InstallationsabrinahaileNo ratings yet

- Ecs V10il1 - 37GV10000-C0 - Rev CDocument32 pagesEcs V10il1 - 37GV10000-C0 - Rev CHendra R. Rattu75% (4)

- Microcontrolador msp430g2231Document61 pagesMicrocontrolador msp430g2231Miguel Angel DkNo ratings yet

- VAMP 300-series-NRJED113425EN - 12-2013-Web-260314Document12 pagesVAMP 300-series-NRJED113425EN - 12-2013-Web-260314Hung Cuong PhamNo ratings yet

- Panasonic Model TG6511FXDocument82 pagesPanasonic Model TG6511FXLakiLakicNo ratings yet

- WIZ811MJ Datasheet v1.2Document13 pagesWIZ811MJ Datasheet v1.2ummonkNo ratings yet

- 24 LC 16Document32 pages24 LC 16Jos RoNo ratings yet

- Soxd-Xx99-40 Sinovo TelecomDocument8 pagesSoxd-Xx99-40 Sinovo TelecommelissaNo ratings yet

- MSP 430 F 2132Document77 pagesMSP 430 F 2132Tiago SilvaNo ratings yet

- 12 Catalog SIP E7 Substation AutomationDocument33 pages12 Catalog SIP E7 Substation AutomationsherubdNo ratings yet

- L1 V4 03 MiCOM C264 Hardware Presentation E 01Document42 pagesL1 V4 03 MiCOM C264 Hardware Presentation E 01Rinda_Rayna100% (1)

- CWDM 1x9 155Mb 120km TransceiverDocument11 pagesCWDM 1x9 155Mb 120km TransceiverdogudoguNo ratings yet

- 32PFL5007 - l12m1.1l - LaDocument87 pages32PFL5007 - l12m1.1l - LaWall Bryson100% (1)

- QuotationDocument8 pagesQuotationSelvanathan RathinamNo ratings yet

- Portable Computer Group HW Department: First International Computer, IncDocument50 pagesPortable Computer Group HW Department: First International Computer, Incchiquinho77No ratings yet

- 100G - CFPZR10 - Sofp1-Zr-80Document84 pages100G - CFPZR10 - Sofp1-Zr-80lina zhengNo ratings yet

- PCF8582C-2: 1. DescriptionDocument21 pagesPCF8582C-2: 1. DescriptionroozbehxoxNo ratings yet

- Quick Installation Guide Gdc-600beDocument4 pagesQuick Installation Guide Gdc-600bexelavNo ratings yet

- HS-1840ARH: Rad-Hard 16 Channel CMOS Analog Multiplexer With High-Z Analog Input Protection FeaturesDocument7 pagesHS-1840ARH: Rad-Hard 16 Channel CMOS Analog Multiplexer With High-Z Analog Input Protection FeaturesDeepa DevarajNo ratings yet

- Monet - Manual de Serviço - TV Philips - 40PFL9605D PDFDocument180 pagesMonet - Manual de Serviço - TV Philips - 40PFL9605D PDFCarlos AraujoNo ratings yet

- Sepam RelayDocument46 pagesSepam RelayLawrence AlexNo ratings yet

- Fiber Optic Ieee c37.94 g.703 E1 Multiplexer Pdf2 133Document18 pagesFiber Optic Ieee c37.94 g.703 E1 Multiplexer Pdf2 133nnt236No ratings yet

- TX-l42dt50y Panasonic TX-l42dt50bTX-lr42dt50 TX-l47dt50b TX-l47dt50y TX-lr47dt50 Chassis La35Document69 pagesTX-l42dt50y Panasonic TX-l42dt50bTX-lr42dt50 TX-l47dt50b TX-l47dt50y TX-lr47dt50 Chassis La35BatMudNo ratings yet

- Analog Devices Welcomes Hittite Microwave Corporation: No Content On The Attached Document Has ChangedDocument10 pagesAnalog Devices Welcomes Hittite Microwave Corporation: No Content On The Attached Document Has ChangedDaniel SantosNo ratings yet

- Datasheet Micro M65582AMF-105FPDocument46 pagesDatasheet Micro M65582AMF-105FPsel_mor100% (1)

- STA013Document38 pagesSTA013rohan09No ratings yet

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionFrom EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNo ratings yet

- Service Manual: LCD Color TVDocument78 pagesService Manual: LCD Color TVHasan AKNo ratings yet

- 17mb35 2 SemaDocument12 pages17mb35 2 SemaHasan AKNo ratings yet

- ServiceDocument121 pagesServiceHasan AK0% (1)

- LCD-TV: ServiceDocument79 pagesLCD-TV: ServiceHasan AK0% (1)

- AOC e2252VW (NT68660)Document66 pagesAOC e2252VW (NT68660)Hasan AKNo ratings yet

- Arçelik SX ChasisDocument13 pagesArçelik SX ChasisHasan AKNo ratings yet

- CPI Ku Band Outdoor TWTADocument2 pagesCPI Ku Band Outdoor TWTAHasan AK100% (1)

- A600CG Trouble Shooting Guide - 20140224Document22 pagesA600CG Trouble Shooting Guide - 20140224Hasan AKNo ratings yet

- SM T230 Tshoo 7Document27 pagesSM T230 Tshoo 7Hasan AK0% (2)

- Worcester Bosch 24CDI RSF Spare PartsDocument34 pagesWorcester Bosch 24CDI RSF Spare PartsHasan AKNo ratings yet

- SF300UKDocument60 pagesSF300UKHasan AKNo ratings yet

- Lenovo Ideapad S10-3C (BM5999)Document42 pagesLenovo Ideapad S10-3C (BM5999)rasrozi51700% (1)

- Hyundai l70sDocument50 pagesHyundai l70sHasan AKNo ratings yet

- LX SemaDocument6 pagesLX SemaHasan AKNo ratings yet

- Apt128a Autv 100LDDocument54 pagesApt128a Autv 100LDHasan AKNo ratings yet

- 17MB11 6 SemaDocument10 pages17MB11 6 SemaHasan AKNo ratings yet

- EL6021 - Serial Interface RS422/RS485: Communication Communication CommunicationDocument2 pagesEL6021 - Serial Interface RS422/RS485: Communication Communication Communicationnilton.flavioNo ratings yet

- Test Report: Report No.: KSCR220100006701 Page: 1 of 36Document36 pagesTest Report: Report No.: KSCR220100006701 Page: 1 of 36rolando ojedaNo ratings yet

- WEG Regulador de Tensao Analogico Wrga 01 10000925431 Manual Portugues BRDocument83 pagesWEG Regulador de Tensao Analogico Wrga 01 10000925431 Manual Portugues BRAugusto KozukiNo ratings yet

- Electromagnetic Induction QPDocument7 pagesElectromagnetic Induction QPRaiyan AlamNo ratings yet

- M68HC11Document107 pagesM68HC11Govardhan HegdeNo ratings yet

- Ofcom A Regulator S View On The Private Networks MarketDocument17 pagesOfcom A Regulator S View On The Private Networks MarketSoniaNo ratings yet

- Manual PLC HNC G 4x4y4a-RDocument7 pagesManual PLC HNC G 4x4y4a-RVictor GutiérrezNo ratings yet

- O-Type Tubes - TWTDocument20 pagesO-Type Tubes - TWTmrunal gajbhiyeNo ratings yet

- KANNAD Auto / Manual+ / Manual: Martec Serpe-Iesm Z.I. Des Cinq Chemins 56520 Guidel - FranceDocument34 pagesKANNAD Auto / Manual+ / Manual: Martec Serpe-Iesm Z.I. Des Cinq Chemins 56520 Guidel - FranceParul MehtaNo ratings yet

- An FM PCM30Document2 pagesAn FM PCM30Amir Sohail100% (1)

- Agilent - User Guide 2123123123Document7 pagesAgilent - User Guide 2123123123Mohammad Haroon WaseemNo ratings yet

- LCD 160Document4 pagesLCD 160FRANKNo ratings yet

- TM8000 SDK Developers' Kits - Product Information SheetDocument3 pagesTM8000 SDK Developers' Kits - Product Information SheetAlaa NoorNo ratings yet

- TDS 5054BDocument35 pagesTDS 5054BIlya KhaitNo ratings yet

- 3DR Radio Telemetry Kit - 433 MHZ PDFDocument2 pages3DR Radio Telemetry Kit - 433 MHZ PDFWahyudin LuthfiNo ratings yet

- WOW Electricals Stock ProductsDocument4 pagesWOW Electricals Stock ProductsWOW ElectricalsNo ratings yet

- Catalog Diode ZenerDocument6 pagesCatalog Diode ZenerBorcan CristiNo ratings yet

- Building Bridges of UnderstandingDocument55 pagesBuilding Bridges of UnderstandingmobinilstarNo ratings yet

- LabVIEW Based EIS DataInterpreter 10Document1 pageLabVIEW Based EIS DataInterpreter 10Tushar Kanti BeraNo ratings yet

- Introduction To Instruction Sets: v4T and v7-MDocument14 pagesIntroduction To Instruction Sets: v4T and v7-MMohammed AlzaaninNo ratings yet

- RTC 402Document54 pagesRTC 402Noufal ShajahanNo ratings yet

- IEEE Yellow BookDocument142 pagesIEEE Yellow BookDelmar FerrerNo ratings yet

- Zet-Horn - 131-141 AC - Arctic PDFDocument1 pageZet-Horn - 131-141 AC - Arctic PDFkhanh123ctmNo ratings yet