Professional Documents

Culture Documents

Set Reset Counter Using 7 Segment Display Documentation

Uploaded by

shairaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Set Reset Counter Using 7 Segment Display Documentation

Uploaded by

shairaCopyright:

Available Formats

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

Set-Reset Circuit

Using 7 Segment

Display

Submitted by:

Olid, Shaira Mae (Prototype)

Merlo, Aljune M. (Documentation)

Collado, Jairo Joshua (Prototype)

Mangubat, Raymond (Documentation)

Submitted to:

Engr. Golbandrio Teo

April 7, 2016

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

CHAPTER 1

THE PROBLEM AND ITS BACKGROUND

Introduction

Digital counters are needed everywhere in this digital world,

and 7 segment display is one the best component to display the

numbers. Counters are needed in object/products counters,

digital stopwatches, calculators, timers etc. To use the 7 segment

with ease, there is a 7 segment driver IC which is IC CD4026, so

we are building 7 segment counter circuit using 4026 IC.

Background of the Study

In digital logic and computing, a counter is a device which

stores (and sometimes displays) the number of times a particular

event or process has occurred, often in relationship to a clock

signal. The most common type is a sequential digital logic circuit

with an input line called the "clock" and multiple output lines. The

values on the output lines represent a number in the binary or

BCD number system. Each pulse applied to the clock input

increments or decrements the number in the counter.

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

A counter circuit is usually constructed of a number of flipflops connected in cascade. Counters are a very widely-used

component in digital circuits, and are manufactured as separate

integrated circuits and also incorporated as parts of larger

integrated circuits.

Statement of the Problem

The need of the people to have a digital counters for tallying

is the idea for this project. Tallying is very important especially to

those in the field of statistics.

Scope and Delimitations

The project is only confined to a two separate 2-digit

counter, and a set and reset button. Therefore can only display

00-99.

Significance of the Study

The study will be beneficial to the following:

For Students will serve as reference for their projects

For Teachers will serve as their tools or modules for

teaching

For Others or for anyone who wants to have an easy to

build digital counter

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

CHAPTER 2

THEORETICAL FRAMEWORK

Review of Related Literature & Studies

In electronics, a flip-flop or latch is a circuit that has two

stable states and can be used to store state information. A flipflop is a bistable multivibrator. The circuit can be made to change

state by signals applied to one or more control inputs and will

have one or two outputs. It is the basic storage element in

sequential logic. Flip-flops and latches are a fundamental building

block of digital electronics systems used in computers,

communications, and many other types of systems.

Flip-flops and latches are used as data storage elements. A

flip-flop stores a single bit (binary digit) of data; one of its two

states represents a "one" and the other represents a "zero". Such

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

data storage can be used for storage of state, and such a circuit

is described as sequential logic. When used in a finite-state

machine, the output and next state depend not only on its current

input, but also on its current state (and hence, previous inputs). It

can also be used for counting of pulses, and for synchronizing

variably-timed input signals to some reference timing signal.

Flip-flops can be either simple (transparent or opaque) or

clocked (synchronous or edge-triggered). Although the term flipflop has historically referred generically to both simple and

clocked circuits, in modern usage it is common to reserve the

term flip-flop exclusively for discussing clocked circuits; the

simple ones are commonly called latches.[1][2]

Using this terminology, a latch is level-sensitive, whereas a

flip-flop is edge-sensitive. That is, when a latch is enabled it

becomes transparent, while a flip flop's output only changes on a

single type (positive going or negative going) of clock edge.

A bistable multivibrator has two stable states, as indicated

by the prefix bi in its name. Typically, one state is referred to

as set and the other as reset. The simplest bistable device,

therefore, is known as a set-reset, or S-R, latch.

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

To create an S-R latch, we can wire two NOR gates in such a

way that the output of one feeds back to the input of another,

and vice versa, like this:

The Q and not-Q outputs are supposed to be in opposite

states. I say supposed to because making both the S and R

inputs equal to 1 results in both Q and not-Q being 0. For this

reason, having both S and R equal to 1 is called

an invalid or illegal state for the S-R multivibrator. Otherwise,

making S=1 and R=0 sets the multivibrator so that Q=1 and

not-Q=0. Conversely, making R=1 and S=0 resets the

multivibrator in the opposite state. When S and R are both equal

to 0, the multivibrators outputs latch in their prior states.

Note how the same multivibrator function can be implemented

in ladder logic, with the same results:

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

By definition, a condition of Q=1 and not-Q=0 is set. A

condition of Q=0 and not-Q=1 is reset. These terms are

universal in describing the output states of any multivibrator

circuit.

The astute observer will note that the initial power-up

condition of either the gate or ladder variety of S-R latch is such

that both gates (coils) start in the de-energized mode. As such,

one would expect that the circuit will start up in an invalid

condition, with both Q and not-Q outputs being in the same

state. Actually, this is true! However, the invalid condition is

unstable with both S and R inputs inactive, and the circuit will

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

quickly stabilize in either the set or reset condition because one

gate (or relay) is bound to react a little faster than the other. If

both gates (or coils) were precisely identical, they would

oscillate between high and low like an astable multivibrator

upon power-up without ever reaching a point of stability!

Fortunately for cases like this, such a precise match of

components is a rare possibility.

It must be noted that although an astable (continually

oscillating) condition would be extremely rare, there will most

likely be a cycle or two of oscillation in the above circuit, and

the final state of the circuit (set or reset) after power-up would

be unpredictable. The root of the problem is a race

condition between the two relays CR1 and CR2.

A race condition occurs when two mutually-exclusive

events are simultaneously initiated through different circuit

elements by a single cause. In this case, the circuit elements

are relays CR1 and CR2, and their de-energized states are

mutually exclusive due to the normally-closed interlocking

contacts. If one relay coil is de-energized, its normally-closed

contact will keep the other coil energized, thus maintaining the

circuit in one of two states (set or reset). Interlocking

prevents both relays from latching. However, if both relay coils

start in their de-energized states (such as after the whole circuit

has been de-energized and is then powered up) both relays will

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

race to become latched on as they receive power (the single

cause) through the normally-closed contact of the other relay.

One of those relays will inevitably reach that condition before

the other, thus opening its normally-closed interlocking contact

and de-energizing the other relay coil. Which relay wins this

race is dependent on the physical characteristics of the relays

and not the circuit design, so the designer cannot ensure which

state the circuit will fall into after power-up.

Race conditions should be avoided in circuit design

primarily for the unpredictability that will be created. One way

to avoid such a condition is to insert a time-delay relay into the

circuit to disable one of the competing relays for a short time,

giving the other one a clear advantage. In other words, by

purposely slowing down the de-energization of one relay, we

ensure that the other relay will always win and the race

results will always be predictable. Here is an example of how a

time-delay relay might be applied to the above circuit to avoid

the race condition:

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

When the circuit powers up, time-delay relay contact TD 1 in

the fifth rung down will delay closing for 1 second. Having that

contact open for 1 second prevents relay CR 2 from energizing

through contact CR1 in its normally-closed state after power-up.

Therefore, relay CR1 will be allowed to energize first (with a 1second head start), thus opening the normally-closed

CR1 contact in the fifth rung, preventing CR2 from being

energized without the S input going active. The end result is

that the circuit powers up cleanly and predictably in the reset

state with S=0 and R=0.

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

It should be mentioned that race conditions are not

restricted to relay circuits. Solid-state logic gate circuits may

also suffer from the ill effects of race conditions if improperly

designed. Complex computer programs, for that matter, may

also incur race problems if improperly designed. Race problems

are a possibility for any sequential system, and may not be

discovered until some time after initial testing of the system.

They can be very difficult problems to detect and eliminate.

A practical application of an S-R latch circuit might be for

starting and stopping a motor, using normally-open, momentary

pushbutton switch contacts for both start (S) and stop (R)

switches, then energizing a motor contactor with either a CR 1 or

CR2 contact (or using a contactor in place of CR 1 or CR2).

Normally, a much simpler ladder logic circuit is employed, such

as this:

In the above motor start/stop circuit, the CR 1 contact in

parallel with the start switch contact is referred to as a seal-in

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

contact, because it seals or latches control relay CR 1 in the

energized state after the startswitch has been released. To

break the seal, or to unlatch or reset the circuit,

the stop pushbutton is pressed, which de-energizes CR1 and

restores the seal-in contact to its normally open status. Notice,

however, that this circuit performs much the same function as

the S-R latch. Also note that this circuit has no inherent

instability problem (if even a remote possibility) as does the

double-relay S-R latch design.

In semiconductor form, S-R latches come in prepackaged

units so that you dont have to build them from individual gates.

They are symbolized as such:

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

Definition of Terms

Counter- is an apparatus used for counting.

Sequential logic- is a form of binary circuit design that

employs one or more inputs and one or more outputs

Flip-flops- also called bistable gates, are digital logic

circuits that can be in one of two states. Flip-flops maintain

their state indefinitely until an input pulse called a trigger is

received. When a trigger is received, the flip-flop outputs

change state according to defined rules and remain in those

states until another trigger is received. Flip-flop circuits are

interconnected to form the logic gates for the digital

integrated circuits (IC s) used in memory chips and

microprocessors. Flip-flops can be used to store one bit, or

binary digit, of data. The data may represent the state of a

sequencer, the value of a counter, an ASCII character in a

computer's memory or any other piece of information.

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

CHAPTER 3

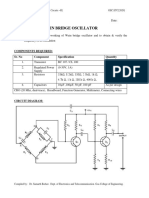

TECHNICAL SPECIFICATIONS

Hardware Specifications

The components we used are the following:

Seven Segment Display

It consists 8 LEDs, each LED used to illuminate one segment/line

of the unit and the 8thLED used to illuminate DOT in 7 segment

display. We can refer each line/segment "a,b,c,d,e,f,g" and for dot

character we will use "h". There are 10 pins, in which 8 pins are

used to refer a,b,c,d,e,f,g and h/dp, the two middle pins are

common anode/cathode of all he LEDs.

IC 4026

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

IC 4026 is used to drive common cathode 7 segment display. In

common cathode 7 segment display cathodes of all the LEDs are

connected together, and all the positive terminals are left alone.

Push button

Press-ON-Press-OFF soft toggle action, where a short button press

of a tactile switch latches the circuit ON and another toggles it

back OFF; or, A Press-ON-Hold-OFF action, where a short press

turns power to a circuit ON, but a longer button hold is needed to

toggle it OFF.

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

Miscellaneous

Resistors (1k ohms)

Capacitors (0.1 uF and 22uF)

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

Software Specifications

Multisim

Multisim simulation and circuit design software gives

engineers the advanced analysis and design capabilities to

optimize performance, reduce design errors, and shorten time to

prototype. Intuitive NI tools result in saved printed circuit board

(PCB) iterations and significant cost savings

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

Logisim

Logisim is an educational tool for designing and simulating

digital logic circuits. With its simple toolbar interface and

simulation of circuits as you build them, it is simple enough to

facilitate learning the most basic concepts related to logic

circuits. With the capacity to build larger circuits from smaller

subcircuits, and to draw bundles of wires with a single mouse

drag, Logisim can be used (and is used) to design and simulate

entire CPUs for educational purposes.

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

CHAPTER 4

PRESENTATION AND ANALYSIS OF THE FINDINGS

Applications

Digital counters and 7 segment display are used in the following:

Digital clock

Calculator

Electronic meters

Pulse counter

Advantages and Disadvantages

Easy to build circuit

It can use up to 2 or more 7 segment each one having an IC

4026

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

It can be used as a tallying purpose or pulse counter

Monostable circuit used for the sync of the counter to count

up, must use correct capacitors to get the correct length of

how long the circuit will count up

Sensitive IC 4026.

It requires a lot of time to achieved correct connection to

each pins up to 7 segment display.

CHAPTER 5

CONCLUSIONS & RECOMMENDATIONS

Conclusions

Using IC4026 and 7 segment display comes a simple digital

counter with set-reset function. The complexity of the circuit

might be confusing but being careful with regards to the

schematic diagram is the key.

Recommendations

We highly recommend this project to anyone who wants to

build a simple digital counter with a set and reset function for any

educational or whatever purposes it may serve. And because the

project can only display 00-99, we recommend others to build a

digital counter with more 7 segment display.

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

References

http://circuitdigest.com/electronic-circuits/555-timerseven-segment-counter-circuit

http://electroniccircuitsforbeginners.blogspot.com/2010/1

1/applications-of-sequential-logic.html

http://www.tutorialspoint.com/computer_logical_organizati

on/digital_counters.html

http://www.ni.com/example/14496/en/

http://whatis.techtarget.com/definition/counter

http://www.allaboutcircuits.com/textbook/digital/chpt10/s-r-latch/

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

Appendices

RESEARCHERS

Circuit

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

Finished Product

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

Researchers Profile

ALJUNE M. MERLO

Address

Contact Number

Email

:177 ULNA Street, West Fairview, Quezon City.

:09107353545

:almerlss012@gmail.com

PERSONALINFORMATION

Nickname

Age

Date of Birth

Place of Birth

Gender

Height

Weight

Civil Status

Religion

Language/s Spoken

Name of Father

Occupation

Name of Mother

Occupation

: Al

: 19 years old

: March 12, 1997

: San Carlos, Negros Occidental

: Male

: 56

: 48 kgs

: Single

: Roman Catholic

: Filipino/English

: Alejandro Merlo

: Vendor

:Juana Merlo

: Housewife

EDUCATIONAL BACKGROUND

Tertiary

: Quezon City Polytechnic University

Bachelor of Science in Electronics and Communications Engineering

673 Quirino Hi-way, San Bartolome, Novaliches Quezon City

2013-Present

Secondary

: Sauyo High School

2nd Laguna Street, Sauyo, Novaliches, Quezon City.

2009-2013

Primary

: Sauyo Elementary School

Del Nacia Village, Sauyo, Novaliches, Quezon City.

2003-2009

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

SHAIRA MAE OLID

Address

Contact Number

:Lot 15 Cmpd 10 King William Street, Kasiyahan Village, Novaliches, Q.C

:09988642670

:olidshaira@gmail.com

PERSONALINFORMATION

Nickname

Age

Date of Birth

Place of Birth

Gender

Height

Weight

Civil Status

Religion

Language/s Spoken

Name of Father

Occupation

Name of Mother

Occupation

: Shai

: 19 years old

: December 09, 1996

: Quezon City

: Female

: 52

: 60 kgs

: Single

: Roman Catholic

: Filipino/English

: Ferdinand T. Olid

: Hospital Employee

:Liezl A. Olid

: Housewife

EDUCATIONAL BACKGROUND

Tertiary

: Quezon City Polytechnic University

Bachelor of Science in Electronics and Communications Engineering

673 Quirino Hi-way, San Bartolome, Novaliches Quezon City

2013-Present

Secondary

: Francisco School

#046 Quirino Highway Baesa, Quezon City.

2009-2013

Primary

: Placido Del Mundo Elementary School

Talipapa, Quezon City.

2003-2009

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

RAYMOND MANGUBAT

Address

Contact Number

Email

:Blk 10 Lot 20, Mirandaville, Bryg, Kaligayaha Novaliches, Q.C

:09186350468

:mangubatraymond30@gmail.com

PERSONALINFORMATION

Nickname

Age

Date of Birth

Place of Birth

Gender

Height

Weight

Civil Status

Religion

Language/s Spoken

Name of Father

Occupation

Name of Mother

Occupation

: Mond

: 23 years old

: November 30,1992

: Quezon City

: Male

: 56

: 59 kgs

: Single

: Roman Catholic

: Filipino/English

: Loloy Mangubat

: Welder

:Evelyn Mangubat

: Great Mom,

EDUCATIONAL BACKGROUND

Tertiary

: Quezon City Polytechnic University

Bachelor of Science in Electronics and Communications Engineering

673 Quirino Hi-way, San Bartolome, Novaliches Quezon City

2013-Present

Secondary

: Novaliches High School

TS-Crus Lakandula st,Brgy,Kaligayahan Novaliches, Quezon City.

2006-2011

Primary

: San Agustis Elemntery School,

San, Agustin Bryg, Kaligayahan Novaliches Quezon City.

2000-2006

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

JAIRO JOSHUA COLLADO

Address

Contact Number

:Blk 10 Lot 20, Mirandaville, Bryg, Kaligayaha Novaliches, Q.C

:09186350468

:mangubatraymond30@gmail.com

PERSONALINFORMATION

Nickname

Age

Date of Birth

Place of Birth

Gender

Height

Weight

Civil Status

Religion

Language/s Spoken

Name of Father

Occupation

Name of Mother

Occupation

: Jairo

: 20 years old

: November 22,1995

: Quezon City

: Male

: 59

: 85 kgs

: Single

: Christian

: Filipino/English

: Rodolfo Collado

: Retired Businessman

:Milagros Collado

: Government Employee

EDUCATIONAL BACKGROUND

Tertiary

: Quezon City Polytechnic University

Bachelor of Science in Electronics and Communications Engineering

673 Quirino Hi-way, San Bartolome, Novaliches Quezon City

2013-Present

Secondary

: San Francisco Highs School

Misamis St. Proj,6 Brgy. Bagong Pag asa

2008-2012

Primary

: People Of Grace Christian School

Judge Jimenez St. Cor. Kamuning St. Brgy Sacred heart.

2002-2008

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

REACTION PAPER FOR

ACADEMIC EXPOSURE

ACTIVITIES

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

The project was part of our academic curriculum which

enable us to perform and create certain ideas, methods and to

improve our skills using electronic components. This project is

started in the middle of March 2016.

Background

Timers were originally designed to fulfill a need in industry

for a means of keeping time on certain devices. Originally, these

timers were mechanical devices and used clockwork mechanisms

as a means of keeping a regular time (Timer, 2006). The invention

of two electromechanical timer designs allowed for more precise

time measurement. The first uses the principle of heat expansion

to increase the temperature of a metal finger made of two

different metals with differing rates of thermal expansion (Timer,

2006). As electric current flows through the metal, it begins to

heat and one side expands more quickly than the other which, in

turn, moves the electrical contact away from an electrical switch

contact. The second uses a small AC motor which turns at a

predetermined rate due to the application of an alternating

current (Timer, 2006). Finally, digital timers were invented. Digital

logic circuits are now so cheap that it has become a better

investment to buy a digital timer than a mechanical or

electromechanical timer. Individual timers are implemented with

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

single chip circuits, similar to a watch (Timer, 2006). The 555

timer used in this project is a combination of a digital logic circuit

and analogue component

Summary of Learnings

We learned the functions of the following components that

has been used in our project to build the circuit of it.

555 timer 555 timers are integrated timing circuits which

are used commonly as a source of clock pulses to drive

subsequent timer circuits.

IC 4026 is a 4000 series IC. It is a CMOS seven-segment

counter IC and can be operated at very low power. It is a

decade counter, counts in decimal digits (0-9).

7-segment Display an LED or Light Emitting Diode, is a solid

state optical PN-Junction diode which emits light energy in

the form of photos. Usually be seen in the as digital

indicators which involves numerical forms.

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

These are the main components which we used in order to

make the project. By combining the components and following

the schematic diagram that we used for basis, and several tries to

run the circuit, we have completed and finished the project. The

connection of wires to the components are the trickiest part of

assembling of the circuit, yet we manage to finish it.

Analysis/Synthesis

By the combination of the following components, which consist

of RESISTORS, CAPACITORS, and IC 4026, CMOS 7-SEGMENT

COUNTER. We have created a project which can provide counting

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

of numbers for the purpose of tallying certain topics, which

involves students. By the guidance of certain tutorial sites, we

have assembled this project, includes certain specifics like an

additional 7segment counters.

Conclusion and Recommendation

Based on our experience, the more components we used,

the more complex the circuit would be, and will be difficult to

analyze yet, the result would be more satisfying. Being careless

and not paying attention in the schematic would be a problem in

assembling the circuit, because there are some schematics that

are not that accurate. This type of project is very useful because

of the counting process. But it needs to be improved and add

more specifications. Due to limited resources, we manage to

accomplish this type of project. We recommend to add more

Quezon City Polytechnic University

673 Quirino Highway, San Bartolome

Novaliches, Quezon City

TEL NOS.: 332-5003 / 468-5021 to 22

functions, although the complexity of the circuit would be more

difficult.

You might also like

- Combinational Circuits LDICDocument129 pagesCombinational Circuits LDIChemanth ramireddyNo ratings yet

- Digital Pulse Counter - Two Digits: DescriptionDocument7 pagesDigital Pulse Counter - Two Digits: DescriptionAsgher KhattakNo ratings yet

- Closed Loop DC Motor Speed ControlDocument3 pagesClosed Loop DC Motor Speed ControlKhayaz KunhabduNo ratings yet

- 555 TimerDocument26 pages555 TimerEngr Wahab MarwatNo ratings yet

- Magnetic Fields of Coils: Lab Report 7Document5 pagesMagnetic Fields of Coils: Lab Report 7StacyNo ratings yet

- PK7 UNO to PC communicationDocument3 pagesPK7 UNO to PC communicationDan M Stone100% (1)

- MergedDocument34 pagesMergedmahamaniNo ratings yet

- Experiment no. 2 Aim: - Theory: c1 (t) = √2/Tb cos 2πƒ1tDocument6 pagesExperiment no. 2 Aim: - Theory: c1 (t) = √2/Tb cos 2πƒ1tMudit GoelNo ratings yet

- 15ecl48 VTU Raghudathesh R 2r DacDocument5 pages15ecl48 VTU Raghudathesh R 2r Dacraghudatheshgp100% (1)

- Digital CounterDocument18 pagesDigital CounterbotakezuNo ratings yet

- Chapter 4Document17 pagesChapter 4haiqa suhailNo ratings yet

- A-Law and U-Law CompandingDocument4 pagesA-Law and U-Law CompandingAchyut Dev50% (2)

- Unit VDocument168 pagesUnit VrajaganabathiNo ratings yet

- Sap 1Document54 pagesSap 1Israr Ahmad Dawar100% (3)

- Digital Electronics Circuits: Experiment: 9Document4 pagesDigital Electronics Circuits: Experiment: 9movabNo ratings yet

- Light Intensity ControlDocument8 pagesLight Intensity ControlRaman GargNo ratings yet

- 0-99 Counter Circuit Project Using 4026 & 555 Timer ICsDocument7 pages0-99 Counter Circuit Project Using 4026 & 555 Timer ICsyashu50% (2)

- K-Map Method for Logic MinimizationDocument57 pagesK-Map Method for Logic MinimizationHugh100% (1)

- Sequential Logic BasicsDocument20 pagesSequential Logic Basicskhairalla mohamedNo ratings yet

- Single Phase Full Wave Voltage Multiplier PDFDocument3 pagesSingle Phase Full Wave Voltage Multiplier PDFJoshua Amiel javines0% (1)

- Lecture Notes: Digital Logic DesignDocument66 pagesLecture Notes: Digital Logic DesignJyoti GroverNo ratings yet

- CH 4Document71 pagesCH 4asisha mostNo ratings yet

- Experiment-7 Design A Binary Subtractor Circuit Half and Full Subtractor 7-1 ObjectDocument4 pagesExperiment-7 Design A Binary Subtractor Circuit Half and Full Subtractor 7-1 ObjectMohammed Dyhia AliNo ratings yet

- Basic Electronics Lab ManualDocument47 pagesBasic Electronics Lab ManualAlpesh ThesiyaNo ratings yet

- Basic Idea of Counters Asynchronous (Ripple) Counter Using Flip-FlopsDocument16 pagesBasic Idea of Counters Asynchronous (Ripple) Counter Using Flip-FlopsSelvasundar KumarNo ratings yet

- Expt 5 - Wein Bridge Oscillator (2020)Document3 pagesExpt 5 - Wein Bridge Oscillator (2020)samarthNo ratings yet

- Pneumatics Activity 2Document2 pagesPneumatics Activity 2Jay Mark BalaneNo ratings yet

- AC Circuits: Fundamentals of Electric CircuitsDocument16 pagesAC Circuits: Fundamentals of Electric CircuitsHiếu Dương100% (1)

- Lab Manual DAC-SignedDocument10 pagesLab Manual DAC-Signedabidrk_21789100% (2)

- ECD Lab EEC 752Document17 pagesECD Lab EEC 752juhi99360% (5)

- Chap 3 Signal Conditioning CircuitDocument26 pagesChap 3 Signal Conditioning CircuitMuhammed I'zwanNo ratings yet

- Study Report DRR Budanilkantha-12Document37 pagesStudy Report DRR Budanilkantha-12sudip100% (1)

- CH - 1 Digital SystemsDocument44 pagesCH - 1 Digital SystemsRaquel BarretoNo ratings yet

- Electrical Circuits LabDocument64 pagesElectrical Circuits LabraveendrababupNo ratings yet

- Iecep EstDocument16 pagesIecep EstRystelle ArganaNo ratings yet

- Delta ModulationDocument44 pagesDelta ModulationJyotirmoy DekaNo ratings yet

- Generation of WaveformsDocument9 pagesGeneration of WaveformsNivas Kumar SureshNo ratings yet

- CRT, LCD, LED, TV Technologies Like Liquid Crystal DisplayDocument28 pagesCRT, LCD, LED, TV Technologies Like Liquid Crystal DisplayKundan VanamaNo ratings yet

- MEC522: Control Engineering PBL AssignmentDocument3 pagesMEC522: Control Engineering PBL Assignmentanisalyaa100% (1)

- Amplitude Modulation & Demodulation Using MATLAB & MultiSimDocument13 pagesAmplitude Modulation & Demodulation Using MATLAB & MultiSimPavan SaiNo ratings yet

- BCD To 7 Segment Display ProjectnewDocument5 pagesBCD To 7 Segment Display ProjectnewSaeed Ali ShahaniNo ratings yet

- Elect Machine Total 2012Document22 pagesElect Machine Total 2012NGOUNENo ratings yet

- Theory:: Experiment No. 6 Implementation of Full Adder and Full Subtractor Using Logic Gates ObjectiveDocument8 pagesTheory:: Experiment No. 6 Implementation of Full Adder and Full Subtractor Using Logic Gates ObjectiveMusic LifeNo ratings yet

- Lab Experiment No: 03 Lab Report On Adder and Subtractor: Abul Barkat Mollah Sayeed Ud Doulah, PHD Dewan Rodela AshrafiDocument7 pagesLab Experiment No: 03 Lab Report On Adder and Subtractor: Abul Barkat Mollah Sayeed Ud Doulah, PHD Dewan Rodela AshrafiIrene SultanaNo ratings yet

- Microwave Engineering Experiments RGPVDocument28 pagesMicrowave Engineering Experiments RGPVYash JainNo ratings yet

- ST2611 PDFDocument1 pageST2611 PDFROHITCHOURASIYANo ratings yet

- SyllabusDocument5 pagesSyllabusChandan Prasai100% (1)

- Logic Design Lab Manual 10ESL38 3rd Sem 2013Document61 pagesLogic Design Lab Manual 10ESL38 3rd Sem 2013vishvakirana75% (4)

- Unit Ii: Digital ProtectionDocument55 pagesUnit Ii: Digital ProtectionViswanathanBalajiNo ratings yet

- How Does Microprocessor Differentiate Between Data and InstructionDocument60 pagesHow Does Microprocessor Differentiate Between Data and InstructionUbaid Saudagar100% (1)

- Embedded System Components: Module-3Document40 pagesEmbedded System Components: Module-3balajibs203285No ratings yet

- Dynamic Traffic Light Control Using Microcontroller: Industrial and Control EngineeringDocument49 pagesDynamic Traffic Light Control Using Microcontroller: Industrial and Control EngineeringTalemaNo ratings yet

- Study of A 8086 Trainer KitDocument6 pagesStudy of A 8086 Trainer KitVENKI0% (1)

- Term Paper Advantages of RTL DTL and TTLDocument5 pagesTerm Paper Advantages of RTL DTL and TTLDebashis Paul100% (2)

- Sequential Logic Circuits Types and ApplicationsDocument67 pagesSequential Logic Circuits Types and ApplicationsAngelica FangonNo ratings yet

- Group2 Ece142Document61 pagesGroup2 Ece142Angelica FangonNo ratings yet

- Sequential Logic Circuits Types and ApplicationsDocument66 pagesSequential Logic Circuits Types and ApplicationsAngelica FangonNo ratings yet

- Sequential Circuits PDFDocument8 pagesSequential Circuits PDFXavier SebastiaoNo ratings yet

- Ecole Nationale Polytechnique Sequential Circuits LabDocument4 pagesEcole Nationale Polytechnique Sequential Circuits LabBoualem MestafaNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Deed of Absolute SaleDocument2 pagesDeed of Absolute SaleshairaNo ratings yet

- MCQs ENGINEERING MATHEMATICS LICENSURE EXAMDocument83 pagesMCQs ENGINEERING MATHEMATICS LICENSURE EXAMJeric Ponteras61% (18)

- USB PortDocument25 pagesUSB PortshairaNo ratings yet

- Intro GPSDocument21 pagesIntro GPSBalasi SimonaNo ratings yet

- Gps SystemDocument33 pagesGps SystemFahad QureshiNo ratings yet

- Advantages and DisadvantagesDocument1 pageAdvantages and DisadvantagesshairaNo ratings yet

- FinalDocument7 pagesFinalshairaNo ratings yet

- DC GeneratorDocument18 pagesDC GeneratorshairaNo ratings yet

- AsmDocument19 pagesAsmshairaNo ratings yet

- Quezon City Polytechnic University: College of EngineeringDocument4 pagesQuezon City Polytechnic University: College of EngineeringshairaNo ratings yet

- Quezon City Polytechnic University: I. ObjectivesDocument10 pagesQuezon City Polytechnic University: I. ObjectivesshairaNo ratings yet

- Smith Chart From Black Magic DesignDocument1 pageSmith Chart From Black Magic DesignkgrhoadsNo ratings yet

- LetterheadDocument1 pageLetterheadshairaNo ratings yet

- AC MotorDocument20 pagesAC MotorshairaNo ratings yet

- Advanced MathDocument24 pagesAdvanced MathshairaNo ratings yet

- Duck WhiskDocument3 pagesDuck WhiskshairaNo ratings yet

- Sigma: Amplitude Modulation/ Demodulation System Trainer Model - Com101Document29 pagesSigma: Amplitude Modulation/ Demodulation System Trainer Model - Com101Vương Thành ĐôNo ratings yet

- Space Division MultiplexingDocument1 pageSpace Division Multiplexingx3b0No ratings yet

- 2021 EMC Fundamentals GuideDocument49 pages2021 EMC Fundamentals GuidewulanluvspinkNo ratings yet

- Beyond CMOS Devices and ArchitecturesDocument93 pagesBeyond CMOS Devices and ArchitecturesAadil Sh100% (1)

- TN2 12VDocument5 pagesTN2 12VJavierPariNo ratings yet

- MS-Micro Electronics SyllabusDocument19 pagesMS-Micro Electronics SyllabusUpendra KumarNo ratings yet

- R01an1115ej0300 Rl78i1aDocument95 pagesR01an1115ej0300 Rl78i1aBantunegerNo ratings yet

- Dell XPS 14z Schematics VersionDocument52 pagesDell XPS 14z Schematics VersionDevender kumarNo ratings yet

- SMT ConsumableDocument20 pagesSMT ConsumableLam HoangNo ratings yet

- Workshop Brochure LATEXnewDocument3 pagesWorkshop Brochure LATEXnewabhishekNo ratings yet

- MOTOR PROTECTION RELAYS for Total Peace of MindDocument9 pagesMOTOR PROTECTION RELAYS for Total Peace of MindSrikanth NakkaNo ratings yet

- High Power Loader ManualDocument7 pagesHigh Power Loader ManualOSAMANo ratings yet

- C18 Accelerating and Deceleerating MethodsDocument59 pagesC18 Accelerating and Deceleerating Methodssathishkumar3eNo ratings yet

- Crompton DC MotorsDocument6 pagesCrompton DC MotorsAzed-dine BoughmarNo ratings yet

- Evs4343 (G) Um Com en 04Document44 pagesEvs4343 (G) Um Com en 04Chung Tbyt Da NangNo ratings yet

- 100 Gbps Dual-Polarization QPSK Long-Haul Communication SystemDocument22 pages100 Gbps Dual-Polarization QPSK Long-Haul Communication SystemDeepak KumarNo ratings yet

- Boiler Controller With Programmable Temperature: A Mini Project Report OnDocument43 pagesBoiler Controller With Programmable Temperature: A Mini Project Report OnSai Kireeti YalamanchiliNo ratings yet

- Ac Part 4Document10 pagesAc Part 4Lester James SaingNo ratings yet

- 19bec149 Exp7 CaDocument8 pages19bec149 Exp7 CaZINZUVADIYA ABHISHEKNo ratings yet

- DC motor voltage, current and power calculationsDocument10 pagesDC motor voltage, current and power calculationsJohn Miko JavierNo ratings yet

- Emergency Switchboard PDFDocument162 pagesEmergency Switchboard PDFPaul Lucian Ventel100% (3)

- Calibracion E69PDocument16 pagesCalibracion E69PmktcableNo ratings yet

- E7290ax Mammography TubeDocument14 pagesE7290ax Mammography TubeHarold FernandezNo ratings yet

- Service Manual: Mobile Terminal (V1.0)Document38 pagesService Manual: Mobile Terminal (V1.0)Cesra HMNo ratings yet

- Understanding the Basics of Television TechnologyDocument33 pagesUnderstanding the Basics of Television TechnologyThs TeekoyNo ratings yet

- Harare Power StationDocument4 pagesHarare Power StationGideon MoyoNo ratings yet

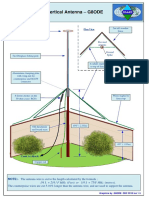

- 20m Elevated Vertical Antenna DesignDocument5 pages20m Elevated Vertical Antenna Designleonardo_manzanoNo ratings yet

- Seongil IM - Yonsei UniversityDocument36 pagesSeongil IM - Yonsei UniversityMartinNo ratings yet

- Ee 310 SyllabusDocument2 pagesEe 310 SyllabusAshwin K ShettyNo ratings yet

- M.tech .Electronics071011Document49 pagesM.tech .Electronics071011John WilliamNo ratings yet