Professional Documents

Culture Documents

A3979 Datasheet

Uploaded by

Иван КосмонавтOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A3979 Datasheet

Uploaded by

Иван КосмонавтCopyright:

Available Formats

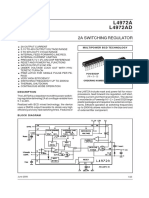

A3979

Microstepping DMOS Driver with Translator

Features and Benefits

Description

The A3979 is a complete microstepping motor driver with

built-in translator, designed as a pin-compatible replacement for

the successful A3977, with enhanced microstepping (1/16 step)

precision. It is designed to operate bipolar stepper motors in

full-, half-, quarter-, and sixteenth-step modes, with an output

drive capacity of up to 35 V and 2.5 A. The A3979 includes a

fixed off-time current regulator that has the ability to operate in

Slow, Fast, or Mixed decay modes. This current-decay control

scheme results in reduced audible motor noise, increased step

accuracy, and reduced power dissipation.

2.5 A, 35 V output rating

Low RDS(On) outputs: 0.28 source, 0.22 sink, typical

Automatic current decay mode detection/selection

3.0 to 5.5 V logic supply voltage range

Slow, Fast or Mixed current decay modes

Home output

Synchronous rectification for low power dissipation

Internal UVLO and thermal shutdown circuitry

Crossover-current protection

Package: 28 lead TSSOP (suffix LP) with

exposed thermal pad

The translator is the key to the easy implementation of the

A3979. It allows the simple input of one pulse on the STEP

pin to drive the motor one microstep, which can be either a full

step, half, quarter, or sixteenth, depending on the setting of the

MS1 and MS2 logic inputs. There are no phase-sequence tables,

high-frequency control lines, or complex interfaces to program.

The A3979 interface is an ideal fit for applications where a

complex microprocessor is unavailable or is overburdened.

Internal synchronous-rectification control circuitry is provided

to improve power dissipation during PWM operation. Internal

circuit protection includes: thermal shutdown with hysteresis,

UVLO (undervoltage lockout), and crossover-current

protection. Special power-on sequencing is not required.

The A3979 is supplied in a low-profile (height 1.20 mm),

28-pin TSSOP with exposed thermal pad. The package is lead

(Pb) free, with 100% matte tin leadframe plating.

Not to scale

Pin-out Diagram

SENSE1 1

28 VBB1

HOME 2

27 SLEEP

DIR 3

26 ENABLE

OUT1A 4

PFD 5

RC1 6

25 OUT1B

AGND 7

REF 8

RC2 9

VDD 10

24 CP2

PWM

Timer

Translator

and

Control

Logic

Charge

Pump

23 CP1

22 VCP

21 PGND

Reg

20 VREG

19 STEP

OUT2A 11

18 OUT2B

MS2 12

17 RESET

MS1 13

16 SR

SENSE2 14

15 VBB2

AGND and PGND must be

connected together externally

26184.23F

A3979

DMOS Microstepping Driver with Translator

Selection Guide

Part Number

Packing

A3979SLPTR-T

4000 pieces per reel

Absolute Maximum Ratings

Load Supply Voltage

VBB

Output Current

IOUT

Logic Supply Voltage

VDD

Logic Input Voltage Range

Sense Voltage

Reference Voltage

Operating Ambient Temperature

VIN

Output current rating may be limited by duty cycle,

ambient temperature, and heat sinking. Under any set of

conditions, do not exceed the specified current rating or a

junction temperature of 150C.

2.5

7.0

tW > 30 ns

0.3 to VDD + 0.3

tW < 30 ns

1 to VDD + 1

0.5

VSENSE

VREF

TA

35

Range S

VDD

20 to 85

Junction Temperature

TJ(max)

150

Storage Temperature

Tstg

55 to 150

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

Functional Block Diagram

0.22 F

0.22 F

CP2

VREG

Logic

Supply

CP1

2V

VDD

UVLO and

Fault

Regulator

Bandgap

Charge

Pump

VCP

Reference

Supply

0.22 F

Load

Supply

REF

DAC

DMOS Full Bridge

VBB1

RC1

>47 F

RT1

CT1

OUT1A

STEP

OUT1B

DIR

PWM Timer:

PWM Latch

Blanking

Mixed Decay

RESET

MS1

Translator

MS2

SENSE1

RS1

Gate

Drive

HOME

CS1

SLEEP

Control

Logic

SR

DMOS Full Bridge

VBB2

ENABLE

OUT2A

VPFD

PFD

0.1 F

RC2

RT2

OUT2B

PWM Timer:

PWM Latch

Blanking

Mixed Decay

CT2

SENSE2

RS2

DAC

CS2

Exposed Thermal Pad

AGND

PGND

(Required)

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

ELECTRICAL CHARACTERISTICS at TA = 25C, VBB = 35 V, VDD = 3.0 to 5.5 V (unless otherwise noted)

Characteristics

Output Drivers

Symbol

Load Supply Voltage Range

VBB

Output Leakage Current2

IDSS

Output On Resistance

RDS(On)

Body Diode Forward Voltage

VF

Motor Supply Current

IBB

Control Logic

Logic Supply Voltage Range

VDD

Logic Supply Current

IDD

Logic Input Voltage

Logic Input Current2

Reference Input Voltage Range

Reference Input Current

HOME Output Voltage

Mixed Decay Mode Trip Point

Gain (Gm) Error3

STEP Pulse Width

Blank Time

Fixed Off-Time

Crossover Dead Time

Test Conditions

Operating

During Sleep mode

VOUT = VBB

VOUT = 0 V

Source driver, IOUT = 2.5 A

Sink driver, IOUT = 2.5 A

Source diode, IF = 2.5 A

Sink diode, IF = 2.5 A

fPWM < 50 kHz

Operating, outputs disabled

Sleep mode

Operating

fPWM < 50 kHz

Outputs off

Sleep mode

VIN(1)

VIN(0)

Min.

Typ.1

Max.

Units

8

0

<1.0

<1.0

0.28

0.22

35

35

20

20

0.335

0.265

1.4

1.4

8.0

6.0

20

V

V

A

A

V

V

mA

mA

A

3.0

5.0

5.5

12

10

20

V

mA

mA

A

0.7 VDD

0.3 VDD

20

IIN(1)

VIN = 0.7 VDD

20

<1.0

IIN(0)

VIN = 0.3 VDD

20

<1.0

20

VREF

IREF

Operating

0.7 VDD

VDD

3

V

A

V

0.3 VDD

0.6 VDD

VHOME(1) IHOME(1) = 200 A

VHOME(0) IHOME(0) = 200 A

VPFDH

0.21VDD

RT = 56 k, CT = 680 pF

1

700

950

10

5.0

5.0

1200

%

%

%

s

ns

RT = 56 k, CT = 680 pF

30

38

46

Synchronous rectification enabled

100

475

800

ns

VPFDL

EG

tW

tBLANK

tOFF

tDT

VREF = 2 V, Phase Current = 38.27%

VREF = 2 V, Phase Current = 70.71%

VREF = 2 V, Phase Current = 100.00%

Continued on the next page...

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

ELECTRICAL CHARACTERISTICS, continued at TA = 25C, VBB = 35 V, VDD = 3.0 to 5.5 V (unless otherwise noted)

Characteristics

Thermal Shutdown Temperature

Thermal Shutdown Hysteresis

UVLO Enable Threshold

UVLO Hysteresis

Symbol

Test Conditions

TJSD

TJSDHYS

VUVLO Increasing VDD

VUVLOHYS

Min.

2.45

0.05

Typ.1

165

15

2.7

0.10

Max.

2.95

Units

C

C

V

V

1Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions. Performance may vary for

individual units, within the specified maximum and minimum limits.

2Negative current is defined as coming out of (sourcing from) the specified device pin.

3E = ( [ V

G

REF / 8] VSENSE ) / ( VREF / 8 ).

THERMAL CHARACTERISTICS may require derating at maximum conditions, see application information

Characteristic

Symbol

Package Thermal Resistance

RJA

Test Conditions*

Value

Units

Two-layer PCB with 3.8 in.2 of copper area on each side

connected with thermal vias and to device exposed pad

32

C/W

High-K PCB (multilayer with significant copper areas,

based on JEDEC standard)

28

C/W

*Additional thermal information available on Allegro Web site.

Maximum Power Dissipation, PD(max)

5.0

4.5

Power Dissipation, PD (W)

4.0

H

(R igh-

3.5

2-

La

3.0

ye

K

= PCB

28

C

/W

rP

)

(R CB w

ith

J

A =

3

32 .8 in 2

C co

/W pp

er

)

p

2.5

2.0

er

1.5

sid

1.0

0.5

0.0

20

40

60

80

100

120

Temperature (C)

140

160

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

Timing Requirements

(TA = +25C, VDD = 5 V, Logic Levels are VDD and Ground)

STEP

50%

MS1/MS2/

DIR/RESET

SLEEP

Dwg. WP-042

A. Minimum Command Active Time

Before Step Pulse (Data Set-Up Time) ..... 200 ns

B. Minimum Command Active Time

After Step Pulse (Data Hold Time) ............ 200 ns

C. Minimum STEP Pulse Width ...................... 1.0 s

D. Minimum STEP Low Time ......................... 1.0 s

E. Maximum Wake-Up Time ......................... 1.0 ms

Figure 1. Logic Interface Timing Diagram

Table 1. Microstep Resolution Truth Table

MS1

MS2

Microstep Resolution

Excitation Mode

Full Step

2 Phase

Half Step

1-2 Phase

Quarter Step

W1-2 Phase

Sixteenth Step

4W1-2 Phase

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

Functional Description

Device Operation. The A3979 is a complete micro-

Step Input (STEP). A low-to-high transition on the

stepping motor driver with a built-in translator for easy

operation with minimal control lines. It is designed to

operate bipolar stepper motors in full-, half-, quarter-, and

sixteenth-step modes. The currents in each of the two output

full-bridges (all of the N-channel MOSFETs) are regulated

with fixed off-time PMW (pulse width modulated) control

circuitry. At each step, the current for each full-bridge is

set by the value of its external current-sense resistor (RS1

or RS2), a reference voltage (VREF), and the output voltage

of its DAC (which in turn is controlled by the output of the

translator).

STEP input sequences the translator and advances the motor

one increment. The translator controls the input to the DACs

and the direction of current flow in each winding. The size

of the increment is determined by the combined state of

inputs MS1 and MS2 (see table 1).

At power-on or reset, the translator sets the DACs and the

phase current polarity to the initial Home state (shown in

figures 2 through 5), and the current regulator to Mixed

decay mode for both phases. When a step command signal

occurs on the STEP input, the translator automatically

sequences the DACs to the next level and current polarity.

(See table 2 for the current-level sequence.) The microstep

resolution is set by the combined effect of inputs MS1 and

MS2, as shown in table 1.

While stepping is occurring, if the next output level of the

DACs is lower than the immediately preceeding output

level, then the decay mode (Fast, Slow, or Mixed) for the

active full bridge is set by the PFD input. If the next DAC

output level is higher than or equal to the preceeding level,

then the decay mode for that full bridge will be Slow decay.

This automatic current-decay selection improves microstepping performance by reducing the distortion of the current

waveform due to back EMF of the motor.

RESET Input (

R

E

S

E

T

). The R

E

SE

T

input (active

low) sets the translator to a predefined Home state (shown

in figures 2 through 5), and turns off all of the DMOS outputs. The HOME output goes low and all STEP inputs are

ignored until the R

E

SE

T

input is set to high.

Home Output (HOME). The HOME output is a logic

output indicator of the initial state of the translator. At

power-on, the translator is reset to the Home state (shown in

figures 2 through 5).

Microstep Select (MS1 and MS2). The input on

terminals MS1 and MS2 selects the microstepping format,

as shown in table 1. Any changes made to these inputs do not

take effect until the next rising edge of a step command signal

on the STEP input.

Direction Input (DIR). The state of the DIR input determines the direction of rotation of the motor. Any changes

made to this input does not take effect until the next rising

edge of a step command signal on the STEP input.

Internal PWM Current Control. Each full bridge is

controlled by a fixedoff-time PWM current-control circuit

that limits the load current to a desired value, ITRIP . Initially,

a diagonal pair of source and sink MOS outputs are enabled

and current flows through the motor winding and the current

sense resistor, RSx. When the voltage across RSx equals the

DAC output voltage, the current-sense comparator resets the

PWM latch. The latch then turns off either the source MOSFETs (when in Slow decay mode) or the sink and source

MOSFETs (when in Fast or Mixed decay mode).

The maximum value of current limiting is set by the selection of RS and the voltage at the VREF input with a transconductance function approximated by:

ITRIPmax = VREF/8RS

The DAC output reduces the VREF output to the current-sense comparator in precise steps (see table 2 for

% ITRIPmax at each step).

ITRIP = (% ITRIPmax/100) ITRIPmax

It is critical that the maximum rating (0.5 V) on either the

SENSE1 and SENSE2 pins is not exceeded. For full stepping, VREF can be applied up to the maximum rating of VDD

because the peak sense value is 0.707 VREF / 8. In all other

modes, VREF should not exceed 4 V.

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

Fixed Off-Time. The internal PWM current-control circuitry uses a one-shot timer to control the duration of time

that the MOSFETs remain off. The one shot off-time, tOFF,

is determined by the selection of external resistors, RTx , and

capacitors, CTx , connected from each RCx timing terminal to

ground. The off-time, over a range of values of CT = 470 pF

to 1500 pF and RT = 12 k to 100 k is approximated by:

tOFF = RTCT

RC Blanking. In addition to the fixed off-time of the

PWM control circuit, the CTx component sets the comparator blanking time. This function blanks the output of the

current-sense comparators when the outputs are switched

by the internal current-control circuitry. The comparator

outputs are blanked to prevent false overcurrent detection

due to reverse recovery currents of the clamp diodes, or to

switching transients related to the capacitance of the load.

The blank time tBLANK can be approximated by:

tBLANK = 1400CT

Charge Pump (CP1 and CP2). The charge pump is

used to generate a gate supply greater than that of VBB for

driving the source-side DMOS gates. A 0.22 F ceramic

capacitor should be connected between CP1 and CP2 for

pumping purposes. In addition, a 0.22 F ceramic capacitor

is required between VCP and VBB, to act as a reservoir for

operating the high-side DMOS gates.

VREG (VREG). This internally-generated voltage is used to

operate the sink-side DMOS outputs. The VREG pin must

be decoupled with a 0.22 F capacitor to ground. VREG is

internally monitored, and in the case of a fault condition, the

DMOS outputs of the device are disabled.

Enable Input (E

N

A

B

L

E ). This active-low input

enables all of the DMOS outputs. When set to a logic high,

the outputs are disabled. The inputs to the translator (STEP,

DIR, MS1, and MS2), all remain active, independent of the

E

NAB

L

E

input state.

Shutdown. During normal operation, in the event of a

fault, such as overtemperature (excess TJ) or an undervolt-

age on VCP, the outputs of the device are disabled until the

fault condition is removed.

At power up, and in the event of low VDD, the undervoltage

lockout (UVLO) circuit disables the drivers and resets the

translator to the Home state.

Sleep Mode ( S

L

E

E

P ). This active-low control input

is used to minimize power consumption when the motor is

not in use. It disables much of the internal circuitry including the output DMOS FETs, current regulator, and charge

pump. Setting this to a logic high allows normal operation,

as well as start-up (at which time the A3979 drives the

motor to the Home microstep position). When bringing the

device out of Sleep mode, in order to allow the charge pump

(gate drive) to stabilize, provide a delay of 1 ms before issuing a step command signal on the STEP input.

Percent Fast Decay Input (PFD). When a STEP

input signal commands a lower output current than the

previous step, it switches the output current decay to either

Slow, Fast, or Mixed decay mode, depending on the voltage

level at the PFD input. If the voltage at the PFD input is

greater than 0.6 VDD , then Slow decay mode is selected.

If the voltage on the PFD input is less than 0.21 VDD , then

Fast decay mode is selected. Mixed decay mode is selected

when VPFD is between these two levels, as described in

the next section. This terminal should be decoupled with a

0.1 F capacitor.

Mixed Decay Operation. If the voltage on the PFD input

is between 0.6 VDD and 0.21 VDD , the bridge operates

in Mixed decay mode, as determined by the step sequence

(shown in figures 2 through 5). As the trip point is reached,

the device goes into Fast decay mode until the voltage

on the RCx terminal decays to the same level as voltage

applied to the PFD terminal. The time that the device operates in fast decay is approximated by:

tFD = RTCTln (0.6VDD/VPFD)

After this Fast decay portion, the device switches to Slow

decay mode for the remainder of the fixed off-time period.

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

Synchronous Rectification. When a PWM offcycle is triggered by an internal fixedoff-time cycle, load

current recirculates according to the decay mode selected

by the control logic. The A3979 synchronous rectification

feature turns on the appropriate MOSFETs during the decay

of the current, and effectively shorts out the body diodes

with the low RDS(On) driver. This reduces power dissipation

significantly and eliminates the need for external Schottky

diodes for most applications. The synchronous rectification

can be set to either Active mode or Disabled mode:

Active Mode. When the SR input is logic low, Active

mode is enabled and synchronous rectification can occur.

This mode prevents reversal of the load current by turning

off synchronous rectification when a zero current level is

detected. This prevents the motor winding from conducting in the reverse direction.

Disabled Mode. When the SR input is logic high, synchronous rectification is disabled. This mode is typically used when external diodes are required to transfer

power dissipation from the A3979 package to the external

diodes.

Applications Information

Layout. The printed circuit board on which the device is

Current Sensing. To minimize inaccuracies caused by

mounted should have a heavy ground plane. For optimum

electrical and thermal performance, the A3979 should be

soldered directly onto the board.

ground-trace IR drops in sensing the output current level,

the current-sense resistors, RSx, should have an independent

ground return to the star ground of the device. This path

should be as short as possible.

The load supply terminals, VBBx, should be decoupled with

an electrolytic capacitor (>47 F is recommended), placed

as close to the device as possible.

To avoid problems due to capacitive coupling of the high

dv / dt switching transients, route the bridge-output traces

away from the sensitive logic-input traces.

Always drive the logic inputs with a low source impedance

to increase noise immunity.

Grounding. The AGND (analog ground) terminal and the

PGND (power ground) terminal must be connected together

externally.

All ground lines should be connected together and be as

short as possible. A star ground system, centered under the

device, is an optimum design.

The copper ground plane located under the exposed thermal

pad is typically used as the star ground.

For low-value sense resistors, the IR drops in the printed circuit board sense resistor traces can be significant and should

be taken into account.

The use of sockets should be avoided as they can introduce

variation in RSx due to their contact resistance.

Allegro MicroSystems recommends a value of RS given by

RS = 0.5/ITRIPmax

Thermal Protection. This internal circuitry turns off

all drivers when the junction temperature reaches 165C,

typical. It is intended only to protect the device from failures

due to excessive junction temperatures and should not imply

that output short circuits are permitted. Thermal shutdown

has a hysteresis of approximately 15C.

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

STEP Input

STEP Input

HOME Output

HOME Output

100.00

100.00

70.71

70.71

Slow

Phase 1

IOUT1A

Direction = H

(%)

100.00

100.00

70.71

100.00

100.00

70.71

Phase 2

IOUT2A

Direction = H

(%)

0.00

Slow

Slow Slow

Mixed

Mixed

Slow

Slow

Mixed

0.00

70.71

70.71

100.00

100.00

Figure 2. Decay Mode for Full-Step Increments

Mixed

0.00

70.71

Phase 2

IOUT2A

Direction = H

(%)

Slow

Mixed

Home Microstep Position

70.71

Home Microstep Position

0.00

Slow

Mixed

Home Microstep Position

Slow

Home Microstep Position

Phase 1

IOUT1A

Direction = H

(%)

Figure 3. Decay Modes for Half-Step Increments

STEP Input

HOME Output

100.00

92.39

70.71

38.27

Slow

Mixed

Slow

Mixed

Slow

0.00

Home Microstep Position

Phase 1

IOUT1A

Direction = H

(%)

38.27

70.71

92.39

100.00

100.00

92.39

70.71

Phase 2

IOUT2A

Direction = H

(%)

38.27

Slow

Mixed

Slow

Mixed

Slow

Mixed

0.00

38.27

70.71

92.39

100.00

Figure 4. Decay Modes for Quarter-Step Increments

10

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

STEP Input

HOME Output

100.00

95.69

88.19

83.15

77.30

70.71

63.44

55.56

47.14

38.27

29.03

19.51

Phase 1

IOUT1A

Direction = H

(%)

9.8

Slow

0.00

Mixed

Slow

Mixed

9.8

19.51

29.03

Home Microstep Position

38.27

47.14

55.56

63.44

70.71

77.30

83.15

88.19

95.69

100.00

100.00

95.69

88.19

83.15

77.30

70.71

63.44

55.56

47.14

38.27

29.03

19.51

Phase 2

IOUT2A

Direction = H

(%)

9.8

0.00

Slow

Mixed

Slow

Mixed

Slow

9.8

19.51

29.03

38.27

47.14

55.56

63.44

70.71

77.30

83.15

88.19

95.69

100.00

Figure 5. Decay Modes for Sixteenth-Step Increments

11

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

Table 2. Step Sequencing Settings

Home microstep position at Step Angle 45; DIR = H; 360 = 4 full steps

Full

Step

#

Half

Step

#

1

1/4

Step

#

1

Phase 1

Current

Phase 2

Current

[% ItripMax]

[% ItripMax]

(%)

100.00

(%)

0.00

Step

Angle

()

0.0

99.52

9.80

5.6

98.08

19.51

11.3

35

98.08

19.51

191.3

95.69

29.03

16.9

36

95.69

29.03

196.9

92.39

38.27

22.5

37

92.39

38.27

202.5

88.19

47.14

28.1

38

88.19

47.14

208.1

83.15

55.56

33.8

39

83.15

55.56

213.8

1/16

Step

#

1

77.30

63.44

39.4

70.71

70.71

45.0

10

63.44

77.30

Full

Step

#

Half

Step

#

5

1/4

Step

#

9

1/16

Step

#

33

34

10

Phase 1

Current

Phase 2

Current

[% ItripMax]

[% ItripMax]

Step

Angle

100.00

(%)

0.00

180.0

99.52

9.80

185.6

(%)

()

40

77.30

63.44

219.4

41

70.71

70.71

225.0

50.6

42

63.44

77.30

230.6

11

11

55.56

83.15

56.3

43

55.56

83.15

236.3

12

47.14

88.19

61.9

44

47.14

88.19

241.9

13

38.27

92.39

67.5

45

38.27

92.39

247.5

14

29.03

95.69

73.1

46

29.03

95.69

253.1

15

19.51

98.08

78.8

47

19.51

98.08

258.8

16

9.80

99.52

84.4

17

0.00

100.00

90.0

18

9.80

99.52

19

19.51

20

29.03

21

22

23

12

48

9.80

99.52

264.4

49

0.00

100.00

270.0

95.6

50

9.80

99.52

275.6

98.08

101.3

51

19.51

98.08

281.3

95.69

106.9

52

29.03

95.69

286.9

38.27

92.39

112.5

53

38.27

92.39

292.5

47.14

88.19

118.1

54

47.14

88.19

298.1

55.56

83.15

123.8

55

55.56

83.15

303.8

24

63.44

77.30

129.4

25

70.71

70.71

135.0

26

77.30

63.44

27

83.15

28

88.19

29

30

13

14

56

63.44

77.30

309.4

57

70.71

70.71

315.0

140.6

58

77.30

63.44

320.6

55.56

146.3

59

83.15

55.56

326.3

47.14

151.9

60

88.19

47.14

331.9

92.39

38.27

157.5

61

92.39

38.27

337.5

95.69

29.03

163.1

62

95.69

29.03

343.1

31

98.08

19.51

168.8

63

98.08

19.51

348.8

32

99.52

9.80

174.4

64

99.52

9.80

354.4

15

16

12

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

Terminal List Table

Number

Name

SENSE1

HOME

Description

Sense resistor for Bridge 1

Logic Output

DIR

OUT1A

Logic input

Output A for Bridge 1

PFD

Mixed decay setting

RC1

Analog input for fixed off-time for Bridge 1

AGND

REF

Current trip reference voltage input

Analog Ground

RC2

Analog input for fixed off-time for Bridge 2

10

VDD

Logic supply

11

OUT2A

12

MS2

Logic input

13

MS1

Logic input

14

SENSE2

15

VBB2

16

SR

Logic input

17

R

E

S

E

T

Logic input

18

OUT2B

Output B for Bridge 2

19

STEP

Output A for Bridge 2

Sense resistor for Bridge 2

Load supply for Bridge 2

Logic input

20

VREG

Regulator decoupling

21

PGND

Power Ground

22

VCP

Reservoir capacitor

23

CP1

Charge pump capacitor 1

24

CP2

Charge pump capacitor 2

25

1OUT1B

Output B for Bridge 1

26

E

N

A

B

L

E

Logic input

27

S

L

E

E

P

Logic input

28

VBB1

Load supply for Bridge 1

13

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

LP Package, 28-pin TSSOP

0.45

9.70 0.10

28

+0.05

0.15 0.06

0.65

28

4 4

1.65

B

3.00

4.40 0.10

6.40 0.20

3.00

6.10

0.60 0.15

A

(1.00)

2

5.00

0.25

28X

SEATING

PLANE

0.10 C

+0.05

0.25 0.06

0.65

SEATING PLANE

GAUGE PLANE

1 2

5.00

C

PCB Layout Reference View

1.20 MAX

0.10 MAX

For reference only

(reference JEDEC MO-153 AET)

Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions

Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

B Exposed thermal pad (bottom surface)

C Reference land pattern layout (reference IPC7351 SOP65P640X120-29CM);

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary

to meet application process requirements and PCB layout tolerances; when

mounting on a multilayer PCB, thermal vias at the exposed thermal pad land

can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

14

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

A3979

DMOS Microstepping Driver with Translator

Revision History

Revision

Revision Date

Rev. F

June 21, 2013

Description of Revision

Update decay charts

Copyright 2005-2013, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to

permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that

the information being relied upon is current.

Allegros products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the

failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its

use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com

15

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

You might also like

- Microstepping DMOS Driver With Translator: Features and Benefits DescriptionDocument17 pagesMicrostepping DMOS Driver With Translator: Features and Benefits DescriptionPaulina VictoriaNo ratings yet

- A 4983Document16 pagesA 4983Boreal3000No ratings yet

- A4988 DatasheetDocument20 pagesA4988 DatasheetJose OnoNo ratings yet

- A4988 DatasheetDocument20 pagesA4988 Datasheetun_diletanteNo ratings yet

- A4982 DatasheetDocument20 pagesA4982 DatasheetmedhyalNo ratings yet

- Microstepping DMOS Driver With Translator: Description Features and BenefitsDocument18 pagesMicrostepping DMOS Driver With Translator: Description Features and BenefitsSaid BoubkerNo ratings yet

- A4989 DatasheetDocument17 pagesA4989 DatasheetGopalkrishnan Nadar100% (1)

- A4982 DatasheetDocument20 pagesA4982 DatasheetLêĐìnhDanhNo ratings yet

- Dual DMOS Full-Bridge Microstepping PWM Motor Driver: Description Features and BenefitsDocument11 pagesDual DMOS Full-Bridge Microstepping PWM Motor Driver: Description Features and BenefitsHamza KhanNo ratings yet

- Aerosemi: Features ApplicationsDocument9 pagesAerosemi: Features Applicationsttnaing100% (1)

- A4954 DatasheetDocument9 pagesA4954 DatasheetAngly1959No ratings yet

- SG6848 Aahbp To Je PDFDocument13 pagesSG6848 Aahbp To Je PDFVukica IvicNo ratings yet

- Data SH Power Supplies Mixed Signal MaximDocument23 pagesData SH Power Supplies Mixed Signal MaximbmmostefaNo ratings yet

- Max 2981Document13 pagesMax 2981Jamila RobinsonNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- Serie GMD06Document2 pagesSerie GMD06Popescu IonicaNo ratings yet

- CNC Shield For A4988Document7 pagesCNC Shield For A4988vaxewiNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- 73M2921 Advanced Single Chip Modem: Description FeaturesDocument42 pages73M2921 Advanced Single Chip Modem: Description FeaturesRicardo MercadoNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- ELECTRONICDocument13 pagesELECTRONICMahmoued YasinNo ratings yet

- Vestel 17mb24h Service ManualDocument46 pagesVestel 17mb24h Service Manualchris_crtv3753No ratings yet

- MP3389 r1.04Document16 pagesMP3389 r1.04Andres Alegria100% (1)

- Ads 7870Document43 pagesAds 7870Moorthy VenkatachalamNo ratings yet

- LMD 18200Document14 pagesLMD 18200Itzamary Romero SosaNo ratings yet

- LMD18201 3A, 55V H-Bridge: Literature Number: SNVS092CDocument14 pagesLMD18201 3A, 55V H-Bridge: Literature Number: SNVS092CIrfan AbbasiNo ratings yet

- Analog Servo Drive: Description Power RangeDocument7 pagesAnalog Servo Drive: Description Power RangeElectromateNo ratings yet

- Led Driver 12 PinDocument39 pagesLed Driver 12 PinМихаил НестеровNo ratings yet

- TDA8929T Datasheet Circuit DiagramDocument36 pagesTDA8929T Datasheet Circuit DiagramSukhanand S. SarpeNo ratings yet

- MC33926 PDFDocument25 pagesMC33926 PDFKACH1234No ratings yet

- Green Mode PWM Controller Ap384XgDocument13 pagesGreen Mode PWM Controller Ap384XgbaphometabaddonNo ratings yet

- DMOS Microstepping Driver With Translator: FeaturesDocument13 pagesDMOS Microstepping Driver With Translator: FeaturesVõ Thành LongNo ratings yet

- 6-Channel Driver IC Controls CD-ROM MotorsDocument3 pages6-Channel Driver IC Controls CD-ROM Motorsdggiyvnxssr9222No ratings yet

- E Tended Environment: Analog Servo DriveDocument8 pagesE Tended Environment: Analog Servo DriveElectromateNo ratings yet

- DRV 8834Document30 pagesDRV 8834Anonymous 10cG5eRp8100% (1)

- Adc11Dl066 Dual 11-Bit, 66 MSPS, 450 MHZ Input Bandwidth A/D Converter W/Internal ReferenceDocument24 pagesAdc11Dl066 Dual 11-Bit, 66 MSPS, 450 MHZ Input Bandwidth A/D Converter W/Internal ReferenceVănThịnhNo ratings yet

- MC3479 Stepper Motor Driver: FeaturesDocument10 pagesMC3479 Stepper Motor Driver: FeaturesHenry CastandNo ratings yet

- L6208D To L6208PDDocument16 pagesL6208D To L6208PDwtn2013No ratings yet

- DRV 8811Document22 pagesDRV 8811nelson_loboNo ratings yet

- 5V Disk Drive Spindle & VCM, Power & Control "Combo": General Bicmos TechnologyDocument17 pages5V Disk Drive Spindle & VCM, Power & Control "Combo": General Bicmos Technologybenjoshu9031No ratings yet

- Analog Servo Drive: Description Power RangeDocument7 pagesAnalog Servo Drive: Description Power RangeElectromateNo ratings yet

- MC 33186Document21 pagesMC 33186Olga PlohotnichenkoNo ratings yet

- Azbh 12 A 8Document8 pagesAzbh 12 A 8ElectromateNo ratings yet

- Allegro STR-W6765 PDFDocument15 pagesAllegro STR-W6765 PDFcomportNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- L4972ADocument23 pagesL4972ARICHIHOTS2No ratings yet

- MITSUBISHI M56784FP SPINDLE MOTOR DRIVER IC DESCRIPTIONDocument11 pagesMITSUBISHI M56784FP SPINDLE MOTOR DRIVER IC DESCRIPTIONAdriano TameouvindoNo ratings yet

- Description Power Range: Analog Servo DriveDocument8 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- MC3PHACDocument36 pagesMC3PHACBảo BìnhNo ratings yet

- 150KHz, 3A Step Down Voltage Switching Regulators DatasheetDocument10 pages150KHz, 3A Step Down Voltage Switching Regulators DatasheetAlfredo Valencia RodriguezNo ratings yet

- A3979 - Micro Stepping DMOS Driver With TranslatorDocument14 pagesA3979 - Micro Stepping DMOS Driver With TranslatorFernando Lizarraga100% (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- B01-TB16I-003 - TB16IN Basic Installation Instructions - ENG - V1.2Document2 pagesB01-TB16I-003 - TB16IN Basic Installation Instructions - ENG - V1.2Kien Nguyen TrungNo ratings yet

- CapBank EatonDocument32 pagesCapBank EatonChristopher BrownNo ratings yet

- Eurotest 61557 User ManualDocument96 pagesEurotest 61557 User Manualmoj_scribdNo ratings yet

- KSP42Document5 pagesKSP42ingucvNo ratings yet

- L&T Type 2 Co-Ordination Selection ChartsDocument48 pagesL&T Type 2 Co-Ordination Selection Chartsrdeepak99100% (7)

- 18B-044-PE Electrical Machines Mid Term 1Document7 pages18B-044-PE Electrical Machines Mid Term 1ShabihNo ratings yet

- Dokumen - Tips - 220v DC Motor Speed Control Circuit Diagram DC Motor Speed Control Circuit MotorDocument4 pagesDokumen - Tips - 220v DC Motor Speed Control Circuit Diagram DC Motor Speed Control Circuit Motorjim campbellNo ratings yet

- SRP (540 555) BMA BG - Frame - 182 - ENDocument2 pagesSRP (540 555) BMA BG - Frame - 182 - ENYilin TeoNo ratings yet

- Yai Kaeps80000123 PDFDocument536 pagesYai Kaeps80000123 PDFIrving CurasantaNo ratings yet

- Presentation On SPS: (Special Protection Scheme)Document9 pagesPresentation On SPS: (Special Protection Scheme)Abhishek SinhaNo ratings yet

- Specification LV Capacitor BankDocument8 pagesSpecification LV Capacitor BankBhaskar DandapathakNo ratings yet

- Appendix A - Status Messages: Armed. Bad Snubber FuseDocument9 pagesAppendix A - Status Messages: Armed. Bad Snubber Fuse이민재No ratings yet

- Electromechanical Relays Zelio Relay: PresentationDocument4 pagesElectromechanical Relays Zelio Relay: PresentationLizandro ManzatoNo ratings yet

- Io ListDocument12 pagesIo ListKrishNo ratings yet

- ST Capacitor Assemblies: Lead Configuration and Assembly OptionsDocument2 pagesST Capacitor Assemblies: Lead Configuration and Assembly OptionsLeonardoNo ratings yet

- Reemplazo de Transistores MosfetDocument36 pagesReemplazo de Transistores Mosfetramon navaNo ratings yet

- SSL Mixbus Compressor CloneDocument11 pagesSSL Mixbus Compressor CloneShane CampbellNo ratings yet

- SK32 - SK36: Surface Mount Schottky Barrier RectifierDocument2 pagesSK32 - SK36: Surface Mount Schottky Barrier RectifierAnonymous 50FYYM2No ratings yet

- THHN Wire Table and PricesDocument1 pageTHHN Wire Table and Pricesjanmczeal100% (2)

- Safety Relays - PSR-SCP-230UC/ESAM4/3X1/1X2/B - 2901428: Key Commercial DataDocument6 pagesSafety Relays - PSR-SCP-230UC/ESAM4/3X1/1X2/B - 2901428: Key Commercial DataConstantin MoldoNo ratings yet

- Siemens Power Engineering Guide 7E 92Document1 pageSiemens Power Engineering Guide 7E 92mydearteacherNo ratings yet

- IECD Capsule NotesDocument59 pagesIECD Capsule NotesANANTHU PRADEEPNo ratings yet

- RINCIAN LISTRIK - RevisiDocument10 pagesRINCIAN LISTRIK - RevisiLiondo PurbaNo ratings yet

- Philips Halogen Safety Light Bulletin 3-90Document2 pagesPhilips Halogen Safety Light Bulletin 3-90Alan MastersNo ratings yet

- Methods of EarthingDocument6 pagesMethods of Earthingbhuvana_eee100% (1)

- Electronics Problem Set 2: Ideal Diode and PN JunctionDocument3 pagesElectronics Problem Set 2: Ideal Diode and PN JunctionAhmedNo ratings yet

- Microelectronic Circuits Chapter 3: Diodes Characteristics Models CircuitsDocument65 pagesMicroelectronic Circuits Chapter 3: Diodes Characteristics Models CircuitsRAIHAN AZWAR IBRAHIM PULUNGANNo ratings yet

- E ASY ASY RevbDocument7 pagesE ASY ASY RevbVirajitha Maddumabandara0% (1)

- Annexure-1 Cable Sizing Calculation For LV CablesDocument14 pagesAnnexure-1 Cable Sizing Calculation For LV CablesAnand Mohan PandeyNo ratings yet

- Final Exam SEE3433 2011 MeiDocument9 pagesFinal Exam SEE3433 2011 MeiFizah Abdul RahmanNo ratings yet