Professional Documents

Culture Documents

Tle 6220 PDF

Uploaded by

Fabio JuniorOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tle 6220 PDF

Uploaded by

Fabio JuniorCopyright:

Available Formats

Data Sheet TLE 6220 GP

Smart Quad Low-Side Switch

Features

Product Summary

Short Circuit Protection

Supply voltage

Overtemperature Protection

Drain source voltage

Overvoltage Protection

8 bit Serial Data Input and DiagOn resistance

nostic Output (SPI protocol)

Output current (all outp. ON equal)

Direct Parallel Control of Four

(individually)

Channels for PWM Applications

Cascadable with Other Quad Switches

Low Quiescent Current

C Compatible Input

Electostatic Discharge (ESD) Protection

Application

C Compatible Power Switch for 12 V and 24 V Applications

Switch for Automotive and Industrial System

Solenoids, Relays and Resistive Loads

Injectors

Robotic controls

4.5 5.5

60

0.32

1

3

VS

VDS(AZ) max

RON

ID(NOM)

V

V

A

A

P-DSO-20-12

Ordering Code:

Q67006-A9315

General Description

Quad Low-Side Switch in Smart Power Technology (SPT) with a Serial Peripheral Interface (SPI) and

four open drain DMOS output stages. The TLE 6220 GP is protected by embedded protection functions and designed for automotive and industrial applications. The output stages can be controlled direct in parallel for PWM applications (injector coils), or through serial control via the SPI. Therefore the

TLE 6220 GP is particularly suitable for engine management and powertrain systems.

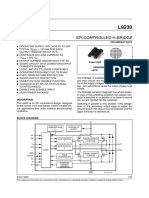

Block Diagram

PRG

GND

VS

RESET

FAULT

VS

normal function

IN1

SCB / overload

IN2

as Ch. 1

IN3

as Ch. 1

IN4

as Ch. 1

short to ground

Output Stage

SCLK

CS

open load

LOGIC

8

SI

VBB

1

8

Serial Interface

SPI

OUT1

4

4

Output Control

Buffer

OUT4

SO

GND

V1.1

Page

26.Aug. 2002

Data Sheet TLE 6220 GP

Pin Description

Pin

1

2

3

4

5

Symbol

GND

IN2

OUT1

VS

CS

PRG

OUT2

IN1

GND

GND

IN4

OUT3

7

8

9

10

11

12

13

14

15

16

17

18

19

20

RESET

FAULT

SO

SCLK

SI

OUT4

IN3

GND

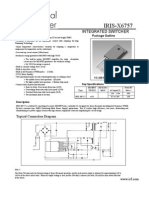

Pin Configuration (Top view)

Function

Ground

Input Channel 2

Power Output Channel 1

Supply Voltage

Reset

Chip Select

Program (inputs high or low active)

Power Output Channel 2

Input Channel 1

Ground

Ground

Input Channel 4

Power Output Channel 3

General Fault Flag

GND

IN2

OUT1

VS

RESET

CS

PRG

OUT2

IN1

GND

1

2

3

4

5

6

7

8

9

10

20 GND

19

IN3

18 OUT4

17

SI

16 SCLK

15

SO

14 FAULT

13 OUT3

12

IN4

11 GND

Power SO-20

Serial Data Output

Serial Clock

Serial Data Input

Power Output Channel 4

Input Channel 3

Ground

Heat slug internally connected to ground pins

V1.1

Page

26.Aug. 2002

Data Sheet TLE 6220 GP

Maximum Ratings for Tj = 40C to 150C

Parameter

Supply Voltage

Symbol

VS

Continuous Drain Source Voltage (OUT1...OUT4)

VDS

Input Voltage, All Inputs and Data Lines

VIN

Values

-0.3 ... +7

Unit

V

45

- 0.3 ... + 7

2)

Load Dump Protection VLoad Dump = UP+US; UP=13.5 V

With Automotive Injector Valve RL = 14

RI1)=2 ; td=400ms; IN = low or high

With RL= 6.8 (ID = 2A)

RI=2 ; td=400ms; IN = low or high

VLoad Dump

Operating Temperature Range

Storage Temperature Range

Tj

Tstg

- 40 ... + 150

- 55 ... + 150

Output Current per Channel (see el. characteristics)

ID(lim)

ID(lim) min

Output Current per Channel @ TA = 25C

(All 4 Channels ON; Mounted on PCB ) 3)

ID

V

62

52

C

Output Clamping Energy

ID = 1A

EAS

50

mJ

Power Dissipation (DC, mounted on PCB) @ TA = 25C

Ptot

Electrostatic Discharge Voltage (human body model)

according to MIL STD 883D, method 3015.7 and EOS/ESD

assn. standard S5.1 - 1993

VESD

2000

DIN Humidity Category, DIN 40 040

IEC Climatic Category, DIN IEC 68-1

40/150/56

K/W

Thermal resistance

junction case (die soldered on the frame)

junction - ambient @ min. footprint

junction - ambient @ 6 cm2 cooling area

Minimum footprint

RthJC

RthJA

2

50

38

PCB with heat pipes,

2

backside 6 cm cooling area

1)

RI=internal resistance of the load dump test pulse generator LD200

VLoadDump is setup without DUT connected to the generator per ISO 7637-1 and DIN 40 839.

3)

Output current rating so long as maximum junction temperature is not exceeded. At TA = 125 C the output current has to be calculated using RthJA according mounting conditions.

2)

V1.1

Page

26.Aug. 2002

Data Sheet TLE 6220 GP

Electrical Characteristics

Parameter and Conditions

VS = 4.5 to 5.5 V ; Tj = - 40 C to + 150 C ; Reset = H

(unless otherwise specified)

Symbol

Values

min

Unit

typ

max

1. Power Supply, Reset

Supply Voltage4

Supply Current

Minimum Reset Duration

(After a reset all parallel inputs are ORed with the SPI

data bits)

VS

4.5

--

5.5

IS

--

tReset,min

V

mA

10

2. Power Outputs

ON Resistance VS = 5 V; ID = 1 A

Output Clamping Voltage

45

53

60

ID(lim)

4.5

ID(lkg)

--

--

10

RDS(ON)

output OFF

Current Limit

Output Leakage Current

--

0.4

0.7

TJ = 25C

TJ = 150C

VRESET = L

--

0.32

-VDS(AZ)

Turn-On Time

ID = 1 A, resistive load

tON

--

10

Turn-Off Time

ID = 1 A, resistive load

tOFF

--

10

Input Low Voltage

VINL

- 0.3

--

1.0

Input High Voltage

VINH

2.0

--

VS+0.3

Input Voltage Hysteresis

VINHys

50

100

200

mV

Input Pull Down/Up Current (IN1 ... IN4)

IIN(1..4)

20

50

100

PRG, RESET Pull Up Current

IIN(PRG,Res)

20

50

100

Input Pull Down Current (SI, SCLK)

IIN(SI,SCLK)

10

20

50

Input Pull Up Current ( CS )

IIN(CS)

10

20

50

3. Digital Inputs

4. Digital Outputs (SO, FAULT )

SO High State Output Voltage

ISOH = 2 mA

VSOH

--

SO Low State Output Voltage

ISOL = 2.5 mA

VSOL

--

--

0.4

ISOlkg

-10

10

VFAULTL

--

--

0.4

Current Limitation; Overload Threshold Current

ID(lim) 1...4

4.5

Overtemperature Shutdown Threshold

Hysteresis6

Tth(sd)

Thys

170

--

-10

200

--

Output Tri-state Leakage Current

CS = H, 0 VSO VS

FAULT Output Low Voltage

IFAULT = 1.6 mA

VS - 0.4 --

C

K

For VS < 4.5V the power stages are switched according the input signals and data bits or are definitely switched

off. This undervoltage reset gets active at VS = 3V (typ. value) and is guaranteed by design.

5

If Reset = L the supply current is reduced to typ. 20A

6

This parameter will not be tested but guaranteed by design

V1.1

Page

26.Aug. 2002

Data Sheet TLE 6220 GP

Electrical Characteristics cont.

Parameter and Conditions

VS = 4.5 to 5.5 V ; Tj = - 40 C to + 150 C ; Reset = H

(unless otherwise specified)

Symbol

Values

min

Unit

typ

max

5. Diagnostic Functions

Open Load Detection Voltage

VDS(OL)

Output Pull Down Current

IPD(OL)

50

Fault Delay Time

td(fault)

50

Short to Ground Detection Voltage

VDS(SHG)

Short to Ground Detection Current

ISHG

-50

-100

-150

Serial Clock Frequency (depending on SO load)

fSCK

DC

--

MHz

Serial Clock Period (1/fclk)

tp(SCK)

200

--

--

ns

Serial Clock High Time

tSCKH

50

--

--

ns

Serial Clock Low Time

tSCKL

50

--

--

ns

Enable Lead Time (falling edge of CS to rising edge of

CLK)

tlead

250

--

--

ns

Enable Lag Time (falling edge of CLK to rising edge of CS ) tlag

250

---

--

ns

Data Setup Time (required time SI to falling of CLK)

tSU

20

--

--

ns

Data Hold Time (falling edge of CLK to SI)

tH

20

--

--

ns

Disable Time @ CL = 50 pF

tDIS

--

--

150

ns

tdt

200

--

--

ns

tvalid

----

----

110

120

150

ns

VS -2.5 VS -2

VS -1.3

90

150

110

200

VS 3.3 VS -2.9 VS -2.5

V

A

6. SPI-Timing

Transfer Delay Time

( CS high time between two accesses)

Data Valid Time

CL = 50 pF

CL = 100 pF8

CL = 220 pF8

This time is necessary between two write accesses. To get the correct diagnostic information, the transfer delay

time has to be extended to the maximum fault delay time td(fault)max = 200s.

8

This parameter will not be tested but guaranteed by design

V1.1

Page

26.Aug. 2002

Data Sheet TLE 6220 GP

Functional Description

The TLE 6220 GP is an quad-low-side power switch which provides a serial peripheral interface (SPI) to control the 4 power DMOS switches, as well as diagnostic feedback. The power

transistors are protected against short to VBB, overload, overtemperature and against overvoltage by an active zener clamp.

The diagnostic logic recognises a fault condition which can be read out via the serial diagnostic output (SO).

Circuit Description

Power Transistor Protection Functions9)

Each of the four output stages has its own zener clamp, which causes a voltage limitation at

the power transistor when solenoid loads are switched off. The outputs are provided with a

current limitation set to a minimum of 3 A. The continuous current for each channel is 1A (all

channels ON; depending on cooling).

Each output is protected by embedded protection functions. In the event of an overload or

short to supply, the current is internally limited and the corresponding bit combination is set

(early warning). If this operation leads to an overtemperature condition, a second protection

level (about 170 C) will change the output into a low duty cycle PWM (selective thermal shutdown with restart) to prevent critical chip temperatures.

SPI Signal Description

CS - Chip Select. The system microcontroller selects the TLE 6220 GP by means of the CS

pin. Whenever the pin is in a logic low state, data can be transferred from the C and vice

versa.

CS High to Low transition: - Diagnostic status information is transferred from the power

outputs into the shift register.

- Serial input data can be clocked in from then on.

- SO changes from high impedance state to logic high or low

state corresponding to the SO bits.

CS Low to High transition: - Transfer of SI bits from shift register into output buffers

- Reset of diagnosis register.

To avoid any false clocking the serial clock input pin SCLK should be logic low state during

high to low transition of CS . When CS is in a logic high state, any signals at the SCLK and SI

pins are ignored and SO is forced into a high impedance state.

9 )

The integrated protection functions prevent an IC destruction under fault conditions and may not be used in normal operation or permanently.

V1.1

Page

26.Aug. 2002

Data Sheet TLE 6220 GP

SCLK - Serial Clock. The system clock pin clocks the internal shift register of the TLE

6220 GP. The serial input (SI) accepts data into the input shift register on the falling edge of

SCLK while the serial output (SO) shifts diagnostic information out of the shift register on the

rising edge of serial clock. It is essential that the SCLK pin is in a logic low state whenever

chip select CS makes any transition.

SI - Serial Input. Serial data bits are shifted in at this pin, the most significant bit first. SI information is read in on the falling edge of SCLK. Input data is latched in the shift register and

then transferred to the control buffer of the output stages.

The input data consists of one byte, made up of four control bits and four data bits. The control word is used to program the device, to operate it in a certain mode as well as providing

diagnostic information (see page 11). The four data bits contain the input information for the

four channels, and are high active.

SO - Serial Output. Diagnostic data bits are shifted out serially at this pin, the most significant

bit first. SO is in a high impedance state until the CS pin goes to a logic low state. New diagnostic data will appear at the SO pin following the rising edge of SCLK.

RESET - Reset pin. If the reset pin is in a logic low state, it clears the SPI shift register and

switches all outputs OFF. An internal pull-up structure is provided on chip. As long as the reset

pin is low the device is in low quiescent current mode and the supply current is reduced to typ.

20A.

Output Stage Control

The four outputs of the TLE 6220 GP can either be controlled in parallel (IN1...IN4), or via the

Serial Peripheral Interface (SPI).

Parallel Control

A Boolean operation (either AND or OR) is performed on each of the parallel inputs and respective SPI data bits, in order to determine the states of the respective outputs. The type of

Boolean operation performed is programmed via the serial interface.

The parallel inputs are high or low active depending on the PRG pin. If the parallel input pins

are not connected (independent of high or low activity) it is guaranteed that the outputs 1 to 4

are switched OFF. PRG pin itself is internally pulled up when it is not connected.

PRG - Program pin.

V1.1

PRG = High (VS): Parallel inputs Channel 1 to 4 are high active

PRG = Low (GND): Parallel inputs Channel 1 to 4 are low active.

Page

26.Aug. 2002

Data Sheet TLE 6220 GP

Serial Control of the Outputs: SPI protocol

Each output is independently controlled by an output latch and a common reset line, which

disables all four outputs. The Serial Input (SI) is read on the falling edge of the serial clock. A

logic high input 'data bit' turns the respective output channel ON, a logic low 'data bit' turns it

OFF. CS must be low whilst shifting all the serial data into the device. A low-to-high transition

of CS transfers the serial data input bits to the output control buffer.

As mentioned above, the serial input byte consists of a 4 bit control word and a 4 bit data

word. Via the control word, the specific mode of the device is programmable.

MSB

LSB

CCCC DDDD : Serial input byte

! !

Control Bits Data Bits

Five specific control words are recognised, having the following functions:

No.

1

2

3

4

5

Serial Input Byte

LLLL XXXX

HHLL XXXX

HLHL XXXX

LLHH DDDD

HHHH DDDD

Function

Only 'Full Diagnosis' performed. No change to output states.

State of four parallel inputs and '1-bit Diagnosis' outputted.

Echo-function of SPI; SI direct connected to SO

IN1...4 and serial data bits 'OR'ed. 'Full Diagnosis' performed.

IN1...4 and serial data bits 'AND'ed. 'Full Diagnosis' performed.

Note: 'X' means 'don't care', because this bit will be ignored

'D' represents the data bit, either being H (=ON) or L (=OFF)

1. LLLL XXXX - Diagnosis only

By clocking in this control byte, it is possible to get pure diagnostic information (two bits per

channel) in accordance with Figure 1 (page 11). The data bits are ignored, so that the state of

the outputs are not influenced. This command is only active once unless the next control

command is again "Diagnosis only".

2. HHLL XXXX - Reading back of input, and 1-bit Diagnosis

If the TLE 6220 GP is used as bare die in a hybrid application, it is necessary to know if proper

connections exist between the C-port and parallel inputs. By entering HHLL as the control

word, the first four bits of the SO give the state of the parallel inputs, depending on the C

signals. By comparing the four IN-bits with the corresponding C-port signal, the necessary

connection between the C and the TLE 6220 can be verified - i.e. read back of the inputs.

The second 4-bit word fed out at the serial output contains 1-bit fault information of the outputs ( H = no fault, L = fault ). In the expression given below for the output byte, FX is the

fault bit for channel X.

MSB

LSB

IN4 IN3 IN2 IN1 F4 F3 F2 F1

V1.1

Page

: Serial Output byte

26.Aug. 2002

Data Sheet TLE 6220 GP

CS

SI

CS

CS

H H L L X X X X

SI

H H H H L H H L

SO H H H H H H H H

SO

IN4 IN3 IN2 IN1 F4 F3 F2 F1

SI command: No change of the

output state; reading back of

inputs and 1bit diagnosis

SO diagnosis: No fault, normal

function

SI command: AND-Operation;

Ch1 and 4 OFF, Ch2 and 3 ON.

SO diagnosis: State of four parallel

inputs and 1 bit diagnosis performed

SI

H H H H L L L L

SO H H H H H H H H

SI command: AND-Operation and

all channels OFF.

SO diagnosis: No fault, normal

function

3. HLHL XXXX - Echo-function of SPI

To check the proper function of the serial interface the TLE 6220 GP provides a "SPI Echo

Function". By entering HLHL as control word, SI and SO are connected during the next CS

period. By comparing the bits clocked in with the serial output bits, the proper function of the

SPI interface can be verified. This internal loop is only closed once (for one CS period).

CS

SI

CS

H L H L X X X X

SI

SI word

SO

SO H H H H L H H H

SI command: No change of the

output states; Echo function of SPI

SO diagnosis: Open load condition

at channel 2, other channels ok.

Echo-function of SPI, i.e. SI

directly connected to SO.

SI information will be accepted

during this cycle and the

outputs set accordingly after

chip select rising edge

4. LLHH DDDD - OR operation, and full diagnosis

With LLHH as the control word, each of the input signals IN1...IN4 are 'OR'ed with the corresponding data bits (DDDD).

IN 1...4

Output

Driver

Serial Input,

data bits 0...3

This OR operation enables the serial interface to switch the channel ON, even though the corresponding parallel input might be in the off state.

SPI Priority for ON-State

Also parallel control of the outputs is possible without an SPI input.

V1.1

Page

26.Aug. 2002

Data Sheet TLE 6220 GP

The OR-function is the default Boolean operation if the device restarts after a Reset, or when

the supply voltage is switched on for the first time.

If the OR operation is programmed it is latched until it is overwritten by the AND operation.

5. HHHH DDDD - AND operation, and full diagnosis

With HHHH as the control word, each of the input signals IN1...IN4 are 'AND'ed with the corresponding data bits (DDDD).

IN 1...4

&

Output

Driver

Serial Input,

data bits 0...3

The AND operation implies that the output can be switched off by the SPI data bit input, even

if the corresponding parallel input is in the ON state.

SPI Priority for OFF-state

This also implies that the serial input data bit can only switch the output channel ON if the corresponding parallel input is in the ON state.

If the AND operation is programmed it is latched until it is overwritten by the OR operation.

Control words beside No. 1- 5

All control words except those for Diag Only, Read Back of Inputs, SPI echo, will be accepted

as an OR or an AND command with valid data bits depending on the boolean operation which

was programmed before.

Example 1:

LLHH HLLH: OR operation between parallel inputs and data bits, i.e channel 1 and 4 will be

switched on.

The next command is now: LHHH HHLH

LHHH as command word has no special meaning but it will be accepted as an OR operation

and the data bits will be ORed with the inputs and the outputs 1,3 and 4 will be switched on.

See above: 'If the OR operation is programmed it is latched until it is overwritten by the AND

operation.'

Example 2:

HHHH LLHL means: Data bits will be ANDed with the parallel inputs and the outputs switch

accordingly. Then HLLH HHLH is clocked in: AND was latched by the command before and is

now valid again by using the HLLH command word. So the data bits will be accepted and

again ANDed with the parallel input signals.

See above: 'If the AND operation is programmed it is latched until it is overwritten by the OR

operation.'

V1.1

Page

10

26.Aug. 2002

Data Sheet TLE 6220 GP

Diagnostics

FAULT - Fault pin. There is a general fault pin (open drain) which shows a high to low transi-

tion as soon as an error occurs for any one of the four channels. This fault indication can be

used to generate a C interrupt. Therefore a diagnosis interrupt routine need only be called

after this fault indication. This saves processor time compared to a cyclic reading of the SO

information.

As soon as a fault occurs, the fault information is latched into the diagnosis register. A new

error will over-write the old error report. Serial data out pin (SO) is in a high impedance state

when CS is high. If CS receives a LOW signal, all diagnosis bits can be shifted out serially.

The rising edge of CS will reset all error registers.

Full Diagnosis

For full diagnosis there are two diagnostic bits per channel configured as shown in Figure 1.

Diagnostic Serial OUT (SO)

7

Ch.4

HH

HL

LH

LL

Ch.3

Ch.2

Ch.1

Normal function

Overload, Shorted Load or Overtemperature

Open Load

Shorted to Ground

Figure 1: Two bits per channel diagnostic feedback

Normal function: The bit combination HH indicates that there is no fault condition, i.e. normal

function.

Overload, Short Circuit to Battery (SCB) or Overtemperature: HL is set when the current

limitation gets active, i.e. there is a overload, short to supply or overtemperature condition.

Open load: An open load condition is detected when the drain voltage decreases below 3 V

(typ.). LH bit combination is set.

Short Circuit to GND: If a drain to ground short circuit exists and the drain to ground current

exceeds 100 A, short to ground is detected and the LL bit combination is set.

A definite distinction between open load and short to ground is guaranteed by design.

The standard way of obtaining diagnostic information is as follows:

Clock in serial information into SI pin and wait approximately 150 s to allow the outputs to

settle. Clock in the identical serial information once again - during this process the data coming out at SO contains the bit combinations representing the diagnosis conditions as described

in Figure 1.

V1.1

Page

11

26.Aug. 2002

Data Sheet TLE 6220 GP

Timing Diagrams

CS

SCLK

Control Bits

Data Bits

$""""%""""& $""""%""""&

SI

LSB

MSB

SO

Outputs

OLD

NEW

Figure 2: Serial Interface

Figure 3: Input Timing Diagram

CS

0.7VS

tdt

0.2 VS

tlag

tSCKH

SCLK

tlead

0.7VS

0.2VS

tSCKL

tSU

tH

0.7VS

SI

0.2VS

Figure 4:

0.7 V S

SC LK

CS

0.2 V S

t valid

t D is

SO

0.7 V S

0.2 V S

SO

SO

0.7 V S

0.2 V S

SO Valid Time Waveforms

V1.1

Enable and Disable Time Waveforms

Page

12

26.Aug. 2002

Data Sheet TLE 6220 GP

VIN

tOFF

tON

VDS

80%

20%

Figure 5: Power Outputs

Application Circuit

VBB

VS

10k

VS

PRG

OUT1

FAULT

OUT2

RESET

IN1

IN2

IN3

IN4

C

e.g. C166

V1.1

MTSR

SI

MRST

SO

CLK

CLK

P xy

CS

OUT4

TLE

6220

GP

GND

Page

13

26.Aug. 2002

Data Sheet TLE 6220 GP

Typical electrical Characteristics

Drain-Source on-resistance

RDS(ON) = f (Tj) ; Vs = 5V

Channel 1-4

Typical Drain- Source ON-Resistance

0,58

0,53

RDS(ON) [Ohm]

0,48

0,43

0,38

0,33

0,28

0,23

-50

-25

25

50

75

100

125

150

175

Tj[C]

Figure 6 :

Typical ON Resistance versus Junction-Temperature

Channel 1-4

Output Clamping Voltage

VDS(AZ) = f (Tj) ; Vs = 5V

Channel 1-4

Typical Clamping Voltage

55

54

VDS (AZ) [V]

53

52

51

50

49

48

-50

-25

25

50

75

100

125

150

175

Tj[C]

Figure 7 :

V1.1

Typical Clamp Voltage versus Junction-Temperature

Channel 1-4

Page

14

26.Aug. 2002

Data Sheet TLE 6220 GP

Parallel SPI Configuration

Engine Management Application

TLE 6230 GP in combination with TLE 6240 GP (16-fold switch) for relays and general purpose loads

and TLE 6220 GP (quad switch) to drive the injector valves. This arrangement covers the numerous

loads to be driven in a modern Engine Management/Powertrain system. From 28 channels in sum 16

can be controlled direct in parallel for PWM applications.

Injector 1

P x.1-4

4 PWM

Channels

MTSR

SI

SO

MRST

CS

Injector 3

TLE

6220 GP

Quad

CLK

CS

CLK

P x.y

Injector 2

Injector 4

4 PWM

Channels

P x.1-4

C

SI

SO

C167

CLK

P x.y

CS

TLE

6230 GP

Octal

8 PWM

Channels

P x.1-8

SI

SO

CLK

P x.y

CS

TLE

6240 GP

16-fold

Daisy Chain Application TLE 6220 GP

Px.1

Px.2

CS

MTSR

CLK

TLE

SO

6220 GP

CS

Quad

SI

CS

SI

CLK

TLE

SO

6220 GP

Quad

CS

SI

CLK

TLE

SO

6220 GP

Quad

MRST

V1.1

Page

15

26.Aug. 2002

Data Sheet TLE 6220 GP

Package and Ordering Code

(all dimensions in mm)

P - DSO - 20 - 12

Ordering Code

TLE 6220 GP

Q67006-A9315

1 5 .7 4 + /- 0 .1

13.7 -0.2

9 x 1.27 = 11.43

1.27

+ 0 .1 3

1.2

-0.3

0.25 M

5.9 + /-0 .1

11

3.2 + /-0 .1

20

0.4

10

1 x 45

P IN 1 IN D E X M A R K IN G

15.9 + /-0 .1 5

1.3

0.1

2.8

8

6.3

11 + /-0 .1 5 1 )

14.2 + /-0 .3

V1.1

Page

16

26.Aug. 2002

Data Sheet TLE 6220 GP

Published by

Infineon Technologies AG,

Bereichs Kommunikation

St.-Martin-Strasse 76,

D-81541 Mnchen

Infineon Technologies AG 1999

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits,

descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question

please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of

Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support

device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it

is reasonable to assume that the health of the user or other persons may be endangered.

V1.1

Page

17

26.Aug. 2002

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Tle6220gp DatasheetDocument18 pagesTle6220gp Datasheetmaelo99999No ratings yet

- 1-Tle6240gp V3 1 1Document24 pages1-Tle6240gp V3 1 1Alexandre Da Silva PintoNo ratings yet

- L9230Document25 pagesL9230Juan LouroNo ratings yet

- Datasheet STR 6757Document11 pagesDatasheet STR 6757Walter CarreroNo ratings yet

- Go-iris-A6159 Fuente TV Samsung LCD 32"Document7 pagesGo-iris-A6159 Fuente TV Samsung LCD 32"Daniel GómezNo ratings yet

- L6208D To L6208PDDocument16 pagesL6208D To L6208PDwtn2013No ratings yet

- 8K X 8 Bit Fast Static RAM MCM6264C: MotorolaDocument8 pages8K X 8 Bit Fast Static RAM MCM6264C: Motorolajackiie16No ratings yet

- IRIS-X6757: FeaturesDocument10 pagesIRIS-X6757: Featuresmiguel angel jaramilloNo ratings yet

- 7214Document12 pages7214Dan EsentherNo ratings yet

- STR W6735 DatasheetDocument13 pagesSTR W6735 DatasheetloagerNo ratings yet

- Tps 2051 BDocument29 pagesTps 2051 Bdragon-red0816No ratings yet

- STR W6753 DatasheetDocument8 pagesSTR W6753 DatasheetjgerabmNo ratings yet

- STR W6735Document14 pagesSTR W6735proctepNo ratings yet

- 128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLDocument11 pages128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLThiago Cristiano TavaresNo ratings yet

- STRW6252Document15 pagesSTRW6252miltoncgNo ratings yet

- MC6821PDocument10 pagesMC6821Pbobyof91No ratings yet

- SSC2001S Application NoteDocument18 pagesSSC2001S Application NoteGerardo Mendez CamarilloNo ratings yet

- Isppac 10: Features Functional Block DiagramDocument23 pagesIsppac 10: Features Functional Block DiagramFaiber CalderonNo ratings yet

- 32kx8bit CMOS SRAM: HY62256B SeriesDocument9 pages32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsrieNo ratings yet

- Datasheet PDFDocument15 pagesDatasheet PDFperro sNo ratings yet

- 60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsDocument14 pages60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsIBSDIALLO0% (1)

- LMD18200 3A, 55V H-Bridge: Features ApplicationsDocument19 pagesLMD18200 3A, 55V H-Bridge: Features ApplicationsLe NhanNo ratings yet

- A4954 DatasheetDocument9 pagesA4954 DatasheetAngly1959No ratings yet

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument18 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesMarco MenezesNo ratings yet

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument17 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesJorge Luis Castillo GuarachiNo ratings yet

- 2114 SramDocument4 pages2114 SramKarloz IbarraNo ratings yet

- CDP 1802 Data Sheet 2Document7 pagesCDP 1802 Data Sheet 2DaveNo ratings yet

- Hqew Tle5216Document17 pagesHqew Tle5216Olga PlohotnichenkoNo ratings yet

- LTC 1625Document24 pagesLTC 1625Sakura KunNo ratings yet

- 3000W Single Output Power Supply Spec SheetDocument6 pages3000W Single Output Power Supply Spec SheetGrigoriu CodrutaNo ratings yet

- 161 20551 0 FS7M0880Document16 pages161 20551 0 FS7M0880Edwin Vitovis TorresNo ratings yet

- MC 34152Document12 pagesMC 34152dcastrelos2000No ratings yet

- Microstepping DMOS Driver With Translator: Description Features and BenefitsDocument18 pagesMicrostepping DMOS Driver With Translator: Description Features and BenefitsSaid BoubkerNo ratings yet

- VND 7 N 04Document30 pagesVND 7 N 04Juan Guillermo MansillaNo ratings yet

- Nte 4013Document4 pagesNte 4013Codinasound CaNo ratings yet

- BTS5215LDocument14 pagesBTS5215LVanny Is AresNo ratings yet

- Quasi-Resonant Topology Primary Switching Regulators: STR-W6735Document13 pagesQuasi-Resonant Topology Primary Switching Regulators: STR-W6735perro sNo ratings yet

- CD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionDocument10 pagesCD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionWillianNo ratings yet

- Datasheet 8259 PIC OKIDocument29 pagesDatasheet 8259 PIC OKIasemenatokatevasoNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-X6769Document9 pagesOff-Line Quasi-Resonant Switching Regulators: STR-X6769Alfredo Valencia RodriguezNo ratings yet

- F2-08SIM Input Simulator D2-08NA-1 AC InputDocument10 pagesF2-08SIM Input Simulator D2-08NA-1 AC InputVladimir Aliro Quezada CidNo ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- Adc 0804 PDFDocument18 pagesAdc 0804 PDFCinthya VillenaNo ratings yet

- Features Description: Ltc3633 Dual Channel 3A, 15V Monolithic Synchronous Step-Down RegulatorDocument28 pagesFeatures Description: Ltc3633 Dual Channel 3A, 15V Monolithic Synchronous Step-Down RegulatorMichael LeeNo ratings yet

- 5M0380RDocument20 pages5M0380RGenaro Santiago MartinezNo ratings yet

- IC-ON-LINE - CN dm0365r 44840Document20 pagesIC-ON-LINE - CN dm0365r 44840MoscandoNo ratings yet

- 74C373Document11 pages74C373Juan Orlando MontesNo ratings yet

- ST3232 Data SheetDocument12 pagesST3232 Data SheetcredioNo ratings yet

- Green Mode PWM Controller Ap384XgDocument13 pagesGreen Mode PWM Controller Ap384XgbaphometabaddonNo ratings yet

- Magna MAX7326 Port ExpanderDocument20 pagesMagna MAX7326 Port ExpanderSudip Mondal100% (1)

- Infineon BTS6143D DS v01 00 enDocument18 pagesInfineon BTS6143D DS v01 00 enNacer MezghicheNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-X6729Document9 pagesOff-Line Quasi-Resonant Switching Regulators: STR-X6729perro sNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Cicuit Temp Air y OleoDocument12 pagesCicuit Temp Air y OleoFabio JuniorNo ratings yet

- K-Suite 1.89Document3 pagesK-Suite 1.89Fabio JuniorNo ratings yet

- Drawings PO80335843Document8 pagesDrawings PO80335843Fabio JuniorNo ratings yet

- F63 Series Liquid Level Float SwitchDocument8 pagesF63 Series Liquid Level Float SwitchFabio JuniorNo ratings yet

- InteliGen 6.0 PDFDocument19 pagesInteliGen 6.0 PDFFabio JuniorNo ratings yet

- F63 SeriesDocument3 pagesF63 SeriesFabio JuniorNo ratings yet

- LINC L471manualDocument20 pagesLINC L471manualFabio JuniorNo ratings yet

- InteliGen 6.0 PDFDocument19 pagesInteliGen 6.0 PDFFabio JuniorNo ratings yet

- ELC Data SheetDocument2 pagesELC Data SheetFabio Junior100% (1)

- 1117 RTDDocument5 pages1117 RTDNa Rukok Sibak JoeNo ratings yet

- Liquid Level Float Switch: Description AccessoriesDocument1 pageLiquid Level Float Switch: Description AccessoriesFabio JuniorNo ratings yet

- Emerson Thermowell Pressure RatingDocument1 pageEmerson Thermowell Pressure RatingFabio JuniorNo ratings yet

- Anzex 07 3081 VM WSVMDocument14 pagesAnzex 07 3081 VM WSVMFabio Junior0% (1)

- NVS Needle ValveDocument1 pageNVS Needle ValveFabio JuniorNo ratings yet

- Farris 3800 ManualDocument12 pagesFarris 3800 ManualNelson AlvarezNo ratings yet

- L471 VerDocument18 pagesL471 VerFabio JuniorNo ratings yet

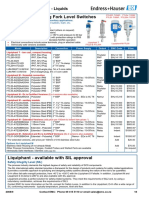

- Liquiphant Vibrating Fork Level SwitchesDocument1 pageLiquiphant Vibrating Fork Level SwitchesFabio JuniorNo ratings yet

- Asco - Iom 327 SeriesDocument4 pagesAsco - Iom 327 SeriesFabio JuniorNo ratings yet

- LFR-D enDocument16 pagesLFR-D enFabio JuniorNo ratings yet

- Mcm3320 Servico 2012 InglesDocument312 pagesMcm3320 Servico 2012 InglesFabio Junior100% (2)

- C-11, C-13, C-15 TS Manual 2006 PDFDocument420 pagesC-11, C-13, C-15 TS Manual 2006 PDFFabio Junior83% (6)

- Cat Electronic Tech Nician 2014A v1.0Document27 pagesCat Electronic Tech Nician 2014A v1.0Fabio JuniorNo ratings yet

- MC68 Adm PDFDocument128 pagesMC68 Adm PDFFabio JuniorNo ratings yet

- In Pulse™ II: ApplicationsDocument4 pagesIn Pulse™ II: ApplicationsFabio JuniorNo ratings yet

- An951 PDFDocument14 pagesAn951 PDFFabio JuniorNo ratings yet

- XC9572 In-System Programmable CPLD: Figure 1: Typical I vs. Frequency For XC9572Document8 pagesXC9572 In-System Programmable CPLD: Figure 1: Typical I vs. Frequency For XC9572Siddhi Nitin MahajanNo ratings yet

- Data Sheet PDFDocument13 pagesData Sheet PDFFabio JuniorNo ratings yet

- Tle 6220 PDFDocument17 pagesTle 6220 PDFFabio JuniorNo ratings yet

- XC9572 In-System Programmable CPLD: Features DescriptionDocument9 pagesXC9572 In-System Programmable CPLD: Features DescriptionManish PushkarNo ratings yet

- Cs 601Document23 pagesCs 601chiNo ratings yet

- 1. Advance Microwave TrainingDocument51 pages1. Advance Microwave TrainingDAVID SAMUEL FRIDAYNo ratings yet

- Radio Altimeter ExplainedDocument4 pagesRadio Altimeter ExplainedKoustubh VadalkarNo ratings yet

- Programmable Logic Controllers ManualDocument171 pagesProgrammable Logic Controllers Manualfarhan usmanNo ratings yet

- Alternador Delco RemyDocument1 pageAlternador Delco RemyJuan Carlos SoHeNo ratings yet

- Rohit Arora Specimen FileDocument5 pagesRohit Arora Specimen FileHimesh JainNo ratings yet

- SyncServer-S200-Enterprise Class GPS Network Time ServerDocument2 pagesSyncServer-S200-Enterprise Class GPS Network Time ServersandmanpayneNo ratings yet

- Datasheet-LDALI CEA709 ControllerDocument5 pagesDatasheet-LDALI CEA709 ControllerЂорђе ЈевтовићNo ratings yet

- Specifications For Planar TD2 TileDocument2 pagesSpecifications For Planar TD2 TileRPhillipsVMPNo ratings yet

- L3 RF Troubleshooting Guide XT1650-01-XT1650-02-XT1650-03-XT1650-05 V1.0.pdf MOTO Z PDFDocument298 pagesL3 RF Troubleshooting Guide XT1650-01-XT1650-02-XT1650-03-XT1650-05 V1.0.pdf MOTO Z PDFesdiguenNo ratings yet

- Applications and Characteristics of Overcurrent Relays (ANSI 50, 51)Document6 pagesApplications and Characteristics of Overcurrent Relays (ANSI 50, 51)catalinccNo ratings yet

- GeiDocument2 pagesGeisansureNo ratings yet

- b8 Digi Anywhereusb Plus DsDocument4 pagesb8 Digi Anywhereusb Plus DsClem CZNo ratings yet

- Enhancement of ALSA Firewire Stack: AcknowledgementDocument65 pagesEnhancement of ALSA Firewire Stack: AcknowledgementBNo ratings yet

- Nortel proprietary handling instructionsDocument38 pagesNortel proprietary handling instructionsjose de la rivaNo ratings yet

- Detailed Syllabus - Optical CommunicationDocument3 pagesDetailed Syllabus - Optical Communicationiamitgarg7No ratings yet

- Text Books:: 3 G.T.Heydt, "Electric Power Quality", Stars in A Circle Publications, 1994Document1 pageText Books:: 3 G.T.Heydt, "Electric Power Quality", Stars in A Circle Publications, 1994Jagadish Babu KondraguntaNo ratings yet

- Brochure Lisa CabinetDocument2 pagesBrochure Lisa CabinetLoloy NorybNo ratings yet

- 通用电气GE Optima CT520Pro 全身用X射线计算机体层摄影装置7f0Document22 pages通用电气GE Optima CT520Pro 全身用X射线计算机体层摄影装置7f0service iyadMedicalNo ratings yet

- Pioneer Receiver - VSX-D512 - Service ManualDocument74 pagesPioneer Receiver - VSX-D512 - Service Manualtony castillo100% (1)

- DATASHEET User Info 250W Power Puck 0 - 95Document4 pagesDATASHEET User Info 250W Power Puck 0 - 95bilgesu7kediNo ratings yet

- Design and Implementation of Hamming Code Using VHDL & DSCH: Divya Mokara, Sushmi Naidu, Akash Kumar GuptaDocument8 pagesDesign and Implementation of Hamming Code Using VHDL & DSCH: Divya Mokara, Sushmi Naidu, Akash Kumar GuptaAbdulrahman behiryNo ratings yet

- Baofeng UV-5R - Reference 4x6Document8 pagesBaofeng UV-5R - Reference 4x6compte emailNo ratings yet

- Zelda Welding Machine CatalogDocument72 pagesZelda Welding Machine CatalogJuan Manuel Suarez OreNo ratings yet

- Router BoardDocument6 pagesRouter BoardISLAMIC LIBRARYNo ratings yet

- Symo GEN24 Full Backup2Document172 pagesSymo GEN24 Full Backup2Mihai RaduNo ratings yet

- 2nd Order Band Pass Chebyshev 0.5 DB Active Filter Design Assignment 2 KHZ - 4 KHZDocument7 pages2nd Order Band Pass Chebyshev 0.5 DB Active Filter Design Assignment 2 KHZ - 4 KHZBuddhiNo ratings yet

- Battery Charger CTEK - MXS 5.0 - ENDocument6 pagesBattery Charger CTEK - MXS 5.0 - ENVladimirNo ratings yet

- Introduction To Multimedia SystemDocument20 pagesIntroduction To Multimedia SystemMichelle Angelie Pudiquet100% (1)

- DCR-TRV240 - 340DCR-TRV240 - 340 L2-v1 L2-v1 (1) .3Document181 pagesDCR-TRV240 - 340DCR-TRV240 - 340 L2-v1 L2-v1 (1) .3domisoftNo ratings yet