Professional Documents

Culture Documents

2.4 GHZ LNA Filter Desing

Uploaded by

NikhilAKothariOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2.4 GHZ LNA Filter Desing

Uploaded by

NikhilAKothariCopyright:

Available Formats

International Journal of Computer Applications (0975 8887)

Volume 88 No.2, February 2014

Design 2.4 GHz 130nm CMOS Low Noise Amplifier

Design for Wireless Network

Aniket Dhongde

Prashant Indurkar

Ravindra Kadam

Dept.of Elec. & Tele Engg

Dept.of Elec. & Tele Engg

Dept.of Elec. & Tele Engg

B.D.College of Engineering

Sevagram, Wardha (M.S),

India

B.D.College of Engineering

Sevagram, Wardha (M.S),

India

B.D.College of Engineering

Sevagram, Wardha (M.S),

India

ABSTRACT

A low noise amplifier is one of the most commonly used

components in analog and digital circuit designs. Low voltage,

low power and low noise amplifier design has become an

increasingly interesting subject as many applications switch to

portable battery powered operations. An amplifier is linear

electronic circuits that may used amplify an input signal and

provide an output signal that is a magnified replica of the input

signal. The need for design techniques to allow amplifiers to

maintain an acceptable level of performance when the supply

voltages are decreased is immense for maintain high gain and

as low as possible noise. Popular LNA topologies are the

inductive source degeneration common-source low noise

amplifier. The common source low noise amplifier is

commonly used for narrow-band applications due to its ease of

input matching, high gain and low noise. Using this method,

overall gain can be increased and the noise figure of the low

noise amplifier can be decreased.. This work we presents a

design of a low noise CMOS amplifier realized in a standard

130 nm CMOS technology with 1.3V supply voltage and

consumes power less than 200uW with <1.5mA current. A

two stage cascode LNA has to achieved noise figure is less

than 2.5dB and achieves a gain >18dB on given frequency

range also have good input and output matching.

Keywords

Two stage, low noise amplifier cascode, CMOS, gain , noise

and power.

1. INTRODUCTION

A low noise amplifier is the first block of receiver also it is key

building block in analog circuit design. Now a days CMOS

become a very fast growing technology for a radio

transreceiver

implementation

of

various

wireless

communication system due to technology scaling. In RF front

end is easy to integration with digital blocks by using CMOS

whole system on single chip. LNA design very much used for

telemetry wireless systems. It has large number of various

sensors and attenuators. Typically first block of a receiver is

LNA. There are several topologies for narrow band single

ended LNA design, an appropriate Topology should be

selected for low power and low voltage optimized LNA

design. For Common gate topology, the gain is less than 10.0

dB with very low power consumption. For shunt series

feedback common source topology, it is difficult to trade off

among gain, small noise figure and better input/output

matching with very low power consumption. Resistor

termination common source topology adds noise to the LNA

because of the resistor thermal noise. Inductive degeneration

common source topology satisfies the specification in very low

power consumption, but the isolation is not good enough

compared to the cascade inductor source degeneration

topology, which can get the similar low noise amplifier

performance with very low power consumption. Above all, the

cascode inductor source degeneration topology provides higher

gain with a low noise figure. For all designs, the circuit's input

matching, noise factor and gain have been derived to verify the

design methodology. The whole performance of any receiver

directly depend upon LNA gain and noise figure. It used such a

design has low noise with a high linearity IIP3 and stable 50

impedance to terminates. The transmission line length is

provide signal from antenna to amplifier. Input matching

increases the overall performance of LNA and each stage of

blocks. The LNA is designed as ISM band 2.4GHz frequency

using 130nm CMOS technology.

2. LNA DESIGN OBJECTIVES

One of the most important features in low noise amplifier

designs is ensuring that the amplifier maintains constant gain

as well as noise at given narrowband frequency. 2.4 GHz

CMOS 130nm Low Noise Amplifier is optimize for low noise

at low current with very low power consumption .Here, we use

inductive source degeneration common source topology, it

helps to give very low noise figure and high gain. The interstage matching between two stages are off-chip, which reduce

chip size. Another objective of this design is that, it is widely

applicable for Bluetooth, WI-FI, ISM band, Mobile phones and

handset. The low noise amplifier is the most important block at

the receiver side which amplifies the week signal, for

Bluetooth there is transmitting and receiving section for

communication and transfer of data.

3. TECHNIUES FOR LOW NOISE

AMPLIFIER DESIGN

There have been a number of works that have explored how to

achieve high gain with minimum noise figure. Inductive source

degeneration common source topology used to maintain the

minimum noise so we used this topology. There are several

topology to design the LNA some for the high gain and some

for minimum noise but mostly depends upon the current and

voltage parameter. To achieved high gain as well as low noise

by using inductive source degeneration topology with two

stage to improve gain but it also have its some disadvantages.

3.1 Design Differential Amplifier for Low

Power and Low Noise

In this LNA[1 In this paper, a low power low noise amplifier

for wireless sensor networks applications was presented. To

reduce the LNAs power consumption and chip area, a twostage cascade common-gate topology and an internal new

designed inductor were used to achieve the input and the

output matching. The LNA contained gain control circuit and

frequency control

circuit to adapt the deviations of process and the

environments.

It is provides a low power low noise differential amplifier

designed for Wireless Sensor Network (WSN) in TSMC 0.18

47

International Journal of Computer Applications (0975 8887)

Volume 88 No.2, February 2014

m RF CMOS process. It should work well centered at 2.44

GHz frequency and the forward gain is variable with highest

gain at 12 dB to lowest gain at -2 dB by 2dB steps. It also has

a two-stage cascade common-gate (CG)topology and two

external inductor choke coils are used to achieve input

matching of LNA under low power consumption, and a

differential inductor has been designed as the load to achieve

reasonable gain and reduce chip area simultaneously. The NF

(Noise Figure) at high gain (12.5 dB) is 3.9 dB, the input

referenced 1dB compression point (IP1dB) is about -1 dBm at

lowest gain mode. The LNA consumes about 1.5 mA current

from 1.8 V power supply.

Figure 2 Resistive feedback LNA

3.3 Low Noise Amplifier with utilizing

-match and capacitive feedback input

network

Fig.1 (a)

Fig.1 (b)

Figure 1 (a) Schematic of the LNA and (b) Double- circuit

model for inductor

3.2 Low Noise Amplifier Based on

Inductor less Shunt-Shunt Topology

This LNA [3] employs an improved gain by using capacitive

feedback. An ultra low-power CMOS low noise amplifier

(LNA) with a new input matching topology will be proposed

and analyzed. The LNA design is based on the capacitive

feedback in conjunction with a -match network. The proposed

LNA saves on chip area by using only one inductor for the

input matching. The -match network introduces an additional

degree of design freedom and allows the LNA to achieve

higher gain. The LNA is designed for 2.4 GHz ISM band in a

130 nm RF-CMOS process. It achieves a gain of 25.2 dB with

an Sll of -14 dB while consuming only 0.6 mW. The noise

figure (NF) is 3.8 dB. The design makes use of the capacitive

feedback and the -match network to realize the input

matching. The design method was explained and the LNA was

designed. Number of inductors used was reduced and higher

gain was achieved when compared to the L-CSLNA. The

proposed LNA consumes only 0.6 mW while providing very

high gain, good input matching and moderate NF and linearity.

This LNA consumes about 0.6 mA current from 1V power

supply

This CMOS LNA[2] A common-source topology with

resistive feedback in a shunt-shunt configuration as represented

in Fig. 2 compromise. For frequencies at which sCgs is

negligible in comparison with gm, the input impedance is

almost real and equal to 1/gm and if gm is high enough it is

possible to have the voltage gain and the input impedance

dimensioned almost independently. The proposed circuit is low

cost and power efficient. To be low cost the circuit is inductor

less and implemented in a standard nanoscale digital CMOS

technology, with a state-of-the-art figure for area. To be power

efficient all the circuits were chosen based on their power

efficiency.

The result shows that a NF (Noise Figure) at high gain (16.5

dB) is 2.66 dB, the input referenced 1dB compression point

(IP1dB) is about -21.8 dBm. This LNA consumes about 2.68

mA current from 1.2 V power supply.

Figure 3 (a) Inductive source-degeneration CSLNA (b)

Capacitive feedback LNA

48

International Journal of Computer Applications (0975 8887)

Volume 88 No.2, February 2014

Figure 4 (b)

Figure 3 (c) Schematic of LNA

3.4 Proposed LNA with cascade inductive

source degeneration topology

For the designing of a low noise amplifier (LNA) it seems

appropriate to establish what the target specifications are. This

is done in terms of a number of various parameters like Sparameter calculation in which we calculate the Gain (S21),

Input return loss (S11), Output return loss (S22), and Isolation.

S-parameter is mostly used for high frequency circuit design.

The cascaded architecture provides a good input output

impedance matching. By using cascaded transistor its

minimize the Millers capacitance. For gain boosting the inter

stage inductor is used between two transistors. By using this

the parasitic capacitance form impedance match network

between input stage and cascoded stage which boost gain and

lower the noise figure. Also used the high-quality factor

inductor is difficult to implement on chip with CMOS

technology. If It is implemented then it will consumes a large

area. So to ensure the normal operation of the on-chip inductor,

the distance between the inductor and any other components

(which include the interconnection metal wire) it should be a

Figure 4 (c)

Figure 4 (a) LNA architecture (b) Inter stage inductor

for gain boosting (c) Matching circuit

minimum length while designing the layout. The parasitic

resistance of a large inductor contributes large thermal noise.

So that use of large-value inductors should be avoided. The

proposed Low Noise CMOS amplifier realized in a standard

130 nm CMOS technology with 1.3V supply voltage and

consumes power less than 200uW with <1.5mA current. A

two stage cascode LNA has to achieved noise figure is less

than 2.5dB and achieves a gain >18dB on given frequency

range also have good input and output matching.

Figure 4 (a)

49

International Journal of Computer Applications (0975 8887)

Volume 88 No.2, February 2014

4. COMPARISON AND DISCUSSION

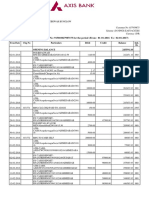

Table 1

Ref .

Paper 1.

technology

Supply Voltage

0.13

um

1.8 V

0.13

um

1.2V

0.13

um

1.7V

[2] Andr Esteves, Jos Dores, Pedro Matos, Miguel A.

Martins, Jorge R. Fernandes An ISM 2.4 GHz Low-IF

Receiver Frontend 978-1-4244-9474-3/11 2011 IEEE

Gain

12.5dB

16.5 dB

25.2dB

[3] Thi Thu Nga Tran, Chim Chye Boon ,Manh Anh Do, and

Kiat Seng Yeo A 2.4 GHz ultra low-power high gain

LNA utilizingx-match and capacitive feedback input

network 978-1-61284-857-0/11@2011 IEEE

Noise

3.9dB

2.66dB

3.8dB

S11

-16

-11.8

-14

-17

-15

Ref.

Paper 3.

6. REFERENCES

parameters

S12

Ref.

Paper 2.

Noise Amplifier can provides high gain > 18dB and less Noise

figure < 2.5dB at the expense of low power consumption.

-18

Power

2.7mW/

8.61mW/

0.6mW/

consumption

1.5mA

2.68mA

0.36mA

and current

As we can see from the above comparison table the proposed

Low Noise Amplifier provides high gain and low noise as

compared to [1],[2],[3] LNA. Proposed LNA has relatively

simple circuitry for gain boosting as compared to the rest of the

configuration.

5. CONCLUSION

Different methodologies for Low Noise Amplifier design has

been seen above. It shows that Low Noise Amplifier has a

differential pair [1] and Low Noise Amplifier with Capacitive

Feedback with -matching Technique [3] has better gain and

noise. Proposed Low Noise Amplifier Circuit less power

consumption than rest of the techniques. The proposed Low

IJCATM : www.ijcaonline.org

[1] Meng Zhang 1, 2, 3, Zhiqun Li 1, 2, 3 A 2.4 GHz Low

Power Common-Gate Low Noise Amplifier for Wireless

Sensor Network Applications 978-1-61284-307-0/11

2011 IEEE

[4] T.T.N. Tran, C.C. Boon, M.A. Do and K.S. Yeo Ultra-low

power series input resonance differential common gate

LNA ELECTRONICS LETTERS 9th June 2011 Vol. 47

No. 12

[5] Franois Belmas1, Frdric Hameau1, Jean-Michel

Fournier2 A 1.3mW 20dB Gain Low Power Inductorless

LNA with 4dB Noise Figure for 2.45GHz ISM Band

978-1-4244-8292-4/11 2011 IEEE

[6] Sambit Datta*, Kunal Datta*, Ashudeb Dutta#, Tarun

Kanti Bhattacharyya* A Concurrent Low-Area Dual

Band 0.9/2.4 GHz LNA in 0.13m RF CMOS

Technology for Multi- Band Wireless Receiver 978-14244-7456-1/10 2010 IEEE

[7] R.J. Baker, CMOS Circuit Design, Layout and

Simulation, 2nd edition, IEEE Press, 2005.

[8] P. E. Allen and D. R. Holberg, CMOS Analog Circuit

Design, 2nd edition, Oxford University Press, 2002

[9] B. Razavi, Design of analog CMOS integrated circuits,

McGraw-Hill, 2000.

[10] D. Johns and K. Martin, Analog integrated circuit

design, in John Wiley & Sons, New York, 1997.

50

You might also like

- Electronics & Communication Department: BY Nethravathi.R 1CR17EC119Document11 pagesElectronics & Communication Department: BY Nethravathi.R 1CR17EC119Nethravathi. RNo ratings yet

- Design and Analysis of 2.4 GHZ Low-Noise, High-Gain 0.18 M Cmos Cascode Low-Noise Amplifier For Irnss ApplicationsDocument12 pagesDesign and Analysis of 2.4 GHZ Low-Noise, High-Gain 0.18 M Cmos Cascode Low-Noise Amplifier For Irnss ApplicationsRami Reddy100% (1)

- Low Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationsDocument5 pagesLow Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationssunilsheelavantNo ratings yet

- LNADocument11 pagesLNASunil KumarNo ratings yet

- Ijisa V4 N9 9Document7 pagesIjisa V4 N9 9Đức QuangNo ratings yet

- Ijermt V-3-1-9Document6 pagesIjermt V-3-1-9Mohammad Mahmudul Hasan TareqNo ratings yet

- Write UpDocument3 pagesWrite Upabhi_jNo ratings yet

- Low Noise Amplifier ThesisDocument8 pagesLow Noise Amplifier Thesisrikkiwrightarlington100% (2)

- Huang 2006Document3 pagesHuang 2006Qazi KamalNo ratings yet

- 4 PDFDocument7 pages4 PDFPramod PuttaNo ratings yet

- Ultra Low Noise Figure, Low Power Consumption Ku-Band LNA With High Gain For Space ApplicationDocument4 pagesUltra Low Noise Figure, Low Power Consumption Ku-Band LNA With High Gain For Space ApplicationPranjal JalanNo ratings yet

- New Report LNADocument51 pagesNew Report LNASaravanan NsNo ratings yet

- Implementation of LNADocument7 pagesImplementation of LNAns saravananNo ratings yet

- Design of Pseudomorphic High Electron Mobility Transistor Based Ultra Wideband Amplifier Using Stepped Impedance Stub MatchingDocument6 pagesDesign of Pseudomorphic High Electron Mobility Transistor Based Ultra Wideband Amplifier Using Stepped Impedance Stub MatchingAJER JOURNALNo ratings yet

- An Optimized High Gain CMOS LNA Using Simulated Annealing and Modified Genetic Algorithm EhrampooshDocument7 pagesAn Optimized High Gain CMOS LNA Using Simulated Annealing and Modified Genetic Algorithm EhrampooshOmarFaruqeNo ratings yet

- RF LNA Design and Performance Analysis in CMOSDocument56 pagesRF LNA Design and Performance Analysis in CMOSPranjal JalanNo ratings yet

- Chen 2007Document3 pagesChen 2007Moustapha BakNo ratings yet

- Design of 1.8V 1Ghz 0.18 Mu M Cmos Lna For GPS: October 2008Document5 pagesDesign of 1.8V 1Ghz 0.18 Mu M Cmos Lna For GPS: October 2008Dũng ĐặngNo ratings yet

- A Low Power, Low Noise Amplifier For Recording Neural SignalsDocument8 pagesA Low Power, Low Noise Amplifier For Recording Neural SignalsIAES IJAINo ratings yet

- 2.294dB Noise-Figure RF Wideband PHEMT LNADocument7 pages2.294dB Noise-Figure RF Wideband PHEMT LNAPaul ShineNo ratings yet

- 16Document6 pages16Isnaldi NasrulNo ratings yet

- V-Band GaAs Metamorphic Low-Noise Amplifier Design Technique For Sharp Gain Roll-Off at Lower FrequenciesDocument4 pagesV-Band GaAs Metamorphic Low-Noise Amplifier Design Technique For Sharp Gain Roll-Off at Lower Frequencieskarthik srivatsa mbNo ratings yet

- Fully Integrated CMOS GPS Radio Seminar ReportDocument26 pagesFully Integrated CMOS GPS Radio Seminar ReportUddipan ChatterjeeNo ratings yet

- Cmos Lna ThesisDocument5 pagesCmos Lna Thesischristinewhitebillings100% (2)

- Design of A 2.0 GHZ Low Noise AmplifierDocument4 pagesDesign of A 2.0 GHZ Low Noise AmplifierVaibhav TiwariNo ratings yet

- 2.4-Ghz Single-Ended Input Low-Power Low-Voltage Active Front-End For Zigbee Applications in 90 NM CmosDocument4 pages2.4-Ghz Single-Ended Input Low-Power Low-Voltage Active Front-End For Zigbee Applications in 90 NM CmosdilixyzNo ratings yet

- 4ghz Low Noise Amplifier For Satellite D ImpDocument5 pages4ghz Low Noise Amplifier For Satellite D ImpAbhishek JajuNo ratings yet

- A 1.5V 1.5GHz CMOS LNADocument16 pagesA 1.5V 1.5GHz CMOS LNAptt3iNo ratings yet

- Bhavna P2Document6 pagesBhavna P2swapnil jainNo ratings yet

- Low Noise Amplifier Lna DesignDocument9 pagesLow Noise Amplifier Lna Designintissar abbesNo ratings yet

- High Frequency Low Cost CMOS LNA Design Procedure For The Wireless IndustryDocument4 pagesHigh Frequency Low Cost CMOS LNA Design Procedure For The Wireless IndustryjaberyemeniNo ratings yet

- 08268871Document4 pages08268871ChandreshSinghNo ratings yet

- PPD1041Document6 pagesPPD1041eNo ratings yet

- A Low Noise and Power Consumption, High-Gain Lna in 130 NM Sige Bicmos Using Transmission LinesDocument4 pagesA Low Noise and Power Consumption, High-Gain Lna in 130 NM Sige Bicmos Using Transmission LinessaidNo ratings yet

- Ultra-Wideband Low Noise Amplifier Using A Cascode Feedback TopologyDocument3 pagesUltra-Wideband Low Noise Amplifier Using A Cascode Feedback TopologyAsad AsadiNo ratings yet

- Design Of A 4-6Ghz Wideband Lna In 0.13Μm Cmos Technology: Sana Arshad, Faiza Zafar And Qamar-Ul WahabDocument5 pagesDesign Of A 4-6Ghz Wideband Lna In 0.13Μm Cmos Technology: Sana Arshad, Faiza Zafar And Qamar-Ul WahabGayathri SrinivasaNo ratings yet

- A Systematic Approach To CMOS Low Noise Amplifier Design For Low Power TransmissionDocument4 pagesA Systematic Approach To CMOS Low Noise Amplifier Design For Low Power TransmissionGanagadhar CHNo ratings yet

- A 1.5-V, 1.5-GHz CMOS Low Noise Amplifier - Solid-State Circuits, IEEE Journal of PDFDocument15 pagesA 1.5-V, 1.5-GHz CMOS Low Noise Amplifier - Solid-State Circuits, IEEE Journal of PDFAnirban HomroyNo ratings yet

- A High-Gain Power-Efficient Wideband V-Band LNA in 0.18-M Sige BicmosDocument3 pagesA High-Gain Power-Efficient Wideband V-Band LNA in 0.18-M Sige BicmosOmarFaruqeNo ratings yet

- A Broadband Low Noise Amplifier Mmic in 0.15M Gaas Phemt TechnologyDocument3 pagesA Broadband Low Noise Amplifier Mmic in 0.15M Gaas Phemt TechnologyNouha Al-MajedNo ratings yet

- A 24-Ghz Active Patch Array: Dai Lu, Milan Kovacevic, Jon Hacker and David RutledgeDocument12 pagesA 24-Ghz Active Patch Array: Dai Lu, Milan Kovacevic, Jon Hacker and David RutledgeDilaawaiz FazalNo ratings yet

- Design of PHEMT UWB Amplifier Using Stepped Impedance Stub MatchingDocument6 pagesDesign of PHEMT UWB Amplifier Using Stepped Impedance Stub MatchingRahul YadavNo ratings yet

- 5yilmaz Tezel LNADocument4 pages5yilmaz Tezel LNAhgNo ratings yet

- LNA DesignDocument5 pagesLNA DesignChetan NegiNo ratings yet

- A 5-Ghz Direct-Conversion Cmos Transceiver Utilizing Automatic Frequency Control For The Ieee 802.11A Wireless Lan StandardDocument12 pagesA 5-Ghz Direct-Conversion Cmos Transceiver Utilizing Automatic Frequency Control For The Ieee 802.11A Wireless Lan StandardJasmin Torres GodoyNo ratings yet

- Analysis and Design of Inductorless Wideband Low-Noise Amplifier With Noise Cancellation TechniqueDocument8 pagesAnalysis and Design of Inductorless Wideband Low-Noise Amplifier With Noise Cancellation TechniqueDHEERAJ KALRANo ratings yet

- RFIC Group: Advanced VLSI Design Lab IIT KharagpurDocument7 pagesRFIC Group: Advanced VLSI Design Lab IIT Kharagpurg.ven18No ratings yet

- Electronics 12 00696Document15 pagesElectronics 12 00696myusufNo ratings yet

- Low Noise Amplifier: Project Report Cmos RficDocument11 pagesLow Noise Amplifier: Project Report Cmos RficNivin PaulNo ratings yet

- A Direct-Conversion CMOS Transceiver For The 802.11a/b/g WLAN Standard Utilizing A Cartesian Feedback TransmitterDocument13 pagesA Direct-Conversion CMOS Transceiver For The 802.11a/b/g WLAN Standard Utilizing A Cartesian Feedback TransmitterdeviNo ratings yet

- Q-Band Low Noise Amplifiers Using A 0.15 - M MHEMT Process For Broadband Communication and Radio Astronomy ApplicationsDocument4 pagesQ-Band Low Noise Amplifiers Using A 0.15 - M MHEMT Process For Broadband Communication and Radio Astronomy ApplicationsAli HattabNo ratings yet

- A 20 GHZ Low Noise Amplifier With Active Balun in A 025 Um SigeDocument9 pagesA 20 GHZ Low Noise Amplifier With Active Balun in A 025 Um SigesaidNo ratings yet

- A 1.5-V 1.5-GHz CMOS Low Noise Amplifier Shafer IEEE JSSC 97Document15 pagesA 1.5-V 1.5-GHz CMOS Low Noise Amplifier Shafer IEEE JSSC 97Abid MullaNo ratings yet

- Cmos Low Noise Amplifier Design For Microwave and Mmwave ApplicationsDocument29 pagesCmos Low Noise Amplifier Design For Microwave and Mmwave ApplicationsAkhendra KumarNo ratings yet

- A 2.4-Ghz Low-Flicker-Noise Cmos Sub-Harmonic ReceiverDocument11 pagesA 2.4-Ghz Low-Flicker-Noise Cmos Sub-Harmonic ReceiverdabalejoNo ratings yet

- 10 35378-Gujs 998008-1984598Document11 pages10 35378-Gujs 998008-1984598nguyentienduy1512No ratings yet

- The Technical Working of Low Noise AmplifierDocument11 pagesThe Technical Working of Low Noise AmplifierjackNo ratings yet

- SAMPLE PaperDocument5 pagesSAMPLE PaperDeepika KumariNo ratings yet

- A 0.2-2.6 GHZ Wideband Noise-ReductionDocument3 pagesA 0.2-2.6 GHZ Wideband Noise-ReductionMohammad MousavikNo ratings yet

- Mosling Consulting Target CV - 2012.10.18Document3 pagesMosling Consulting Target CV - 2012.10.18NikhilAKothariNo ratings yet

- Skill Matrix - v1.3 - 20161203Document2 pagesSkill Matrix - v1.3 - 20161203NikhilAKothariNo ratings yet

- AMS VerificationDocument16 pagesAMS VerificationNikhilAKothariNo ratings yet

- AuthenticationDocument3 pagesAuthenticationNikhilAKothariNo ratings yet

- Interpritation of ColorsDocument4 pagesInterpritation of ColorsNikhilAKothariNo ratings yet

- 3D IC TechnologyDocument33 pages3D IC TechnologyNikhilAKothariNo ratings yet

- Face ReadingDocument6 pagesFace ReadingNikhilAKothariNo ratings yet

- Analog Cmos Design 09Document46 pagesAnalog Cmos Design 09rrajmohan28No ratings yet

- 20 NMDocument35 pages20 NMNikhilAKothariNo ratings yet

- 14 NMDocument23 pages14 NMNikhilAKothariNo ratings yet

- CCNAv3 All Question PDFDocument16 pagesCCNAv3 All Question PDFNikhilAKothariNo ratings yet

- 1 2 - SELECT FROM Customers SELECT FROM Products CustomersDocument3 pages1 2 - SELECT FROM Customers SELECT FROM Products CustomersNikhilAKothariNo ratings yet

- PDFDocument7 pagesPDFNikhilAKothariNo ratings yet

- CCNAv3 All Question PDFDocument16 pagesCCNAv3 All Question PDFNikhilAKothariNo ratings yet

- HASLE Datasheet OverviewDocument2 pagesHASLE Datasheet OverviewkINGNo ratings yet

- Main OutlineDocument3 pagesMain OutlineFahim AshabNo ratings yet

- ThermocouplesDocument21 pagesThermocouplesdhineshpNo ratings yet

- Mimo BoostDocument13 pagesMimo BoostdeborahjestinNo ratings yet

- DLD Lab No. 3Document4 pagesDLD Lab No. 3rizwan900No ratings yet

- Guru Tegh Bahadur Institute by ManpreetDocument67 pagesGuru Tegh Bahadur Institute by ManpreetmanpreetsinghpannuNo ratings yet

- Wave Function Summation of Bloch ElectronDocument14 pagesWave Function Summation of Bloch Electronalokesh1982No ratings yet

- ISSCC 2021 Advance ProgramDocument79 pagesISSCC 2021 Advance ProgramZhe SuNo ratings yet

- cv86 MeDocument18 pagescv86 Mecuongnv_19No ratings yet

- Magnetic Properties and Superconductivity: Code No. 07A1BS03 UNIT-3 Engineering PhysicsDocument11 pagesMagnetic Properties and Superconductivity: Code No. 07A1BS03 UNIT-3 Engineering PhysicsNizam Institute of Engineering and Technology LibraryNo ratings yet

- LogixPro CISE 313 Automation Devices and Electronics Lab ManualDocument36 pagesLogixPro CISE 313 Automation Devices and Electronics Lab ManualHelder NascimentoNo ratings yet

- Ics 61800 4Document9 pagesIcs 61800 4Bharat Kumar0% (2)

- Bruker Axs Saxs Webinar XRDDocument119 pagesBruker Axs Saxs Webinar XRDhafizalNo ratings yet

- Repo TitDocument10 pagesRepo TitAaditya BaidNo ratings yet

- Knowles MLC Catalogue 2016Document102 pagesKnowles MLC Catalogue 2016SalvadorNo ratings yet

- StacoAVR2 PDFDocument20 pagesStacoAVR2 PDFmaungNo ratings yet

- CH22 LectDocument60 pagesCH22 LectdaNo ratings yet

- Java RingDocument12 pagesJava RingMegha OmshreeNo ratings yet

- Absensi Peserta Seminar (Jawaban)Document24 pagesAbsensi Peserta Seminar (Jawaban)Sopika AsmuniNo ratings yet

- DMC tz57 PDFDocument51 pagesDMC tz57 PDFRavi Chandran100% (1)

- EC8353 Electron Devices and Circuits: Department of Electronics and Instrumentation EngineeringDocument15 pagesEC8353 Electron Devices and Circuits: Department of Electronics and Instrumentation EngineeringDr G Hari KrishnanNo ratings yet

- Characterizing PV Array Output Using Few Measured ParametersDocument5 pagesCharacterizing PV Array Output Using Few Measured ParametersAbdelkaderGourbiNo ratings yet

- Isolator Amplifier 07-7311-97MT BA22Document2 pagesIsolator Amplifier 07-7311-97MT BA22piterNo ratings yet

- Ug1075 Zynq Ultrascale PKG Pinout PDFDocument234 pagesUg1075 Zynq Ultrascale PKG Pinout PDFanhxcoNo ratings yet

- Transistor Catalog 2005Document24 pagesTransistor Catalog 2005Angelo PalamingNo ratings yet

- Mitsubishi 7-Unit 400mA Darlington Transistor ArrayDocument4 pagesMitsubishi 7-Unit 400mA Darlington Transistor ArrayRomi KabelNo ratings yet

- That 1246Document8 pagesThat 1246João PauloNo ratings yet

- MOS and CMOS Process OverviewDocument36 pagesMOS and CMOS Process OverviewashishNo ratings yet