Professional Documents

Culture Documents

Air Acond Ps21246 Ondulador

Uploaded by

J CorreoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Air Acond Ps21246 Ondulador

Uploaded by

J CorreoCopyright:

Available Formats

MITSUBISHI

MITSUBISHI

SEMICONDUCTOR

SEMICONDUCTOR

<Intelligent

<Intelligent

Power

Power

Module>

Module>

PS21246-E

PS21246-E

TRANSFER-MOLD

TRANSFER-MOLD

TYPE

TYPE

INSULATED

INSULATED

TYPE

TYPE

PS21246-E

INTEGRATED POWER FUNCTIONS

4th generation (planar) IGBT inverter bridge for 3 phase

DC-to-AC power conversion.

INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS

For upper-leg IGBTS : Drive circuit, High voltage isolated high-speed level shifting, Control circuit under-voltage (UV) protection.

Note : Bootstrap supply scheme can be applied.

For lower-leg IGBTS : Drive circuit, Control circuit under-voltage protection (UV), Short circuit protection (SC).

Fault signaling : Corresponding to a SC fault (Low-side IGBT) or a UV fault (Low-side supply).

Input interface : 5V line CMOS/TTL compatible, Schmitt Trigger receiver circuit.

APPLICATION

AC100V~200V three-phase inverter drive for small power motor control.

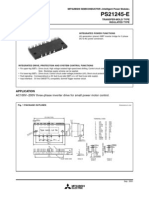

Fig. 1 PACKAGE OUTLINES

Dimensions in mm

272.8(=75.6)

TERMINAL CODE

12 13

14 15 16 17 18 19 20 21

.2

24

25

26

A

100.3 100.3 100.3

200.3

3.80.2

14

15

16

17

18

19

20

21

22

23

24

25

26

VN1

VNC

CIN

CFO

FO

UN

VN

WN

P

U

V

W

N

0.50.2

(71)

HEAT SINK SIDE

Detail A

1.90.05

10.2

3.25MAX

Detail B

(t=0.7)

1.75MAX

0.80.2

0.60.5

80.5

Irrgulor solder remains

0.5MAX

790.5

Irrgulor solder remains

0.5MAX

670.3

0.60.5

23

UP

VP1

VUFB

VUFS

VP

VP1

VVFB

VVFS

WP

VP1

VPC

VWFB

VWFS

45

22

11.50.5

Type name , Lot No.

0

4.5

2-

280.5

9 10 11

21.40.5

7 8

310.5

5 6

1

2

3

4

5

6

7

8

9

10

11

12

13

13.40.5

3 4

161 or

12.81

1 2

3~5

2.80.3

Detail C

(t=0.7)

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21246-E

TRANSFER-MOLD TYPE

INSULATED TYPE

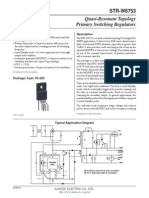

Fig. 2 INTERNAL FUNCTIONS BLOCK DIAGRAM (TYPICAL APPLICATION EXAMPLE)

CBW

CBW+

CBU+

CBV+

CBV

CBU

High-side input (PWM)

(5V line) (Note 1,2)

C3 : Tight tolerance, temp-compensated electrolytic type

(Note : The capacitance value depends on the PWM control

scheme used in the applied system).

C4 : 0.22~2F R-category ceramic capacitor for noise filtering.

Bootstrap circuit

C4

C3

Input signal Input signal Input signal

coditioning coditioning coditioning

For detailed description

of the boot-strap circuit

construction, please

contact Mitsubishi

Electric

Level shifter Level shifter Level shifter

Protection

circuit (UV)

Protection

circuit (UV)

(Note 6)

Protection

circuit (UV)

DIP-IPM

Drive circuit Drive circuit Drive circuit

Inrush current

limiter circuit

AC line input

H-side IGBTS

(Note 4)

Fig. 3

U

V

W

M

AC line output

N1

VNC

Z : ZNR (Surge absorber)

C : AC filter (Ceramic capacitor 2.2~6.5nF)

(Note : Additionally, an appropriate line-to line

surge absorber circuit may become necessary

depending on the application environment).

N

L-side IGBTS

CIN

Drive circuit

Protection

circuit

Fo logic

Input signal conditioning

Control supply

Under-Voltage

protection

FO CFO

Low-side input (PWM)

(5V line)

(Note 1, 2) Fault output (5V line)

(Note 3, 5)

Note1:

2:

3:

4:

5:

6:

VNC

VD

(15V line)

To prevent the input signals oscillation, an RC coupling at each input is recommended. (see also Fig. 6)

By virtue of integrating an application specific type HVIC inside the module, direct coupling to CPU terminals without any opto-coupler or transformer

isolation is possible. (see also Fig. 6)

This output is open collector type. The signal line should be pulled up to the positive side of the 5V power supply with approximately 5.1k resistance.

(see also Fig. 6)

The wiring between the power DC link capacitor and the P/N1 terminals should be as short as possible to protect the DIP-IPM against catastrophic high

surge voltages. For extra precaution, a small film type snubber capacitor (0.1~0.22F, high voltage type) is recommended to be mounted close to

these P and N1 DC power input pins.

Fo output pulse width should be decided by putting external capacitor between CFO and VNC terminals. (Example : CFO=22nF tFO=1.8ms (Typ.))

High voltage (600V or more) and fast recovery type (less than 100ns) diodes should be used in the bootstrap circuit.

Fig. 3 EXTERNAL PART OF THE DIP-IPM PROTECTION CIRCUIT

DIP-IPM

Short Circuit Protective Function (SC) :

SC protection is achieved by sensing the L-side DC-Bus current (through the external

shunt resistor) after allowing a suitable filtering time (defined by the RC circuit).

When the sensed shunt voltage exceeds the SC trip-level, all the L-side IGBTs are turned

OFF and a fault signal (Fo) is output. Since the SC fault may be repetitive, it is

recommended to stop the system when the Fo signal is received and check the fault.

Drive circuit

IC (A)

H-side IGBTS

SC Protection

Trip Level

U

V

W

L-side IGBTS

External protection circuit

N1

Shunt Resistor

(Note 1)

VNC

C R

Drive circuit

CIN

B

C

Collector current

waveform

Protection circuit

(Note 2)

Note1: In the recommended external protection circuit, please select the RC time constant in the range 1.5~2.0s.

2: To prevent erroneous protection operation, the wiring of A, B, C should be as short as possible.

0

2

tw (s)

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21246-E

TRANSFER-MOLD TYPE

INSULATED TYPE

MAXIMUM RATINGS (Tj = 25C, unless otherwise noted)

INVERTER PART

Symbol

VCC

VCC(surge)

VCES

IC

ICP

PC

Tj

Parameter

Condition

Applied between P-N

Supply voltage

Supply voltage (surge)

Collector-emitter voltage

Each IGBT collector current

Each IGBT collector current (peak)

Collector dissipation

Junction temperature

Ratings

Applied between P-N

TC = 25C

TC = 25C, instantaneous value (pulse)

TC = 25C, per 1 chip

(Note 1)

450

500

600

25

50

59.5

20~+150

Unit

V

V

V

A

A

W

C

Note 1 : The maximum junction temperature rating of the power chips integrated within the DIP-IPM is 150C (@ TC 100C) however, to ensure safe operation of the DIP-IPM, the average junction temperature should be limited to Tj(ave) 125C (@ TC 100C).

CONTROL (PROTECTION) PART

Symbol

VD

Parameter

Control supply voltage

Condition

Applied between VP1-VPC, VN1-VNC

VDB

Control supply voltage

VCIN

Input voltage

VFO

Fault output supply voltage

Fault output current

Current sensing input voltage

Applied between VUFB-VUFS, VVFB-VVFS ,

VWFB-VWFS

Applied between UP, VP, WP-VPC, UN, VN,

W N-VNC

Applied between F O-VNC

Sink current at F O terminal

Applied between CIN-V NC

IFO

VSC

Ratings

20

Unit

V

20

0.5~+5.5

0.5~VD+0.5

15

0.5~VD+0.5

V

mA

V

Ratings

Unit

400

20~+100

40~+125

C

C

1500

Vrms

TOTAL SYSTEM

Symbol

Parameter

VCC(PROT) Self protection supply voltage limit

(short circuit protection capability)

Module case operation temperature

TC

Tstg

Storage temperature

Viso

Isolation voltage

Condition

VD = 13.5~16.5V, Inverter part

Tj = 125C, non-repetitive, less than 2 s

(Note 2)

60Hz, Sinusoidal, AC 1 minute, connection

pins to heat-sink plate

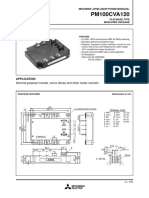

Note 2 : T C MEASUREMENT POINT

Control Terminals

DIP-IPM

Heat sink boundary

Heat sink

Tc

Tc

Power Terminals

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21246-E

TRANSFER-MOLD TYPE

INSULATED TYPE

THERMAL RESISTANCE

Symbol

Parameter

Rth(j-c)Q

Rth(j-c)F

Junction to case thermal

resistance

Rth(c-f)

Contact thermal resistance

Limits

Condition

Inverter IGBT part (per 1/6 module)

Inverter FWD part (per 1/6 module)

Case to fin, (per 1 module)

thermal grease applied

Unit

Min.

Typ.

Max.

2.1

3.0

C/W

C/W

0.067

C/W

Limits

Typ.

Max.

1.55

1.65

2.50

0.80

0.10

0.30

1.50

0.80

2.15

2.25

3.40

1.30

0.70

2.60

1.70

1

10

ELECTRICAL CHARACTERISTICS (Tj = 25C, unless otherwise noted)

INVERTER PART

Symbol

Condition

Parameter

IC = 25A, Tj = 25C

VD = VDB = 15V

VCIN = 0V

IC = 25A, Tj = 125C

Tj = 25C, IC = 25A, VCIN = 5V

VCE(sat)

Collector-emitter saturation

voltage

VEC

ton

trr

tc(on)

toff

tc(off)

FWD forward voltage

Switching times

IC = 25A, Tj = 125C, V CIN = 5V 0V

Inductive load (upper-lower arm)

ICES

Collector-emitter cut-off

current

VCE = VCES

Min.

0.10

VCC = 300V, VD = VDB = 15V

Tj = 25C

Tj = 125C

Unit

V

V

s

s

s

s

s

mA

CONTROL (PROTECTION) PART

Symbol

Parameter

VD

VDB

Control supply voltage

Control supply voltage

ID

Circuit current

VFOH

VFOL

VFOsat

Fault output voltage

tdead

Arm shoot-through blocking time

VSC(ref)

UVDBt

UVDBr

UVDt

UVDr

tFO

Vth(on)

Vth(off)

Short circuit trip level

Supply circuit under-voltage

protection

Fault output pulse width

ON threshold voltage

OFF threshold voltage

Limits

Condition

Applied between VP1-VPC, VN1 -VNC

Applied between VUFB-VUFS, VVFB-VVFS , VWFB-VWFS

VD = VDB = 15V Total of VP1-VPC, VN1 -VNC

VUFB-VUFS, VVFB-V VFS, VWFB-VWFS

VCIN= 5V

VSC = 0V, FO = 10k 5V pull-up

VSC = 1V, FO = 10k 5V pull-up

VSC = 1V, IFO = 15mA

Relates to corresponding input signal for blocking arm

shoot-through.

20C TC 100C

Tj = 25C, VD = 15V

Trip level

Reset level

T j 125C

Trip level

Reset level

CFO = 22nF

(Note 3)

(Note 4)

Applied between : UP, VP, WP-VPC, UN, VN, WN-VNC

Min.

13.5

13.5

Unit

4.9

Typ.

15.0

15.0

Max.

16.5

16.5

8.50

1.00

0.8

0.8

1.2

1.2

1.8

V

V

V

2.5

0.45

10.0

10.5

10.3

0.5

10.8

1.0

0.8

2.5

1.8

1.4

3.0

0.55

12.0

12.5

12.5

13.0

2.0

4.0

V

V

V

V

V

ms

V

V

mA

V

V

Note 3 : Short circuit protection is functioning only at the low-arms. Please select the value of the external shunt resistor such that the SC triplevel is less than 42.5 A.

4 : Fault signal is output when the low-arms short circuit or control supply under-voltage protective functions operate. The fault output pulsewidth tFO depends on the capacitance value of CFO according to the following approximate equation : CFO = 12.2 10-6 tFO [F].

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21246-E

TRANSFER-MOLD TYPE

INSULATED TYPE

MECHANICAL CHARACTERISTICS AND RATINGS

Condition

Parameter

Mounting torque

Terminal pulling strength

Bending strength

Weight

Heat-sink flatness

Mounting screw : M4

Weight 19.6N

Weight 9.8N. 90deg bend

EIAJ-ED-4701

EIAJ-ED-4701

(Note 5)

Min.

0.98

10

2

50

Limits

Typ.

1.18

54

Max.

1.47

100

Min.

Limits

Typ.

Max.

Unit

Nm

s

times

g

m

Note 5: Measurement point of heat-sink flatness

(Note 5)

DIP-IPM

Measurement point

3mm

Place to contact

a heat sink

Heat sink

Heat sink

RECOMMENDED OPERATION CONDITIONS

Symbol

Parameter

VCC

VD

VDB

VD, VDB

tdead

fPWM

VCIN(ON)

VCIN(OFF)

Supply voltage

Control supply voltage

Control supply voltage

Control supply variation

Arm shoot-through blocking time

PWM input frequency

Input ON threshold voltage

Input OFF threshold voltage

Condition

Applied between P-N

Applied between VP1-VPC, VN1 -VNC

Applied between VUFB-VUFS, V VFB-VVFS , VWFB-VWFS

Relates to corresponding input signal for blocking arm shoot-through

TC 100C, Tj 125C

Applied between UP, VP, WP-VPC

Applied between UN, VN, WN-VNC

0

13.5

13.5

1

2.5

300

15.0

15.0

5

0~0.65

4.0~5.5

400

16.5

16.5

1

Unit

V

V

V

V/s

s

kHz

V

V

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21246-E

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 4 THE DIP-IPM INTERNAL CIRCUIT

DIP-IPM

VUFB

VUFS

VP1

UP

HVIC 1

VB

VCC

IGBT1

Di1

HO

IN

VS

COM

VVFB

VVFS

VP1

VP

HVIC 2

VB

VCC

IGBT2

Di2

HO

IN

VS

COM

VWFB

VWFS

HVIC 3

VP1

VCC

WP

IN

VPC

COM

VB

IGBT3

Di3

HO

VS

W

IGBT4

LVIC

Di4

UOUT

VN1

VCC

IGBT5

Di5

VOUT

UN

UN

VN

VN

WN

WN

Fo

Fo

IGBT6

Di6

WOUT

VNO

CIN

VNC

GND

CFO

CFO

CIN

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21246-E

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 5 TIMING CHARTS OF THE DIP-IPM PROTECTIVE FUNCTIONS

[A] Short-Circuit Protection (N-side only)

(For the external shunt resistor and CR connection.)

a1. Normal operation : IGBT ON and carrying current.

a2. Short circuit current detection (SC trigger).

a3. Hard IGBT gate interrupt.

a4. IGBT turns OFF.

a5. FO timer operation starts : The pulse width of the F O signal is set by the external capacitor CFO.

a6. Input H : IGBT OFF state.

a7. Input L : IGBT ON state.

a8. IGBT OFF state.

N-side control input

a6

Protection circuit state

a7

SET

Internal IGBT gate

RESET

a3

a2

SC

a4

a1

Output current Ic(A)

a8

SC reference voltage

Sense voltage of the

shunt resistor

CR circuit time constant DELAY

Error output Fo

a5

[B] Under-Voltage Protection (N-side, UVD)

a1. Normal operation : IGBT ON and carrying current.

a2. Under voltage trip (UVDt).

a3. IGBT OFF in spite of control input condition.

a4. FO timer operation starts.

a5. Under voltage reset (UVDr).

a6. Normal operation : IGBT ON and carrying current.

Control input

Protection circuit state

Control supply voltage VD

RESET

SET

UVDr

UVDt

a5

a2

a1

a3

a6

Output current Ic(A)

Error output Fo

a4

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21246-E

TRANSFER-MOLD TYPE

INSULATED TYPE

[C] Under-Voltage Protection (P-side, UVDB)

a1. Control supply voltage rises : After the voltage level reachs UVDBr, the circuits start to operate when the next input is applied.

a2. Normal operation : IGBT ON and carrying current.

a3. Under voltage trip (UVDBt).

a4. IGBT OFF in spite of control input condition, but there is no FO signal output.

a5. Under-voltage reset (UVDBr).

a6. Normal operation : IGBT ON and carrying current.

Control input

Protection circuit state

RESET

SET

RESET

UVDBr

Control supply voltage VDB

a1

UVDBt

a2

a5

a3

a4

a6

Output current Ic(A)

High-level (no fault output)

Error output Fo

Fig. 6 RECOMMENDED CPU I/O INTERFACE CIRCUIT

5V line

DIP-IPM

5.1k

4.7k

UP,VP,WP,UN,VN,WN

CPU

Fo

1nF

1nF

VPC, VNC(Logic)

Note : RC coupling at each input (parts shown dotted) may change depending on the

PWM control scheme used in the application and on the wiring impedances of

the applications printed circuit board.

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21246-E

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 7 TYPICAL DIP-IPM APPLICATION CIRCUIT EXAMPLE

C1: Tight tolerance temp - compensated electrolytic type; C2,C3: 0.22~2 F R-category ceramic capacitor for noise filtering

5V line

C2

VUFB

C1

VUFS

DIP-IPM

P

VP1

C3

UP

VCC

VB

IN

HO

COM

VS

VCC

VB

IN

HO

COM

VS

VCC

VB

IN

HO

C2

VVFB

C1

VVFS

VP1

C3

VP

C2

VWFB

C1

C

P

U

VWFS

VP1

C3

WP

VPC

U

N

I

T

COM

VS

UOUT

C3

VN1

VCC

5V line

VOUT

UN

VN

WN

Fo

UN

VN

WOUT

If this wiring is too long, short

circuit might be caused.

WN

Fo

VNO

CIN

VNC

GND

CFO

C

CFO

CIN

C4(CFO )

15V line

A

The long wiring of GND might generate

noise on input signals and cause IGBT to

be malfunctioned.

R1

C5

If this wiring is too long, the SC level

fluctuation might be larger and cause SC

malfunction.

Shunt

resistor

N1

Note 1 : To prevent the input signals oscillation, an RC coupling at each input is recommended, and the wiring of each input should be as short

as possible. (Less than 2cm)

2 : By virtue of integrating an application specific type HVIC inside the module, direct coupling to CPU terminals without any opto-coupler

or transformer isolation is possible.

3 : FO output is open collector type. This signal line should be pulled up to the positive side of the 5V power supply with approximately

5.1k resistance.

4 : FO output pulse width should be decided by connecting an external capacitor between CFO and VNC terminals (C FO). (Example : CFO

= 22 nF tFO = 1.8 ms (typ.))

5 : Each input signal line should be pulled up to the 5V power supply with approximately 4.7k resistance (other RC coupling circuits at

each input may be needed depending on the PWM control scheme used and on the wiring impedances of the systems printed circuit

board). Approximately a 0.22~2F by-pass capacitor should be used across each power supply connection terminals.

6 : To prevent errors of the protection function, the wiring of A, B, C should be as short as possible.

7 : In the recommended protection circuit, please select the R1C5 time constant in the range 1.5~2s.

8 : Each capacitor should be put as nearby the pins of the DIP-IPM as possible.

9 : To prevent surge destruction, the wiring between the smoothing capacitor and the P&N1 pins should be as short as possible. Approximately a 0.1~0.22F snubber capacitor between the P&N1 pins is recommended.

Sep. 2001

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

You might also like

- PS21245 eDocument9 pagesPS21245 eTol SirtNo ratings yet

- MITSUBISHI PS21245-E 4th Gen IGBT Inverter ModuleDocument9 pagesMITSUBISHI PS21245-E 4th Gen IGBT Inverter ModulepukymottoNo ratings yet

- Mitsubishi Semiconductor Mitsubishi SemiconductorDocument8 pagesMitsubishi Semiconductor Mitsubishi Semiconductoramired2No ratings yet

- Ps 21 A 79Document10 pagesPs 21 A 79Omar LeonNo ratings yet

- Ps 11034Document5 pagesPs 11034Tanvon MalikNo ratings yet

- Optimize Motor Drive Inverter Module Application NoteDocument10 pagesOptimize Motor Drive Inverter Module Application Notevishwa_001No ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- Mitsubishi SemiconductorDocument8 pagesMitsubishi Semiconductoredgardo2004No ratings yet

- IRAMX16UP60ADocument18 pagesIRAMX16UP60Atheylor1990No ratings yet

- Iramx 16 Up 60 ADocument17 pagesIramx 16 Up 60 AJandfor Tansfg ErrottNo ratings yet

- Irams 06 Up 60 ADocument18 pagesIrams 06 Up 60 AAndré Roberto EvangelistaNo ratings yet

- Double Channel High Side Solid State Relay: VND600SPDocument17 pagesDouble Channel High Side Solid State Relay: VND600SPDan EsentherNo ratings yet

- L6565Document18 pagesL6565Sergio Daniel BarretoNo ratings yet

- PM 150 CSD 120Document7 pagesPM 150 CSD 120elecompinnNo ratings yet

- FSBB20CH60: Smart Power ModuleDocument16 pagesFSBB20CH60: Smart Power ModuleDhaka AsasaNo ratings yet

- Uc3842b 3843BDocument10 pagesUc3842b 3843Bbob75No ratings yet

- 10884Document13 pages10884karthikeidNo ratings yet

- 5101 Motor DriverDocument11 pages5101 Motor DriverMoise CristinaNo ratings yet

- Infineon BTS740S2Document15 pagesInfineon BTS740S2dasho1No ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- Driver Bobina de Encendido VB326SPDocument9 pagesDriver Bobina de Encendido VB326SPteroplasNo ratings yet

- BTS5215LDocument14 pagesBTS5215LVanny Is AresNo ratings yet

- Thb7128 InstructionsDocument9 pagesThb7128 InstructionsanhxcoNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- PM20CSJ060Document6 pagesPM20CSJ060Dany Carrasco Ysus TecladosNo ratings yet

- 04 Spec Sheet PWM Controller ChipDocument16 pages04 Spec Sheet PWM Controller Chipxuanhiendk2No ratings yet

- ACS102-5Tx: Ac Line Switch Asd™ AC Switch FamilyDocument8 pagesACS102-5Tx: Ac Line Switch Asd™ AC Switch FamilyeduardopercicaroliNo ratings yet

- MB39A132Document60 pagesMB39A132Krum BumbarovNo ratings yet

- TCK101G/102G 1A Load Switch IC with Slew Rate Control DriverDocument12 pagesTCK101G/102G 1A Load Switch IC with Slew Rate Control DriverLuis OliveiraNo ratings yet

- D Escriptio: S FeatureDocument8 pagesD Escriptio: S Featurevsc2012No ratings yet

- LM358 Low Power Dual Op AmpDocument8 pagesLM358 Low Power Dual Op AmpAmrutha AmmuNo ratings yet

- Aic 1084-33PMDocument6 pagesAic 1084-33PMluismilenio3111No ratings yet

- STR W6753 DatasheetDocument8 pagesSTR W6753 DatasheetjgerabmNo ratings yet

- NCP 3063Document20 pagesNCP 3063Roozbeh BahmanyarNo ratings yet

- Three-Terminal Positive Fixed Voltage Regulators: Semiconductor Technical DataDocument16 pagesThree-Terminal Positive Fixed Voltage Regulators: Semiconductor Technical DataBetancur AlejandroNo ratings yet

- VN800S VN800PT: High Side DriverDocument21 pagesVN800S VN800PT: High Side DriverDan EsentherNo ratings yet

- IC 3842 para FonteDocument8 pagesIC 3842 para FonteTomNedscNo ratings yet

- Dual Output Voltage Regulator With Power Saving: BA44W12SATDocument10 pagesDual Output Voltage Regulator With Power Saving: BA44W12SATBeatris Medellin MendozaNo ratings yet

- STCC05-B: Home Appliance Control CircuitDocument13 pagesSTCC05-B: Home Appliance Control Circuitsvhanu4010No ratings yet

- Pm100cva120 - e IGBT PDFDocument6 pagesPm100cva120 - e IGBT PDFDoDuyBacNo ratings yet

- Fully Integrated H-Bridge Motor Driver: VNH3SP30Document26 pagesFully Integrated H-Bridge Motor Driver: VNH3SP30Dan EsentherNo ratings yet

- Datasheet STR 6757Document11 pagesDatasheet STR 6757Walter CarreroNo ratings yet

- LTC 1625Document24 pagesLTC 1625Sakura KunNo ratings yet

- Synchronous Rectification DC/DC Converter IC For Charging Li-Ion BatteryDocument56 pagesSynchronous Rectification DC/DC Converter IC For Charging Li-Ion BatterydigenioNo ratings yet

- VND810MSP: Double Channel High Side DriverDocument18 pagesVND810MSP: Double Channel High Side DriverDan EsentherNo ratings yet

- VND830MSP: Double Channel High Side DriverDocument18 pagesVND830MSP: Double Channel High Side DriverDan EsentherNo ratings yet

- Double Channel High Side Solid State RelayDocument18 pagesDouble Channel High Side Solid State RelayDan EsentherNo ratings yet

- Ir 2153Document9 pagesIr 2153Carlos Marinho SilvaNo ratings yet

- MC34063AMDocument16 pagesMC34063AMSajjad4434No ratings yet

- Ir 2151Document6 pagesIr 2151RintheGreatNo ratings yet

- ZXSC410 420Document12 pagesZXSC410 420Catalin TirtanNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : High Voltage Ignition Coil Driver Power I.CDocument9 pagesObsolete Product(s) - Obsolete Product(s) : High Voltage Ignition Coil Driver Power I.CFer NandoNo ratings yet

- M54649LDocument5 pagesM54649LAllan AlexNo ratings yet

- Two-Phase Stepper Motor Driver: DescriptionDocument19 pagesTwo-Phase Stepper Motor Driver: DescriptionDan EsentherNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- A New Family of Sensors For Pulse OximetryDocument22 pagesA New Family of Sensors For Pulse OximetryEmilio CánepaNo ratings yet

- MSHA Approved 24-Hour Battery Backup UPS for NS40 NetworkDocument4 pagesMSHA Approved 24-Hour Battery Backup UPS for NS40 NetworkedgarNo ratings yet

- Aprisa - Alarm PDFDocument333 pagesAprisa - Alarm PDFNhân Tâm100% (1)

- Asr 44 - Asr Self Hold Thermal CutoutDocument4 pagesAsr 44 - Asr Self Hold Thermal CutoutHotel WijayaNo ratings yet

- Test Report: Samil Power Co - LTDDocument5 pagesTest Report: Samil Power Co - LTDCALİNo ratings yet

- Protection & Coordination by - Dr. Hamid JaffariDocument83 pagesProtection & Coordination by - Dr. Hamid JaffariMuhammad HusnainNo ratings yet

- Contamination Control Through Room PressurisationDocument5 pagesContamination Control Through Room PressurisationAnkit JainNo ratings yet

- Nec Pasolink NeoDocument57 pagesNec Pasolink NeohheinsNo ratings yet

- CNT-81 & CNT-81R: Timer/Counter/CalibratorsDocument4 pagesCNT-81 & CNT-81R: Timer/Counter/CalibratorsMichael DixonNo ratings yet

- Quote #1603 - Electronics Starter KitDocument1 pageQuote #1603 - Electronics Starter KitHala ItaniNo ratings yet

- gpg68 NoiseDocument67 pagesgpg68 NoiseMF100% (1)

- SAPCDocument2 pagesSAPCShanArisNo ratings yet

- Wenling Yuhai Electromechanical 180sy-M35015 Sg-50a DatasheetDocument62 pagesWenling Yuhai Electromechanical 180sy-M35015 Sg-50a DatasheetJoimir PerezNo ratings yet

- Teac GF 480 Service ManualDocument20 pagesTeac GF 480 Service ManualLloyd WarrenNo ratings yet

- EN - Woodward-Manual B028035.DDocument100 pagesEN - Woodward-Manual B028035.DChhoan Nhun100% (1)

- DIY Mains Slave Switcher Circuit GuideDocument2 pagesDIY Mains Slave Switcher Circuit GuidedewasuryantoNo ratings yet

- Ultra Controller INDDocument2 pagesUltra Controller INDRuben TorresNo ratings yet

- AD-99 Encatalog 1705 SankoshaDocument100 pagesAD-99 Encatalog 1705 SankoshaLiliek Prasetyo WidiyonoNo ratings yet

- Optical Communication LabDocument2 pagesOptical Communication LabShoebahmed100% (1)

- BEI605 Embedded SystemDocument79 pagesBEI605 Embedded SystemKani Mozhi100% (2)

- RKP18 Motor Project Board: Component List and Instructions ForDocument4 pagesRKP18 Motor Project Board: Component List and Instructions ForVDT2420 EmbeddedNo ratings yet

- Lec 13 Radiographic Grids IIDocument27 pagesLec 13 Radiographic Grids IIwaelNo ratings yet

- AMI Backplane Controller MG9070 Data SheetDocument2 pagesAMI Backplane Controller MG9070 Data SheetAnderson Andrade de LimaNo ratings yet

- SZ-16V DatasheetDocument3 pagesSZ-16V DatasheetCezar Adrian SimereaNo ratings yet

- Encoders Go BarrierDocument2 pagesEncoders Go BarrierkaicyemNo ratings yet

- 3G Radio Network Planning & Optimization V2Document11 pages3G Radio Network Planning & Optimization V2Pongpang ObNo ratings yet

- Lab 08: Construct Half and Full Subtractor CircuitsDocument7 pagesLab 08: Construct Half and Full Subtractor CircuitsAbdul BasitNo ratings yet

- Service Note EN Maintenance KitsDocument1 pageService Note EN Maintenance KitsJatupol PongsirisartNo ratings yet

- HP 260 G3 Desktop Mini Business PC PDFDocument29 pagesHP 260 G3 Desktop Mini Business PC PDFRuben LopezNo ratings yet

- Fluid Power ControlDocument25 pagesFluid Power Controlshantanuchoudhary007No ratings yet