Professional Documents

Culture Documents

COSC121 L0c LC3 Instruction Set Summary

Uploaded by

Teresa RobertsCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

COSC121 L0c LC3 Instruction Set Summary

Uploaded by

Teresa RobertsCopyright:

Available Formats

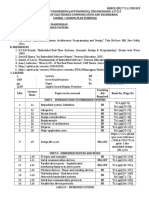

== LC3 Instruction Set Summary

==

== For details, see, PP_Append_C-LC3_Instruction_Formats_and_Semantics

Instruction Format Assembly Language Operation

and Example Code for Example Code Semantics

-------------------- ----------------- --------------------

Op DR SR1 i.. SR2 ADD R5 R6 R7 ADD R6 plus R7,

0001 101 110 000 111 write result into R5. (see Note 0)

Op DR SR1 i imm5 ADD R1 R6 x7 ADD R6 plus 0000000000000111,

0001 001 110 1 00111 write result into R1. (Note 1)

Op DR SR1 i.. SR2 AND R5 R7 R6 R5 gets Bitwise AND of R7 with

0101 101 111 000 110 R6.

Op DR SR1 i imm5 AND R1 R3 x6 R1 gets Bitwise AND of R3 with

0101 001 011 1 00110 0000000000000110. (Note 1)

Op DR SR1 ... ... NOT R1 R2 R1 gets Bitwise NOT of R2.

1001 001 010 000 000

Op DR imm9 LD R1 x89 R1 gets contents of memory at

0010 001 0_1000_1001 address = PC + x89. (Note 2)

Op DR imm9 ST R1 x89 R1 written to memory at

0011 001 0_1000_1001 address = PC + x89.

Op DR SR1 imm6 LDR R1 R6 x13 R1 gets contents of memory at

0110 001 110 01_0011 address = R6 + x13. (Note 2)

Op DR SR1 imm6 STR R1 R6 x13 R1 written to memory at

0111 001 110 01_0011 address = R6 + x13.

Op DR imm9 LDI R1 x89 R1 gets contents of memory via

pointer at

1010 001 0_1000_1001 address = PC + x89. (Note 3)

Op DR imm9 STI R1 x89 R1 written to memory via pointer at

1011 001 0_1000_1001 address = PC + x89.

Op DR imm9 LEA R1 x89 R1 gets PC + x89.

1110 001 1_1000_1001

Op nzp imm9 BRp x89 PC get PC + x89, if

0000 001 0_1000_1001 PSR.NZP = IR.nzp = 001. (Note 4)

Op ... SR1 ...... JMP R1 PC gets content of R7.

1100 000 111 000000 JMP R1

OP i.. SR1 ...... JSRR R6 PC gets R6, and simultaneously

0100 000 110 000000 R7 gets PC. (Note 5)

Op i imm11 JSR x3F PC gets PC + x3F, and simultaneously

0100 1 0_0011_1111 R7 gets PC.

Op ... ... ... ... RTI PC gets memory at R6; R6++;

1000 000 000 000 000 RTI PSR get memory at R6; R6++. (Note 6)

Op .... vector TRAP x3F PC gets memory at address x003F, and

1111 0000 0011_1111 TRAP x08 simultaneously, R7 gets PC.

(Note 0) The "." in the instruction format means the bit is ignored when decoding and executing the instruction.

(Note 1) An "immediate" value, imm5, contained in IR[4:0] is converted from a 5-bit 2s-Complement

representation to 16-bit 2s-Complement by duplicating bit IR[4] to all 11 most-significant bits. This is called "sign

extension". The result is fed to the ALU.

(Note 2) The 9-bit immediate value, imm9, in IR[8:0] is sign extended to 16-bits.

(Note 3) A "pointer" is a memory location whose content is treated as an address. In this case, the memory location

at address = PC + x89 contains a 16-bit address that is first fetched and then sent to the memory to do a second

fetch. This is called "dereferencing a pointer."

(Note 4) The Processor Status Register (PSR) records the status of executed instructions, among other information.

Part of the PSR is the branch condition codes (NZP). PSR.NZP is a 3-bit field that records whether the value

written into a register was negative (PSR.NZP == 100) or was zero (PSR.NZP == 010) or was positive (PSR.NZP

== 001). A branch instruction specifies when a branch will be taken by its IR.nzp bits, IR[11:9]. If a non-zero

IR.nzp bit matches the non-zero PSR.NZP bit, the branch it taken. E.g., suppose the last register value written was

zero. Then, PSR.NZP == 010. Suppose a branch instruction's bits are IR[11:9] = IR.nzp = 011. Then the branch

will be taken because PSR.Z == 1 == IR.z. Note that the branch also would be taken if PSR.NZP = 001. This

instruction is thus a branch on non-negative, written in LC3 assembly language as "BRzp".

(Note 5) A jump to a subroutine requires that the address immediately following the jump instruction be recorded

so that the subroutine code can jump back when it completes its job. In the LC3, the "return address" is recorded in

R7. The jump address (the address written into the PC that causes the jump) is calculated in the same way memory

addresses are. In this case, PC <=== R6. That is, the PC flipflop gets written with the content of register R6.

Because the PC is a flipflop, it can also be read simultaneously. So, the valu

(Note 6) The register R6 has a special usage: it is the "stack" pointer. It holds a memory address. Information can

be written to an area of memory called the "stack". By convention, whenever we read or write the stack area, we

use R6 as the address. We adjust R6 so that we can use the next stack location. When we write, we do R6--, when

we read, we do R6++. This is called "pushing" and "popping" to/from the stack. Interrupts are a special kind of

jump that is not controlled by an instruction. The PC is loaded from a special source (either memory or for some

architectures from a special register.) This is triggered by a signal coming from external hardware. As a

consequence, the PC is clobbered and we cannot return to the "interrupted" instruction. To deal with this, the

architecture must record the address that was clobbered. So, part of what happens is the PC is pushed to the stack.

When the interrupt code that was jumped to is finished, it jumps back to the interrupted instruction by popping the

stack into the PC.

Our Notation Conventions:

16'h123F a 16-bit constant expressed in hex:

16' for bits (or, 8' for eight bits, etc.)

h for hex, d for decimal, or b for binary notation.

SEXTk k-to-16-bit sign-extension

LC3 Assembler's Notation Conventions:

x10 constant expressed in hex

#16 decimal (can have a minus sign, e.g., #-16)

.ORIG x0200 1st line of .asm file: memory location to load program

.END last line of .asm file: end-of-program

.FILL x1234 create a 16-bit word containing 16'h1234

;-comment

.BLKW 5 create five 16-bit words containing 16'h0000

.STRINGZ "string" create seven 16-bit words, one 8-bit ASCII code

per word, last word contains ASCII NUL.

You might also like

- Homework 8 solution subroutine numeric keyboard inputDocument2 pagesHomework 8 solution subroutine numeric keyboard inputMustafa ShamsNo ratings yet

- DLX InfoDocument28 pagesDLX InforazaNo ratings yet

- The ARC ProcessorDocument10 pagesThe ARC ProcessorDaniel LoveraNo ratings yet

- LC3 Instruction DetailsDocument26 pagesLC3 Instruction DetailsJeff Pratt100% (4)

- Introduction To MicroprocessorsDocument27 pagesIntroduction To Microprocessorsnoway snirfyNo ratings yet

- The LC-3 ISA OverviewDocument26 pagesThe LC-3 ISA OverviewThanh ThanhNo ratings yet

- Solution: Computer OrganizationDocument6 pagesSolution: Computer OrganizationDavid Gutierrez AriasNo ratings yet

- Fetch Execute CycleDocument17 pagesFetch Execute CycleMuhammad Ehtisham HassanNo ratings yet

- The LC-3b ISA: 1.1 OverviewDocument23 pagesThe LC-3b ISA: 1.1 OverviewVan ChanNo ratings yet

- Basic Computer Organization - Part 05Document5 pagesBasic Computer Organization - Part 05Kamala Rani RoyNo ratings yet

- LC-3 ISA overviewDocument26 pagesLC-3 ISA overviewSarthak SrinivasNo ratings yet

- UntitledDocument14 pagesUntitledStevan RadulovicNo ratings yet

- Introduction To Computing Systems - Homework 4Document6 pagesIntroduction To Computing Systems - Homework 4Minh ĐoànNo ratings yet

- TRAP Routines and SubroutinesDocument32 pagesTRAP Routines and SubroutinesNirmal GuptaNo ratings yet

- 03 Bagian 1 Arsitektur AVRDocument22 pages03 Bagian 1 Arsitektur AVRTito Adi NugrohoNo ratings yet

- Interrupts: - Figure Shows A Time Line That Indicates A Typist TypingDocument33 pagesInterrupts: - Figure Shows A Time Line That Indicates A Typist TypingVuggam VenkateshNo ratings yet

- ARM Prog Model 6 Subroutines PDFDocument34 pagesARM Prog Model 6 Subroutines PDFnaveenNo ratings yet

- Design Contest 2010 MentorDocument27 pagesDesign Contest 2010 MentorUjjwal KantNo ratings yet

- 001Document6 pages001StefanMiticNo ratings yet

- Exam2 ReviewDocument54 pagesExam2 ReviewSurbhie Kalia ChebaNo ratings yet

- L 2Document48 pagesL 2pinku0911No ratings yet

- Lecture 08Document17 pagesLecture 08Swetha Rani MunirajuNo ratings yet

- HP-15C Quick Reference GuideDocument16 pagesHP-15C Quick Reference Guidejeff_56No ratings yet

- Coa Important QuestionsDocument49 pagesCoa Important QuestionsLet's LearnNo ratings yet

- Coa QaDocument25 pagesCoa QaHimanshu VermaNo ratings yet

- Unit3 Coa NotesDocument32 pagesUnit3 Coa Notesvivek kumarNo ratings yet

- F2010 552 Project DescriptionDocument6 pagesF2010 552 Project DescriptionJamil_fawadNo ratings yet

- Set7 Memory InterfacingDocument32 pagesSet7 Memory Interfacing666667No ratings yet

- Lecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofDocument7 pagesLecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofWilliamNo ratings yet

- ARM Architecture: Logical InstructionDocument4 pagesARM Architecture: Logical InstructionNinda KhoirunnisaNo ratings yet

- Basic Computer Organization and Design: - Computer Registers - Instruction CycleDocument21 pagesBasic Computer Organization and Design: - Computer Registers - Instruction CycleShashank PandeyNo ratings yet

- HP 15C Quick ReferenceDocument11 pagesHP 15C Quick ReferenceLuiz Carlos RodriguesNo ratings yet

- Chapter - 2: Basic Computer Organization and DesignDocument74 pagesChapter - 2: Basic Computer Organization and Designketulmp0% (1)

- RigExpert Data ExchangeDocument5 pagesRigExpert Data ExchangeLeopoldoNo ratings yet

- 03 PIC16F84A Assembly ProgrammingDocument29 pages03 PIC16F84A Assembly ProgrammingMarcos Marcelon Alcantara Abueva IIINo ratings yet

- Application Note, Nordic nRF24L01 With Bascom-AvrDocument8 pagesApplication Note, Nordic nRF24L01 With Bascom-AvrLalinda Rathnabharatie100% (1)

- Asynchronous FIFODocument21 pagesAsynchronous FIFOMarium Mazhar50% (2)

- CPE 221 Final Exam Solution Fall 2018Document6 pagesCPE 221 Final Exam Solution Fall 2018Kyra LathonNo ratings yet

- 5-stage Pipeline CPU hardware analysis and ARM architecture overviewDocument33 pages5-stage Pipeline CPU hardware analysis and ARM architecture overviewrosestrikesNo ratings yet

- Programmed I/O - Interrupts - Interrupt Driven I/O - Trap Service RoutinesDocument30 pagesProgrammed I/O - Interrupts - Interrupt Driven I/O - Trap Service Routinesdavelnx2291No ratings yet

- Von Neuman Model Part-2Document42 pagesVon Neuman Model Part-2G.PranithaNo ratings yet

- PRELAB1Document36 pagesPRELAB1NHUẬN NGUYỄN HỮUNo ratings yet

- Anomie's SPC700Document11 pagesAnomie's SPC700picolo789No ratings yet

- Single Clock RISC Datapath for 16-bit R-type InstructionsDocument7 pagesSingle Clock RISC Datapath for 16-bit R-type InstructionsKanwal GillNo ratings yet

- PCSRCDocument2 pagesPCSRCLord LightningNo ratings yet

- ARM Instruction SetDocument29 pagesARM Instruction SetNeeshank MahajanNo ratings yet

- LectEPE1301 3 RegistersRAMMemory AddressMappingAndDecoding1Document25 pagesLectEPE1301 3 RegistersRAMMemory AddressMappingAndDecoding1Bryan KekNo ratings yet

- Assembly Programs Examples - Assembling Process: Topics To DiscussDocument10 pagesAssembly Programs Examples - Assembling Process: Topics To Discussvipulugale100% (1)

- LC3 1 1Document59 pagesLC3 1 1Kevin HarvardNo ratings yet

- Assembly Language ProgrammingDocument11 pagesAssembly Language ProgrammingUsman Ullah AsifNo ratings yet

- Autosar Complete ReferenceDocument55 pagesAutosar Complete ReferenceSureshNo ratings yet

- Basic Computer OrganizationDocument19 pagesBasic Computer OrganizationBarikly RobbyNo ratings yet

- EEE 204 - Lecture4Document27 pagesEEE 204 - Lecture4furkanarslan1285No ratings yet

- Introduction To TI MSP430Document9 pagesIntroduction To TI MSP430hickimse1No ratings yet

- 6803 Instruction Set (68HC11 Subset)Document93 pages6803 Instruction Set (68HC11 Subset)Saukani HalimNo ratings yet

- Data Movement Instructions: Topics To DiscussDocument14 pagesData Movement Instructions: Topics To DiscussvipulugaleNo ratings yet

- Wipro Confidential: Stack Tracing and Variable Arguments in C - WorkshopDocument15 pagesWipro Confidential: Stack Tracing and Variable Arguments in C - WorkshopPrasanna KakumanuNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Mono MythDocument12 pagesMono MythTeresa RobertsNo ratings yet

- Vanboven RGP 2005 PDFDocument11 pagesVanboven RGP 2005 PDFTeresa RobertsNo ratings yet

- Bits and Bytes and BitchesDocument2 pagesBits and Bytes and BitchesTeresa RobertsNo ratings yet

- Mustafa AliDocument12 pagesMustafa AliTeresa RobertsNo ratings yet

- Brotton, The Renaissance Bazaar - 1Document16 pagesBrotton, The Renaissance Bazaar - 1Teresa Roberts100% (1)

- Frederik BorgesiusDocument15 pagesFrederik BorgesiusCalperniaUSANo ratings yet

- chp:10.1007/978 3 642 14527 8 - 1Document18 pageschp:10.1007/978 3 642 14527 8 - 1Teresa RobertsNo ratings yet

- F6 Solutions - Algorithm, DeMorgan's Law, Vector AdditionDocument3 pagesF6 Solutions - Algorithm, DeMorgan's Law, Vector AdditionTeresa RobertsNo ratings yet

- Recently in Rap, or Hip-HopDocument1 pageRecently in Rap, or Hip-HopTeresa RobertsNo ratings yet

- 889 899Document1 page889 899Teresa RobertsNo ratings yet

- Advanced Programming Final ReviewDocument3 pagesAdvanced Programming Final ReviewTeresa RobertsNo ratings yet

- Lewis paradoxesofTimeTravelDocument8 pagesLewis paradoxesofTimeTravelTeresa RobertsNo ratings yet

- Dante Quiz 1 Study GuideDocument5 pagesDante Quiz 1 Study GuideTeresa RobertsNo ratings yet

- Author Bretscher, Ottopublisher Title: Linear Algebra With Application Isbn: 9780321796974 Publisher: Pearson Custom Publishing Subject Edition: 5Document1 pageAuthor Bretscher, Ottopublisher Title: Linear Algebra With Application Isbn: 9780321796974 Publisher: Pearson Custom Publishing Subject Edition: 5Teresa RobertsNo ratings yet

- LC3 UnixDocument24 pagesLC3 UnixLeandro MussoNo ratings yet

- Loyola Icam College of Engineering and Technology Department of Ece Cs 2252 Microprocessors and Microcontrollers Question Bank With AnswersDocument38 pagesLoyola Icam College of Engineering and Technology Department of Ece Cs 2252 Microprocessors and Microcontrollers Question Bank With AnswersKarthik KarthiksNo ratings yet

- COAL Lec 7Document15 pagesCOAL Lec 7ABRAR RASUL QADRINo ratings yet

- CMS Class VII Additional BookletDocument15 pagesCMS Class VII Additional BookletCrafting VillaNo ratings yet

- ARMBook PDFDocument176 pagesARMBook PDFSandhiya JagarnathanNo ratings yet

- 03.embedded System - Question BankDocument31 pages03.embedded System - Question BankK.MATHAN HICET STAFF EEENo ratings yet

- Compiler DesignDocument47 pagesCompiler DesignLearn UpNo ratings yet

- SE5 M.Sc. INFORMATION TECHNOLOGYDocument93 pagesSE5 M.Sc. INFORMATION TECHNOLOGYwwea1234No ratings yet

- The Type of Memory Assignment Used in Intel Processors IsDocument26 pagesThe Type of Memory Assignment Used in Intel Processors IsSuchit KumarNo ratings yet

- CPU Organisation: Instructions and Instruction SequencingDocument30 pagesCPU Organisation: Instructions and Instruction SequencingSamit NagNo ratings yet

- QB - 2018 - EEM303 Soln (Updated 2.10.18) PDFDocument40 pagesQB - 2018 - EEM303 Soln (Updated 2.10.18) PDFMiNo ratings yet

- Instruction SetDocument6 pagesInstruction SetmraleroNo ratings yet

- Week 1 - Assembly Language and Computer Programming + Number SystemDocument36 pagesWeek 1 - Assembly Language and Computer Programming + Number SystemHira WaheedNo ratings yet

- A Mobile Greenhouse Environment Monitoring System Based On The Internet of ThingsDocument60 pagesA Mobile Greenhouse Environment Monitoring System Based On The Internet of Thingsaravind kumarNo ratings yet

- Microprocessor Experiment 1Document4 pagesMicroprocessor Experiment 1yyeominNo ratings yet

- 28x C CompilarDocument166 pages28x C CompilarKeith FengNo ratings yet

- C 2348967Document636 pagesC 2348967aramis01No ratings yet

- MathDocument67 pagesMathPeniel JimenezNo ratings yet

- System Software Unit 1 Exercise SolutionDocument8 pagesSystem Software Unit 1 Exercise Solutionvtu paper100% (12)

- CS2304 - INTRO TO SYSTEM SOFTWAREDocument100 pagesCS2304 - INTRO TO SYSTEM SOFTWAREmukesh9133% (6)

- Example of SIC Assembler Language ProgramDocument66 pagesExample of SIC Assembler Language ProgramPreeti Joshi Sachdeva100% (1)

- Assembly Language (Lab Manual)Document13 pagesAssembly Language (Lab Manual)Nurfaizah Hasanah Sahimi100% (2)

- Mpasm DirectiveDocument22 pagesMpasm DirectiveDublu_VNo ratings yet

- Syllabus: Microcontrollers 4 Sem Ece/TceDocument60 pagesSyllabus: Microcontrollers 4 Sem Ece/TceRaviNo ratings yet

- CSLDocument1,108 pagesCSLUsman KhanNo ratings yet

- Introduction To Computer OrganizationDocument66 pagesIntroduction To Computer OrganizationSajeev G PNo ratings yet

- APU CSLLT - 9 - Mathematical CommandsDocument47 pagesAPU CSLLT - 9 - Mathematical CommandsAbdullah AfzalNo ratings yet

- SP 11Document50 pagesSP 11Anonymous V0TkkvWNo ratings yet

- Microprocessors AND Microcontrollers Lab ELE306L: Submitted By: Submitted ToDocument50 pagesMicroprocessors AND Microcontrollers Lab ELE306L: Submitted By: Submitted ToVidhu ChaudharyNo ratings yet

- Chapter-5: Assembly Language Programming Using 8086 (16 Marks)Document55 pagesChapter-5: Assembly Language Programming Using 8086 (16 Marks)PRABHAKAR MORENo ratings yet