Professional Documents

Culture Documents

Datasheet 6

Uploaded by

Ivanor Ipanaque CordovaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Datasheet 6

Uploaded by

Ivanor Ipanaque CordovaCopyright:

Available Formats

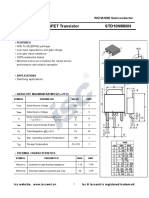

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN015-100B, PSMN015-100P

FEATURES SYMBOL QUICK REFERENCE DATA

Trench technology d

Very low on-state resistance VDSS = 100 V

Fast switching

Low thermal resistance ID = 75 A

g

RDS(ON) 15 m

s

GENERAL DESCRIPTION

SiliconMAX products use the latest Philips Trench technology to achieve the lowest possible on-state resistance in

each package at each voltage rating.

Applications:-

d.c. to d.c. converters

switched mode power supplies

The PSMN015-100P is supplied in the SOT78 (TO220AB) conventional leaded package.

The PSMN015-100B is supplied in the SOT404 surface mounting package.

PINNING SOT78 (TO220AB) SOT404 (D2PAK)

PIN DESCRIPTION tab

tab

1 gate

2 drain1

3 source

2

tab drain 1 3

1 23

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

VDSS Drain-source voltage Tj = 25 C to 175C - 100 V

VDGR Drain-gate voltage Tj = 25 C to 175C; RGS = 20 k - 100 V

VGS Gate-source voltage - 20 V

ID Continuous drain current Tmb = 25 C - 752 A

Tmb = 100 C - 53 A

IDM Pulsed drain current Tmb = 25 C - 240 A

PD Total power dissipation Tmb = 25 C - 230 W

Tj, Tstg Operating junction and - 55 175 C

storage temperature

1 It is not possible to make connection to pin:2 of the SOT404 package

2 Maximum continuous current limited by package

August 1999 1 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN015-100B, PSMN015-100P

AVALANCHE ENERGY LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

EAS Non-repetitive avalanche Unclamped inductive load, IAS = 74 A; - 481 mJ

energy tp = 100 s; Tj prior to avalanche = 25C;

VDD 50 V; RGS = 50 ; VGS = 10 V; refer

to fig:15

IAS Non-repetitive avalanche - 75 A

current

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS TYP. MAX. UNIT

Rth j-mb Thermal resistance junction - 0.65 K/W

to mounting base

Rth j-a Thermal resistance junction SOT78 package, in free air 60 - K/W

to ambient SOT404 package, pcb mounted, minimum 50 - K/W

footprint

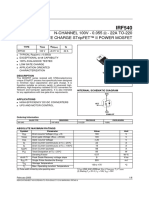

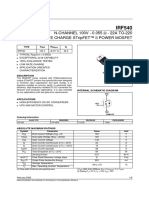

ELECTRICAL CHARACTERISTICS

Tj= 25C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V(BR)DSS Drain-source breakdown VGS = 0 V; ID = 0.25 mA; 100 - - V

voltage Tj = -55C 89 - - V

VGS(TO) Gate threshold voltage VDS = VGS; ID = 1 mA 2.0 3.0 4.0 V

Tj = 175C 1.0 - - V

Tj = -55C - - 6 V

RDS(ON) Drain-source on-state VGS = 10 V; ID = 25 A - 12 15 m

resistance Tj = 175C - - 41 m

IGSS Gate source leakage current VGS = 10 V; VDS = 0 V - 2 100 nA

IDSS Zero gate voltage drain VDS = 100 V; VGS = 0 V; - 0.05 10 A

current Tj = 175C - - 500 A

Qg(tot) Total gate charge ID = 75 A; VDD = 80 V; VGS = 10 V - 109 - nC

Qgs Gate-source charge - 20 - nC

Qgd Gate-drain (Miller) charge - 50 - nC

td on Turn-on delay time VDD = 50 V; RD = 1.8 ; - 30 - ns

tr Turn-on rise time VGS = 10 V; RG = 5.6 - 80 - ns

td off Turn-off delay time Resistive load - 150 - ns

tf Turn-off fall time - 95 - ns

Ld Internal drain inductance Measured from tab to centre of die - 3.5 - nH

Ld Internal drain inductance Measured from drain lead to centre of die - 4.5 - nH

Ls Internal source inductance Measured from source lead to source - 7.5 - nH

bond pad

Ciss Input capacitance VGS = 0 V; VDS = 25 V; f = 1 MHz - 4720 - pF

Coss Output capacitance - 650 - pF

Crss Feedback capacitance - 380 - pF

August 1999 2 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN015-100B, PSMN015-100P

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

IS Continuous source current - - 75 A

(body diode)

ISM Pulsed source current (body - - 240 A

diode)

VSD Diode forward voltage IF = 25 A; VGS = 0 V - 0.8 1.2 V

trr Reverse recovery time IF = 20 A; -dIF/dt = 100 A/s; - 90 - ns

Qrr Reverse recovery charge VGS = 0 V; VR = 30 V - 0.3 - C

August 1999 3 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN015-100B, PSMN015-100P

Normalised Power Derating, PD (%) Transient thermal impedance, Zth j-mb (K/W)

1

100

90 D = 0.5

80 0.2

70 0.1

0.1

60

0.05

50

0.02 P D = tp/T

D tp

40 0.01

30

20 single pulse

T

10

0.001

0

1E-06 1E-05 1E-04 1E-03 1E-02 1E-01 1E+00

0 25 50 75 100 125 150 175

Mounting Base temperature, Tmb (C) Pulse width, tp (s)

Fig.1. Normalised power dissipation. Fig.4. Transient thermal impedance.

PD% = 100PD/PD 25 C = f(Tmb) Zth j-mb = f(t); parameter D = tp/T

Drain Current, ID (A)

Normalised Current Derating, ID (%) 50

100 VGS = 15V 10 V 5V Tj = 25 C

45

90

40

80

35

70 4.6 V

30

60

50 25

4.4 V

40 20

30 15 4.2 V

20 10 4V

10

5 3.8 V

0 3.6 V

0

0 25 50 75 100 125 150 175

0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2

Mounting Base temperature, Tmb (C) Drain-Source Voltage, VDS (V)

Fig.2. Normalised continuous drain current. Fig.5. Typical output characteristics, Tj = 25 C.

ID% = 100ID/ID 25 C = f(Tmb) ID = f(VDS); parameter VGS

Peak Pulsed Drain Current, IDM (A) Drain-Source On Resistance, RDS(on) (Ohms)

1000

0.05

4V 4.2 V 4.4 V 4.6 V Tj = 25 C

RDS(on) = VDS/ ID 0.045

0.04

tp = 10 us

100 0.035

0.03

100 us

0.025

D.C. 1 ms 0.02 5V

10

0.015

10 ms 10 V

0.01

100 ms

0.005 VGS = 15V

1 0

1 10 100 1000 0 5 10 15 20 25 30 35 40 45 50

Drain-Source Voltage, VDS (V) Drain Current, ID (A)

Fig.3. Safe operating area. Tmb = 25 C Fig.6. Typical on-state resistance, Tj = 25 C.

ID & IDM = f(VDS); IDM single pulse; parameter tp RDS(ON) = f(VGS)

August 1999 4 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN015-100B, PSMN015-100P

Drain current, ID (A) Threshold Voltage, VGS(TO) (V)

4.5

80

VDS > ID X RDS(ON) 4

70 maximum

3.5

60

3 typical

50

2.5

40 minimum

2

30 175 C 1.5

20

Tj = 25 C 1

10 0.5

0 0

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 5.5 6 -60 -40 -20 0 20 40 60 80 100 120 140 160 180

Gate-source voltage, VGS (V) Junction Temperature, Tj (C)

Fig.7. Typical transfer characteristics. Fig.10. Gate threshold voltage.

ID = f(VGS); parameter Tj VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

Transconductance, gfs (S) Drain current, ID (A)

80 1.0E-01

VDS > ID X RDS(ON)

70

Tj = 25 C 1.0E-02

60

175 C

50 minimum

1.0E-03

40

typical

30 1.0E-04

maximum

20

1.0E-05

10

0 1.0E-06

0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 75 80 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5

Drain current, ID (A) Gate-source voltage, VGS (V)

Fig.8. Typical transconductance, Tj = 25 C. Fig.11. Sub-threshold drain current.

gfs = f(ID) ID = f(VGS); Tj = 25 C

Normalised On-state Resistance

2.9 Capacitances, Ciss, Coss, Crss (pF)

2.7 10000

2.5

Ciss

2.3

2.1

1.9

1.7

1000

1.5

Coss

1.3

1.1 Crss

0.9

0.7

0.5 100

-60 -40 -20 0 20 40 60 80 100 120 140 160 180 0.1 1 10 100

Junction temperature, Tj (C) Drain-Source Voltage, VDS (V)

Fig.9. Normalised drain-source on-state resistance. Fig.12. Typical capacitances, Ciss, Coss, Crss.

RDS(ON)/RDS(ON)25 C = f(Tj) C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

August 1999 5 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN015-100B, PSMN015-100P

Maximum Avalanche Current, IAS (A)

Gate-source voltage, VGS (V) 100

15

14 ID = 75A

13

Tj = 25 C

12 25 C

11

10

9 VDD = 20 V

Tj prior to avalanche = 150 C

8 10

7 VDD = 80 V

6

5

4

3

2

1

0 1

0 10 20 30 40 50 60 70 80 90 100 110 120 0.001 0.01 0.1 1 10

Gate charge, QG (nC) Avalanche time, tAV (ms)

Fig.13. Typical turn-on gate-charge characteristics Fig.15. Maximum permissible non-repetitive

VGS = f(QG) avalanche current (IAS) versus avalanche time (tAV);

unclamped inductive load

Source-Drain Diode Current, IF (A)

100

VGS = 0 V

90

80

70

60 175 C

50 Tj = 25 C

40

30

20

10

0

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2 1.3 1.4 1.5

Source-Drain Voltage, VSDS (V)

Fig.14. Typical reverse diode current.

IF = f(VSDS); conditions: VGS = 0 V; parameter Tj

August 1999 6 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN015-100B, PSMN015-100P

MECHANICAL DATA

Plastic single-ended package; heatsink mounted; 1 mounting hole; 3-lead TO-220 SOT78

E A

P A1

q

D1

L2(1) L1

Q

b1

L

1 2 3

b c

e e

0 5 10 mm

scale

DIMENSIONS (mm are the original dimensions)

(1)

UNIT A A1 b b1 c D D1 E e L L1 L2 P q Q

max.

4.5 1.39 0.9 1.3 0.7 15.8 6.4 10.3 15.0 3.30 3.8 3.0 2.6

mm 2.54 3.0

4.1 1.27 0.7 1.0 0.4 15.2 5.9 9.7 13.5 2.79 3.6 2.7 2.2

Note

1. Terminals in this zone are not tinned.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

SOT78 TO-220 97-06-11

Fig.16. SOT78 (TO220AB); pin 2 connected to mounting base (Net mass:2g)

Notes

1. This product is supplied in anti-static packaging. The gate-source input must be protected against static

discharge during transport or handling.

2. Refer to mounting instructions for SOT78 (TO220AB) package.

3. Epoxy meets UL94 V0 at 1/8".

August 1999 7 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN015-100B, PSMN015-100P

MECHANICAL DATA

Plastic single-ended surface mounted package (Philips version of D2-PAK); 3 leads

(one lead cropped) SOT404

E A1

D1 mounting

base

HD

Lp

1 3

b c

e e Q

0 2.5 5 mm

scale

DIMENSIONS (mm are the original dimensions)

D

UNIT A A1 b c D1 E e Lp HD Q

max.

mm 4.50 1.40 0.85 0.64 11 1.60 10.30 2.54 2.90 15.40 2.60

4.10 1.27 0.60 0.46 1.20 9.70 2.10 14.80 2.20

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

98-12-14

SOT404

99-06-25

Fig.17. SOT404 surface mounting package. Centre pin connected to mounting base.

Notes

1. This product is supplied in anti-static packaging. The gate-source input must be protected against static

discharge during transport or handling.

2. Refer to SMD Footprint Design and Soldering Guidelines, Data Handbook SC18.

3. Epoxy meets UL94 V0 at 1/8".

August 1999 8 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PSMN015-100B, PSMN015-100P

MOUNTING INSTRUCTIONS

Dimensions in mm 11.5

9.0

17.5

2.0

3.8

5.08

Fig.18. SOT404 : soldering pattern for surface mounting.

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 1999

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

August 1999 9 Rev 1.100

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- N2 Industrial ElectronicsDocument46 pagesN2 Industrial ElectronicsbokangtsogangNo ratings yet

- 34b64 Iphone 2g SchematicsDocument11 pages34b64 Iphone 2g SchematicsIvanor Ipanaque CordovaNo ratings yet

- Sylvania 1976 Large Lamp Ordering GuideDocument52 pagesSylvania 1976 Large Lamp Ordering GuideAlan MastersNo ratings yet

- Facebook OSINT PDFDocument42 pagesFacebook OSINT PDFCater AidNo ratings yet

- Electricity and MagnetismDocument12 pagesElectricity and MagnetismTrisha Bonita Restauro100% (1)

- M. Standard Stock Materials For 33kV SystemDocument9 pagesM. Standard Stock Materials For 33kV SystemSandesh PattanashettiNo ratings yet

- IRF540Document9 pagesIRF540paul mathewNo ratings yet

- N-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataLenin Cadillo GutierrezNo ratings yet

- N-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataRobert sibueaNo ratings yet

- N-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DatareparacionesdmaNo ratings yet

- N-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataingucvNo ratings yet

- N-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataNixon MaldonadoNo ratings yet

- IRFZ24NDocument8 pagesIRFZ24NarcatusNo ratings yet

- BUK 9575 - Interruptor de PotênciaDocument8 pagesBUK 9575 - Interruptor de PotênciaTiago LeonhardtNo ratings yet

- Buk9635-100a 1Document7 pagesBuk9635-100a 1Raul OsoNo ratings yet

- PDF Philips 26610Document11 pagesPDF Philips 26610ecsa tallerNo ratings yet

- Trenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference DataDocument8 pagesTrenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference DataNicki LarsonNo ratings yet

- N-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDaniel Orlando Carballo FernándezNo ratings yet

- Powermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataRio CandrapurwitaNo ratings yet

- Buk7508 Buk7608-55a 1Document9 pagesBuk7508 Buk7608-55a 1Habacuc LopezNo ratings yet

- P75N02LDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP75N02LDG: N-Channel Enhancement Mode MOSFETAriel Rodrigo MuñozNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionzakreaNo ratings yet

- Buk7514 55a - Buk7614 55aDocument9 pagesBuk7514 55a - Buk7614 55aHabacuc LopezNo ratings yet

- CRST065N08N Datasheet - Moto ElétricaDocument10 pagesCRST065N08N Datasheet - Moto ElétricaDenis OliveiraNo ratings yet

- skst065n08n skss063n08nDocument10 pagesskst065n08n skss063n08nStefan IuscoNo ratings yet

- Buk555 60a PDFDocument7 pagesBuk555 60a PDFGiraldoCarpioRamosNo ratings yet

- CRST045N10N, CRSS042N10N: 100% Avalanche Tested 100% Avalanche Tested 100% Avalanche TestedDocument10 pagesCRST045N10N, CRSS042N10N: 100% Avalanche Tested 100% Avalanche Tested 100% Avalanche TestedLuis FigueroaNo ratings yet

- Powermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataCarlos Morales AvilaNo ratings yet

- HGP105N15SLDocument6 pagesHGP105N15SLمحمد الراويNo ratings yet

- Isc N-Channel MOSFET Transistor STD10NM60N: INCHANGE SemiconductorDocument2 pagesIsc N-Channel MOSFET Transistor STD10NM60N: INCHANGE SemiconductorY. Leonel MolinaNo ratings yet

- Trenchmos Transistor Buk9535-55A Logic Level Fet Buk9635-55ADocument9 pagesTrenchmos Transistor Buk9535-55A Logic Level Fet Buk9635-55AMotor CsillagNo ratings yet

- APM2518NU: Pin Description FeaturesDocument10 pagesAPM2518NU: Pin Description FeaturesJeyson BolivarNo ratings yet

- Buk455 200a PDFDocument8 pagesBuk455 200a PDFCarl Conter OnderNo ratings yet

- SKD503T, SKSS042N10N: 100% Avalanche Tested 100% Avalanche Tested 100% Avalanche TestedDocument10 pagesSKD503T, SKSS042N10N: 100% Avalanche Tested 100% Avalanche Tested 100% Avalanche TestedYamila CruzNo ratings yet

- STP60NS04Z: N-Channel Clamped 10M - 60A TO-220 Fully Protected Mesh Overlay™ MosfetDocument8 pagesSTP60NS04Z: N-Channel Clamped 10M - 60A TO-220 Fully Protected Mesh Overlay™ MosfetВлад НNo ratings yet

- STD38NH02L: N-CHANNEL 24V - 0.011 - 38A Dpak/Ipak Stripfet™ Iii Power MosfetDocument13 pagesSTD38NH02L: N-CHANNEL 24V - 0.011 - 38A Dpak/Ipak Stripfet™ Iii Power MosfetJose luisNo ratings yet

- Hyg042n10ns1p Hyg042n10ns1bDocument10 pagesHyg042n10ns1p Hyg042n10ns1brennybenitezNo ratings yet

- Powermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedDocument9 pagesPowermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedEmmanuel ZambranoNo ratings yet

- CRJQ190N65GCFDocument9 pagesCRJQ190N65GCFVadim PopovichNo ratings yet

- STP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetDocument8 pagesSTP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetCarlos A AvilaNo ratings yet

- STP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetDocument11 pagesSTP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetRyn YahuFNo ratings yet

- Important Notice: Kind RegardsDocument8 pagesImportant Notice: Kind Regardscarlosjamal95No ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- Irf 540Document8 pagesIrf 540Tom TweedleNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFRubenNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- Isc N-Channel MOSFET Transistor IRFS3607: FeaturesDocument2 pagesIsc N-Channel MOSFET Transistor IRFS3607: FeaturesBarkat HussainNo ratings yet

- Low Input Capacitance N-Channel MOSFET Transistor with 100% Avalanche Testing (IRFS3607Document2 pagesLow Input Capacitance N-Channel MOSFET Transistor with 100% Avalanche Testing (IRFS3607Barkat HussainNo ratings yet

- Hgp045ne4sl - V1.0 DS-101416Document6 pagesHgp045ne4sl - V1.0 DS-101416selandrinoNo ratings yet

- Mosfet Data SheetDocument9 pagesMosfet Data SheetMark RecioNo ratings yet

- 25N06Document6 pages25N06Luismar LimaNo ratings yet

- AP86T02GHJDocument6 pagesAP86T02GHJEsmelin AlvarezNo ratings yet

- High-Speed Switching N-Channel MOSFET Transistor IRFP260NPBFDocument2 pagesHigh-Speed Switching N-Channel MOSFET Transistor IRFP260NPBFhudi elcoNo ratings yet

- High-speed N-Channel MOSFET with TO-220 packaging (HRF3205Document2 pagesHigh-speed N-Channel MOSFET with TO-220 packaging (HRF3205AnjitNo ratings yet

- Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 pagesNiko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorJulio Rafael GamboaNo ratings yet

- Transistor MosfetDocument2 pagesTransistor MosfetFlavin MedinaNo ratings yet

- Pc817 DatasheetDocument5 pagesPc817 DatasheetprincebahariNo ratings yet

- English Manual PDFDocument2 pagesEnglish Manual PDFIvanor Ipanaque CordovaNo ratings yet

- CR160 Series Optimus RedDocument4 pagesCR160 Series Optimus RedIvanor Ipanaque CordovaNo ratings yet

- Ipad3 DiagramDocument48 pagesIpad3 Diagrampsapwell100% (1)

- Socket 478 Pentium 4-M: P/N: KK0G550011010Document0 pagesSocket 478 Pentium 4-M: P/N: KK0G550011010taraservNo ratings yet

- LB#820-2327 Macbook - 13 - A1278 - M97Document78 pagesLB#820-2327 Macbook - 13 - A1278 - M97Dan PerezNo ratings yet

- English Manual PDFDocument2 pagesEnglish Manual PDFIvanor Ipanaque CordovaNo ratings yet

- Ipad3 DiagramDocument48 pagesIpad3 Diagrampsapwell100% (1)

- Toshiba Satellite l300d (Inventec Ps10a - 6050a2174501)Document54 pagesToshiba Satellite l300d (Inventec Ps10a - 6050a2174501)drop9721100% (1)

- Toshiba - L300 - (Invatec) - SchematicsDocument63 pagesToshiba - L300 - (Invatec) - SchematicsbcatlockNo ratings yet

- Compal Confidential: IAKAA LA-3401P Schematics DocumentDocument38 pagesCompal Confidential: IAKAA LA-3401P Schematics DocumentjotantonioNo ratings yet

- HP Compaq Presario c700 - Compal La-4031 Jbl81 - Rev 1.0 - ZouaveDocument42 pagesHP Compaq Presario c700 - Compal La-4031 Jbl81 - Rev 1.0 - ZouaveYonny MunozNo ratings yet

- Eula Microsoft Visual StudioDocument3 pagesEula Microsoft Visual StudioqwwerttyyNo ratings yet

- Curso de TV Plasma Part - 2Document40 pagesCurso de TV Plasma Part - 2s0nytechNo ratings yet

- NPN13007Document2 pagesNPN13007rmdejanNo ratings yet

- English ManualDocument2 pagesEnglish ManualIvanor Ipanaque CordovaNo ratings yet

- Eula Microsoft Visual StudioDocument3 pagesEula Microsoft Visual StudioqwwerttyyNo ratings yet

- Eula Microsoft Visual StudioDocument3 pagesEula Microsoft Visual StudioqwwerttyyNo ratings yet

- Eula Microsoft Visual StudioDocument3 pagesEula Microsoft Visual StudioqwwerttyyNo ratings yet

- Backpack 1 U6Document2 pagesBackpack 1 U6Ivanor Ipanaque CordovaNo ratings yet

- Lista Almacen Proway 2022 - Imp. JulDocument5 pagesLista Almacen Proway 2022 - Imp. JulFermin Tafur LliuyaNo ratings yet

- Elektroenerģētikas TehnoloģijasDocument6 pagesElektroenerģētikas TehnoloģijasMihails LarionovsNo ratings yet

- Technology Basics Axial Fans PDFDocument17 pagesTechnology Basics Axial Fans PDFSanthosh KumarNo ratings yet

- Composite Video SignalDocument17 pagesComposite Video SignalKashyap MistryNo ratings yet

- 1 FT7 Servo Motor BrochureDocument324 pages1 FT7 Servo Motor BrochureAlondra ArellanoNo ratings yet

- Internal Resistance IA PDFDocument10 pagesInternal Resistance IA PDFtuvvacNo ratings yet

- Energy-Saving Project of 5500-HP 13-kV Wound Rotor Induction Motor On A Kiln ID Fan Using A Low-Voltage Slip Power Recovery Drive-A Case StudyDocument5 pagesEnergy-Saving Project of 5500-HP 13-kV Wound Rotor Induction Motor On A Kiln ID Fan Using A Low-Voltage Slip Power Recovery Drive-A Case StudyJulioNo ratings yet

- Module 7Document17 pagesModule 7jimmyboyjr50% (2)

- Operation and Maintenance Instructions for Air Insulated Metal-Clad Switchgear Type 8BK88PLUSDocument36 pagesOperation and Maintenance Instructions for Air Insulated Metal-Clad Switchgear Type 8BK88PLUSRitesh Maheshwari100% (1)

- MLX75012Document18 pagesMLX75012Ali AbdoNo ratings yet

- Noblex: SERVICE MANUAL Colour TelevisionDocument33 pagesNoblex: SERVICE MANUAL Colour TelevisionLeonel FontanaNo ratings yet

- Electric and Hybrid Vehicles Design Fundamentals S... - (Chapter 9. Control of AC Machines)Document26 pagesElectric and Hybrid Vehicles Design Fundamentals S... - (Chapter 9. Control of AC Machines)Iria LlausiNo ratings yet

- Optical Mineralogy: Lab 14 - Fall, 2012 Biaxial Interference FiguresDocument13 pagesOptical Mineralogy: Lab 14 - Fall, 2012 Biaxial Interference Figuressagnik royNo ratings yet

- SP1905016-01-C Electrical Diagram - SpeedAC IQ E55B PDFDocument41 pagesSP1905016-01-C Electrical Diagram - SpeedAC IQ E55B PDFB Lal MughalNo ratings yet

- Network Theorems: Publishing As Pearson (Imprint) BoylestadDocument62 pagesNetwork Theorems: Publishing As Pearson (Imprint) BoylestadKavinesh AnanthanNo ratings yet

- LG 32SL8000 Chassis LD91KDocument50 pagesLG 32SL8000 Chassis LD91KBiju PrestcomNo ratings yet

- Long-Channel I-V Characteristics: Chapter 2 MOS Transistor TheoryDocument1 pageLong-Channel I-V Characteristics: Chapter 2 MOS Transistor TheoryCarlos SaavedraNo ratings yet

- Preamplifiers: Matching The Preamplifier To The Detector and The ApplicationDocument8 pagesPreamplifiers: Matching The Preamplifier To The Detector and The ApplicationsuryaNo ratings yet

- GW - HT 1500V - Datasheet-ENDocument2 pagesGW - HT 1500V - Datasheet-ENGabooNo ratings yet

- WEG Automation Drives and Controls Usadrivescontrols Brochure EnglishDocument16 pagesWEG Automation Drives and Controls Usadrivescontrols Brochure EnglishAndrés NarvaezNo ratings yet

- W5 - Thevenin - Norton Theorem-1Document16 pagesW5 - Thevenin - Norton Theorem-1Rima MohammedNo ratings yet

- DC - DC Vicore Arc1000 PDFDocument2 pagesDC - DC Vicore Arc1000 PDFsrijithbpillai7087No ratings yet

- 2012 Dep of Conductivity On Charge Density and Echem Pot in Polymer SC W Ionic LiquidsDocument10 pages2012 Dep of Conductivity On Charge Density and Echem Pot in Polymer SC W Ionic LiquidsChris SmithNo ratings yet

- Data Sheet: HEF40174B MSIDocument6 pagesData Sheet: HEF40174B MSIPedroZevallosNo ratings yet

- AN218 Vehicle Detection Using AMR SensorsDocument10 pagesAN218 Vehicle Detection Using AMR SensorsIndra Panggalo100% (1)

- Chapter 5 Part 2Document10 pagesChapter 5 Part 2george manNo ratings yet