Professional Documents

Culture Documents

8K/16K 5.0V I C Serial Eeproms: Features Package Types

Uploaded by

arunan55Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8K/16K 5.0V I C Serial Eeproms: Features Package Types

Uploaded by

arunan55Copyright:

Available Formats

24C08B/16B

8K/16K 5.0V I2C™ Serial EEPROMs

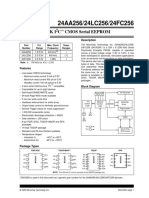

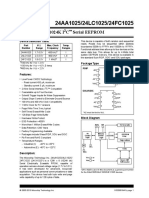

FEATURES PACKAGE TYPES

• Single supply with operation from 4.5-5.5V PDIP

• Low power CMOS technology A0 1 8 VCC

24C08B/16B

- 1 mA active current typical

A1 2 7 WP

- 10 µA standby current typical at 5.5V

• Organized as 4 or 8 blocks of 256 bytes

(4 x 256 x 8) or (8 x 256 x 8) A2 3 6 SCL

• 2-wire serial interface bus, I2C compatible

• Schmitt trigger, filtered inputs for noise suppres- VSS 4 5 SDA

sion

• Output slope control to eliminate ground bounce

• 100 kHz compatibility

• Self-timed write cycle (including auto-erase) 8-lead

• Page-write buffer for up to 16 bytes SOIC 1 8

A0 VCC

• 2 ms typical write cycle time for page-write

24C08B/16B

• Hardware write protect for entire memory A1 2 7 WP

• Can be operated as a serial ROM

• ESD protection > 4,000V 3 6

A2 SCL

• 1,000,000 ERASE/WRITE cycles guaranteed

• Data retention > 200 years 4 5

VSS SDA

• 8-pin DIP, 8-lead or 14-lead SOIC packages

• Available for extended temperature range

- Commercial (C): 0°C to +70°C 14-lead

1 14 NC

- Industrial (I): -40°C to +85°C SOIC NC

- Automotive (E): -40˚C to +125˚C A0 2 13 VCC

24C08B/16B

3 12

DESCRIPTION A1 WP

NC 4 11 NC

The Microchip Technology Inc. 24C08B/16B is an 8K or

16K bit Electrically Erasable PROM intended for use in A2 5 10 SCL

extended/automotive temperature ranges. The device 6 9

VSS SDA

is organized as four or eight blocks of 256 x 8-bit mem-

ory with a 2-wire serial interface. The 24C08B/16B also NC 7 8 NC

has a page-write capability for up to 16 bytes of data.

The 24C08B/16B is available in the standard 8-pin DIP

and both 8-lead and 14-lead surface mount SOIC pack- BLOCK DIAGRAM

ages. WP

HV GENERATOR

I/O MEMORY EEPROM

CONTROL CONTROL ARRAY

LOGIC LOGIC XDEC

PAGE LATCHES

SDA SCL

YDEC

VCC SENSE AMP

VSS R/W CONTROL

I2C is a trademark of Philips Corporation.

1999 Microchip Technology Inc. DS21081F-page 1

24C08B/16B

1.0 ELECTRICAL CHARACTERISTICS TABLE 1-1: PIN FUNCTION TABLE

1.1 Maximum Ratings* Name Function

VCC...................................................................................7.0V VSS Ground

All inputs and outputs w.r.t. VSS ................-0.6V to VCC +1.0V

Storage temperature ..................................... -65˚C to +150˚C SDA Serial Address/Data I/O

Ambient temp. with power applied................. -65˚C to +125˚C

Soldering temperature of leads (10 seconds) ............. +300˚C

SCL Serial Clock

ESD protection on all pins ..................................................≥ 4 kV WP Write Protect Input

*Notice: Stresses above those listed under “Maximum ratings”

may cause permanent damage to the device. This is a stress rat- VCC +4.5V to 5.5V Power Supply

ing only and functional operation of the device at those or any

A0, A1, A2 No Internal Connection

other conditions above those indicated in the operational listings

of this specification is not implied. Exposure to maximum rating

conditions for extended periods may affect device reliability.

TABLE 1-2: DC CHARACTERISTICS

VCC = +4.5V to +5.5V

Commercial (C): Tamb = 0°C to +70°C

Industrial (I): Tamb = -40°C to +85°C

Automotive (E): Tamb = -40˚C to +125˚C

Parameter Symbol Min Max Units Conditions

WP, SCL and SDA pins:

High level input voltage VIH .7 Vcc — V

Low Level input voltage VIL — .3 VCC V

Hysteresis of Schmitt trigger VHYS .05 Vcc — V (Note)

inputs

Low level output voltage VOL — .40 V IOL = 3.0 mA, VCC=4.5V

Input leakage current ILI -10 10 µA VIN =.1V to VCC

Output leakage current ILO -10 10 µA VOUT = .1V to VCC

Pin capacitance CIN, COUT — 10 pF VCC = 5.0V (Note 1)

(all inputs/outputs) Tamb = 25˚C, FCLK=1 MHz

Operating current ICC write — 3 mA VCC = 5.5V, SCL = 400 kHz

ICC read — 1 mA

Standby current ICCS — 100 µA VCC = 5.5V, SDA = SCL = VCC

WP = VSS

Note: This parameter is periodically sampled and not 100% tested.

FIGURE 1-1: BUS TIMING START/STOP

VHYS

SCL

THD:STA

TSU:STA TSU:STO

SDA

START STOP

DS21081F-page 2 1999 Microchip Technology Inc.

24C08B/16B

TABLE 1-3: AC CHARACTERISTICS

Parameter Symbol Min Max Units Remarks

Clock frequency FCLK — 100 kHz

Clock high time THIGH 4000 — ns

Clock low time TLOW 4700 — ns

SDA and SCL rise time TR — 1000 ns (Note1)

SDA and SCL fall time TF — 300 ns (Note 1)

START condition hold time THD:STA 4000 — ns After this period the first clock

pulse is generated

START condition setup TSU:STA 4700 — ns Only relevant for repeated

time START condition

Data input hold time THD:DAT 0 — ns

Data input setup time TSU:DAT 250 — ns

STOP condition setup time TSU:STO 4000 — ns

Output valid from clock TAA — 3500 ns (Note 2)

Bus free time TBUF 4700 — ns Time the bus must be free before

a new transmission can start

Output fall time from VIH TOF — 250 ns (Note 1), CB ≤ 100 pF

min to VIL max

Input filter spike suppres- TSP — 50 ns (Note 3)

sion (SDA and SCL pins)

Write cycle time TWR — 10 ms Byte or Page mode

Endurance — 1M — cycles 25°C, VCC = 5.0V, Block Mode

(Note 4)

Note 1: Not 100% tested. CB = total capacitance of one bus line in pF.

2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region

(minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

3: The combined TSP and VHYS specifications are due to new Schmitt trigger inputs which provide improved

noise and spike suppression. This eliminates the need for a TI specification.

4: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific appli-

cation, please consult the Total Endurance Model which can be obtained on our website.

FIGURE 1-2: BUS TIMING DATA

TF TR

THIGH

TLOW

SCL

TSU:STA

THD:DAT TSU:DAT TSU:STO

THD:STA

SDA

IN TSP

TAA TAA TBUF

THD:STA

SDA

OUT

1999 Microchip Technology Inc. DS21081F-page 3

24C08B/16B

2.0 FUNCTIONAL DESCRIPTION 3.4 Data Valid (D)

The 24C08B/16B supports a Bi-directional 2-wire bus The state of the data line represents valid data when,

and data transmission protocol. A device that sends after a START condition, the data line is stable for the

data onto the bus is defined as transmitter, and a duration of the HIGH period of the clock signal.

device receiving data as receiver. The bus has to be

The data on the line must be changed during the LOW

controlled by a master device which generates the

period of the clock signal. There is one clock pulse per

serial clock (SCL), controls the bus access, and gener-

bit of data.

ates the START and STOP conditions, while the

24C08B/16B works as slave. Both, master and slave Each data transfer is initiated with a START condition

can operate as transmitter or receiver but the master and terminated with a STOP condition. The number of

device determines which mode is activated. the data bytes transferred between the START and

STOP conditions is determined by the master device

3.0 BUS CHARACTERISTICS and is theoretically unlimited, although only the last 16

The following bus protocol has been defined: will be stored when doing a write operation. When an

overwrite does occur it will replace data in a first in first

• Data transfer may be initiated only when the bus

out fashion.

is not busy.

• During data transfer, the data line must remain 3.5 Acknowledge

stable whenever the clock line is HIGH. Changes

in the data line while the clock line is HIGH will be Each receiving device, when addressed, is obliged to

interpreted as a START or STOP condition. generate an acknowledge after the reception of each

byte. The master device must generate an extra clock

Accordingly, the following bus conditions have been

pulse which is associated with this acknowledge bit.

defined (Figure 3-1).

Note: The 24C08B/16B does not generate any

3.1 Bus not Busy (A) acknowledge bits if an internal program-

ming cycle is in progress.

Both data and clock lines remain HIGH.

The device that acknowledges, has to pull down the

3.2 Start Data Transfer (B) SDA line during the acknowledge clock pulse in such a

way that the SDA line is stable LOW during the HIGH

A HIGH to LOW transition of the SDA line while the period of the acknowledge related clock pulse. Of

clock (SCL) is HIGH determines a START condition. course, setup and hold times must be taken into

All commands must be preceded by a START condi- account. During reads, a master must signal an end of

tion. data to the slave by NOT generating an acknowledge

bit on the last byte that has been clocked out of the

3.3 Stop Data Transfer (C)

slave. In this case, the slave (24C08B/16B) will leave

A LOW to HIGH transition of the SDA line while the the data line HIGH to enable the master to generate the

clock (SCL) is HIGH determines a STOP condition. All STOP condition.

operations must be ended with a STOP condition.

FIGURE 3-1: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

(A) (B) (D) (D) (C) (A)

SCL

SDA

START ADDRESS OR DATA STOP

CONDITION ACKNOWLEDGE ALLOWED CONDITION

VALID TO CHANGE

DS21081F-page 4 1999 Microchip Technology Inc.

24C08B/16B

3.6 Device Addressing 4.0 WRITE OPERATION

A control byte is the first byte received following the 4.1 Byte Write

start condition from the master device. The control byte

consists of a 4-bit control code, for the 24C08B/16B Following the start condition from the master, the

this is set as 1010 binary for read and write operations. device code (4 bits), the block address (3 bits), and the

The next three bits of the control byte are the block R/W bit which is a logic low is placed onto the bus by

select bits (B2, B1, B0). They are used by the master the master transmitter. This indicates to the addressed

device to select which of the eight 256 word blocks of slave receiver that a byte with a word address will follow

memory are to be accessed. These bits are in effect the after it has generated an acknowledge bit during the

three most significant bits of the word address. ninth clock cycle. Therefore the next byte transmitted by

The last bit of the control byte defines the operation to the master is the word address and will be written into

be performed. When set to one a read operation is the address pointer of the 24C08B/16B. After receiving

selected, when set to zero a write operation is selected. another acknowledge signal from the 24C08B/16B the

Following the start condition, the 24C08B/16B monitors master device will transmit the data word to be written

the SDA bus checking the device type identifier being into the addressed memory location. The 24C08B/16B

transmitted, upon a 1010 code the slave device outputs acknowledges again and the master generates a stop

an acknowledge signal on the SDA line. Depending on condition. This initiates the internal write cycle, and dur-

the state of the R/W bit, the 24C08B/16B will select a ing this time the 24C08B/16B will not generate

read or write operation. acknowledge signals (Figure 4-1).

Control 4.2 Page Write

Operation Block Select R/W

Code

The write control byte, word address and the first data

Read 1010 Block Address 1 byte are transmitted to the 24C08B/16B in the same

Write 1010 Block Address 0 way as in a byte write. But instead of generating a stop

condition the master transmits up to 16 data bytes to

FIGURE 3-2: CONTROL BYTE the 24C08B/16B which are temporarily stored in the

ALLOCATION on-chip page buffer and will be written into the memory

START READ/WRITE after the master has transmitted a stop condition. After

the receipt of each word, the four lower order address

pointer bits are internally incremented by one. The

SLAVE ADDRESS R/W A higher order seven bits of the word address remains

constant. If the master should transmit more than 16

words prior to generating the stop condition, the

address counter will roll over and the previously

received data will be overwritten. As with the byte write

1 0 1 0 B2 B1 B0 operation, once the stop condition is received an inter-

nal write cycle will begin (Figure 4-2).

Note: Page write operations are limited to writing

bytes within a single physical page, regard-

less of the number of bytes actually being

written. Physical page boundaries start at

addresses that are integer multiples of the

page buffer size (or Ôpage sizeÕ) and end at

addresses that are integer multiples of

[page size - 1]. If a page write command

attempts to write across a physical page

boundary, the result is that the data wraps

around to the beginning of the current page

(overwriting data previously stored there),

instead of being written to the next page as

might be expected. It is therefore neces-

sary for the application software to prevent

page write operations that would attempt to

cross a page boundary.

1999 Microchip Technology Inc. DS21081F-page 5

24C08B/16B

FIGURE 4-1: BYTE WRITE

S S

BUS ACTIVITY T CONTROL WORD T

MASTER A BYTE ADDRESS DATA O

R P

T

SDA LINE S P

A A A

BUS ACTIVITY C C C

K K K

FIGURE 4-2: PAGE WRITE

S S

BUS ACTIVITY T T

MASTER A CONTROL WORD

BYTE ADDRESS (n) DATA n DATA n + 1 DATA n + 15 O

R P

T

SDA LINE S P

A A A A A

BUS ACTIVITY C C C C C

K K K K K

DS21081F-page 6 1999 Microchip Technology Inc.

24C08B/16B

5.0 ACKNOWLEDGE POLLING 7.0 READ OPERATION

Since the device will not acknowledge during a write Read operations are initiated in the same way as write

cycle, this can be used to determine when the cycle is operations with the exception that the R/W bit of the

complete (this feature can be used to maximize bus slave address is set to one. There are three basic types

throughput). Once the stop condition for a write com- of read operations: current address read, random

mand has been issued from the master, the device ini- read, and sequential read.

tiates the internally timed write cycle. ACK polling can

be initiated immediately. This involves the master send- 7.1 Current Address Read

ing a start condition followed by the control byte for a

The 24C08B/16B contains an address counter that

write command (R/W = 0). If the device is still busy with

maintains the address of the last word accessed, inter-

the write cycle, then no ACK will be returned. If the

nally incremented by one. Therefore, if the previous

cycle is complete, then the device will return the ACK

access (either a read or write operation) was to

and the master can then proceed with the next read or

address n, the next current address read operation

write command. See Figure 5-1 for flow diagram.

would access data from address n + 1. Upon receipt of

FIGURE 5-1: ACKNOWLEDGE POLLING the slave address with R/W bit set to one, the

FLOW 24C08B/16B issues an acknowledge and transmits the

8-bit data word. The master will not acknowledge the

Send transfer but does generate a stop condition and the

Write Command 24C08B/16B discontinues transmission (Figure 7-1).

7.2 Random Read

Send Stop Random read operations allow the master to access

Condition to any memory location in a random manner. To perform

Initiate Write Cycle this type of read operation, first the word address must

be set. This is done by sending the word address to the

24C08B/16B as part of a write operation. After the word

Send Start address is sent, the master generates a start condition

following the acknowledge. This terminates the write

operation, but not before the internal address pointer is

set. Then the master issues the control byte again but

Send Control Byte with the R/W bit set to a one. The 24C08B/16B will then

with R/W = 0 issue an acknowledge and transmits the 8-bit data

word. The master will not acknowledge the transfer but

does generate a stop condition and the 24C08B/16B

discontinues transmission (Figure 7-2).

Did Device NO

Acknowledge 7.3 Sequential Read

(ACK = 0)?

Sequential reads are initiated in the same way as a ran-

YES dom read except that after the 24C08B/16B transmits

the first data byte, the master issues an acknowledge

Next

Operation as opposed to a stop condition in a random read. This

directs the 24C08B/16B to transmit the next sequen-

tially addressed 8 bit word (Figure 7-3).

6.0 WRITE PROTECTION To provide sequential reads the 24C08B/16B contains

an internal address pointer which is incremented by

The 24C08B/16B can be used as a serial ROM when one at the completion of each operation. This address

the WP pin is connected to VCC. Programming will be pointer allows the entire memory contents to be serially

inhibited and the entire memory will be write-protected. read during one operation.

7.4 Noise Protection

The 24C08B/16B employs a VCC threshold detector cir-

cuit which disables the internal erase/write logic if the

VCC is below 1.5 volts at nominal conditions.

The SCL and SDA inputs have Schmitt trigger and filter

circuits which suppress noise spikes to assure proper

device operation even on a noisy bus.

1999 Microchip Technology Inc. DS21081F-page 7

24C08B/16B

FIGURE 7-1: CURRENT ADDRESS READ

S

T CONTROL S

BUS ACTIVITY A T

MASTER BYTE DATA n

R O

T P

SDA LINE S P

A N

BUS ACTIVITY C O

K

A

C

K

FIGURE 7-2: RANDOM READ

S S

T T S

BUS ACTIVITY A CONTROL WORD A CONTROL T

MASTER R BYTE ADDRESS (n) R BYTE DATA (n) O

T T P

S S P

SDA LINE

A A A N

C C C O

K K K

BUS ACTIVITY A

C

K

FIGURE 7-3: SEQUENTIAL READ

S

T

O

BUS ACTIVITY CONTROL P

MASTER BYTE DATA n DATA n + 1 DATA n + 2 DATA n + X

SDA LINE P

A A A A N

BUS ACTIVITY C C C C O

K K K K

A

C

K

8.0 PIN DESCRIPTIONS 8.3 WP

8.1 SDA Serial Address/Data Input/Output This pin must be connected to either VSS or VCC.

If tied to VSS, normal memory operation is enabled

This is a Bi-directional pin used to transfer addresses (read/write the entire memory 000-7FF).

and data into and data out of the device. It is an open

drain terminal, therefore the SDA bus requires a pull-up If tied to VCC, WRITE operations are inhibited. The

resistor to VCC (typical 10 kΩ). entire memory will be write-protected. Read opera-

tions are not affected.

For normal data transfer SDA is allowed to change only

during SCL low. Changes during SCL high are This feature allows the user to use the 24C08B/16B as

reserved for indicating the START and STOP condi- a serial ROM when WP is enabled (tied to VCC).

tions.

8.4 A0, A1, A2

8.2 SCL Serial Clock

These pins are not used by the 24C08B/16B. They

This input is used to synchronize the data transfer from may be left floating or tied to either VSS or VCC.

and to the device.

DS21081F-page 8 1999 Microchip Technology Inc.

24C08B/16B

NOTES:

1999 Microchip Technology Inc. DS21081F-page 9

24C08B/16B

NOTES:

DS21081F-page 10 1999 Microchip Technology Inc.

24C08B/16B

24C08B/16B Product Identification System

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed

sales offices.

24C08B/16B – E /P

P = Plastic DIP (300 mil Body), 8-lead

Package: SL = Plastic SOIC (150 mil Body), 14-lead

SN = Plastic SOIC (150 mil Body), 8-lead

Temperature Blank = 0°C to +70°C

Range: I = -40°C to +85°C

E = -40°C to +125°C

24C08B 8K I2C Serial EEPROM

Device: 24C08BT 8K I2C Serial EEPROM (Tape and Reel)

24C16B 16K I2C Serial EEPROM

24C16BT 16K I2C Serial EEPROM (Tape and Reel)

Sales and Support

Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-

mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277

3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

1999 Microchip Technology Inc. DS21081F-page 11

Note the following details of the code protection feature on PICmicro® MCUs.

• The PICmicro family meets the specifications contained in the Microchip Data Sheet.

• Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today,

when used in the intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowl-

edge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet.

The person doing so may be engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable”.

• Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of

our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device Trademarks

applications and the like is intended through suggestion only

and may be superseded by updates. It is your responsibility to The Microchip name and logo, the Microchip logo, FilterLab,

ensure that your application meets with your specifications. KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER,

No representation or warranty is given and no liability is PICSTART, PRO MATE, SEEVAL and The Embedded Control

assumed by Microchip Technology Incorporated with respect Solutions Company are registered trademarks of Microchip Tech-

to the accuracy or use of such information, or infringement of nology Incorporated in the U.S.A. and other countries.

patents or other intellectual property rights arising from such

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB,

use or otherwise. Use of Microchip’s products as critical com-

In-Circuit Serial Programming, ICSP, ICEPIC, microPort,

ponents in life support systems is not authorized except with

Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM,

express written approval by Microchip. No licenses are con-

MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode

veyed, implicitly or otherwise, under any intellectual property

and Total Endurance are trademarks of Microchip Technology

rights.

Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark

of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2002, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received QS-9000 quality system

certification for its worldwide headquarters,

design and wafer fabrication facilities in

Chandler and Tempe, Arizona in July 1999. The

Company’s quality system processes and

procedures are QS-9000 compliant for its

PICmicro® 8-bit MCUs, KEELOQ® code hopping

devices, Serial EEPROMs and microperipheral

products. In addition, Microchip’s quality

system for the design and manufacture of

development systems is ISO 9001 certified.

2002 Microchip Technology Inc.

M

WORLDWIDE SALES AND SERVICE

AMERICAS ASIA/PACIFIC Japan

Microchip Technology Japan K.K.

Corporate Office Australia

Benex S-1 6F

2355 West Chandler Blvd. Microchip Technology Australia Pty Ltd

3-18-20, Shinyokohama

Chandler, AZ 85224-6199 Suite 22, 41 Rawson Street

Kohoku-Ku, Yokohama-shi

Tel: 480-792-7200 Fax: 480-792-7277 Epping 2121, NSW

Kanagawa, 222-0033, Japan

Technical Support: 480-792-7627 Australia

Web Address: http://www.microchip.com Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Rocky Mountain China - Beijing Korea

2355 West Chandler Blvd. Microchip Technology Consulting (Shanghai) Microchip Technology Korea

Chandler, AZ 85224-6199 Co., Ltd., Beijing Liaison Office 168-1, Youngbo Bldg. 3 Floor

Tel: 480-792-7966 Fax: 480-792-7456 Unit 915 Samsung-Dong, Kangnam-Ku

Bei Hai Wan Tai Bldg. Seoul, Korea 135-882

Atlanta No. 6 Chaoyangmen Beidajie Tel: 82-2-554-7200 Fax: 82-2-558-5934

500 Sugar Mill Road, Suite 200B Beijing, 100027, No. China Singapore

Atlanta, GA 30350 Tel: 86-10-85282100 Fax: 86-10-85282104 Microchip Technology Singapore Pte Ltd.

Tel: 770-640-0034 Fax: 770-640-0307 200 Middle Road

China - Chengdu

Boston #07-02 Prime Centre

Microchip Technology Consulting (Shanghai)

2 Lan Drive, Suite 120 Singapore, 188980

Co., Ltd., Chengdu Liaison Office

Westford, MA 01886 Tel: 65-334-8870 Fax: 65-334-8850

Rm. 2401, 24th Floor,

Tel: 978-692-3848 Fax: 978-692-3821 Taiwan

Ming Xing Financial Tower

Chicago No. 88 TIDU Street Microchip Technology Taiwan

333 Pierce Road, Suite 180 Chengdu 610016, China 11F-3, No. 207

Itasca, IL 60143 Tel: 86-28-6766200 Fax: 86-28-6766599 Tung Hua North Road

Tel: 630-285-0071 Fax: 630-285-0075 Taipei, 105, Taiwan

China - Fuzhou

Dallas Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

Microchip Technology Consulting (Shanghai)

4570 Westgrove Drive, Suite 160 Co., Ltd., Fuzhou Liaison Office

Addison, TX 75001 Unit 28F, World Trade Plaza

Tel: 972-818-7423 Fax: 972-818-2924 EUROPE

No. 71 Wusi Road

Detroit Fuzhou 350001, China Denmark

Tri-Atria Office Building Tel: 86-591-7503506 Fax: 86-591-7503521 Microchip Technology Nordic ApS

32255 Northwestern Highway, Suite 190 China - Shanghai Regus Business Centre

Farmington Hills, MI 48334 Microchip Technology Consulting (Shanghai) Lautrup hoj 1-3

Tel: 248-538-2250 Fax: 248-538-2260 Co., Ltd. Ballerup DK-2750 Denmark

Kokomo Room 701, Bldg. B Tel: 45 4420 9895 Fax: 45 4420 9910

2767 S. Albright Road Far East International Plaza France

Kokomo, Indiana 46902 No. 317 Xian Xia Road Microchip Technology SARL

Tel: 765-864-8360 Fax: 765-864-8387 Shanghai, 200051 Parc d’Activite du Moulin de Massy

Los Angeles Tel: 86-21-6275-5700 Fax: 86-21-6275-5060 43 Rue du Saule Trapu

18201 Von Karman, Suite 1090 China - Shenzhen Batiment A - ler Etage

Irvine, CA 92612 91300 Massy, France

Microchip Technology Consulting (Shanghai)

Tel: 949-263-1888 Fax: 949-263-1338 Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Co., Ltd., Shenzhen Liaison Office

New York Rm. 1315, 13/F, Shenzhen Kerry Centre, Germany

150 Motor Parkway, Suite 202 Renminnan Lu Microchip Technology GmbH

Hauppauge, NY 11788 Shenzhen 518001, China Gustav-Heinemann Ring 125

Tel: 631-273-5305 Fax: 631-273-5335 Tel: 86-755-2350361 Fax: 86-755-2366086 D-81739 Munich, Germany

Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

San Jose Hong Kong

Microchip Technology Inc. Microchip Technology Hongkong Ltd. Italy

2107 North First Street, Suite 590 Unit 901-6, Tower 2, Metroplaza Microchip Technology SRL

San Jose, CA 95131 223 Hing Fong Road Centro Direzionale Colleoni

Tel: 408-436-7950 Fax: 408-436-7955 Kwai Fong, N.T., Hong Kong Palazzo Taurus 1 V. Le Colleoni 1

Tel: 852-2401-1200 Fax: 852-2401-3431 20041 Agrate Brianza

Toronto

Milan, Italy

6285 Northam Drive, Suite 108 India Tel: 39-039-65791-1 Fax: 39-039-6899883

Mississauga, Ontario L4V 1X5, Canada Microchip Technology Inc.

Tel: 905-673-0699 Fax: 905-673-6509 India Liaison Office United Kingdom

Divyasree Chambers Arizona Microchip Technology Ltd.

1 Floor, Wing A (A3/A4) 505 Eskdale Road

No. 11, O’Shaugnessey Road Winnersh Triangle

Bangalore, 560 025, India Wokingham

Tel: 91-80-2290061 Fax: 91-80-2290062 Berkshire, England RG41 5TU

Tel: 44 118 921 5869 Fax: 44-118 921-5820

01/18/02

2002 Microchip Technology Inc.

You might also like

- Embedded Systems Basics - Lecture Notes - DrJineshDocument114 pagesEmbedded Systems Basics - Lecture Notes - DrJineshJineshNo ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Question Bank For EEE 366Document6 pagesQuestion Bank For EEE 366sramukNo ratings yet

- ESP32 IoT DEVELOPMENT TRAINER KIT ManualDocument67 pagesESP32 IoT DEVELOPMENT TRAINER KIT ManualandiNo ratings yet

- 24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsDocument12 pages24Lc04B/08B: 4K/8K 2.5V I C Serial Eepromsjiaxin zhangNo ratings yet

- 24LC08 PDFDocument30 pages24LC08 PDFJaime BarrancoNo ratings yet

- Datasheet PDFDocument26 pagesDatasheet PDFNicoli LourençoNo ratings yet

- 24AA08/24LC08B: 8KI C Serial EEPROMDocument30 pages24AA08/24LC08B: 8KI C Serial EEPROMjoseNo ratings yet

- 24AA16/24LC16B: 16K I C Serial EEPROMDocument25 pages24AA16/24LC16B: 16K I C Serial EEPROMDaniel VásquezNo ratings yet

- 24aa08 - 24lc08 Eeprom PDFDocument40 pages24aa08 - 24lc08 Eeprom PDFEdgar DauzonNo ratings yet

- CAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromDocument11 pagesCAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromAdnen GuedriaNo ratings yet

- 1K/2K/4K 5.0V CMOS Serial EEPROM: Features Package TypeDocument8 pages1K/2K/4K 5.0V CMOS Serial EEPROM: Features Package TypeHarris RaoNo ratings yet

- EEPROM 24LC256 - Microchip PDFDocument28 pagesEEPROM 24LC256 - Microchip PDFValdir DerlannNo ratings yet

- 24AA256/24LC256: 256K I C Cmos Serial EepromDocument12 pages24AA256/24LC256: 256K I C Cmos Serial EepromWelleyNo ratings yet

- 24AA00/24LC00/24C00: 128 Bit I C™ Bus Serial EEPROMDocument12 pages24AA00/24LC00/24C00: 128 Bit I C™ Bus Serial EEPROMmacepaNo ratings yet

- 24AA64/24LC64/24FC64: 64K I C Serial EEPROMDocument28 pages24AA64/24LC64/24FC64: 64K I C Serial EEPROMJuan Luis Pineda GonzálezNo ratings yet

- Ic PDFDocument36 pagesIc PDFdharamNo ratings yet

- 32K 5.0V I C Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Serial EEPROM: Features Package TypesChrono GtzNo ratings yet

- IS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromDocument16 pagesIS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromPablo Diego Cecere CasadoNo ratings yet

- IS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromDocument16 pagesIS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromPablo Diego Cecere CasadoNo ratings yet

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument32 pages24AA02/24LC02B: 2KI C Serial EEPROMhanifNo ratings yet

- 24 LC 256Document38 pages24 LC 256johnNo ratings yet

- I2c EEPROM 24xx256 DsDocument28 pagesI2c EEPROM 24xx256 DsRizwan AmirNo ratings yet

- 24AA024 MicrochipTechnologyDocument22 pages24AA024 MicrochipTechnologydasdracheNo ratings yet

- 24C01A/02A/04A 1K/2K/4K 5.0V I2C Serial EEPROMsDocument12 pages24C01A/02A/04A 1K/2K/4K 5.0V I2C Serial EEPROMsABDUL QADIRNo ratings yet

- 24aa515, 24LC515, 24FC515Document20 pages24aa515, 24LC515, 24FC515dorudNo ratings yet

- 21073K PDFDocument24 pages21073K PDFadfumegaNo ratings yet

- 24lc512 DatasheetDocument27 pages24lc512 DatasheetLeonardo QuevedoNo ratings yet

- Atmel 24c02 PDFDocument30 pagesAtmel 24c02 PDFMAX GNo ratings yet

- CAT24WC01/02/04/08/16: 1K/2K/4K/8K/16K-Bit Serial E Prom FeaturesDocument10 pagesCAT24WC01/02/04/08/16: 1K/2K/4K/8K/16K-Bit Serial E Prom FeaturesAgustin AndrokaitesNo ratings yet

- 24LC04B PDFDocument22 pages24LC04B PDFEddy RosarioNo ratings yet

- 24WC01 PDFDocument10 pages24WC01 PDFneko1212121515123001No ratings yet

- 1K 5.0V I C™ Serial EEPROM: Features: DescriptionDocument36 pages1K 5.0V I C™ Serial EEPROM: Features: DescriptionDanna PerezNo ratings yet

- 24AA02H 24LC02BH 2K I2C Serial EEPROM With Half Array Write Protect 20002105BDocument40 pages24AA02H 24LC02BH 2K I2C Serial EEPROM With Half Array Write Protect 20002105BAlhassan Ahmed OmranNo ratings yet

- At24c02a 04a 08aDocument16 pagesAt24c02a 04a 08aretno.endah ekowatiNo ratings yet

- 32K 5.0V I C Smart Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Smart Serial EEPROM: Features Package TypesRamon LopezNo ratings yet

- 24aa512 Mic PDFDocument28 pages24aa512 Mic PDFkt2018No ratings yet

- NM24C04/05 - 4K-Bit Standard 2-Wire Bus Interface Serial EEPROMDocument14 pagesNM24C04/05 - 4K-Bit Standard 2-Wire Bus Interface Serial EEPROMAbel RodriguezNo ratings yet

- 24AA04/24LC04B/24FC04: 4KI C Serial EEPROMDocument45 pages24AA04/24LC04B/24FC04: 4KI C Serial EEPROMDinu Racautanu MironNo ratings yet

- 24C32Document12 pages24C32SilviuCocoloșNo ratings yet

- 25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMDocument23 pages25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMЕвгенийNo ratings yet

- 24AA128/24LC128/24FC128: 128K I C Serial EEPROMDocument44 pages24AA128/24LC128/24FC128: 128K I C Serial EEPROMJosemar M. FerreiraNo ratings yet

- A25L016 Series: 16mbit Low Voltage, Serial Flash Memory With 100Mhz Uniform 4Kb SectorsDocument41 pagesA25L016 Series: 16mbit Low Voltage, Serial Flash Memory With 100Mhz Uniform 4Kb SectorsНиколайNo ratings yet

- 24AA1025/24LC1025/24FC1025: 1024K I C Serial EEPROMDocument29 pages24AA1025/24LC1025/24FC1025: 1024K I C Serial EEPROMSudhagarSubbiyanNo ratings yet

- 24FC1025 EepromDocument28 pages24FC1025 EepromAnirudh ReddyNo ratings yet

- 24AA128/24LC128/24FC128: 128K I C Cmos Serial EepromDocument26 pages24AA128/24LC128/24FC128: 128K I C Cmos Serial EepromcraponzelNo ratings yet

- 24l1026i Memoria EEPROM 1024kDocument28 pages24l1026i Memoria EEPROM 1024kMarta_d_eNo ratings yet

- 32K 5.0V I C Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Serial EEPROM: Features Package Typesinsomnium86No ratings yet

- FM24C08U/09U - 8K-Bit Standard 2-Wire Bus Interface Serial EEPROMDocument15 pagesFM24C08U/09U - 8K-Bit Standard 2-Wire Bus Interface Serial EEPROMlord_beast2.05No ratings yet

- CAT24WC256: 256K-Bit I C Serial Cmos EepromDocument10 pagesCAT24WC256: 256K-Bit I C Serial Cmos EepromAntonio ManuelNo ratings yet

- 24AA1025 24LC1025 24FC1025 1024 Kbit I2C Serial EE-2853738Document32 pages24AA1025 24LC1025 24FC1025 1024 Kbit I2C Serial EE-2853738İbrahim DemircioğluNo ratings yet

- 8K/16K 5.0V SPI Bus Serial EEPROM: Features Package TypesDocument12 pages8K/16K 5.0V SPI Bus Serial EEPROM: Features Package Typesrıdvan71No ratings yet

- 24aa256uid 256k I2c Serial Eeprom With Eui48 Eui64 20005215dDocument28 pages24aa256uid 256k I2c Serial Eeprom With Eui48 Eui64 20005215dAbhishek BhattacharjeeNo ratings yet

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument24 pages24AA02/24LC02B: 2KI C Serial EEPROMMayk OzNo ratings yet

- 32K 2.5V I C Serial EEPROM: Features Package TypesDocument12 pages32K 2.5V I C Serial EEPROM: Features Package Typesinsomnium86No ratings yet

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocument34 pages24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMKhalid BenaribaNo ratings yet

- 24LC21 1K 2.5V Dual Mode I2C Serial EEPROMDocument12 pages24LC21 1K 2.5V Dual Mode I2C Serial EEPROMVictor TruccoNo ratings yet

- Atmel 752 24c08aDocument13 pagesAtmel 752 24c08aEngin UzunNo ratings yet

- EEPROM 24WC256 - CatalystDocument8 pagesEEPROM 24WC256 - CatalystValdir DerlannNo ratings yet

- Serial Eeprom: K24C02 / K24C04 / K24C08 / K24C16Document14 pagesSerial Eeprom: K24C02 / K24C04 / K24C08 / K24C16eliarNo ratings yet

- AT24C01A/02/04/08/16: FeaturesDocument14 pagesAT24C01A/02/04/08/16: FeaturesVeronica GonzalezNo ratings yet

- 24AA02 24LC02B 24FC02 2K I2C Serial EEPROM 2000170-2577009Document52 pages24AA02 24LC02B 24FC02 2K I2C Serial EEPROM 2000170-2577009MindSet MarcosNo ratings yet

- Label Printer: User's ManualDocument33 pagesLabel Printer: User's Manualarunan55No ratings yet

- Srp-350352iii Rev 1 04Document24 pagesSrp-350352iii Rev 1 04arunan55No ratings yet

- Manual Slp-t40xx User English Rev 1 10Document33 pagesManual Slp-t40xx User English Rev 1 10arunan55No ratings yet

- ThanthrsamuchayamDocument167 pagesThanthrsamuchayamarunan55No ratings yet

- VHDL RecDocument173 pagesVHDL Recarunan55No ratings yet

- Altium Designer 14 License OptionsDocument1 pageAltium Designer 14 License Optionsarunan55No ratings yet

- Hermetic Silicon PhototransistorDocument5 pagesHermetic Silicon PhototransistorRahul SushruthNo ratings yet

- D D D D D D D D D: Description/ordering InformationDocument19 pagesD D D D D D D D D: Description/ordering Informationarunan55No ratings yet

- Heatsinks For DIL-IC, PLCC and SMDDocument1 pageHeatsinks For DIL-IC, PLCC and SMDthetkhinechoNo ratings yet

- Datasheet PDFDocument7 pagesDatasheet PDFarunan55No ratings yet

- Atmega64 Dev BoardDocument1 pageAtmega64 Dev Boardarunan55100% (1)

- Altium Designer 14 License OptionsDocument1 pageAltium Designer 14 License Optionsarunan55No ratings yet

- PIC 16f877a Data SheetDocument234 pagesPIC 16f877a Data Sheetanon-26401438% (8)

- 2716Document15 pages2716arunan55No ratings yet

- C For PICDocument10 pagesC For PICarunan55No ratings yet

- 27128Document10 pages27128arunan55No ratings yet

- 1 N 4148Document4 pages1 N 4148arunan55No ratings yet

- 8051 Micro Controller To UART Serial Interface Evaluation BoaDocument8 pages8051 Micro Controller To UART Serial Interface Evaluation Boaarunan55No ratings yet

- DSDocument4 pagesDSarunan55No ratings yet

- 24 C 32Document8 pages24 C 32arunan55No ratings yet

- Nmos 32K (4K X 8) Uv Eprom: DescriptionDocument9 pagesNmos 32K (4K X 8) Uv Eprom: Descriptionarunan55No ratings yet

- 1N4148.1N4448 (Fast Diodes)Document5 pages1N4148.1N4448 (Fast Diodes)arunan55No ratings yet

- 1N4148 - Diode DatasheetDocument2 pages1N4148 - Diode Datasheethelp-me-quickNo ratings yet

- LCD-240G064A 240 X 64 Dots Graphic LCD: VishayDocument3 pagesLCD-240G064A 240 X 64 Dots Graphic LCD: Vishayarunan55No ratings yet

- 1N4728A... 1N4761A Silicon Power Z-DiodesDocument5 pages1N4728A... 1N4761A Silicon Power Z-Diodesarunan55No ratings yet

- 1N4728 4752 PDFDocument2 pages1N4728 4752 PDFarunan55No ratings yet

- Diod ZenerDocument6 pagesDiod ZenerLeonel MartinezNo ratings yet

- 1 N 4148Document1 page1 N 4148arunan55No ratings yet

- LCD-020M004B 20 X 4 Character LCD: VishayDocument3 pagesLCD-020M004B 20 X 4 Character LCD: Vishayarunan55No ratings yet

- Shenzhen First-Rank Technology Co., Ltd T24C02A/T24C04A/T24C08A/T24C16A EEPROM SpecificationDocument15 pagesShenzhen First-Rank Technology Co., Ltd T24C02A/T24C04A/T24C08A/T24C16A EEPROM SpecificationgenedgNo ratings yet

- Data Sheet of RL508 FM TunerDocument20 pagesData Sheet of RL508 FM Tunerapi-432313169No ratings yet

- 20005356BDocument20 pages20005356Banil ariNo ratings yet

- MAX9669 MaximIntegrated PDFDocument23 pagesMAX9669 MaximIntegrated PDFvdiazp85No ratings yet

- Adt 7420Document24 pagesAdt 7420Vlad TusanNo ratings yet

- Wii NotesDocument36 pagesWii NotesThomas ErikssenNo ratings yet

- I 2 CDocument3 pagesI 2 CTrieu HuynhNo ratings yet

- Ibm Openpower Power p9 Boot Flow NotesDocument81 pagesIbm Openpower Power p9 Boot Flow NotesPonmalai SNo ratings yet

- DIY Arduino + GY-906 Infrared Thermometer - Arduino Project HubDocument19 pagesDIY Arduino + GY-906 Infrared Thermometer - Arduino Project HubPhops FrealNo ratings yet

- Usage of D6T-44L - 8L - 1A Thermal SensorDocument23 pagesUsage of D6T-44L - 8L - 1A Thermal SensorEduardo ggNo ratings yet

- DS1307 RTC Clock Displays TimeDocument6 pagesDS1307 RTC Clock Displays TimeSohaib Ahmad100% (2)

- Networks For Embedded Systems I2C BusDocument4 pagesNetworks For Embedded Systems I2C BusAhmed Al-MasoodiNo ratings yet

- Digital Controlled Stereo Audio Processor with Loudness and Volume ControlDocument13 pagesDigital Controlled Stereo Audio Processor with Loudness and Volume ControlJose BenavidesNo ratings yet

- Watt Hour 00220aDocument97 pagesWatt Hour 00220ajb609No ratings yet

- PBX-USB Manual PDFDocument2 pagesPBX-USB Manual PDFIon MoldoveanuNo ratings yet

- Pca 9306Document32 pagesPca 9306Adhiezzz GamingNo ratings yet

- Zumo Shield For ArduinoDocument40 pagesZumo Shield For ArduinoJhony TacuriNo ratings yet

- Service Manual JVC RX-7010vbkDocument53 pagesService Manual JVC RX-7010vbkaliarroNo ratings yet

- Battery Cell Balancing For Improved Performance in EVsDocument11 pagesBattery Cell Balancing For Improved Performance in EVsSayyidatul Isarah AllamahNo ratings yet

- Neonode Touch Sensor Module User's Guide PDFDocument121 pagesNeonode Touch Sensor Module User's Guide PDFdummy accountNo ratings yet

- Description of Components 3.1 MPU 6050Document13 pagesDescription of Components 3.1 MPU 6050nishtha bansalNo ratings yet

- Sony KD-55X9005C, KD-65X9005C, KD-75X9105C GN1T-XBDocument257 pagesSony KD-55X9005C, KD-65X9005C, KD-75X9105C GN1T-XBDJALMA MOREIRANo ratings yet

- SimpleBGC Manual 2.2 (English Version)Document12 pagesSimpleBGC Manual 2.2 (English Version)Otto HerreroNo ratings yet

- Hackatronics Arduino Multi-Function Shield Projects: by Kashif Baig © 2019 Cohesivecomputing - Co.ukDocument30 pagesHackatronics Arduino Multi-Function Shield Projects: by Kashif Baig © 2019 Cohesivecomputing - Co.ukJUAN PEREZNo ratings yet

- Level 3 Repair: 8-1. Components LayoutDocument36 pagesLevel 3 Repair: 8-1. Components LayoutGideao AstunNo ratings yet

- Trojan T-225Ah LAB battery charger programDocument15 pagesTrojan T-225Ah LAB battery charger programDuraya IsmailNo ratings yet

- PIC16F1503Document352 pagesPIC16F1503kamalNo ratings yet