Professional Documents

Culture Documents

Data Isolation For Loop-Powered Applications: TI Designs

Uploaded by

Milan ĐorđevicOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Data Isolation For Loop-Powered Applications: TI Designs

Uploaded by

Milan ĐorđevicCopyright:

Available Formats

TI Designs

Data Isolation for Loop-Powered Applications

TI Designs Design Features

TI Designs provide the foundation that you need Isolated Single-Wire Bidirectional Data

including methodology, testing and design files to Transmission

quickly evaluate and customize the system. TI Designs Bit Rates up to 1Mbps

help you accelerate your time to market.

Low-Power Data Transmission

Design Resources System Shutdown Current 4-A at 3 V

Integrated 64KB FRAM with 8MBps In-System

TIDA-00245 Design Folder

Writes

MSP430FR5969 Product Folder

Featured Applications

Factory Automation and Process Control

ASK Our E2E Experts

WEBENCH Calculator Tools Sensors and Field Transmitters

Building Automation

Field Actuators

4- to 20-mA Loop Process Control

Sensor Management

Data Logging

VCC VCC

TX/RX TX/RX

MSP430FR5969 MSP430FR5969

Isolation

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other

important disclaimers and information.

All trademarks are the property of their respective owners.

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 1

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Introduction www.ti.com

1 Introduction

Because ground potential differences higher than 100 V are common in industrial environments, some

sensors (like thermocouple sensors) and signal conditioning circuitry must be galvanically isolated from

ground. In isolated sensor transmitters, both the power supply and the data transmission have to be

isolated. The data transmission can be either unidirectional or bidirectional. An isolated thermocouple

sensor is shown in Figure 1. This design focuses on only the bidirectional communication between two

microcontrollers (MSP430FR5969) across the isolation. For an isolated ultra-low power (ULP) design for

4- to 20-mA loop-powered transmitters, please see TIDA-00167.

A bidirectional communication is needed in systems in which not only the isolated sensor side sends the

data, but also the host provides, for example, configuration data to the isolated sensor side. The challenge

of such a solution is first of all the limited size within sensor transmitters (industry standard) and, in case of

a loop-powered system, the overall current consumption.

A single-wire interface is crucial to insure space and power consumption constrains. In the real

application, one MCU (placed on the isolated side) takes care of the signal conditioning (linearization,

calibration, data acquisition routine) while the second MCU (on the non-isolated side) takes care for the

communication (in case of HART or more complex communications than just 4 to 20 mA) but as well of

sending different configurations to the sensor side.

To show case the functionality, the hardware of the TIDA-00245 includes BoosterPack connectors on

both sides of the isolation. BoosterPack plug-in modules allow the user to extend the functionality of the

hardware and add features like wireless connectivity, capacitive touch, temperature sensing, displays, and

much more. The design files include design considerations, block diagrams, schematics, bill of materials

(BOM), layer plots, Altium files, Gerber files, and MSP430 firmware.

4.5 V

LDO Half Bridge LDO

4.7 V

3.3 V

LDO

TC Filters 3.3 V

Loop:

Protections 10 33 V

ADC MCU MCU DAC

PT100

Isothermal

block

CJ RTD

Isolation

TIDA-00245

Figure 1. Isolated Thermocouple Sensor

2 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Key System Specifications

2 Key System Specifications

The key design requirements and features are as follows:

Table 1. Key System Specifications

PARAMETER SPECIFICATION MIN TYP MAX UNIT

VCC Supply voltage range 1.8 3.6 V

TA Operating free-air temperature 40 85 C

fSYSTEM Processor frequency (maximum MCLK frequency) 16 MHz

Data rate 1 Mbps

Both CPUs active at 8 MHz and bidirectional communication

1826 A

with 1 Mbaud at 3 V

Both CPUs active at 8 MHz and bidirectional communication

1772 A

Active current for with 1 Mbaud at 2.2 V

complete system Both CPUs active at 8 MHz and unidirectional communication

2157 A

with 1 Mbaud at 3 V

Both CPUs active at 8 MHz and unidirectional communication

2090 A

with 1 Mbaud at 2.2 V

Standby current System standby and receive ready at 3 V 44 A

System standby and receive ready at 2.2 V 33 A

Shutdown current System shutdown current at 3 V 4 A

System shutdown current at 2.2 V 3.4 A

FRAM write speed 8 MBps

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 3

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

System Description www.ti.com

3 System Description

3.1 Transformer Coupled Interface

The TIDA-00245 uses galvanic isolation, which has an inherent life span advantage over an optocoupler

isolator. Industrial devices are typically pressed into service for much longer periods of time than

consumer electronics. Therefore, maintenance of effective isolation over a period of over 15 years is

important. In systems requiring galvanic isolation between the transmitter and the receiver, the commonly

used coupling element is a pulse transformer.

For the data transmission, the eUSCI_A (Enhanced Universal Serial Communication Interface) module

and the Comparator_E (COMP_E) module of the MSP430FR5969 are used. The eUSCI_A module is

configured for asynchronous UART mode. In asynchronous UART mode, the eUSCI_A module connect

the MSP430FR5969 to an external system through two external pins, UCAxRXD and UCAxTXD. In UART

mode, the eUSCI_A transmits and receives characters at a bit rate asynchronous to another device.

Timing for each character is based on the selected baud rate of the eUSCI_A module. The transmit and

receive functions use the same baud-rate frequency. Alternatively, the automatic baud rate detection

feature of the eUSCI_A module can be used. For automatic baud rate detection, a data frame is preceded

by a synchronization sequence that consists of a break and a synch field.

The transformer passes only the AC components of the eUSCI_A square waveform resulting in an

impulse train across the secondary winding. The COMP_E of the MSP430 then converts the impulse train

into a square waveform. This square waveform is identical to the TX square waveform of the eUSCI_A

module from the primary side and is fed into the UCAxRXD pin of the eUSCI_A module on the secondary

side.

Because the transformer is a symmetrical device (particularly one with a 1:1 winding ratio), it is simple to

reverse the data flow through it and have bidirectional communication. In general, the transformers

developed for T1/E1 telecom applications are well suited as the interface element in an galvanically

isolated industrial transmitter. A number of suggested off the shelf transformers are listed in Table 2.

Table 2. Transformers

MANUFACTURER P/N MIN INDUCTANCE (H) ISOLATION

Wurth Elektronik 750315105 400 1500-V AC

Wurth Elektronik 750315155 400 1500-V AC

Coilcraft S5394CLB 400 1500-V AC

4 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com System Description

3.2 MSP430 ULP FRAM Platform

The MSP430 ULP ferroelectric RAM (FRAM) platform is used in the TIDA-00245 reference design. The

MSP430 combines uniquely embedded FRAM and a holistic ULP system architecture, allowing innovators

to increase performance at lowered energy budgets. FRAM is much faster to write to than flash and has

near infinite endurance, which means that in a remote sensor, data could be written more often for

improved data accuracy, or it could collect data for longer. Due to the lack of a charge pump, FRAM

enables lower average and peak power during writes. Writing to FRAM does not require a setup sequence

or additional power when compared to reading from FRAM. The FRAM read current is included in the

active mode current consumption numbers already.

The bitwise programmable memory can be used at the programmers convenience for data or program

storage. It also does not require things like pre-erasure of segments before a write. Security is another

area where FRAM can offer advantages. It is inherently more secure due to its makeup and de-layering is

not effective. FRAM is also resistant to alpha radiation and SER effects. There are two main differences

between FRAM and SRAM:

FRAM is nonvolatile; that is, it retains contents on loss of power.

The embedded FRAM on MSP430 devices can be accessed (read or write) at a maximum speed of 8

MHz.

Incomparison to MSP430 flash, FRAM:

Is very easy to use

Requires no setup or preparation such as unlocking of control registers

Is not segmented and each bit is individually erasable, writable, and addressable

Does not require an erase before a write

Allows low-power write accesses (does not require a charge pump)

Can be written to across the full voltage range (1.8 to 3.6 V)

Can be written to at speeds close to 8MBps (maximum flash write speed including the erase time is

approximately 14 kBps)

Writing to FRAM does not require additional power when compared to reading from FRAM. The FRAM

read current is included in the active mode current consumption numbers already.

Table 3 summarizes the FRAM advantage versus other memory technologies.

Table 3. FRAM Advantages

SPECIFICATION FRAM SRAM FLASH

Write speed per word 125 ns < 125 ns 85 s

No pre-erase

Erase time No pre-erase required 23 ms for 512 bytes

required

Bit-wise programmable Yes Yes No

1015 write per 5

Write endurance N/A 10 write per erase cycle

erase cycle

Nonvolatile Yes No Yes

Internal write voltage 1.5 V 1.5 V 12 to 14 V (charge pump required)

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 5

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Block Diagram www.ti.com

4 Block Diagram

TX/RX RX/TX

COUT/C1

+ C1/COUT +

MUX

C2 VCC/2 Vref0/ MUX

COUT C2 Vref1

COUT

MSP430FR5969

MSP430FR5969

TX TX

eUSCI_A

eUSCI_A

RX RX

Isolation

Figure 2. TIDA-00245 Block Diagram

4.1 Highlighted Products

For the low-power isolated bidirectional data transmission, the COMP_E module and the eUSCI module of

the MSP430FR5969 have been used in this design. For more details regarding the functionality of these

modules, please see MSP430FR58xx, MSP430FR59xx, MSP430FR68xx, and MSP430FR69xx Family

User's Guide [2].

4.1.1 MSP430FR5969

The MSP430 ULP FRAM platform combines uniquely embedded FRAM and a holistic ULP system

architecture, allowing innovators to increase performance at lowered energy budgets. FRAM technology

combines the speed, flexibility, and endurance of SRAM with the stability and reliability of flash at much

lower power.

Features:

Embedded microcontroller

16-bit RISC architecture up to 16-MHz clock

Wide supply voltage range (1.8 to 3.6 V; minimum supply voltage is restricted by SVS levels.)

Optimized ULP modes

Active mode: Approximately 100 A/MHz

Standby (LPM3 with VLO): 0.4 A (typical)

Real-time clock (LPM3.5): 0.25 A (typical; RTC is clocked by a 3.7-pF crystal.)

Shutdown (LPM4.5): 0.02 A (typical)

6 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Block Diagram

ULP FRAM

Up to 64KB of nonvolatile memory

ULP writes

Fast write at 125 ns per word (64KB in 4 ms)

Unified memory = Program + Data + Storage in one single space

1015 write cycle endurance

Radiation resistant and nonmagnetic

Intelligent digital peripherals

32-bit hardware multiplier (MPY)

Three-channel internal DMA

RTC with calendar and alarm functions

Five 16-bit timers with up to seven capture/compare registers each

16-Bit cyclic redundancy checker (CRC)

High-performance analog

16-channel analog comparator

12-bit analog-to-digital converter (ADC) with internal reference and sample-and-hold and up to 16

external input channels

Multifunction I/O ports

All pins support capacitive touch capability with no need for external components

Accessible bit-, byte-, and word-wise (in pairs)

Edge-selectable wake from LPM on all ports

Programmable pullup and pulldown on all ports

Code security and encryption

128-bit or 256-bit AES security encryption and decryption coprocessor

Random number seed for random number generation algorithms

Enhanced serial communication

eUSCI_A0 and eUSCI_A1 support

UART with automatic baud-rate detection

IrDA encode and decode

SPI at rates up to 10 Mbps

eUSCI_B0 supports

I2C with multiple slave addressing

SPI at rates up to 8Mbps

Hardware UART and I2C bootstrap loader (BSL)

Flexible clock system

Fixed-frequency DCO with 10 selectable factory-trimmed frequencies

Low-power low-frequency internal clock source (VLO)

32-kHz crystals (LFXT)

High-frequency crystals (HFXT)

Development tools and software

Free professional development environments with EnergyTrace++ technology development kit

(MSP-TS430RGZ48C)

For complete module descriptions, see the MSP430FR58xx, MSP430FR59xx, MSP430FR68xx, and

MSP430FR69xx Family User's Guide [2].

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 7

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Block Diagram www.ti.com

P1.x, P2.x P3.x, P4.x PJ.x

LFXIN, 2x8 2x8 1x8

LFXOUT,

HFXIN HFXOUT

Capacitive Touch IO 0/1

ADC12_B

I/O Ports I/O Ports I/O Port

MCLK ACLK Comp_E (up to 16 REF_A P1, P2 P3, P4 PJ

Clock standard 2x8 I/Os 2x8 I/Os 1x8 I/Os

System (up to 16 inputs, Voltage

SMCLK inputs) up to 8 Reference PA PB

differential

DMA inputs)

1x16 I/Os 1x16 I/Os

Controller

3 Channel

MAB

Bus

Control MDB

Logic

MAB

CPUXV2

incl. 16

Registers MPU TA2

MDB IP Encap Power AES256

TA3

FRAM RAM Mgmt

Security

CRC16 MPY32 Watchdog Timer_A

LDO Encryption,

EEM 64KB 2KB 2 CC

SVS Decryption

(S: 3 + 1) 48KB 1KB Registers

Brownout (128, 256)

32KB (int. only)

EnergyTrace++

MDB

JTAG

Interface MAB

Spy-Bi-Wire

TB0 TA0 TA1

eUSCI_A0 eUSCI_B0

eUSCI_A1

Timer_B Timer_A Timer_A (I2C, RTC_B

RTC_A

7 CC 3 CC 3 CC (UART, SPI)

Registers Registers Registers IrDA,

(int, ext) (int, ext) (int, ext) SPI)

LPM3.5 Domain

Figure 3. MSP430FR5969 Block Diagram

The MSP430 ULP FRAM portfolio consists of a diverse set of devices featuring FRAM, the ULP 16-bit

MSP430 CPU, and intelligent peripherals targeted for various applications. The COMP_E and the

eUSCI_A modules are used in this application.

The COMP_E module supports precision slope analog-to-digital conversions, supply voltage supervision,

and monitoring of external analog signals.

Features of COMP_E include:

Inverting and non-inverting terminal input multiplexer

Software-selectable RC filter for the comparator output

Output provided to Timer_A capture input

Software control of the port input buffer

Interrupt capability

Selectable reference voltage generator and voltage hysteresis generator

Reference voltage input from shared reference

ULP comparator mode

Interrupt driven measurement system for low-power operation support

8 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Block Diagram

The enhanced universal serial communication interface A (eUSCI_A) supports multiple serial

communication modes with one hardware module. In this design the UART mode is used. UART mode

features include:

7-bit or 8-bit data with odd, even, or non-parity

Independent transmit and receive shift registers

Separate transmit and receive buffer registers

LSB-first or MSB-first data transmit and receive

Built-in idle-line and address-bit communication protocols for multiprocessor systems

Receiver start-edge detection for auto wake up from LPMx modes (wake up from LPMx.5 is not

supported)

Programmable baud rate with modulation for fractional baud-rate support

Status flags for error detection and suppression

Status flags for address detection

Independent interrupt capability for receive, transmit, start bit received, and transmit complete

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 9

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

System Design Theory www.ti.com

5 System Design Theory

5.1 Design Challenges

This design provides a method for transmitting digital data bidirectional over an isolation boundary from

one MCU to another MCU using a single isolation component, a pulse transformer. The use of the

transformers to cross the isolation boundary is typical in industrial applications due to their robustness,

low-power consumption, and low cost. The challenge of such a solution is first of all the limited size within

sensor transmitters (industry standard) and in case of a loop-powered system the overall current

consumption.

5.2 Isolated Data Transmission

For the MCUs, the MSP430FR5969 has been chosen because of its ULP system architecture, integrated

comparator, and integrated UART module, which is used for the isolated data transmission. The UART

square waveform for the data transmission is generated with the eUSCI_A module. The transmitters DC

component is blocked by a capacitor and the transformer passes only the AC components of the UART

square waveform resulting in an impulse train across the secondary winding. The square waveform needs

then to be recovered from the impulse train on the secondary winding. For restoring the signal, the internal

COMP_E of the MSP430FR5969 is used. The COMP_E has a feature to generate a hysteresis for the

output signal, which is used to restore the square waveform from the impulse train. The port pin of the

MSP430 connected to the transmission circuit is P1.1. This pin is multiplexed with several functions like

comparator output COUT and comparator input C1. When the MSP430 is configured as the transceiver,

this pin is configured as COUT, and when the MSP430 is configured as the receiver this pin is configured

as C1. Because the transformer is a symmetrical device (particularly one with 1:1 winding ratio) and the

circuit is symmetrical as well, it is simple to reverse the data flow through it. The block diagram for the

isolated data transmission can be seen in Figure 2.

10 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com System Design Theory

5.2.1 Receiving Data

If the MSP430 is in receiving mode, the P1.1 pin connected to the transmission circuit is configured as

comparator input C1. The comparator output COUT is mapped to a different pin P3.5, which is externally

connected to the UART RX pin (see Figure 4).

TX RX

R2

C2 R4

C1/COUT +

R7 Vref0/ MUX

R8 Vref1

COUT

MSP430FR5969

RX eUSCI_A

Isolation

Figure 4. Receiving Block Diagram

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 11

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

System Design Theory www.ti.com

The internal comparator of the MSP430 has two different reference voltages: Vref0 and Vref1. Vref1 is

used while the output signal COUT of the comparator is 1, and Vref0 is used while COUT is 0. This allows

the generation of a hysteresis without using external components. If the magnitude of the positive impulse

exceeds the threshold Vref0 of the comparator, COUT goes high. This new COUT state will persist until

an opposite polarity impulse appears across the secondary winding and exceeds the threshold Vref1 of

the comparator. COUT will go low and this state will again persist until another positive pulse will occur. If

no data is transmitted and no pulses occur, the voltage on the comparator input will be VCC/2. As Vref0 is

above VCC/2 and Vref1 is below VCC/2 the comparator output COUT will keep its state until a pulse in the

opposite direction occurs. Figure 5 shows the output signal of the comparator depending on the pulses on

the comparator input C1. The output signal of the comparator COUT on the receiver side looks again like

the TX signal on the transmitter side. This COUT signal is then feed into the eUSCI_A module RX pin and

the eUSCI_A module is used to decode the UART protocol.

Figure 5. Comparator Input and Output Signal

12 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com System Design Theory

5.2.2 Transmitting Data

In this circuit, the default VCC level on the connected MCU pin is VCC/2 when no data is transmitted. This is

necessary to have the negative pulses not be going below 0 V as the I/O pins of the MSP430 do not

accept negative voltage. But when voltage levels around VCC/2 are applied to digital CMOS gates,

parasitic current can flow from VCC to GND inside the pin. This parasitic current occurs if the input voltage

is near the transition level of the gate. As the TX pin of the eUSCI module is a digital CMOS gate, it

should not be directly connected to the transmission circuitry as parasitic current would flow from VCC to

GND inside the pin. But on the P1.1/COUT/C1 pin, the port pin buffer can be disabled and this eliminates

the parasitic current flow. Therefore, P1.1/COUT/C1 pin is connected to the transmission circuit. For

transmitting, P1.1 is configured as comparator output COUT and the TX signal of the eUSCI_A module is

connected to the comparator input pin C2 (see Figure 6).The inverting input of the comparator is

connected to VCC/2 as a reference and the comparator output signal COUT then follows directly the TX

signal on pin C2. To transmit data, the eUSCI_A module is used in UART mode. The transmitters DC

component is blocked by a capacitor and only the AC components of the TX square waveform are passed

to the secondary winding of the transformer.

RX TX

COUT/C1

+

MUX

C2 VCC/2

MSP430FR5969

TX

eUSCI_A

Isolation

Figure 6. Transmitting Block Diagram

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 13

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

System Design Theory www.ti.com

When the MSP430FR5969 on one side of the isolation is configured for RX and the other MSP430FR5969

on the other side is configured for TX, data transmission in one direction can be done continuously without

any delay (see Figure 7). The turquoise signal is the transmitted data and the green signal is the received

signal on the other side of the isolation.

Figure 7. Transmitting Data

14 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com System Design Theory

5.2.3 Bidirectional Data Communication

Because the used transformer is a symmetrical device (1:1 winding ratio) and the circuit is symmetrical as

well, data transmission can be done in both directions. The only thing that needs to be considered is to

change the configuration of the MSP430FR5969 pins from transmitting to receiving and vice versa. When

changing from transmitting to receiving the capacitor C1 or respectively C2 has to be first discharged and

the voltage needs to settle at VCC/2 for receiving. This takes less than 10 s and then the transmission can

start again in the other direction (see Figure 8). If the CPU is running with 8 MHz this equates to about 80

CPU cycles. So this time should not be a problem as after receiving the last byte it usually takes much

more CPU cycles until the received byte has been processed and a new transmission gets started. This

idle time needs only be adhered to when changing the communication direction. See the delay in Figure 8.

The blue signal is restored from the turquoise signal on one side of the isolation and the purple signal is

restored from the green signal on the other side of the isolation. The turquoise and the green signals are

the signals on the pins C1/COUT. The blue and the purple signals are the signals on the eUSCI_A RX

input.

Figure 8. Bidirectional Data Communication

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 15

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

System Design Theory www.ti.com

5.2.4 Automated Baud-Rate Detection and Break/Synch Sequence Feature

Automatic baud-rate (ABR) detection feature of the eUSCI module allows matching of baud rates between

the different isolations sides. For ABR detection, a data frame is preceded by a synchronization sequence

that consists of a break and a synch field. A break is detected when 11 or more continuous zeros (spaces)

are received. If the length of the break exceeds 21 bit times, the break timeout error flag UCBTOE is set.

The synch field follows the break as shown in Figure 9.

Break Delimiter Synch

Figure 9. ABR Detection Break/Synch Sequence

The synch field consists of the data 055h inside a byte field (see Figure 10). The synchronization is based

on the time measurement between the first falling edge and the last falling edge of the pattern. The result

of the measurement is transferred into the baud-rate control registers.

Synch

8 Bit Times

Start Stop

0 1 2 3 4 5 6 7

Bit Bit

Figure 10. ABR Detection Synch Field

The break field can be used to detect the beginning of a new frame. The UCDORM bit is used to control

data reception in this mode. When UCDORM is set, all characters are received but not transferred into the

eUSCI receive buffer UCA0RXBUF, and interrupts are not generated. When UCDORM is set, in UART

mode with ABR detection, only the combination of a break and synch field sets the UCRXIFG. When a

break/synch field is detected, the character following the break/synch field is transferred into UCA0RXBUF

and the UCRXIFG interrupt flag is set. When a break/synch field is received, user software must reset

UCDORM to continue receiving data. If UCDORM remains set, only the character after the next reception

of a break/synch field is received. This feature can make the communication really robust in noisy

environments. In addition the MSP430FR5969 includes a hardware CRC module (CRC16). The CRC16

produces a signature based on a sequence of entered data values and can be used for data checking

purposes. The CRC16 module signature is based on the CRC-CCITT standard.

16 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com System Design Theory

Figure 11 shows a scope screenshot of the communication using the ABR Detection and Break/Synch

Sequence feature followed by one data byte.

Figure 11. ABR Detection Break/Synch Sequence Plus One Data Byte

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 17

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Getting Started: Hardware www.ti.com

6 Getting Started: Hardware

6.1 Board Description

Figure 12 shows the different sections of the TIDA-00245 design.

Isolation

barrier

Primary board side Secondary board side

JTAG connector

JTAG connector

MSP430FR5969

Boosterpack J4 J1 Boosterpack

MSP430FR5969 Transformer

Connectors Connectors

J16 J23

J15 J22

J11 J18

Figure 12. TIDA-00245 Board Description

6.2 Hardware Setup

Jumper J11 and jumper J18 can be used for external power supply. The current consumption can be

measured for the primary side on jumper J16 and for the secondary side on jumper J23.

6.2.1 Power During Debugging

If an external power supply is used during debug, make sure pin 2 and pin 3 are connected on jumper J16

and respectively on jumper J22. If there is no external power connected and power from the MSP-FET

Debugger Interface should be used, make sure pin 1 and pin 2 are connected on jumper J16 and

respectively on jumper J22.

6.2.2 Isolation

Jumper J4 and jumper J1 can be used to disconnect the two MSP430FR5969 from the isolation circuitry

and the transformer on the board. Instead the jumpers can be used to connect different isolation circuits

and transformers.

18 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Getting Started: Firmware

7 Getting Started: Firmware

To download the software files for this reference design, please see the link at

http://www.ti.com/tool/TIDA-00245.

7.1 Software Setup

1. Install Code Composer Studio (CCS) before connecting MSP-FET to PC. During CCS installation,

USB drivers are installed automatically. Make sure to use the latest CCS version, otherwise the USB

drivers might not be able to recognize the MSP-FET.

2. Connect the MSP-FET to a USB port on the PC with the provided USB cable.

3. The following procedure applies to operation under Windows:

(a) After connecting to the PC, the MSP-FET should be recognized automatically, as the USB device

driver has been already installed together with the IDE.

(b) If the driver has not been installed yet, the Found New Hardware wizard starts. Follow the

instructions and point the wizard to the driver files.

(c) The default location for CCS is c:\ti\ccsv6\ccs_base\emulation\drivers\msp430\USB_CDC.

4. After connecting to a PC, the MSP-FET performs a self-test. If the self-test passes successfully, the

green LED stays on.

5. If an external power supply is used during debug, make sure pin 2 and pin 3 are connected on jumper

J16 and respectively on jumper J22. If there is no external power connected and power from the MSP-

FET Debugger Interface should be used, make sure pin 1 and pin 2 are connected on jumper J16 and

respectively on jumper J22.

6. Connect the MSP-FET with the 14-conductor cable to one of the JTAG connectors of the TIDA-00245

board.

7. Import the CCS project (TIDA-00245) into CCS and download the firmware to the MSP430FR5969 on

the TIDA-00245 board.

8. Connect the MSP-FET with the 14-conductor cable to the other JTAG connector of the TIDA-00245

board.

9. Download the firmware to the other MSP430FR5969 on the TIDA-00245 board.

7.2 Software Function Documentation

The file swif.c contains the functions for the data transmission.

void initCompE(void)

This function is called to configure the COMP_E

void config_USCIA0_UART(uint16_t div)

This function is called to configure the eUSCIA0 module in UART mode.

void sendByte(uint8_t x)

This function is called to send the break/synch field plus one byte. The parameter x is the byte to send.

The MSP430 stays in TX mode.

void sendByte_RX(uint8_t x)

This function is called to send the break/synch field plus one byte. After transmission is completed the

MSP430 is configured for receive again. The parameter x is the byte to send.

void prepareTX(void)

This function is called to prepare the MSP430 for TX mode.

void prepareRX(void)

This function is called to prepare the MSP430 for RX mode.

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 19

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Getting Started: Firmware www.ti.com

7.3 Demo Software: Bidirectional Communication

The software files can be downloaded at http://www.ti.com/tool/TIDA-00245. The CCS project TIDA-

00245_bidirectional is an example project for bidirectional communication.

Transmission is started on one side with the buttons S1 or S4. The value for the first transmitted byte is

0x00. When the byte has been received on the other side of the isolation, it is echoed back. The value is

then incremented by one and sent again. If the value of the echoed back byte is not the same as the

transmitted byte the red LED goes on. After transmitting 1 kB, the green LED toggles. The transmission

can be stopped with button S1 or S4. The LEDs can be disabled with the buttons S2 and S3 or S5 and S6

for current measurement purposes.

7.4 Demo Software: Unidirectional Communication

The software files can be downloaded at http://www.ti.com/tool/TIDA-00245. The CCS project TIDA-

00245_unidirectional is an example project for unidirectional communication.

Transmission is started on one side with button S1 or S4. The value for the first transmitted byte is 0x00.

The value is then incremented by one and sent again. The receiver checks the received byte and

increments the counter. If the value of the received byte is not equal to the counter the red LED goes on.

After transmitting 1 kB, the green LED toggles. The transmission can be stopped with button S1 or S4.

The LEDs can be disabled with the buttons S2 and S3 or S5 and S6 for current measurement purposes.

20 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Test Results

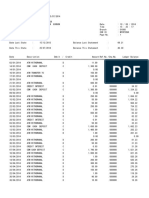

8 Test Results

The current can be measured on jumper J16 and on the other side of the isolation on jumper J23. Table 4

shows the results for the shutdown and the standby current of the complete system.

Table 4. Shutdown and Standby Current

COMPLETE

PARAMETER SPECIFICATION TRANSMITTER RECEIVER UNIT

SYSTEM

System standby and receive ready at 3 V 22 22 44 A

Standby current

System standby and receive ready at 2.2 V 16.5 16.5 33 A

System shutdown current at 3 V 2 2 4 A

Shutdown current

System shutdown current at 2.2 V 1.7 1.7 3.4 A

Figure 13 shows the typical dynamic current consumption of the complete system in unidirectional mode.

Both MSP430FR5969s are active and the CPU is running with 8 MHz. The communication is continuously

running in one direction.

2200

2.2 V

3V

T o ta l S yste m S u p p ly C u rre n t ( A )

2150

2100

2050

2000

1950

1900

1850

0 100 200 300 400 500 600 700 800 900 1000

Data Rate (Kbps)

D001

Figure 13. Total Supply Current in Unidirectional Mode

Figure 14 shows the typical dynamic current consumption of the complete system in bidirectional mode.

Both MSP430FR5969s are active and the CPU is running with 8 MHz. The communication is continuously

running in both directions. One byte is sent and than echoed back from the other side of the isolation.

1850

2.2 V

3V

T o ta l S yste m S u p p ly C u rre n t ( A )

1800

1750

1700

1650

1600

1550

0 100 200 300 400 500 600 700 800 900 1000

Data Rate (Kbps)

D002

Figure 14. Total Supply Current in Bidirectional Mode

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 21

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Design Files www.ti.com

9 Design Files

9.1 Schematics

To download the most recent schematics, see the design files at TIDA-00245.

VCC_iso

U1

1 P1.0/TA0.1/DMAE0/RTCCLK/A0/C0/VREF-/VeREF- AVCC 48

P1.0_iso

2 P1.1/TA0.2/TA1CLK/COUT/A1/C1/VREF+/VeREF+

ISO_RX/TX_iso

3 P1.2/TA1.1/TA0CLK/COUT/A2/C2 DVCC 37

ISO_TX_iso

9 C3 C4 C5 C6

P1.3_iso P1.3/TA1.2/UCB0STE/A3/C3

10 10F 0.1F 10F 0.1F

P1.4_SPI_CS_iso P1.4/TB0.1/UCA0STE/A4/C4

11

P1.5_SPI_CS_iso P1.5/TB0.2/UCA0CLK/A5/C5

31

P1.6_UCB0SIMO_iso P1.6/TB0.3/UCB0SIMO/UCB0SDA/TA0.0

32 P1.7/TB0.4/UCB0SOMI/UCB0SCL/TA1.0

P1.7_UCB0SOMI_iso

24 P2.0/TB0.6/UCA0TXD/UCA0SIMO/TB0CLK/ACLK

ISO_TX_iso

25 P2.1/TB0.0/UCA0RXD/UCA0SOMI/TB0.0

GND_iso

ISO_RX_iso

26

P2.2_UCB0CLK_iso P2.2/TB0.2/UCB0CLK

39

P2.3_iso P2.3/TA0.0/UCA1STE/A6/C10

40 P2.4/TA1.0/UCA1CLK/A7/C11 TEST/SBWTCK 22

P2.4_iso TEST_iso

20 P2.5/TB0.0/UCA1TXD/UCA1SIMO

P2.5_UCA1TXD_iso

21 P2.6/TB0.1/UCA1RXD/UCA1SOMI

P2.6_UCA1RXD_iso

38 P2.7 RST/NMI/SBWTDIO 23

P2.7_iso RST_iso

4 P3.0/A12/C12

P3.0_iso

5 P3.1/A13/C13

P3.1_A13_iso

1 2 6 P3.2/A14/C14

P3.2_A14_iso

S1 7 P3.3/A15/C15

P3.3_A15_iso

27 P3.4/TB0.3/SMCLK

P3.4_iso

1 2 28 P3.5/TB0.4/COUT

ISO_RX_iso

S2 29 P3.6/TB0.5

P3.6_iso

30 P3.7/TB0.6

P3.7_iso

1 2

S3 16 P4.0/A8

P4.0_A8_iso

17 P4.1/A9

P4.1_A9_iso

18 P4.2/A10

GND_iso 19 P4.3/A11

33 P4.4/TB0.5

R9 470 34 P4.5

R10 470 35 P4.6

R11 470 8 P4.7

12 PJ.0/TDO/TB0OUTH/SMCLK/SRSCG1/C6

TDO_iso

13 PJ.1/TDI/TCLK/MCLK/SRSCG0/C7

TDI_iso

14 PJ.2/TMS/ACLK/SROSCOFF/C8 DVSS 36

TMS_iso

C7 15 PJ.3/TCK/SRCPUOFF/C9

TCK_iso

45 PJ.4/LFXIN AVSS 47

2

46 44

2

PJ.5/LFXOUT AVSS

D1 D2 D3 10pF 42 41

PJ.6/HFXIN AVSS

Super Red Green Yellow Y1 43 49

PJ.7/HFXOUT PAD

C8 MS3V-T1R 32.768KHZ +/-20PPM 12.5PF

1

32.768kHz

MSP430FR5969IRGZ

10pF GND_iso

GND_iso GND_iso

SH-J15 SH-J16

J15 J16

VCC_iso

1

2

3

2

1

J9 61300211121

1 2 VCC_TOOL_iso

TDO_iso

VCC_iso J13 +5V_LP_iso J14 3 4 VCC_TARGET_iso

TDI_iso

1 2 1 2 VCC_iso 5 6

TMS_iso

3 4 3 4 7 8

P3.2_A14_iso P1.3_iso TCK_iso TEST_iso

5 6 5 6 9 10

P2.6_UCA1RXD_iso P3.3_A15_iso P3.0_iso

7 8 7 8 GND_iso 11 12 J11

P2.5_UCA1TXD_iso P4.0_A8_iso P2.5_UCA1TXD_iso

9 10 GND_iso 9 10 13 14 1

P2.3_iso P4.1_A9_iso P1.0_iso RST_iso P2.6_UCA1RXD_iso

11 12 11 12 R12 2

P3.1_A13_iso P3.4_iso P1.6_UCB0SIMO_iso

13 14 13 14 47k GND_iso SBH11-PBPC-D07-RA-BK 3

P2.2_UCB0CLK_iso P1.7_UCB0SOMI_iso

15 16 15 16 47k

P2.4_iso P1.5_SPI_CS_iso

17 18 17 18 TSW-103-08-G-S-RA

P3.6_iso P1.4_SPI_CS_iso

19 20 19 20

P3.7_iso P2.7_iso

GND_iso

RST_iso

SSW-110-23-F-D SSW-110-23-F-D

C9

2200pF

GND_iso

Figure 15. TIDA-00245 Schematic Page 1

22 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Design Files

VCC

U2

1 P1.0/TA0.1/DMAE0/RTCCLK/A0/C0/VREF-/VeREF- AVCC 48

P1.0

2 P1.1/TA0.2/TA1CLK/COUT/A1/C1/VREF+/VeREF+

ISO_RX/TX

3 P1.2/TA1.1/TA0CLK/COUT/A2/C2 DVCC 37

ISO_TX

9 C10 C11 C12 C13

P1.3 P1.3/TA1.2/UCB0STE/A3/C3

10 10F 0.1F 10F 0.1F

P1.4_SPI_CS P1.4/TB0.1/UCA0STE/A4/C4

11

P1.5_SPI_CS P1.5/TB0.2/UCA0CLK/A5/C5

31

P1.6_UCB0SIMO P1.6/TB0.3/UCB0SIMO/UCB0SDA/TA0.0

32 P1.7/TB0.4/UCB0SOMI/UCB0SCL/TA1.0

P1.7_UCB0SOMI

24 P2.0/TB0.6/UCA0TXD/UCA0SIMO/TB0CLK/ACLK

ISO_TX

25 P2.1/TB0.0/UCA0RXD/UCA0SOMI/TB0.0

GND

ISO_RX

26

P2.2_UCB0CLK P2.2/TB0.2/UCB0CLK

39 P2.3/TA0.0/UCA1STE/A6/C10

P2.3

40 22

P2.4 P2.4/TA1.0/UCA1CLK/A7/C11 TEST/SBWTCK TEST

20

P2.5_UCA1TXD P2.5/TB0.0/UCA1TXD/UCA1SIMO

21 P2.6/TB0.1/UCA1RXD/UCA1SOMI

P2.6_UCA1RXD

38 P2.7 RST/NMI/SBWTDIO 23

P2.7 RST

4 P3.0/A12/C12

P3.0

5 P3.1/A13/C13

P3.1_A13

1 2 6 P3.2/A14/C14

P3.2_A14

S4 7 P3.3/A15/C15

P3.3_A15

27 P3.4/TB0.3/SMCLK

P3.4

1 2 28 P3.5/TB0.4/COUT

ISO_RX

S5 29 P3.6/TB0.5

P3.6

30 P3.7/TB0.6

P3.7

1 2

S6 16 P4.0/A8

P4.0_A8

17 P4.1/A9

P4.1_A9

18 P4.2/A10

GND 19 P4.3/A11

33 P4.4/TB0.5

R13 470 34 P4.5

R14 470 35 P4.6

R15 470 8 P4.7

12 PJ.0/TDO/TB0OUTH/SMCLK/SRSCG1/C6

TDO

13 PJ.1/TDI/TCLK/MCLK/SRSCG0/C7

TDI

14 PJ.2/TMS/ACLK/SROSCOFF/C8 DVSS 36

TMS

C14 15 PJ.3/TCK/SRCPUOFF/C9

TCK

45 PJ.4/LFXIN AVSS 47

2

46 44

2

PJ.5/LFXOUT AVSS

D4 D5 D6 10pF 42 41

PJ.6/HFXIN AVSS

Super Red Green Yellow Y2 43 49

PJ.7/HFXOUT PAD

C15 MS3V-T1R 32.768KHZ +/-20PPM 12.5PF

1

32.768kHz

MSP430FR5969IRGZ

10pF GND

GND GND

SH-22 SH-J23

J22 J23

VCC

1

2

3

2

1

+5V_LP J10 61300211121

VCC J20 J21 1 2 VCC_TOOL

TDO

1 2 1 2 3 4 VCC_TARGET

TDI

3 4 3 4 VCC 5 6

P3.2_A14 P1.3 TMS

5 6 5 6 7 8

P2.6_UCA1RXD P3.3_A15 P3.0 TCK TEST

7 8 7 8 GND 9 10

P2.5_UCA1TXD P4.0_A8

9 10 GND 9 10 11 12

P2.3 P4.1_A9 P1.0 RST P2.5_UCA1TXD

11 12 11 12 13 14

P3.1_A13 P3.4 P1.6_UCB0SIMO P2.6_UCA1RXD

13 14 13 14 R16

P2.2_UCB0CLK P1.7_UCB0SOMI

15 16 15 16 47k GND SBH11-PBPC-D07-RA-BK

P2.4 P1.5_SPI_CS

17 18 17 18 47k

P3.6 P1.4_SPI_CS

19 20 19 20

P3.7 P2.7

J18

SSW-110-23-F-D SSW-110-23-F-D 1

RST

2

3

C16

2200pF TSW-103-08-G-S-RA

GND

GND

Figure 16. TIDA-00245 Schematic Page 2

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 23

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Design Files www.ti.com

VCC VCC_iso

J7 J8

1 1

61300111121 61300111121

SH-J1 SH-J4

J1 R1 J2 J3 R2 J4

1.0M 1.0M

C1 C2

R3 T1 R4

1

2

1

2

1 6

ISO_RX/TX ISO_RX/TX_iso

61300211121 1.0k 61300111121 61300111121 1.0k 61300211121

220pF 220pF

R5 R6 2 4 R7 R8

1.0M 1.50k 1.50k 1.0M

3

750315155

GND GND_iso

1

J5 GND GND_iso J6

61300111121 61300111121

Figure 17. TIDA-00245 Schematic Page 3

24 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Design Files

9.2 Bill of Materials

To download the most recent bill of materials (BOM), see the design files at TIDA-00245.

Table 5. BOM

PACKAGE

ITEM # DESIGNATOR QTY VALUE PARTNUMBER MANUFACTURER DESCRIPTION

REFERENCE

Printed Circuit

1 !PCB1 1 TIDA-00245 Any

Board

CAP, CERM, 220

2 C1, C2 2 220pF C1608C0G1H221J TDK pF, 50 V, +/- 5%, 0603

C0G/NP0, 0603

CAP, CERM, 10

GRM21BR70J106KE7

3 C3, C5, C10, C12 4 10uF MuRata F, 6.3 V, +/- 0805

6L

10%, X7R, 0805

CAP, CERM, 0.1

GRM155R71A104KA0

4 C4, C6, C11, C13 4 0.1uF MuRata F, 10 V, +/- 0402

1D

10%, X7R, 0402

CAP, CERM, 10

GRM1555C1H100JA01

5 C7, C8, C14, C15 4 10pF MuRata pF, 50 V, +/- 5%, 0402

D

C0G/NP0, 0402

CAP, CERM,

GRM155R70J222KA01 2200 pF, 6.3 V,

6 C9, C16 2 2200pF MuRata 0402

D +/- 10%, X7R,

0402

Super Wurth Elektronik LED, Super Red,

7 D1, D4 2 150060SS75000 LED_0603

Red eiSos SMD

Wurth Elektronik

8 D2, D5 2 Green 150060VS75000 LED, Green, SMD LED_0603

eiSos

Wurth Elektronik LED, Yellow,

9 D3, D6 2 Yellow 150060YS75000 LED_0603

eiSos SMD

Machine Screw,

Round, #4-40 x

10 H1, H2, H3, H4 4 NY PMS 440 0025 PH B&F Fastener Supply Screw

1/4, Nylon, Philips

panhead

Standoff, Hex,

11 H5, H6, H7, H8 4 1902C Keystone Standoff

0.5"L #4-40 Nylon

Header,

Wurth Elektronik Header, 2.54 mm,

12 J1, J4, J16, J23 4 61300211121 2.54mm, 2x1,

eiSos 2x1, Gold, TH

TH

J2, J3, J5, J6, J7, Wurth Elektronik Header, 2.54 mm, Header, 2.54

13 6 61300111121

J8 eiSos 1x1, Gold, TH mm, 1x1, TH

Header Header

SBH11-PBPC-D07-RA- Sullins Connector (Shrouded), 2.54 (Shrouded),

14 J9, J10 2

BK Solutions mm, 7x2, Gold, 2.54 mm, 7x2,

R/A, TH R/A, TH

Header, 100mil,

3x1 R/A

15 J11, J18 2 TSW-103-08-G-S-RA Samtec 3x1, Gold, R/A,

Header

TH

Connector,

J13, J14, J20, Receptacle, 10x2

16 4 SSW-110-23-F-D Samtec

J21 100mil, 10x2, Receptacle

Gold plated, TH

Header,

Wurth Elektronik Header, 2.54 mm,

17 J15, J22 2 61300311121 2.54mm, 3x1,

eiSos 3x1, Gold, TH

TH

RES, 1.0 M, 5%,

18 R1, R2, R5, R8 4 1.0Meg CRCW06031M00JNEA Vishay-Dale 0603

0.1 W, 0603

RES, 1.0 k, 5%,

19 R3, R4 2 1.0k CRCW06031K00JNEA Vishay-Dale 0603

0.1 W, 0603

RES, 1.50 k, 1%,

20 R6, R7 2 1.50k CRCW06031K50FKEA Vishay-Dale 0603

0.1 W, 0603

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 25

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Design Files www.ti.com

Table 5. BOM (continued)

PACKAGE

ITEM # DESIGNATOR QTY VALUE PARTNUMBER MANUFACTURER DESCRIPTION

REFERENCE

R9, R10, R11, RES, 470, 5%,

21 6 470 CRCW0402470RJNED Vishay-Dale 0402

R13, R14, R15 0.063 W, 0402

RES, 47 k, 5%,

22 R12, R16 2 47k CRCW040247K0JNED Vishay-Dale 0402

0.063 W, 0402

S1, S2, S3, S4, Wurth Elektronik Switch, Tactile,

23 6 434121025816 SMD, 6x3.9mm

S5, S6 eiSos SPST, 12 V, SMD

SH-22, SH-J1, Shunt, 100mil,

24 SH-J4, SH-J15, 6 1x2 969102-0000-DA 3M Gold plated, Shunt

SH-J16, SH-J23 Black

Wurth Elektronik Transformer, 400 SMD, Body

25 T1 1 400 uH 750315155

eiSos uH, SMT 8.26x6.6mm

Mixed Signal

26 U1, U2 2 MSP430FR5969IRGZ Texas Instruments Microcontroller, RGZ0048B

RGZ0048B

Crystal,

MS3V-T1R 32.768KHZ 1.4x1.4x5.0mm

27 Y1, Y2 2 Micro Crystal AG 32.768kHz,

+/-20PPM 12.5PF SMD

12.5pF, SMD

Fiducial mark.

28 FID1, FID2, FID3 0 N/A N/A There is nothing N/A

to buy or mount.

26 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Design Files

9.3 PCB Layout Recommendations

The TIDA-00245 board has the form factor of a LaunchPad. A LaunchPad is an easy-to-use

development tool intended for beginners and experienced users alike for creating microcontroller-based

applications. For the LaunchPad, there are BoosterPack plug-in boards available to expand the

LaunchPad's functionality. BoosterPack plug-in modules (www.ti.com/boosterpack) allow the user to add

features like wireless connectivity, capacitive touch, temperature sensing, displays, and much more.

To create a BoosterPack for specific needs, use the resources at

http://www.ti.com/ww/en/launchpad/byob.html to create your BoosterPack design files, get support from

the community, and take an idea from concept to PCB to product in a few easy steps.

9.3.1 Layout Prints

To download the most recent layer plots, see the design files at TIDA-00245.

Figure 18. Top Overlay Figure 19. Top Solder Mask

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 27

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Design Files www.ti.com

Figure 20. Top Layer Figure 21. MidLayer1

Figure 22. MidLayer2 Figure 23. Bottom Layer

28 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Design Files

Figure 24. Bottom Solder Mask Figure 25. Bottom Overlay

Figure 26. Drill Drawing Figure 27. Board Dimensions

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 29

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Design Files www.ti.com

9.4 Altium Project

To download the most recent Altium project files, see the design files at TIDA-00245.

Figure 28. Multilayer Composite Print

30 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

www.ti.com Design Files

9.5 Gerber Files

To download the most recent Gerber files, see the design files at TIDA-00245.

Figure 29. Fabrication Drawing

TIDU804 March 2015 Data Isolation for Loop-Powered Applications 31

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

Design Files www.ti.com

9.6 Assembly Drawings

To download the most recent assembly drawings, see the design files at TIDA-00245.

Figure 30. Top Assembly Drawing Figure 31. Bottom Assembly Drawing

9.7 Software Files

To download the most recent software files, see the design files at TIDA-00245.

10 References

1. Texas Instruments, MSP430FR59xx Mixed-Signal Microcontrollers (SLAS704)

2. Texas Instruments, MSP430FR58xx, MSP430FR59xx, MSP430FR68xx, and MSP430FR69xx Family

User's Guide (SLAU367)

3. Texas Instruments, Maximizing Write Speed on the MSP430 FRAM (SLAA498)

4. Texas Instruments, MSP430 FRAM Technology How To and Best Practices (SLAA628)

11 About the Author

THOMAS SCHNEIDER is a systems applications engineer at Texas Instruments where he is responsible

for developing reference design solutions for the industrial segment. Thomas brings to this role his wide

experience in TI microcontrollers, especially MSP430. Thomas earned his Dipl.-Ing. (Univ.) degree in

electrical engineering from the Technical University Munich (TUM) in Munich, Germany.

32 Data Isolation for Loop-Powered Applications TIDU804 March 2015

Submit Documentation Feedback

Copyright 2015, Texas Instruments Incorporated

IMPORTANT NOTICE FOR TI REFERENCE DESIGNS

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers (Buyers) who are developing systems that

incorporate TI semiconductor products (also referred to herein as components). Buyer understands and agrees that Buyer remains

responsible for using its independent analysis, evaluation and judgment in designing Buyers systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. TI has not conducted any

testing other than that specifically described in the published documentation for a particular reference design. TI may make

corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the

reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL

OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY

OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right,

or other intellectual property right relating to any combination, machine, or process in which TI components or services are used.

Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE

REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR

COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY

INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE

FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO

OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE

LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY

THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN

ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYERS USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per

JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant

information before placing orders and should verify that such information is current and complete. All semiconductor products are sold

subject to TIs terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TIs terms

and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI

deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not

necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers products. Buyers are responsible for their products and

applications using TI components. To minimize the risks associated with Buyers products and applications, Buyers should provide

adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is

without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for

such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements

concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support

that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that

anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate

remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in

Buyers safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TIs goal is to

help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and

requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties

have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or enhanced plastic are designed and intended for use in

military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that

have not been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory

requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of

non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.IMPORTANT NOTICE

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright 2015, Texas Instruments Incorporated

You might also like

- Tidue 64Document31 pagesTidue 64Arun GuptaNo ratings yet

- Data Concentrator Cape For Beaglebone Black: Ti DesignsDocument39 pagesData Concentrator Cape For Beaglebone Black: Ti Designsrazila rasheedNo ratings yet

- Lm317 3-Terminal Adjustable Regulator: 1 Feateeures 3 DescriptionDocument32 pagesLm317 3-Terminal Adjustable Regulator: 1 Feateeures 3 DescriptiontheserviceNo ratings yet

- Datasheet 2Document23 pagesDatasheet 2iman86zNo ratings yet

- LM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionDocument33 pagesLM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionAlberto DanNo ratings yet

- LM317 3-Terminal Adjustable Regulator (RevDocument33 pagesLM317 3-Terminal Adjustable Regulator (RevluisNo ratings yet

- LM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionDocument32 pagesLM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionCalon SuspendNo ratings yet

- LM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionDocument32 pagesLM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionIrham NurNo ratings yet

- 12V To 24V, 27A Brushed DC Motor Reference Design: TI DesignsDocument55 pages12V To 24V, 27A Brushed DC Motor Reference Design: TI DesignsMarc DonaldNo ratings yet

- LM 317Document31 pagesLM 317Ramiro MezaNo ratings yet

- Tmux 1247Document31 pagesTmux 1247waqasasad408No ratings yet

- DP83822 Robust, Low Power 10/100 Mbps Ethernet Physical Layer TransceiverDocument110 pagesDP83822 Robust, Low Power 10/100 Mbps Ethernet Physical Layer TransceiverKattie ValerioNo ratings yet

- LM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionDocument32 pagesLM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionHappy TourisiantoNo ratings yet

- TMUX1208 5-V Bidirectional 8:1, 1-Channel Multiplexer: 1 Features 3 DescriptionDocument33 pagesTMUX1208 5-V Bidirectional 8:1, 1-Channel Multiplexer: 1 Features 3 Descriptionkishore_bulli6666No ratings yet

- KSZ8061 PDFDocument64 pagesKSZ8061 PDFsaberNo ratings yet

- LAN8740ADocument136 pagesLAN8740AJaviCuellorNo ratings yet

- Temperature Transmitter On Single Chip Mixed-Signal MCU: TI DesignsDocument31 pagesTemperature Transmitter On Single Chip Mixed-Signal MCU: TI DesignsMilan ĐorđevicNo ratings yet

- Tiducv 9Document24 pagesTiducv 9zizouhicheNo ratings yet

- Ethernet Physical Layer Transceiver - TI DP83825IDocument78 pagesEthernet Physical Layer Transceiver - TI DP83825ItungNo ratings yet

- Tiduay6e PDFDocument50 pagesTiduay6e PDFLeo SilvaNo ratings yet

- ESP32-S2-WROVER & ESP32-S2-WROVER-I: DatasheetDocument26 pagesESP32-S2-WROVER & ESP32-S2-WROVER-I: DatasheetWesllen Dias SouzaNo ratings yet

- Ts 5 MP 646Document36 pagesTs 5 MP 646hakapaarNo ratings yet

- Esp32 s2 Wroom - Esp32 s2 Wroom I - Datasheet - en PDFDocument27 pagesEsp32 s2 Wroom - Esp32 s2 Wroom I - Datasheet - en PDFViki YusdiantoNo ratings yet

- McGraw-Edison VPL Valet LEDDocument4 pagesMcGraw-Edison VPL Valet LEDneuvoNo ratings yet

- MD22 Line-EDS-PS M61065 ENDocument4 pagesMD22 Line-EDS-PS M61065 ENfaikNo ratings yet

- LM 317Document31 pagesLM 317h125954445No ratings yet

- LM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionDocument31 pagesLM317 3-Terminal Adjustable Regulator: 1 Features 3 DescriptionDi ZhangNo ratings yet

- LM 317Document30 pagesLM 317Cristian BelliazziNo ratings yet

- A6V11420333 enDocument5 pagesA6V11420333 enmarklmendozaNo ratings yet

- Lm317 3-Terminal Adjustable Regulator: 1 Feateeures 3 DescriptionDocument32 pagesLm317 3-Terminal Adjustable Regulator: 1 Feateeures 3 DescriptiontheserviceNo ratings yet

- A True System-On-Chip Solution For 2.4-Ghz Ieee 802.15.4 and Zigbee ApplicationsDocument36 pagesA True System-On-Chip Solution For 2.4-Ghz Ieee 802.15.4 and Zigbee Applicationsminhtutran1983No ratings yet

- LM 317Document32 pagesLM 317theserviceNo ratings yet

- ESP32-WROOM-32E - UE - Datasheet v1.2Document35 pagesESP32-WROOM-32E - UE - Datasheet v1.2StefanoViganóNo ratings yet

- Tidudk 5 ADocument36 pagesTidudk 5 ASowhat SowhatNo ratings yet

- Cc3100 Simplelink™ Wi-Fi Network Processor, Internet-Of-Things Solution For Mcu ApplicationsDocument42 pagesCc3100 Simplelink™ Wi-Fi Network Processor, Internet-Of-Things Solution For Mcu ApplicationsyandexNo ratings yet

- 103 - Tidu449bDocument92 pages103 - Tidu449bMahdi TavassoliNo ratings yet

- ESP32-S2-MINI-1 & ESP32-S2-MINI-1U: DatasheetDocument29 pagesESP32-S2-MINI-1 & ESP32-S2-MINI-1U: DatasheetYurii VovchenkoNo ratings yet

- Esp32 s2 Wrover - Esp32 s2 Wrover I - Datasheet - enDocument26 pagesEsp32 s2 Wrover - Esp32 s2 Wrover I - Datasheet - encesarNo ratings yet

- THVD 1400Document33 pagesTHVD 1400victorvpaiva07No ratings yet

- EN29LV040ADocument35 pagesEN29LV040AteddystoNo ratings yet

- CC 2540Document34 pagesCC 2540oZk4hNo ratings yet

- dp83848q q1Document83 pagesdp83848q q1Marius IoacaraNo ratings yet

- SEL-2240 Axion: Modular Real-Time Automation ControllerDocument16 pagesSEL-2240 Axion: Modular Real-Time Automation ControllerJulian Pineda100% (1)

- EY-RC 500: Room Automation Station, Ecos500: FeaturesDocument14 pagesEY-RC 500: Room Automation Station, Ecos500: FeaturesRhizhailNo ratings yet

- 54-V, 1.5 KW, 99% Efficient, 70x69 MM Power Stage Reference Design For 3-Phase BLDC DrivesDocument37 pages54-V, 1.5 KW, 99% Efficient, 70x69 MM Power Stage Reference Design For 3-Phase BLDC DrivesMohaned Kamal HassanNo ratings yet

- Tps 65218 D 0Document112 pagesTps 65218 D 0carlos huenupanNo ratings yet

- Max 3243Document29 pagesMax 3243alephzeroNo ratings yet

- KSZ8841 16M 32M Single Port Ethernet MAC Controller With Non PCI Interface DS00003147ADocument98 pagesKSZ8841 16M 32M Single Port Ethernet MAC Controller With Non PCI Interface DS00003147AMarcos Roberto da SilvaNo ratings yet

- DS Lan8742 00001989a PDFDocument124 pagesDS Lan8742 00001989a PDFpiyushpandeyNo ratings yet

- Voltage Source Inverter - Grid - TexasDocument50 pagesVoltage Source Inverter - Grid - TexasirfanNo ratings yet

- MSP430F22x2 Automotive Mixed-Signal Microcontrollers: 1 FeaturesDocument78 pagesMSP430F22x2 Automotive Mixed-Signal Microcontrollers: 1 FeaturesMiljenko PolićNo ratings yet

- DP83848C PDFDocument84 pagesDP83848C PDFpriyosantosaNo ratings yet

- LAN8700/LAN8700 IDocument74 pagesLAN8700/LAN8700 Ivaibhav savajadiyaNo ratings yet

- Max3232 PDFDocument27 pagesMax3232 PDFpiyushpandeyNo ratings yet

- MAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver/Receiver With 15-kV ESD ProtectionDocument29 pagesMAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver/Receiver With 15-kV ESD ProtectionBechir BrahmiNo ratings yet

- MAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver/Receiver With 15-kV ESD ProtectionDocument31 pagesMAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver/Receiver With 15-kV ESD Protectionsuperpuma86No ratings yet

- 8-Channel Digital Input Module For Programmable Logic Controllers (PLCS)Document26 pages8-Channel Digital Input Module For Programmable Logic Controllers (PLCS)adaptive4u4527No ratings yet

- Tidua10a Ultrasonic Water Flow Measurement Design Guide Using MSP430FR6972Document13 pagesTidua10a Ultrasonic Water Flow Measurement Design Guide Using MSP430FR6972A N ArunkumarNo ratings yet

- Wi.232Dts User'S Manual: U.S 902-928Mhz Ism Band VersionDocument27 pagesWi.232Dts User'S Manual: U.S 902-928Mhz Ism Band VersionapnegraoNo ratings yet

- Practical Data Acquisition for Instrumentation and Control SystemsFrom EverandPractical Data Acquisition for Instrumentation and Control SystemsNo ratings yet

- Inverting vs. Noninverting - VAZNODocument12 pagesInverting vs. Noninverting - VAZNOMilan ĐorđevicNo ratings yet

- RF & Microwave Design Guide - Sierra Circuits - November 2021Document44 pagesRF & Microwave Design Guide - Sierra Circuits - November 2021Milan Đorđevic100% (1)

- Input Bias Current Cancelation Resistors-Uticaj Bias CurrentDocument3 pagesInput Bias Current Cancelation Resistors-Uticaj Bias CurrentMilan ĐorđevicNo ratings yet

- ETH EkstraDocument42 pagesETH EkstraMilan ĐorđevicNo ratings yet

- dn015f NOISEDocument2 pagesdn015f NOISEMilan ĐorđevicNo ratings yet

- Temperature Transmitter On Single Chip Mixed-Signal MCU: TI DesignsDocument31 pagesTemperature Transmitter On Single Chip Mixed-Signal MCU: TI DesignsMilan ĐorđevicNo ratings yet

- AC/DC Converter: FeaturesDocument4 pagesAC/DC Converter: FeaturesMilan ĐorđevicNo ratings yet

- 3-Wire RTD Measurement System Reference Design, - 200°C To 850°CDocument39 pages3-Wire RTD Measurement System Reference Design, - 200°C To 850°CMilan ĐorđevicNo ratings yet

- Design Tips For A Resistive-Bridge Pressure Sensor in Industrial Process-Control SystemsDocument7 pagesDesign Tips For A Resistive-Bridge Pressure Sensor in Industrial Process-Control SystemsMilan ĐorđevicNo ratings yet

- 1ACOS - S Ima Da Se Nadju 1wDocument4 pages1ACOS - S Ima Da Se Nadju 1wMilan ĐorđevicNo ratings yet

- Voltage Output Programmable Sensor Conditioner: Features DescriptionDocument25 pagesVoltage Output Programmable Sensor Conditioner: Features DescriptionMilan ĐorđevicNo ratings yet

- Searaq I/O Modules: User ManualDocument59 pagesSearaq I/O Modules: User ManualMilan ĐorđevicNo ratings yet

- Christian AnderssonDocument55 pagesChristian Anderssonmarconi-agNo ratings yet

- XC6204/XC6205: General DescriptionDocument51 pagesXC6204/XC6205: General DescriptionMilan ĐorđevicNo ratings yet

- PSSI2021SAY: 1. Product ProfileDocument12 pagesPSSI2021SAY: 1. Product ProfileMilan ĐorđevicNo ratings yet

- CN0376Document7 pagesCN0376Milan ĐorđevicNo ratings yet

- C Sharp Logical TestDocument6 pagesC Sharp Logical TestBogor0251No ratings yet

- Leeka Kheifets PrincipleDocument6 pagesLeeka Kheifets PrincipleAlexandreau del FierroNo ratings yet

- SemiDocument252 pagesSemiGNo ratings yet

- Home Guaranty Corp. v. Manlapaz - PunzalanDocument3 pagesHome Guaranty Corp. v. Manlapaz - PunzalanPrincess Aliyah Punzalan100% (1)

- BMT6138 Advanced Selling and Negotiation Skills: Digital Assignment-1Document9 pagesBMT6138 Advanced Selling and Negotiation Skills: Digital Assignment-1Siva MohanNo ratings yet

- Principles of SOADocument36 pagesPrinciples of SOANgoc LeNo ratings yet

- Liga NG Mga Barangay: Resolution No. 30Document2 pagesLiga NG Mga Barangay: Resolution No. 30Rey PerezNo ratings yet

- Bismillah SpeechDocument2 pagesBismillah SpeechanggiNo ratings yet

- 1980WB58Document167 pages1980WB58AKSNo ratings yet

- Ethercombing Independent Security EvaluatorsDocument12 pagesEthercombing Independent Security EvaluatorsangelNo ratings yet

- Interest Rates and Bond Valuation: All Rights ReservedDocument22 pagesInterest Rates and Bond Valuation: All Rights ReservedAnonymous f7wV1lQKRNo ratings yet

- Introduction Into Post Go-Live SizingsDocument26 pagesIntroduction Into Post Go-Live SizingsCiao BentosoNo ratings yet

- Sun Nuclear 3D SCANNERDocument7 pagesSun Nuclear 3D SCANNERFranco OrlandoNo ratings yet

- Mounting BearingDocument4 pagesMounting Bearingoka100% (1)

- Ramp Footing "RF" Wall Footing-1 Detail: Blow-Up Detail "B"Document2 pagesRamp Footing "RF" Wall Footing-1 Detail: Blow-Up Detail "B"Genevieve GayosoNo ratings yet

- Terms and Conditions 27 06 PDFDocument4 pagesTerms and Conditions 27 06 PDFShreyash NaikwadiNo ratings yet

- RCC Design of Toe-Slab: Input DataDocument2 pagesRCC Design of Toe-Slab: Input DataAnkitaNo ratings yet

- WHO Partograph Study Lancet 1994Document6 pagesWHO Partograph Study Lancet 1994Dewi PradnyaNo ratings yet

- Alternator: From Wikipedia, The Free EncyclopediaDocument8 pagesAlternator: From Wikipedia, The Free EncyclopediaAsif Al FaisalNo ratings yet

- Insurance Smart Sampoorna RakshaDocument10 pagesInsurance Smart Sampoorna RakshaRISHAB CHETRINo ratings yet

- La Salle Lipa Integrated School Senior High School Community 1 Quarter Summative Assessment Earth Science AY 2021-2022 Household Conservation PlanDocument4 pagesLa Salle Lipa Integrated School Senior High School Community 1 Quarter Summative Assessment Earth Science AY 2021-2022 Household Conservation PlanKarlle ObviarNo ratings yet

- Circuitos Digitales III: #IncludeDocument2 pagesCircuitos Digitales III: #IncludeCristiamNo ratings yet

- ACM2002D (Display 20x2)Document12 pagesACM2002D (Display 20x2)Marcelo ArtolaNo ratings yet

- Nat Law 2 - CasesDocument12 pagesNat Law 2 - CasesLylo BesaresNo ratings yet

- Salem Telephone CompanyDocument4 pagesSalem Telephone Company202211021 imtnagNo ratings yet

- Starkville Dispatch Eedition 12-9-18Document28 pagesStarkville Dispatch Eedition 12-9-18The DispatchNo ratings yet

- List of People in Playboy 1953Document57 pagesList of People in Playboy 1953Paulo Prado De Medeiros100% (1)

- Bank Statement SampleDocument6 pagesBank Statement SampleRovern Keith Oro CuencaNo ratings yet

- Canopy CountersuitDocument12 pagesCanopy CountersuitJohn ArchibaldNo ratings yet

- Toa Valix Vol 1Document451 pagesToa Valix Vol 1Joseph Andrei BunadoNo ratings yet