Professional Documents

Culture Documents

Electronics MCQ

Uploaded by

Hary KrizOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electronics MCQ

Uploaded by

Hary KrizCopyright:

Available Formats

CERTC-ECE PRE-BOARD EXAM 2 ELEX

Instruction: Select the correct answer for each of the following C. negative voltage operation, high speed, and high power

questions. Mark only one answer for each item by shading the box consumption *

corresponding to the letter of your choice on the answer sheet provided. D. poor noise immunity, positive supply voltage operation, good low-

frequency operation, and low power

1. Which of the following memories uses a MOSFET and a capacitor as

its memory cell? 14. When an IC has two rows of parallel connecting pins, the device is

A. DRAM * C. DROM referred to as:

B. SRAM D. ROM A. CMOS C. a DIP *

B. a phase splitter D. a QFP

2. Which of the following is not a basic element within the

microprocessor? 15. A digital logic device used as a buffer should have what input/output

A. Microcontroller * C. Register array characteristics?

B. Arithmetic logic unit D. Control unit A. low input impedance and low output impedance

B. low input impedance and high output impedance

3. Which of the following best describes a fusible-link PROM? C. high input impedance and high output impedance

A. user programmable, reprogrammable D. high input impedance and low output impedance *

B. manufacturer programmable, one-time programmable

C. user programmable, one-time programmable * 16. A TTL totem pole circuit is designed so that the output transistors

D. manufacturer programmable, reprogrammable are:

A. providing phase splitting

4. How do we define the resolution of a digital-to-analog converter B. providing voltage regulation

(DAC)? C. always on together

A. It is the deviation between the ideal straight-line output and the D. never on together *

actual output of the converter.

B. It is its ability to resolve between forward and reverse steps when 17. If a signal passing through a gate is inhibited by sending a low into

sequenced over its entire range. one of the inputs, and the output is HIGH, the gate is a(n):

C. It is the comparison between the actual output of the converter and A. AND C. OR

its expected output. B. NOR D. NAND *

D. It is the smallest analog output change that can occur as a result

of an increment in the digital input. * 18. Exclusive-OR (XOR) logic gates can be constructed from what other

logic gates?

5. What is the purpose of the fast carry or look-ahead carry circuits A. OR gates only

found in most 4-bit parallel-adder? B. AND gates, OR gates, and NOT gates *

A. add a 1 to complemented inputs C. OR gates and NOT gates

B. determine sign and magnitude D. AND gates and NOT gates

C. increase ripple delay

D. reduce propagation delay * 19. Which of the following best describe the operation of a TRIAC?

A. can trigger only on negative gate voltages

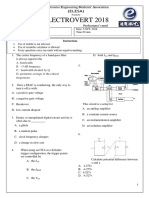

6. What type of register would shift a complete binary number in one bit B. can be triggered by either a positive or a negative gate voltage *

at a time and shift all the stored bits out one bit at a time? C. cannot be triggered with gate voltages

A. PIPO C. SIPO D. can trigger only on positive gate voltages

B. SISO * D. PISO

20. Which of the following is the best description of a read-only memory

7. The propagation delay of which of the following limits the speed of a (ROM).

ripple counter? A. nonvolatile, used to store information that does not change during

A. each flip-flop * system operation *

B. only circuit gates B. nonvolatile, used to store information that changes during system

C. all flip-flops and gates operation

D. the flip-flops only with gates C. volatile, used to store information that changes during system

operation

8. The truth table for an S-R flip-flop has how many VALID entries? D. volatile, used to store information that does not change during

A. 4 C. 3 * system operation

B. 1 D. 2

21. What is the primary disadvantage of the flash analog-to digital

9. It is defined as the time needed for a pulse to increase from 10% to converter (ADC)?

90% of its amplitude. A. it requires the input voltage to be applied to the inputs

A. propagation delay C. rise time * simultaneously

B. pulse width D. duty cycle B. a large number of output lines is required to simultaneously

decode the input voltage

10. What is the next step after discovering a faulty gate within an IC? C. a large number of comparators is required to represent a

A. replace the IC involved * reasonable sized binary number *

B. recheck the power source D. a long conversion time is required

C. resolder the tracks

D. repair the gate 22. When checking a good SCR or TRIAC with an ohmmeter it will:

A. show high resistance in both directions *

11. Once a DIAC is conducting, the only way to turn it off is with B. show low resistance in both directions

A. a positive gate voltage C. show low resistance with positive on anode and negative on

B. a negative gate voltage cathode, and high resistance when reversed

C. breakover D. show high resistance with negative on anode and positive on

D. low-current dropout cathode, and low resistance when reversed

12. What is the difference between a PLA and a PAL? 23. How do you define IDSS?

A. PALs and PLAs are the same thing. A. the maximum possible current with VGS held at 4 V

B. the PLA has a programmable OR plane and a programmable AND B. the maximum drain current with the source shorted

plane, while the PAL only has a programmable AND plane * C. the maximum possible current with VGS held at 0 V *

C. the PAL has a programmable OR plane and a programmable AND D. the minimum possible drain current

plane, while the PLA only has a programmable AND plane

D. the PAL has more possible product terms than the PLA 24. What does a voltage-divider bias provide?

A. an unstable Q point

13. Which of the following summarizes the important features of emitter- B. a stable Q point *

coupled logic (ECL)? C. a Q point that is stable and easily varies with changes in the

A. good noise immunity, negative logic, high frequency capability, low transistors current gain

power dissipation, and short propagation time D. a Q point that easily varies with changes in the transistor's current

B. slow propagation time, high frequency response, low power gain

consumption, and high output voltage swings

CERTC-ECE: MANILA-CEBU-BAGUIO-DAVAO-ILO-ILO (0932-175-1218) Page 1

CERTC-ECE PRE-BOARD EXAM 2 ELEX

25. The change in value of an analog signal during the conversion 39. Which statement best describes input offset voltage?

process produces what is called the A. an error voltage produced by an op-amp

A. resolution error C. Nyquist error B. the voltage required to compensate for an error output voltage of

B. sampling error D. quantization error * an op-amp *

C. the desired output voltage of an op-amp circuit

26. Power (brightness) of a 100W, 110 V tungsten lamp is to be varied D. the average input voltage of both inputs of an op-amp

by controlling the firing angle of an SCR in a half-wave rectifier circuit

supplied with 110 V AC. What rms voltage is developed in the lamp 40. Suppose the apparent power in a circuit is 100 W, and the imaginary

at firing angle = 60? power is 40 W. What is the true power?

A. 96.3 V C. 98.9 V * A. 92 W * C. 140 W

B. 95.5 V D. 97.2 V B. 100 W D. 108 W

27. In the classic three-op-amp instrumentation amplifier, the differential 41. Which of the following is not a computer functional block?

voltage gain is usually produced by the A. Analog-to-digital converter C. Memory

A. output op-amp C. first stage * B. Central-processing unit D. Input/output ports

B. second stage D. mismatched resistors

42. The first Intel microprocessor to contain on-board cache memory was

28. What is the principal advantage of using address multiplexing with the ________.

DRAM memory? A. 80386 C. Pentium

A. reduced pin count and decrease in package size * B. 80486 * D. Pentium Pro

B. reduced requirement for constant refreshing of the memory

contents 43. A full-wave half-controlled bridge has a supply voltage of 220V at

C. reduced memory access time 50Hz. The firing angle delay = 90. Determine the values of the

D. no requirement for a chip-select input line, thereby reducing the rms current for a resistive load of R = 100 .

pin count A. 0.725 A C. 1.225 A

B. 0.990 A D. 1.556 A *

29. If the value of resistor Rf in an averaging amplifier circuit is equal to

the value of one input resistor divided by the number of inputs, the 44. The Pentium microprocessor has a data bus of ________.

output will be equal to A. 16 bits C. 64 bits *

A. the inverted sum of the individual inputs B. 32 bits D. 128 bits

B. the sum of the individual inputs

C. the inverted average of the individual inputs * 45. Which is not part of the execution unit (EU)?

D. the average of the individual inputs A. Arithmetic logic unit (ALU) C. General registers

B. Clock * D. Flags

30. A silicon PN junction is forward biased with a constant current at

room temperature. When the temperature is increased by 10C, the 46. Sample-and-hold circuits in analog-to digital converters (ADCs) are

forward bias voltage across the PN junction designed to:

A. increases by 60mV C. increases by 25mV A. stabilize the input analog signal during the conversion process *

B. decreases by 60mV D. decreases by 25mV * B. stabilize the comparator's threshold voltage during the conversion

process

31. An 8085 microprocessor based system uses a 4k x 8 bit RAM whose C. sample and hold the output of the binary counter during the

starting address is AA00 H. The address of the last byte in this RAM conversion process

is D. sample and hold the D/A converter staircase waveform during the

A. 0FFF H C. B9FF H conversion process

B. 1000 H D. BA00 H *

47. Which is not an operand?

32. A step up chopper has input voltage 110 V and output voltage 150 V. A. Variable C. Memory location

What is the value of the duty cycle? B. Register D. Assembler *

A. 0.32 C. 0.45

B. 0.67 * D. none of these 48. A step-up chopper is to provide a 48V across a 12 ohms load from a

12V DC supply. The chopper inductance is 10tzH and the chopper

33. Thermocouple work on which of the following effects? frequency is 100 kHz. Determine the duty cycle required.

A. Thomson effect C. Peltier effect A. 0.50 C. 0.55

B. Seebeck effect * D. Joule effect B. 0.75 * D. 0.85

34. A JFET might work better than a bipolar transistor in 49. The phenomenon known as Early Effect in a bipolar transistor

A. a high-voltage rectifier refers to a reduction of the effective base-width caused by which of

B. a weak-signal RF amplifier * the following?

C. a power-supply filter A. Electron-hole recombination at the base

D. a power transformer B. The reverse biasing of the base-collector junction *

C. The forward biasing of emitter-base junction

35. The first microprocessor had a(n)________. D. the early removal of stored base charge during saturation-to-cut

A. 1-bit data bus C. 4-bit data bus * off switching.

B. 2-bit data bus D. 8-bit data bus

50. With interrupt-driven I/O, if two or more devices request service at

36. An SCR full-wave rectifier supplies to a load of 100 . If the peak AC the same time, ________.

voltage between center tap and one end of secondary is 200V, find A. the device closest to the CPU gets priority

the DC output voltage for a firing angle of 60. B. the device that is fastest gets priority

A. 96.3 V C. 98.9 V C. the device assigned the highest priority is serviced first *

B. 95.5 V * D. 97.2 V D. the system is likely to crash

37. Which of the following is a type of error associated with digital-to- 51. Which method bypasses the CPU for certain types of data transfer?

analog converters (DACs)? A. Software interrupts

A. nonmonotonic error B. Interrupt-driven I/O

B. incorrect output codes C. Polled I/O

C. nonmonotonic and offset error * D. Direct memory access (DMA) *

D. offset error

52. If the differential voltage gain and the common mode voltage gain of

38. Which of the following would cause an op-amp circuit to severely clip a differential amplifier are 48 dB and 2 dB respectively, what is the

the signal? common mode rejection ratio?

A. open input resistance (Ri) A. 23 dB C. 46 dB *

B. op-amp open internally B. 25 dB D. 50 dB

C. shorted input resistance (Ri)

D. open feedback resistance (Rf) * 53. In a transistor amplifier, the reverse saturation current I CO

A. double for every 10 rise in temperature *

CERTC-ECE: MANILA-CEBU-BAGUIO-DAVAO-ILO-ILO (0932-175-1218) Page 2

CERTC-ECE PRE-BOARD EXAM 2 ELEX

B. doubles for every 1 rise in temperature

C. increase linearly with the temperature 63. One input terminal of a high gain comparator circuit is connected to

D. doubles for every 5 rise in temperature ground and a sinusoidal voltage is applied to the other input. What

will be the output of the comparator?

54. Suppose an AC ammeter and an AC voltmeter indicate that there are A. a sinusoid C. a half rectified sinusoid

220 W of VA power in a circuit that consists of a resistance of 50 in B. a full rectified sinusoid D. a square wave

series with a capacitive reactance of 20 . What is the true power? *

A. 237 W C. 88.0 W 64. A DC generator is producing 24 V while operating at 1200 rpm with a

B. 204 W * D. 81.6 W magnetic flux of 0.02 Wb. The same generator is operated at 1000

rpm with a magnetic flux of 0.05 Wb. What is most nearly the new

55. The amplifier circuit shown below uses a silicon transistor. The voltage the generator produces?

capacitors CC and CE can be assumed to be short at signal A. 20 V C. 60 V

frequency and the effect of output resistance r O can be ignored. If CE B. 50 V * D. 100 V

is disconnected from the circuit, which one of the following

statements is TRUE? 65. Which bus is bidirectional?

A. Address bus C. Data bus *

B. Control bus D. None of the above

66. A DC voltage source is connected across a series R-L-C circuit.

Under steady state conditions, the applied DC voltage drops entirely

across the

A. R only C. C only *

B. L only D. R and L combination

67. Which of the following is not a jump instruction?

A. JB (jump back) *

B. JA (jump above)

C. JO (jump if overflow)

A. The input resistance Ri increases and the magnitude of voltage D. JMP (unconditional jump)

gain AV decreases. *

B. The input resistance Ri decreases and the magnitude of voltage 68. The upper cutoff frequency of an RC coupled amplifier mainly

gain AV increases. depends upon

C. Both input resistance Ri and the magnitude of voltage gain AV A. Coupling Capacitor

decrease. B. Emitter bypass capacitor

D. Both input resistance Ri and the magnitude of voltage gain AV C. Output capacitance of signal source

increase. D. Inter-electrode capacitance and stray shunt capacitance *

56. Which of the following is not an essential element of a dc power 69. Which of the following is not an 8086/8088 general-purpose register?

supply? A. Code segment (CS) C. Stack segment (SS)

A. Rectifier C. Voltage regulator B. Data segment (DS) D. Address segment (AS) *

B. Filter D. Voltage amplifier *

70. The type of power amplifier which exhibits crossover distortion in its

57. A 20-bit address bus can locate ________. output is

A. 1,048,576 locations * C. 4,194,304 locations A. Class A C. Class AB

B. 2,097,152 locations D. 8,388,608 locations B. Class B * D. Class C

58. What will happen to the Zener current if the load resistance 71. Which of the following is not an enhancement to the Pentium that

increases in a Zener regulator? was unavailable in the 8086/8088?

A. Decreases A. "Pipelined" architecture

B. Stays the same B. Expansion of cache memory

C. Increases * C. Inclusion of an internal math coprocessor

D. Equals the source voltage divided by series resistance D. Data/address line multiplexing *

59. A bulb in a staircases has two switches, one switch being at the 72. A 60V chopper drives a resistive load of 12 . The chopper

ground floor and the other one at the first floor. The bulb can be frequency is set to 1 kHz. Calculate the value of load power for a

turned ON and also can be turned OFF by and one of the switches turn-on time of 0.2 ms.

irrespective of the state of the other switch. The logic of switching of A. 20 W C. 60 W *

the bulb resembles. B. 50 W D. 100 W

A. an AND gate C. an XOR gate *

B. an OR gate D. a NAND gate 73. The input offset current of an operational amplifier is equal to which

of the following?

60. The symbols on this flip-flop device indicate ________. A. Difference between the two base currents *

B. Average of the two base currents

C. Collector current divided by current gain

D. Difference between the two base-emitter voltages

74. A series RLC circuit has a resonance frequency of 1 kHz and a

quality factor Q = 100. If each R, L and C is doubled from its original

A. A .triggering takes place on the negative-going edge of the CLK value, what is the new Q of the circuit?

pulse * A. 25 C. 100

B. triggering takes place on the positive-going edge of the CLK pulse B. 50 * D. 200

C. triggering can take place anytime during the HIGH level of the CLK

waveform 75. Which of the following is not an arithmetic instruction?

D. triggering can take place anytime during the LOW level of the CLK A. INC (increment) C. DEC (decrement)

waveform B. CMP (compare) D. ROL (rotate left) *

61. Which microprocessor has multiplexed data and address lines? 76. Generally, the gain of a transistor amplifier falls at high frequencies

A. 8086/8088 * C. 80386 due to the

B. 80286 D. Pentium A. internal capacitances of the device *

B. coupling capacitor at the input

62. The minimum number of 2-input NAND gates required to implement C. skin effect

the Boolean function Z = ABC, assuming that A, B and C are D. coupling capacitor at the output

available is

A. Two C. Five * 77. What is the minimum number of comparators required to build an 8-

B. Three D. Six bits flash ADC?

CERTC-ECE: MANILA-CEBU-BAGUIO-DAVAO-ILO-ILO (0932-175-1218) Page 3

CERTC-ECE PRE-BOARD EXAM 2 ELEX

A. 8 C. 255 A. 2V, 2mA C. 4V, 2mA

B. 63 D. 256 B. 3V, 2mA D. 4V, 1 mA

78. A silicon PN junction is forward biased with a constant current at roo 90. An op-amp can be considered as an ideal

temperature. What will be the forward bias voltage across the PN A. Voltage controlled current source

junction when the temperature is increased by 10C? B. Voltage controlled voltage source

A. increases by 60 mV C. increases by 25 mV C. Current controlled current source

B. decreases by 60 mV D. decreases by 25 mV * D. Current controlled voltage source

79. What will be the output of the circuit shown in the figure when the 91. In a full-wave rectifier using two ideal diodes, Vdc and Vm are the DC

input is a triangular wave? and peak values of the voltage respectively across a resistive load .

If PIV is the peak inverse voltage of the diode, then what are the

appropriate relationships for this rectifier?

V V

A. Vdc = m , PIV = 2Vm C. Vdc = 2 m , PIV = Vm

Vm Vm

B. Idc = 2 , PIV = 2Vm D. Vdc = , PIV = Vm

92. 11001, 1001, 111001 correspond to the 2s complement

representation of which one of the following set of numbers?

A. 25, 9 and 57 respectively C. -7, -7 and -7 respectively

A. square wave C. parabolic wave B. -6, -6 and -6 respectively D. -25, -9 and -57 respectively

B. triangular wave D. sine wave

93. A Silicon PN junction at a temperature of 20 C has a reverse

80. What is occurring when two or more sources of data attempt to use saturation current of 10 pico - Amperes (pA). What will be the

the same bus? approximate reserve saturation current at 40 C for the same bias?

A. Bus contention * C. Bus interruption A. 30 pA C. 50 pA

B. Direct memory access D. PPI B. 40 pA * D. 60 pA

81. The output of the 74 series of GATE of TTL gates is taken from BJT 94. Which of the following is not a computer bus?

in A. Data bus C. Timer bus *

A. totem pole and common collector configuration B. Control bus D. Address bus

B. either totem pole or open collector configuration *

C. common base configuration 95. What are the values of input impedance and output impedance of an

D. common collector configuration ideal transconductance (voltage controlled current source amplifier?

A. Zi = 0, Zo = 0 C. Zi = , Zo = 0

82. When the gate-to-source voltage (VGS) of a MOSFET with threshold B. Zi = 0, Zo = D. Zi = , Zo =

voltage of 400 mV, working in saturation is 900 mV, the drain current

is observed to be 1 mA. Neglecting the channel width modulation 96. The Boolean function Y = AB + CD is to be realized using 2 input

effect and assuming that the MOSFET is operating at saturation, NAND gates. What is the minimum number of gates required?

what is the drain current for an applied VGS of 1400 mV? A. 2 C. 4

A. 0.5 mA C. 3.5 mA B. 3 * D. 5

B. 2.0 mA D. 4.0 mA

97. The drain current of MOSFET in saturation is given by ID = K(VGS -

83. During a read operation the CPU fetches ________.

VT )2 where K is a constant. What is the magnitude of the

A. a program instruction C. data itself

transconductance gm?

B. another address D. all of the above *

K(VGS - VT )2 ID

A. C.

VDS VGS - VDS

84. Which of the following can best represent the action of JFET in its K(VGS - VT )2

equivalent circuit? B. 2K(VGS - VT )2 D.

VGS

A. Current controlled current source

B. Current controlled voltage source 98. The output Y of a 2-bit comparator is logic 1 whenever the 2-bit input

C. Voltage controlled voltage source A is greater than the 2-bit input B. The number of combinations for

D. Voltage controlled current source which the output is logic 1, is

A. 4 C. 8

85. An amplifier without feedback has a voltage gain of 50, input B. 6 * D. 10

resistance of 1 k and output resistance of 2.5 k. What is the input

resistance of the current-shunt negative feedback amplifier using the 99. What should be done to unused inputs on TTL gates?

above amplifier with a feedback factor of 0.2? A.They should be left disconnected so as not to produce a load on

A. 1/11 k C. 5 k any of the other circuits and to minimize power loading on the

B. 1/5 k D. 11 k voltage source.

B.All unused gates should be connected together and tied to V

86. This is the process of jointly establishing communication. through a 1 kresistor.

A. DMA C. multiplexing C.All unused inputs should be connected to an unused output; this

B. bidirectional addressing D. handshaking will ensure compatible loading on both the unused inputs and unused

outputs.

87. Which of the following logic families has the shortest propagation D.Unused AND and NAND inputs should be tied to VCC through a 1

delay? kresistor; unused OR and NOR inputs should be grounded. *

A.CMOS C. BiCMOS

B.ECL * D. 74SXX 100. Refer to the given figure. What type of output arrangement is being

used for the output?

88. What will be the photocurrent generated in (A) when the optical

incident on a photodiode is 10 W and the responsivity is 0.8 A/W?

A. 8 C. 12.5

B. 1.25 D. 6

89. In the amplifier circuit shown in the figure, the values of R1 and R2 are

such that the transistor is operating at VCE = 3V and IC = 1.5 mA

when its is 150. What is the operating point (VCE, IC) for a transistor

with of 200.

A. Complementary-symmetry C. Quasi push-pull

B. Push-pull D. Totem-pole

CERTC-ECE: MANILA-CEBU-BAGUIO-DAVAO-ILO-ILO (0932-175-1218) Page 4

You might also like

- Answer:: Y Abc + A + B + CDocument10 pagesAnswer:: Y Abc + A + B + CKarumon UtsumiNo ratings yet

- IndiaBIX - Analog Electronics - Section 1Document6 pagesIndiaBIX - Analog Electronics - Section 1Mikaela VillalunaNo ratings yet

- 1.basic Coms Noise - 2018rgs PDFDocument4 pages1.basic Coms Noise - 2018rgs PDFJefrilAmboyNo ratings yet

- Electronics Engineering FundamentalsDocument77 pagesElectronics Engineering FundamentalsLeonard Jobet Villaflor PantonNo ratings yet

- Periodic Exam 6Document5 pagesPeriodic Exam 6Inah RamosNo ratings yet

- Answers Self Test Grob's Basic Electronics-11edDocument6 pagesAnswers Self Test Grob's Basic Electronics-11edTaufiq Fahlifi YfzerobrrNo ratings yet

- Iecep Elecs 2Document10 pagesIecep Elecs 2Rick SarmientoNo ratings yet

- Indiabix With ExplanationsDocument46 pagesIndiabix With ExplanationsJustin ConsonNo ratings yet

- BASIC ELECTRICAL PRINCIPLESDocument44 pagesBASIC ELECTRICAL PRINCIPLESvon kervy onradeNo ratings yet

- Pre Board Exam ReviewerDocument24 pagesPre Board Exam Revieweremerson masangcayNo ratings yet

- CERTC - DAVAO WEEKLY EXAM 1 ELECSDocument1 pageCERTC - DAVAO WEEKLY EXAM 1 ELECSJj JumawanNo ratings yet

- Sand NotesDocument226 pagesSand NotesHGFLJJ0% (1)

- S10 Face Access Controller-Hardware Manual - SESAMEDocument17 pagesS10 Face Access Controller-Hardware Manual - SESAMEDaniel Jesus LozanoNo ratings yet

- Advance Review Weekly Exam 2 BacolodDocument4 pagesAdvance Review Weekly Exam 2 BacolodgiophilipNo ratings yet

- ChemDocument3 pagesChemLeeanne CabalticaNo ratings yet

- Certc - Davao Diagnostic Exam: Instruction: Select The Correct Answer For Each of The FollowingDocument4 pagesCertc - Davao Diagnostic Exam: Instruction: Select The Correct Answer For Each of The FollowingJj JumawanNo ratings yet

- CERTC Weekly Exam 5 ESASDocument4 pagesCERTC Weekly Exam 5 ESASArnel Pamaos Lopiba MontañezNo ratings yet

- ECE Reviewer 1Document1 pageECE Reviewer 1Light CloudNo ratings yet

- Transmission LinesDocument2 pagesTransmission LinesGlazylynCortezPalo100% (1)

- Certcdavao: Electronics EngineeringDocument4 pagesCertcdavao: Electronics EngineeringJj JumawanNo ratings yet

- Find SWR of Line Terminated in 25 Ω ResistanceDocument2 pagesFind SWR of Line Terminated in 25 Ω ResistanceMaria Deborah Vivas BaluranNo ratings yet

- ECE Materials and Components Section 1Document9 pagesECE Materials and Components Section 1MoneyNo ratings yet

- Iecep GeasDocument9 pagesIecep GeaswengNo ratings yet

- ECE Board Performance Review 2019Document20 pagesECE Board Performance Review 2019Elaine R RiveraNo ratings yet

- Powerline Pre Board Ree Sept 2010Document15 pagesPowerline Pre Board Ree Sept 2010Junnar Jay AbañoNo ratings yet

- MCQ in Electronic Circuits Part 1Document17 pagesMCQ in Electronic Circuits Part 1Palani C100% (1)

- Communications Test YourselfDocument35 pagesCommunications Test Yourselfpatrick0308No ratings yet

- MCQ Semiconductor PDFDocument7 pagesMCQ Semiconductor PDFboomaNo ratings yet

- ECS QuestionsDocument130 pagesECS Questionsjjmmnn1001100% (1)

- Draft of October 2015 Electronics Engineering Board Exam Questions and ConceptsDocument5 pagesDraft of October 2015 Electronics Engineering Board Exam Questions and ConceptsAyel Cejas Costiniano100% (1)

- Excel Review Center Refresher Course EST: Give Your Best Shot !Document4 pagesExcel Review Center Refresher Course EST: Give Your Best Shot !Nida Bagoyboy NatichoNo ratings yet

- Geas and EstDocument3 pagesGeas and EstPeejay OllabracNo ratings yet

- Exam Primer McqsDocument25 pagesExam Primer McqsGemalyn NacarioNo ratings yet

- CH 9Document33 pagesCH 9mugammad wasimNo ratings yet

- Elex RF PDFDocument40 pagesElex RF PDFKarumon UtsumiNo ratings yet

- Water DragonDocument1 pageWater DragonGlenn Paul PaceteNo ratings yet

- Pinoybix WADocument28 pagesPinoybix WAKenNo ratings yet

- Basic Electronics Subject Code 22225 NotesDocument6 pagesBasic Electronics Subject Code 22225 NotesashaNo ratings yet

- 01 ElectricalDocument15 pages01 ElectricalKrishna KrishNo ratings yet

- Digital Electronics - 40 CharacterDocument50 pagesDigital Electronics - 40 CharacterChristian CuevasNo ratings yet

- Reviewer Pcomms SummaryDocument135 pagesReviewer Pcomms SummaryMelric LamparasNo ratings yet

- ElecDocument4 pagesElecJj JumawanNo ratings yet

- Powerful Review Center: For October 2013 ExamDocument1 pagePowerful Review Center: For October 2013 ExamShalom Wenceslao100% (1)

- Module 2 Op-AmpDocument26 pagesModule 2 Op-AmpSTUDENTS OF DOE CUSATNo ratings yet

- Coaching 5 (Geas)Document10 pagesCoaching 5 (Geas)cajaroNo ratings yet

- AC Circuits Fundamentals QuizDocument4 pagesAC Circuits Fundamentals QuizCris Diane G. DatingginooNo ratings yet

- Line Encoding TechniquesDocument21 pagesLine Encoding TechniquesRenjelle Mae AutrizNo ratings yet

- ChemistryDocument24 pagesChemistryJimmy OrajayNo ratings yet

- Chapter 16 AntennaDocument10 pagesChapter 16 AntennaStephany Bryan Diez ItaoNo ratings yet

- BSNL JTO Exam 2006 Question PaperDocument17 pagesBSNL JTO Exam 2006 Question PaperROHITCHOURASIYANo ratings yet

- Dac MCQDocument10 pagesDac MCQTrojan0% (1)

- Iecep EsatDocument29 pagesIecep EsatIvy Cee100% (1)

- ProteusRound1 FinalDocument5 pagesProteusRound1 FinalDhanraj BhosaleNo ratings yet

- ELEX Digital Electronics PDFDocument21 pagesELEX Digital Electronics PDFJustine MiraNo ratings yet

- Advance CMOS Cell Design-Book3Document44 pagesAdvance CMOS Cell Design-Book3Melvic MacalaladNo ratings yet

- Certcdavao: Instruction: Select The Correct Answer For Each of The FollowingDocument4 pagesCertcdavao: Instruction: Select The Correct Answer For Each of The FollowingJj JumawanNo ratings yet

- Writable Uploads Resources Files Elec 15-01 To Elec 15-06 QuestionnaireDocument3 pagesWritable Uploads Resources Files Elec 15-01 To Elec 15-06 Questionnairejethro wilsonNo ratings yet

- Exp-10 COLabDocument7 pagesExp-10 COLabAdarsh DwivediNo ratings yet

- Logic CircuitsDocument6 pagesLogic CircuitsLeandro MiñonNo ratings yet

- Voltzfest Mystefii: Questions Considered For Tie BreakerDocument4 pagesVoltzfest Mystefii: Questions Considered For Tie BreakermanimaranNo ratings yet

- Weekly Exam 1 - DC & Ac CircuitsDocument5 pagesWeekly Exam 1 - DC & Ac CircuitsHary KrizNo ratings yet

- Review Guide Series Review Guide Series: E = 4.44◌ּf◌ּN◌ּβ ◌ּADocument6 pagesReview Guide Series Review Guide Series: E = 4.44◌ּf◌ּN◌ּβ ◌ּAHary Kriz100% (2)

- Ref.1 Math - Ee..kevinDocument3 pagesRef.1 Math - Ee..kevinHary Kriz0% (1)

- Impulse and Momentum ExplainedDocument5 pagesImpulse and Momentum ExplainedHary KrizNo ratings yet

- Electrical Engineering Board Examination Review QuestionsDocument9 pagesElectrical Engineering Board Examination Review QuestionsHary Kriz100% (1)

- Electronics Refresher I RF Review Center: CE CCDocument6 pagesElectronics Refresher I RF Review Center: CE CCHary KrizNo ratings yet

- EST - Refresher Bring HomeDocument4 pagesEST - Refresher Bring HomeHary Kriz100% (1)

- AP Rotation Review 13 SCDocument24 pagesAP Rotation Review 13 SCHary KrizNo ratings yet

- and A - and A - and ADocument1 pageand A - and A - and AHary KrizNo ratings yet

- Engineering Sciences ReviewerDocument7 pagesEngineering Sciences ReviewerHary Kriz100% (1)

- Review in CommunicationsDocument11 pagesReview in CommunicationsHary KrizNo ratings yet

- Elecs Ref 2019Document8 pagesElecs Ref 2019Hary KrizNo ratings yet

- Electrical 02Document10 pagesElectrical 02Hary Kriz33% (3)

- US Navy Course - Electronics Technician, Volume 6-Digital Data Systems NAVEDTRA 14091Document522 pagesUS Navy Course - Electronics Technician, Volume 6-Digital Data Systems NAVEDTRA 14091BaoJun100% (2)

- Uc Preboard ExamDocument4 pagesUc Preboard ExamHary KrizNo ratings yet

- Pre-Board EST GlenDocument5 pagesPre-Board EST GlenHary KrizNo ratings yet

- Volume 1-SafetyDocument68 pagesVolume 1-SafetyChoochart ThongnarkNo ratings yet

- Convolution PDFDocument6 pagesConvolution PDFHary KrizNo ratings yet

- Cert-Ece Mathematics: Final CoachingDocument7 pagesCert-Ece Mathematics: Final CoachingHary KrizNo ratings yet

- Certc: Mathematics Refresher 2Document4 pagesCertc: Mathematics Refresher 2Hary Kriz100% (1)

- Certc Final Cns - MathDocument1 pageCertc Final Cns - MathHary KrizNo ratings yet

- Radar Systems CourseDocument86 pagesRadar Systems CourseBhukya VenkateshNo ratings yet

- Electronics Technician: Volume 5-Navigation SystemsDocument24 pagesElectronics Technician: Volume 5-Navigation SystemsHary KrizNo ratings yet

- Electronics Technician: Volume 2-AdministrationDocument24 pagesElectronics Technician: Volume 2-AdministrationHary KrizNo ratings yet

- Electronics Technician: Volume 9-Electro-OpticsDocument20 pagesElectronics Technician: Volume 9-Electro-OpticsHary KrizNo ratings yet

- Electronics MCQDocument4 pagesElectronics MCQHary KrizNo ratings yet

- Et V04Document30 pagesEt V04Hary KrizNo ratings yet

- Math ProblemsDocument8 pagesMath ProblemsHary KrizNo ratings yet

- Series CH4200: Chemical Feed Equipment Floor-Mounted Gas DispenserDocument5 pagesSeries CH4200: Chemical Feed Equipment Floor-Mounted Gas DispenserCandra Tier'z100% (1)

- API 5l Grade l245 PipesDocument1 pageAPI 5l Grade l245 PipesMitul MehtaNo ratings yet

- Max 223C Pipeline Welding InverterDocument2 pagesMax 223C Pipeline Welding InvertermtonellyNo ratings yet

- Datasheet CONTI SILENTSYNC ENDocument1 pageDatasheet CONTI SILENTSYNC ENViniciusNo ratings yet

- Eductor AgitationDocument2 pagesEductor AgitationNicolás Solano CondeNo ratings yet

- Quantifying Life Safety Part II - Quantification of Fire Protection SystemsDocument6 pagesQuantifying Life Safety Part II - Quantification of Fire Protection SystemskusumawardatiNo ratings yet

- Tensile Test AnalysisDocument8 pagesTensile Test AnalysisNazmul HasanNo ratings yet

- Gauss Lab 01Document4 pagesGauss Lab 01Diego Giraldo BoteroNo ratings yet

- Vena SIF Piping CalculationDocument5 pagesVena SIF Piping CalculationPratap KollapaneniNo ratings yet

- 2.3 Drawing Operations: Need To See If It Really Works For All Tasks, and If Not Then Get Rid of ItDocument1 page2.3 Drawing Operations: Need To See If It Really Works For All Tasks, and If Not Then Get Rid of ItTrogo BoNo ratings yet

- Intro to Process Control Part 3 by Omar Y IsmaelDocument25 pagesIntro to Process Control Part 3 by Omar Y IsmaelHATAM TALAL ALINo ratings yet

- Richard GrisenthwaiteDocument25 pagesRichard GrisenthwaitecaarthiyayiniNo ratings yet

- Smart is the most intelligent solution yet for urban drivingDocument8 pagesSmart is the most intelligent solution yet for urban drivingHenrique CorreiaNo ratings yet

- Icwe14 - Id02441 HfpiDocument36 pagesIcwe14 - Id02441 HfpiSergio StolovasNo ratings yet

- JNTU Previous Paper Questions ThermodynamicsDocument61 pagesJNTU Previous Paper Questions ThermodynamicsVishnu MudireddyNo ratings yet

- Design Diesel-Photovoltaic Hybrid Power PlantDocument93 pagesDesign Diesel-Photovoltaic Hybrid Power PlantDaniel Okere100% (1)

- Hydraulic Cylinder Seal Kits: Quality With Value GuaranteedDocument16 pagesHydraulic Cylinder Seal Kits: Quality With Value GuaranteedHenry GamboaNo ratings yet

- Solid Mechanics: Amit Sir (M-Tech (STRUCTURE), BE, Diploma in Civil), 7020059691/7385990691Document9 pagesSolid Mechanics: Amit Sir (M-Tech (STRUCTURE), BE, Diploma in Civil), 7020059691/7385990691Nikita GonnadeNo ratings yet

- Technical Spec & BOQ Screw ConveyorDocument7 pagesTechnical Spec & BOQ Screw ConveyorjhsudhsdhwuNo ratings yet

- Machine Tools Questions and Answers - GrindingDocument4 pagesMachine Tools Questions and Answers - GrindingRohit GhulanavarNo ratings yet

- UCI274D - Technical Data SheetDocument8 pagesUCI274D - Technical Data SheetFloresNo ratings yet

- ISA SymbolsDocument2 pagesISA Symbolsmahesh009No ratings yet

- Space Programming 1Document10 pagesSpace Programming 1Mache SebialNo ratings yet

- TS1A-13A: Operation and Maintenance ManualDocument204 pagesTS1A-13A: Operation and Maintenance ManualJavier AponteNo ratings yet

- ABH-2 Pile - RamDocument5 pagesABH-2 Pile - RamGaneshalingam Ramprasanna2No ratings yet

- Eee MCQDocument39 pagesEee MCQRoshnal BluestacksNo ratings yet

- Galvanic CorrosionDocument35 pagesGalvanic CorrosionSyarief NahdiNo ratings yet

- Bill of Quantities: Fifteen-Classrooms ADocument1 pageBill of Quantities: Fifteen-Classrooms AFritz NatividadNo ratings yet

- Ducha EmpotradaDocument1 pageDucha Empotradagilmar melendresNo ratings yet

- MVC Project Jarvis DatabaseDocument30 pagesMVC Project Jarvis DatabaseSravan SaiNo ratings yet