Professional Documents

Culture Documents

Controle Mars 2003 ECE Complet PDF

Uploaded by

baydiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Controle Mars 2003 ECE Complet PDF

Uploaded by

baydiCopyright:

Available Formats

Contrle Architecture des microprocesseurs ECE INGE3 / PREPA MASTER

Dure : 2 heures - mars 2003

Contrle

Architecture des microprocesseurs

Dure 2 heures

Tous les documents personnels (cours, TD, TP) sont autoriss.

La machine calculer est autorise.

La qualit de la prsentation sera prise en compte dans le barme de notation.

Les trois parties de ce contrle sont totalement indpendantes.

Il vous est demand de rdiger chacune des parties sur une copie spare.

Pensez rappeler le numro des questions auxquelles vous rpondez.

Noubliez pas de joindre tous les documents rponses votre copie.

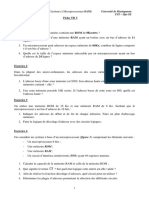

Partie A

Architecture du microprocesseur 68000 de MOTOROLA

Dcodage dadresses

Une carte micro-programme comporte un composant RAM et un composant EPROM

cbls sur le bus dadresse comme indiqu ci-dessous :

(A0A15) (A0A15)

Bus dadresse U2

A0 D0

A1 D1

U1 A2 D2

A0 D0 A3 D3

A1 A4 D4

D1

A2 A5 D5

D2

A3 D3 A6 D6

A4 A7 D7

D4

A5 A8

D5

A6 D6 A9

A7 A10

A8 D7 A11

A9 A12

A10 A13

A11 A14

U3

A 15

E1 CE E2

OE 1 CE

VPP

WE

74LS04 0V

RAM: 6132

EPROM: 2764

(D0D7)

Bus de donnes

A.1. Etude du composant RAM (U1) (3 points / 8mn)

A.1.1) Indiquer le rle de lentre E1. Quel doit tre ltat actif de cette entre pour effectuer une

criture dune donne dans la RAM (U1).

A.1.2) Dterminer la capacit du composant U1 en Kbits et en Ko.

A.1.3) En supposant que les lignes A15, A14, A13 et A12 du bus dadresse sont ltat logique

bas, dterminer la plage dadresse occupe par le composant U1.

A.2. Etude du composant EPROM (U2) (2 points / 8mn)

A.2.1) Dterminer la capacit du composant U2 en Kbits et en Ko.

A.2.2) Sachant que le bit A15 du bus dadresse est invers puis connect lentre E2 du

composant U2, dterminer la plage dadresse occupe par le composant U2

J. FRANCOMME francom@ece.fr - J.M. HENRI henri@ece.fr

1/7

Contrle Architecture des microprocesseurs ECE INGE3 / PREPA MASTER

Dure : 2 heures - mars 2003

Partie B

Programmation dans le langage assembleur du microprocesseur 68000 de

MOTOROLA

B.1. Gnralits (3 points / 14mn)

B.1.1) Donnez le nom dune mmoire volatile.

B.1.2) Quels sont les diffrents bits du registre de code condition ?

B.1.3) Proposez une solution permettant de mettre zro le cinquime bit du registre de code

condition en partant de la droite. Dcrivez convenablement votre solution.

B.1.4) Convertir la valeur $EF en binaire.

B.1.5) Dcrire la fonction de la ligne suivante dans un programme crit en langage assembleur

68000.

DC.L 2

B.1.6) Quel est le rle du registre PC du processeur 68000 ?

B.1.7) Montrez que linstruction, dbf est quivalente linstruction dbra

Info: consulter la description de linstruction DBcc dans le document annexe/jeu

dinstructions.

B.1.8) Indiquer de manire simplifie les diffrentes tapes pour lenregistrement dune donne

dans la pile.

B.1.9) Dcrire les modes dadressages mis en uvre dans les deux instructions suivantes pour

chacun des oprande s et donner le contenu de chacun des registres 32 bits et de la mmoire

aprs excution :

MOVEA #$9123, A0

MOVE A0, (A0)

B.2. Cration dun programme. (5 points / 40mn)

Objectif : Ecrire un programme permettant de trier les valeurs (8 octets) dun tableau VAL de faon

sparer les nombres pairs des nombres impairs comme suit :

Le tableau "VAL" se situe ladresse $3000

Le tableau "PAIR" qui recevra les nombres pairs se situe ladresse $3100

Le tableau "IMPAIR" qui recevra les nombres impairs se situe ladresse $3200

B.2.1) En quelques mots, indiquer une mthode permettant de dterminer si un nombre est pair ou

impair en utilisant la notion de dcalage.

B.2.2) Sur quel indicateur dtat, le test doit-il agir pour dfinir la parit du nombre ?

En dduire le nom en langage assembleur des 2 tests quil est possible de mettre en uvre.

B.2.3) Ecrire le programme en langage assembleur 68000 partir de ladresse $1000,

correspondant au cahier des charges dcrit ci-dessus.

Vous considrerez un tableau VAL de 8 octets dfini comme suit :

VAL DC.B $12, $C9, $5F, $FC, $A2, $52, $3B, $FD

Vous utiliserez les registres suivants :

D0 Contient le nombre doctet de la chane VAL, initialis la valeur 8.

D1 Contient successivement les valeurs de la chane VAL.

A0 Pointe la chane VAL.

A1 Pointe la chane PAIR.

A2 Pointe la chane IMPAIR.

J. FRANCOMME francom@ece.fr - J.M. HENRI henri@ece.fr

2/7

Contrle Architecture des microprocesseurs ECE INGE3 / PREPA MASTER

Dure : 2 heures - mars 2003

Partie C

Analyse dun programme en langage assembleur pour le microprocesseur 68000

de MOTOROLA

C.1. Comprhension dun programme en langage assembleur 68000 (7 points / 50mn)

Le programme suivant ralise une opration sur deux oprandes de deux digits cods en BCD.

Remarque : Vous considrerez donc pour ces deux oprandes la reprsentation BCD et pas

hexadcimale : Oubliez le $ marqu devant loprande mais ne lenlevez pas.

Si on ne met pas le $ , le logiciel dassemblage fait la conversion dcimal? hexadcimal

************************************* *************************************

* ECE Mars 2003 * Bibliothque de sous-programmes

* INGE3 - PREPA MASTER *************************************

* Contrle Architecture des microprocesseurs DOFOISD5

* J. FRANCOMME - http://francomme.fr.fm CLR.W D6

* Etat initial du registre des flags : X N Z V BRA NEXT

C tous 0. SUITE ANDI #efface_X,CCR

************************************* ABCD D0,D6

************************************* BCC NEXT

* Assignations ADD.W #$0100,D6

************************************* NEXT DBF D5,SUITE

DEBPROG EQU $1000 RTS

VAL1 EQU $35

VAL2 EQU $11 D6PLUSD7

efface_X EQU $EF ANDI #efface_X,CCR

ABCD D7,D6

************************************* ROR.W #8,D6

* Initialisation des vecteurs de dmarrage ROR.W #8,D7

************************************* ABCD D7,D6

ORG $0 ROR.W #8,D6

DC.L $8000 Pointeur de pile RTS

aprs un reset

DC.L DEBPROG Compteur de END

programme (PC) aprs un reset

*************************************

* Programme principal

*************************************

ORG DEBPROG

MOVE.W #VAL1,D0

MOVE.W #VAL2,D1

MOVE.W D1,D5

ANDI #$0F,D5

BSR DOFOISD5

MOVE.W D6,D7

MOVE.W D1,D5

LSR.B #4,D5

ANDI.W #$0F,D5

BSR DOFOISD5

LSL.W #4,D6

BSR D6PLUSD7

FIN BRA FIN

J. FRANCOMME francom@ece.fr - J.M. HENRI henri@ece.fr

3/7

Contrle Architecture des microprocesseurs ECE INGE3 / PREPA MASTER

Dure : 2 heures - mars 2003

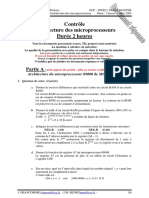

C.1.1) Compltez les documents rponses joints pages 5 et 6 en vous aidant des remarques

suivantes ;

Aide pour complter les documents rponses :

Vous remarquerez que le sous-programme D0FOISD5 est appel deux fois et que le

sous-programme D6PLUSD7 est appel une seule fois la fin de lapplication.

Vous trouverez donc le groupe dinstructions de chaque sous-programme autant de fois

que celui-ci est appel , sur les documents rponses.

Aprs lexcution de chaque instruction, donnez le contenu de tous les registres cits

dans le tableau, sur la mme ligne ; c'est--dire : D0, D1, D5, D6, D7, les bits X et C

du registre de code condition puis le contenu du registre PC.

Comme cela est indispensable, le fichier listing vous est fourni en annexe 1.

Toutes les valeurs ngatives du tableau seront notes en complment 2.

C.1.2) Aprs avoir complt les documents rponses joints, il vous est demand de dduire

lopration effectue par cette application sur les deux oprandes.

C.1.3) Pour vrification, posez lopration sur votre copie et dcrivez le processus pour obtenir le

rsultat.

C.1.4) Quelle sera la diffrence dans lexcution du sous-programme D0FOISD5 si loprande

VAL2 = 12 (ie : nombre de boucle) ?

C.1.5) La procdure D6PLUSD7 est constitue dun certain nombre dinstructions de rotation

ROR

C.1.5.1) Expliquez ce que fait linstruction ROR sur la donne dont le format est celui

donn dans ce sous-programme (.W).

C.1.5.2) Indiquez la raison de cette manipulation en utilisant le rappel sur les oprations en

BCD donn ci-dessous.

C.1.6) Justifier la valeur $FFF0 de la ligne 103C du fichier listing donn en annexe 1.

C.1.7.synthse) Ne rpondre cette question que si vous avez rpondu toutes les questions

prcdentes ;

Proposez une modification du programme donn dans cette partie C afin de pouvoir faire la

mme opration sur des oprandes de 32 bits

Remarque : Le rsultat tient sur un format plus grand que celui dorigine que vous

considrerez afin de toujours obtenir un rsultat valide.

Rappel : Opration sur les chiffres dcimaux cods en binaire (BCD).

ABCD ? Addition dcimale sur un octet utilisant le bit X (extended carry).

Syntaxe utilise : ABCD Dy, Dx

Additionne loprande source et loprande destination avec le contenu du bit X et

enregistre le rsultat dans le registre de destination.

Registre de code condition :

X : Positionn la mme valeur que la retenue C

N : Non utilis

Z : Mis zro si le rsultat est diffrent de zro, sinon inchang.

V : Non utilis

C : Mis un si une retenue dcimale est gnre, sinon mis zro.

Thats all Folks

La correction de ce contrle sera sur Internet

ladresse suivante http://francomme.fr.fm

dans la rubrique Informatique Industrielle, 68000, cours.

Bon courage

J. FRANCOMME francom@ece.fr - J.M. HENRI henri@ece.fr

4/7

Nom :

Contrle Architecture des microprocesseurs ECE INGE3 / PREPA MASTER

Dure : 2 heures - mars 2003

VAL1 EQU $35

VAL2 EQU $11 Instructions Registres Registres PC

efface_X EQU $EF A0

D0 A1D1 A2 D5A3 D0D6 D7 Bit N Bit C Bit X

avant xxxxxxxx xxxxxxxx xxxxxxxx xxxxxxxx xxxxxxxx 0 0 0

MOVE.W #VAL1,D0 aprs

MOVE.W #VAL2,D1 aprs

aprs

MOVE.W D1,D5 aprs

aprs

ANDI #$0F,D5 aprs

aprs

BSR DOFOISD5 aprs

aprs

MOVE.W D6,D7 avant

aprs

aprs

MOVE.W D1,D5 avant

aprs

aprs

LSR.B #4,D5 avant

aprs

aprs

ANDI.W #$0F,D5 avant

aprs

aprs

BSR DOFOISD5 aprs

LSL.W #4,D6 aprs

BSR D6PLUSD7 aprs

FIN BRA FIN aprs

Lors du premier appel de la procdure D0FOISD5

DOFOISD5 CLR.W D6 aprs

BRA NEXT aprs

SUITE ANDI #efface_X,CCR aprs

ABCD D0,D6 aprs

BCC NEXT aprs

ADD.W #$0100,D6 aprs

NEXT DBF D5,SUITE aprs

RTS aprs

J. FRANCOMME francom@ece.fr - J.M. HENRI henri@ece.fr

5/7

Nom :

Contrle Architecture des microprocesseurs ECE INGE3 / PREPA MASTER

Dure : 2 heures - mars 2003

Instructions Registres Registres PC

A0

D0 A1D1 A2 D5A3 D0D6 D7 Bit N Bit C Bit X

Lors du deuxime appel de la procdure D0FOISD5

DOFOISD5 CLR.W D6 aprs

BRA NEXT aprs

SUITE ANDI #efface_X,CCR aprs

ABCD D0,D6 aprs

BCC NEXT aprs

ADD.W #$0100,D6 aprs

NEXT DBF D5,SUITE aprs

RTS aprs

Lors de lappel de la procdure D6PLUSD7

D6PLUSD7 ANDI #efface_X,CCR aprs

ABCD D7,D6 aprs

ROR.W #8,D6 aprs

ROR.W #8,D7 aprs

ABCD D7,D6 aprs

ROR.W #8,D6 aprs

RTS aprs

J. FRANCOMME francom@ece.fr - J.M. HENRI henri@ece.fr

6/7

Contrle Architecture des microprocesseurs ECE INGE3 / PREPA MASTER

Dure : 2 heures - mars 2003

Annexe 1 Fichier listing de lapplication partie C

00000000 1 **********************************************************

00000000 2 * ECE Mars 2003

00000000 3 * INGE3 - PREPA MASTER

00000000 4 * Contrle Architecture des microprocesseurs

00000000 5 * J. FRANCOMME - http://francomme.fr.fm

00000000 6 * Etat initial du registre des flags : X N Z V C tous 0.

00000000 7 **********************************************************

00000000 8

00000000 9 **********************************************************

00000000 10 * Assignations

00000000 11 **********************************************************

00000000 =00001000 12 DEBPROG EQU $1000

00000000 =00000035 13 VAL1 EQU $35

00000000 =00000011 14 VAL2 EQU $11

00000000 =000000EF 15 efface_X EQU $EF

00000000 16

00000000 17

00000000 18 **********************************************************

00000000 19 * Initialisation des vecteurs de dmarrage

00000000 20 **********************************************************

00000000 21 ORG $0

00000000 00008000 22 DC.L $8000 Pointeur de pile aprs un reset

00000004 00001000 23 DC.L DEBPROG Compteur de programme (PC) aprs un reset

00000008 24

00000008 25

00000008 26 **********************************************************

00000008 27 * Programme principal

00000008 28 **********************************************************

00001000 29 ORG DEBPROG

00001000 30

00001000 31 * Charger un registre d'adresse (A1) avec adresse de la zone des donnes

00001000 32 * Utilisation de l'adressage indirect pour le lecture des donnes

00001000 33

00001000 34

00001000 303C 0035 35 MOVE.W #VAL1,D0

00001004 323C 0011 36 MOVE.W #VAL2,D1

00001008 3A01 37 MOVE.W D1,D5

0000100A 0245 000F 38 ANDI #$0F,D5

0000100E 6100 0018 39 BSR DOFOISD5

00001012 3E06 40 MOVE.W D6,D7

00001014 3A01 41 MOVE.W D1,D5

00001016 E80D 42 LSR.B #4,D5

00001018 0245 000F 43 ANDI.W #$0F,D5

0000101C 6100 000A 44 BSR DOFOISD5

00001020 E94E 45 LSL.W #4,D6

00001022 6100 001E 46 BSR D6PLUSD7

00001026 60FE 47 FIN BRA FIN * pour viter l'excution des codes qui se trouvent

00001028 48 * aprs le programme dans la mmoire.

00001028 49

00001028 50 **********************************************************

00001028 51 * Bibliothque de sous-programmes

00001028 52 **********************************************************

00001028 53 DOFOISD5

00001028 4246 54 CLR.W D6

0000102A 6000 0010 55 BRA NEXT

0000102E 023C 00EF 56 SUITE ANDI #efface_X,CCR

00001032 CD00 57 ABCD D0,D6

00001034 6400 0006 58 BCC NEXT

00001038 0646 0100 59 ADD.W #$0100,D6

0000103C 51CD FFF0 60 NEXT DBF D5,SUITE

00001040 4E75 61 RTS

00001042 62

00001042 63 D6PLUSD7

00001042 023C 00EF 64 ANDI #efface_X,CCR

00001046 CD07 65 ABCD D7,D6

00001048 E05E 66 ROR.W #8,D6

0000104A E05F 67 ROR.W #8,D7

0000104C CD07 68 ABCD D7,D6

0000104E E05E 69 ROR.W #8,D6

00001050 4E75 70 RTS

00001052 71

00001052 72 END

J. FRANCOMME francom@ece.fr - J.M. HENRI henri@ece.fr

7/7

You might also like

- TD - N°2 - EN - Systèmes À MicroprocesseurDocument7 pagesTD - N°2 - EN - Systèmes À MicroprocesseurTimble Puteur100% (2)

- Exercices Assembleur MEHDIDocument52 pagesExercices Assembleur MEHDIMehdi Amrani76% (21)

- Adressage MemoireDocument10 pagesAdressage MemoireLibre HamataNo ratings yet

- Chap I Systèmes Embarqués Et MicroprocesseursDocument22 pagesChap I Systèmes Embarqués Et MicroprocesseursMohamed Aziz Ben RomdhaneNo ratings yet

- TP N1-Prise en Main de QuartusDocument22 pagesTP N1-Prise en Main de QuartusIlham KinichNo ratings yet

- 16FXXXDocument86 pages16FXXXkhmNo ratings yet

- Chapitre 8 Convertisseur Adc DacDocument9 pagesChapitre 8 Convertisseur Adc DacMedNo ratings yet

- td1 Arduino Ing2Document6 pagestd1 Arduino Ing2youssouf ismaNo ratings yet

- TD Exam PDFDocument12 pagesTD Exam PDFpapNo ratings yet

- TD 6 Eno-P PDFDocument3 pagesTD 6 Eno-P PDFKhalid WasimNo ratings yet

- Cours HC11Document27 pagesCours HC11bjm63No ratings yet

- IjDocument7 pagesIjAbderrahmane WardiNo ratings yet

- SYS Up Serie1 12-13Document2 pagesSYS Up Serie1 12-13Abde Lilah Dgaigui100% (1)

- Poly TP en Tp2 Geii 2019Document12 pagesPoly TP en Tp2 Geii 2019sdfNo ratings yet

- TD - N°2 - EN - Systèmes À Microprocesseur PDFDocument7 pagesTD - N°2 - EN - Systèmes À Microprocesseur PDFTimble Puteur100% (1)

- Ser TD4 20222023Document4 pagesSer TD4 20222023ramzi ayadi100% (1)

- M - Microprocesseurs Et DSP-Chap2Document17 pagesM - Microprocesseurs Et DSP-Chap2MENANI ZineddineNo ratings yet

- 3 Cours Microprocesseur 16 BitsDocument15 pages3 Cours Microprocesseur 16 BitsSeghiour AbdellatifNo ratings yet

- Chapitre 4 Alimentation - Moteur - Pas - À - PasDocument37 pagesChapitre 4 Alimentation - Moteur - Pas - À - Paskhaled100% (1)

- Compte Rendu TP Archetecture Des Systèmes EmbarquésDocument19 pagesCompte Rendu TP Archetecture Des Systèmes EmbarquésKhawla KholitaNo ratings yet

- Partie-2-Microprocesseur + MemoireDocument14 pagesPartie-2-Microprocesseur + MemoireyaoNo ratings yet

- CHAP1Document6 pagesCHAP1riadh hassnaouiNo ratings yet

- DauphinDocument48 pagesDauphinAnas KertyNo ratings yet

- Presentation Cour Microproc2Document33 pagesPresentation Cour Microproc2user2014523No ratings yet

- TP1Document5 pagesTP1Oumayma AmiriNo ratings yet

- Presenatationassembleur 2010Document169 pagesPresenatationassembleur 2010NOURDINE EZZALMADINo ratings yet

- MMO Corrigé Sujet 1synthèse M21Document3 pagesMMO Corrigé Sujet 1synthèse M21Abdou KarimNo ratings yet

- Programmation Assembleur 8086Document51 pagesProgrammation Assembleur 8086zied harchayNo ratings yet

- Mise en Route Du Compilateur MPLAB XC8Document11 pagesMise en Route Du Compilateur MPLAB XC8nawzatNo ratings yet

- Ampli ACCORDEDocument10 pagesAmpli ACCORDEMaria MEKLI100% (1)

- Jeu D - Instructions Du PIC16F84ADocument9 pagesJeu D - Instructions Du PIC16F84AOMAR ENNAJINo ratings yet

- 68 HC 11Document15 pages68 HC 11Abdelhadi TaoufikNo ratings yet

- Port Parallèle Pia 8255Document11 pagesPort Parallèle Pia 8255alex bbapNo ratings yet

- TD N - 1architecture PDFDocument2 pagesTD N - 1architecture PDFABDELKARIM AINNo ratings yet

- TP TD N2 Microntroleur AssembleurDocument4 pagesTP TD N2 Microntroleur AssembleurKhaoula EddouibNo ratings yet

- TD 06 CorrigeDocument12 pagesTD 06 CorrigeOmar KhayyamNo ratings yet

- Cours GratuitDocument7 pagesCours GratuitMlokhiaNo ratings yet

- Pic 16 FDocument20 pagesPic 16 FMarie MimiiNo ratings yet

- Exercice 21 - 22 - 23Document8 pagesExercice 21 - 22 - 23Riham abNo ratings yet

- La Programmation en Assembleur Du Microprocesseur 8086Document18 pagesLa Programmation en Assembleur Du Microprocesseur 8086Abdou Bensalek100% (1)

- Pic 16 F 877Document10 pagesPic 16 F 877Youssef Boughallad100% (1)

- TD 2tech 2EIDocument3 pagesTD 2tech 2EIoussamaNo ratings yet

- Compte Rendu Assembleur 1Document3 pagesCompte Rendu Assembleur 1El Oufir El MehdiNo ratings yet

- Chapitre IV Programmation PIC 16F84Document12 pagesChapitre IV Programmation PIC 16F84Sanae BOUNOUANo ratings yet

- (Ele) 6809 Doc Asm RS v3-00Document239 pages(Ele) 6809 Doc Asm RS v3-00Mila zNo ratings yet

- TP Initiation A La Programmation Du C PIC 16F84A en Mikro CDocument6 pagesTP Initiation A La Programmation Du C PIC 16F84A en Mikro CPaty MuyengwaNo ratings yet

- Architecture Superscalaire Et PipelineDocument7 pagesArchitecture Superscalaire Et PipelineRomuald AHODEHINTONo ratings yet

- 3.Dsp Tmsf28335cpuDocument45 pages3.Dsp Tmsf28335cpuMassi Massy MassyNo ratings yet

- TD Decodage AdressesDocument10 pagesTD Decodage AdressesDhafer MezghaniNo ratings yet

- 10manuel BT Maintenance Des Equipements InformatiqueDocument181 pages10manuel BT Maintenance Des Equipements InformatiqueAmine KordaraNo ratings yet

- TP N °1: Vérin:: Commande Par Microprocesseur 6809Document10 pagesTP N °1: Vérin:: Commande Par Microprocesseur 6809Mouhcine Ben MoussaNo ratings yet

- TDDocument10 pagesTDredNo ratings yet

- TP 1 Info Indus07Document15 pagesTP 1 Info Indus07MOHAMED TAMZAITINo ratings yet

- Cours VHDL 2Document45 pagesCours VHDL 2Zine Elabidine MoslihNo ratings yet

- TP2 MicroprocesseurDocument14 pagesTP2 MicroprocesseurAdem AounNo ratings yet

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesFrom EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesNo ratings yet

- TD MicroprocesseurDocument6 pagesTD MicroprocesseurtchoudjafandjaNo ratings yet

- CONTROLE TERMINAL MiscroprocesseurDocument10 pagesCONTROLE TERMINAL MiscroprocesseurSalma NsalmaNo ratings yet

- Archi 6Document11 pagesArchi 6Ahmed Yacine abdelmalekNo ratings yet

- Fiche Td3 SamDocument2 pagesFiche Td3 Samfashionista louliNo ratings yet

- Projet Nucleair Youssef3Document8 pagesProjet Nucleair Youssef3baydiNo ratings yet

- Partie FakhirDocument6 pagesPartie FakhirbaydiNo ratings yet

- Exercices Redress ComDocument4 pagesExercices Redress ComHAMZA112233No ratings yet

- TD5Document3 pagesTD5baydiNo ratings yet

- Resume STS1 15 HacheursDocument4 pagesResume STS1 15 HacheursbaydiNo ratings yet

- Soutenance Stage SgeDocument30 pagesSoutenance Stage SgebaydiNo ratings yet

- Exercices Redress ComDocument4 pagesExercices Redress ComHAMZA112233No ratings yet

- Projet Nucleair Youssef3Document8 pagesProjet Nucleair Youssef3baydiNo ratings yet

- ECE 2004-Controle Final PDFDocument6 pagesECE 2004-Controle Final PDFbaydiNo ratings yet

- Exercices Redress ComDocument4 pagesExercices Redress ComHAMZA112233No ratings yet

- Projet Nucleair Youssef3Document8 pagesProjet Nucleair Youssef3baydiNo ratings yet

- DS Version 2 PDFDocument1 pageDS Version 2 PDFbaydiNo ratings yet

- ECE 2006 Controle PDFDocument5 pagesECE 2006 Controle PDFbaydiNo ratings yet

- ECE 2004-Corrige PDFDocument6 pagesECE 2004-Corrige PDFbaydiNo ratings yet

- Compte RenduDocument21 pagesCompte Rendubaydi100% (1)

- Tubo CapilarDocument12 pagesTubo CapilarJuan Carlos SerranoNo ratings yet

- 2011 CtresEtrangers Exo1 Correction FamilleCurie 5 5pts PDFDocument2 pages2011 CtresEtrangers Exo1 Correction FamilleCurie 5 5pts PDFbaydiNo ratings yet

- Compte-Rendu Des TP Des Energies Renouvlables: Realise Par: ELGHACHI Brahim Bouskif Hiba MANDARISS MajdoulineDocument1 pageCompte-Rendu Des TP Des Energies Renouvlables: Realise Par: ELGHACHI Brahim Bouskif Hiba MANDARISS MajdoulinebaydiNo ratings yet

- Initiation Lab ViewDocument13 pagesInitiation Lab ViewbaydiNo ratings yet

- Lvcore1 2010 Exercisemanual French SampleDocument22 pagesLvcore1 2010 Exercisemanual French SamplebaydiNo ratings yet

- Compte-Rendu Des TP Des Energies RenouvlablesDocument1 pageCompte-Rendu Des TP Des Energies RenouvlablesbaydiNo ratings yet

- Compte RenduDocument21 pagesCompte Rendubaydi100% (1)

- Architecture Des Ordinateurs: Exercices: Exercices Sur La Partie Langage D'assemblageDocument11 pagesArchitecture Des Ordinateurs: Exercices: Exercices Sur La Partie Langage D'assemblageNouzha BoukoubaNo ratings yet

- Os 06 MemoryDocument20 pagesOs 06 Memoryben houria yassineNo ratings yet

- Cours-No-02 Calculateur Et InterfaçageDocument4 pagesCours-No-02 Calculateur Et Interfaçagestone freeNo ratings yet

- Controle Mars 2003 ECE Complet PDFDocument7 pagesControle Mars 2003 ECE Complet PDFbaydiNo ratings yet

- Cours 8085Document103 pagesCours 8085Abd ELmoumene Yasser100% (1)

- TD Mips (1076)Document2 pagesTD Mips (1076)Sabri Mahmoud100% (1)

- Série Exercices TD1Document2 pagesSérie Exercices TD1Colmain Nassiri100% (2)

- LISTEPIECESDocument17 pagesLISTEPIECESTA RA GUNo ratings yet

- Red Ac Microcon TR Ô LeurDocument6 pagesRed Ac Microcon TR Ô LeurSylvain NomenjanaharyNo ratings yet

- Presentation PICsDocument68 pagesPresentation PICsMila zNo ratings yet

- Ab Pic 16F84Document46 pagesAb Pic 16F84Kamal PcNo ratings yet

- Chapitre 2 Architecture Des OrdinateursDocument32 pagesChapitre 2 Architecture Des Ordinateursaya ni miniNo ratings yet

- SoumaireDocument3 pagesSoumairekolechi dzNo ratings yet

- OutputDocument134 pagesOutputDouar AymenNo ratings yet

- Un Microcontrôleur Est Un Circuit Intégré Rassemblant Dans Un Même Boitier Un MicroprocesseurDocument9 pagesUn Microcontrôleur Est Un Circuit Intégré Rassemblant Dans Un Même Boitier Un MicroprocesseuromarNo ratings yet

- Cours - Elec - Num - 3 - Partie IDocument47 pagesCours - Elec - Num - 3 - Partie IJacques Gregoire100% (1)

- Cours 3 - Le ProcesseurDocument61 pagesCours 3 - Le Processeurlisa lisaNo ratings yet

- Compte RenduDocument8 pagesCompte RenduGhizlaneNo ratings yet

- Chapitre 3Document14 pagesChapitre 3baha.jamel32No ratings yet

- Cours Electronique NumeriqueDocument44 pagesCours Electronique NumeriqueYoussef El AjraouiNo ratings yet

- Cours7 MemoiresDocument12 pagesCours7 MemoiresRoi du SilenceNo ratings yet

- Jeu D'instruction Du 6809Document2 pagesJeu D'instruction Du 6809arnaud tchouaniNo ratings yet

- C4 SequentielleDocument82 pagesC4 Sequentiellekhlifa alouiNo ratings yet

- ch2 - C - Logiques Séquentiels (Complet)Document85 pagesch2 - C - Logiques Séquentiels (Complet)DønuTsNo ratings yet

- Cours 1 Microprocesseurs - BoukhobzaDocument13 pagesCours 1 Microprocesseurs - BoukhobzaMohamed LMNo ratings yet

- TP2: Instructions Arithmétiques en 8086Document2 pagesTP2: Instructions Arithmétiques en 8086Meriem ZegNo ratings yet

- TD2 Aléas Du PipelineDocument9 pagesTD2 Aléas Du PipelineWejdène GuedriNo ratings yet

- ch5 CircuitssequentielsDocument14 pagesch5 CircuitssequentielsHicham Edd0% (1)

- Polycopie InfoIndus V2 16 ImprDocument83 pagesPolycopie InfoIndus V2 16 ImprkhaledNo ratings yet

- IntroductionassembleurDocument17 pagesIntroductionassembleurMohamed HmamouchNo ratings yet