Professional Documents

Culture Documents

UC3842B/3843B: Unisonic Technologies Co., LTD

Uploaded by

vannadioOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UC3842B/3843B: Unisonic Technologies Co., LTD

Uploaded by

vannadioCopyright:

Available Formats

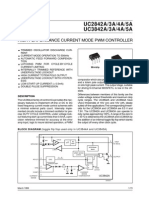

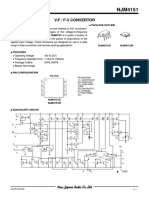

UNISONIC TECHNOLOGIES CO.

, LTD

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

HIGH PERFORMANCE

CURRENT MODE

CONTROLLERS

DESCRIPTION

The UTC UC3842B/3843B are specifically designed for off-line

and dc-to-dc converter applications offering the designer a

cost-effective solution with minimal external components.

The UC3842B has UVLO thresholds 16V (on) and 10V(off),

ideally suited for off-line converters. The UC3843B is tailored for

lower voltage applications having UVLO thresholds of 8.4V(on)

and 7.6V(off).

FEATURES Lead-free: UC3842BL

* Trimmed oscillator for precise frequency control UC3843BL

* Oscillator frequency guaranteed at 250kHz Halogen-free: UC3842BP

* Current mode operation to 500kHz UC3843BP

* Automatic feed forward compensation

* Latching PWM for cycle-by-cycle current limiting

* Internally trimmed reference with undervoltage lockout

* High current totem pole output

* Undervoltage lockout with hysteresis

* Low startup and operating current

ORDERING INFORMATION

Ordering Number

Package Packing

Normal Lead Free Halogen Free

UC3842B-D08-T UC3842BL-D08-T UC3842BP-D08-T DIP-8 Tube

UC3842B-S08-R UC3842BL-S08-R UC3842BP-S08-R SOP-8 Tape Reel

UC3843B-D08-T UC3843BL-D08-T UC3843BP-D08-T DIP-8 Tube

UC3843B-S08-R UC3843BL-S08-R UC3843BP-S08-R SOP-8 Tape Reel

www.unisonic.com.tw 1 of 11

Copyright © 2008 Unisonic Technologies Co., Ltd QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

PIN CONFIGURATION

COMP 1 8 VREF

VFB 2 7 VCC

CS 3 6 OUTPUT

RTCT 4 5 GND

PIN DESCRIPTIONS

PIN NO. PIN NAME I/O DESCRIPTION

1 COMP O Error amp output to provide loop compensation maintaing VFB at 2.5V

Error amp inverting input, The non-inverting input of error amp is 2.5V band

2 VFB I

gap reference

3 CS I Current sense input to PWM control gate drive of output

4 RTCT I To set oscillator frequency and maximum output duty cycle

5 GND Power ground

6 OUTPUT O To direct drive power MOSFET

7 VCC Power supply

8 VREF O 5V regulated output provides charging current for CT through RT

UNISONIC TECHNOLOGIES CO., LTD 2 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

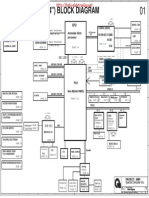

BLOCK DIAGRAM

UNISONIC TECHNOLOGIES CO., LTD 3 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

ABSOLUTE MAXIMUM RATINGS(Ta=25°C)

PARAMETER SYMBOL RATINGS UNIT

Total Power Supply and Zener Current (ICC + Iz) 30 mA

Output Current, Source or Sink (note1) Io 1.0 A

Output Energy (capacitive load per cycle) W 5.0 μJ

Current Sense and Voltage Feedback Inputs VIN -0.3 ~ +5.5 V

Error Amp. Output Sink Current IO(SINK) 10 mA

DIP-8 1250 mW

Power Dissipation PD

SOP-8 702 mW

Operating Junction Temperature TJ +150 °C

Operating Temperature TOPR 0 ~ +70 °C

Storage Temperature Range TSTG -65 ~ +150 °C

Note Absolute maximum ratings are those values beyond which the device could be permanently damaged.

Absolute maximum ratings are stress ratings only and functional device operation is not implied.

THERMAL DATA

PARAMETER SYMBOL RATINGS UNIT

DIP-8 100 °C/W

Thermal Resistance Junction to Ambient θJA

SOP-8 178 °C/W

ELECTRICAL CHARACTERISTICS

(0°C ≤TA≤70°C, VCC=15V [note 2], RT=10k, CT=3.3nF, unless otherwise specified)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT

REFERENCE SECTION

Output Voltage VREF Io=1.0mA, TJ =25°C 4.9 5.0 5.1 V

Line Regulation ΔVLINE VCC=12V ~ 25V 2.0 20 mV

Load Regulation ΔVLOAD Io=1.0mA ~ 20mA 3.0 25 mV

Temperature Stability TS 0.2 mV/°C

Total Output Variation VREF Line, Load, Temperature 4.82 5.18 V

Output Noise Voltage eN F=10kHz ~ 10Hz, TJ =25°C 50 uV

Long Term Stability S TA=125°C,1000Hrs 5 mV

Output Short Circuit Current ISC -30 -85 -180 mA

OSCILLATOR SECTION

TJ =25°C 49 52 55

Frequency F Ta=0°C ~ 70°C 48 56 kHz

TJ =25°C (RT=6.2k,CT=1.0nF) 225 250 275

Frequency Change with Voltage ΔfOSC/ΔV 12 ≤ VCC ≤25V 0.2 1.0 %

Frequency Change with

ΔfOSC/ΔT 0°C ≤TA ≤70°C 0.5 %

Temperature

Oscillator Voltage Swing(Peak to

VOSC 1.6 V

Peak)

TJ =25°C 7.8 8.8

Discharge Current Idischg 8.3 mA

0°C ≤TA ≤70°C 7.6 8.8

ERROR AMPLIFIER SECTION

Voltage Feedback Input VFB Vo=2.5V 2.42 2.50 2.58 V

Input Bias Current II(BIAS) VFB=5.0V -0.1 -2.0 μA

Open Loop Voltage Gain GVO 2 ≤Vo≤4V 65 90 dB

Unity Gain Bandwidth GBW TJ =25°C 0.7 1.0 MHz

Power Supply Rejection Ratio PSRR I2V≤Vcc≤25V 60 70 dB

Output Sink Current ISINK Vo=1.1V,VFB =2.7V 2.0 12 mA

Output Source Current ISOURCE Vo=5.0V,VFB=2.3V -0.5 -1.0 mA

Output Voltage Swing High State VOH VFB=2.3V, RL=15k to GND 5.0 6.2 V

UNISONIC TECHNOLOGIES CO., LTD 4 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

ELECTRICAL CHARACTERISTICS (Cont.)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT

Output Voltage Swing Low State VOL VFB=2.7V, RL=15k to VREF 0.8 1.1 V

CURRENT SENSE SECTION

Current Sense Input Voltage Gain GV (Note 3,4) 2.85 3.0 3.15 V/V

Maximum Current Sense Input

VI(THR) (Note 3) 0.9 1.0 1.1 V

Threshold

Power Supply Rejection Ratio PSRR 12≤Vcc≤25V (Note 3) 70 dB

Input Bias Current II(BIAS) -2 -10 μA

Propagation Delay tD(IN/OUT) Current Sense Input to Output 150 300 ns

OUTPUT SECTION

ISINK=20mA 0.1 0.4 V

Output Low Voltage VOL

ISINK=200mA 1.6 2.2 V

ISOURCE=20mA 13 13.5 V

Output High Voltage VOH

ISOURCE=200mA 12 13.4 V

Output Voltage with UVLO

VOL (UVLO) VCC=6.0V,ISINK=1.0mA 0.1 1.1 V

Activated

Output Voltage Rise Time tR TJ =25°C,CL=1nF 50 150 ns

Output Voltage Fall Time tF TJ =25°C,CL=1nF 50 150 ns

UNDER-VOLTAGE LOCKOUT SECTION

UTC UC3842B 14.5 16 17.5 V

Startup Threshold VTHR

UTC UC3843B 7.8 8.4 9 V

Min. Operating Voltage After UTC UC3842B 8.5 10 11.5 V

VCC(MIN)

Turn-on(Vcc) UTC UC3843B 7.0 7.6 8.2 V

PWM SECTION

MAX 94 96 %

Duty Cycle DC

MIN 0 %

Total DEVICE

VCC=6.5V for UC3843B

Power Startup Supply Current ICC+IC 0.3 0.5 mA

VCC=14V for UC3842B

Power Operating Supply Current ICC+IC Note2 12 17 mA

Power Supply Zener Voltage VZ ICC=25mA 30 36 V

Note: 1. Maximum Package power dissipation limits must be observed.

2. Adject VCC above the Startup threshold before setting to 15V.

3. This parameter is measured at the latch trip point with VFB=0V.

ΔV Output Compensation

4. Comparator gain is defined as : GV

ΔV Current Sense Input

UNISONIC TECHNOLOGIES CO., LTD 5 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

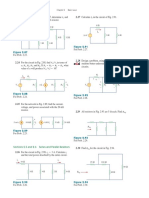

TYPICAL APPLICATION CIRCUIT

Open Loop Test Circuit

All of the parameters are not all tested in production, although been guaranteed. The timing and bypass capacitors

must be connected to pin 5 in a single point ground very closely. To sample the oscillator waveform, the transistor

and 5kΩ potentiometer are used, and also can apply an adjustable ramp to ISENSE pin.

VREF

2N UTC

2222 RT UC3842B/3843B

1 COMP VREF 8

100K

2 VFB VC 7 A V1

4.7K

3 ISENSE OUTPUT 6 OUTPUT

E/A 1K

0.1

ADJUST

ISENSE 5K 4 RT/CT GND 5

ADJUST

4.7K CT 0.1

1K/1W

Under Voltage Lockout

Under-Voltage Lock-Out: the output driver is biased to a high impedance state. To prevent activating the power

switch with output leakage current, pin 6 should be shunted to ground with a bleeder resistor.

Error Amp Configuration

UNISONIC TECHNOLOGIES CO., LTD 6 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

APPLICATION INFORMATION(Cont.)

Current Sense Circuit

Peak current (IS) is equaled:

IS(MAX)=1.0V/RS

There should be a small RC filter to suppress switch transients.

Oscillator Waveforms and Maximum Duty Cycle

LARGE RT

SMALL CT V4

VREF 8

RT

RT/RC 4 INTERINAL CLOCK

CT SMALL CT

LARGE RT

V4

GND 5

INTERINAL CLOCK

CT (Oscillator timing capacitor) can be charged by VREF through RT and discharged by an internal current source. At

discharge time, the internal clock signal blanks the output to the low. Both oscillator frequency and maximum duty

cycle can be determined by Selection of RT and CT. All charge and discharge times can be calculated by the next

formulas:

tC=0.55 RT CT

⎛ 0.0063R T − 2.7 ⎞

tD=RTCTIn ⎜⎜ ⎟

⎟

⎝ 0.0063R T − 4 ⎠

UNISONIC TECHNOLOGIES CO., LTD 7 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

APPLICATION INFORMATION(Cont.)

Shutdown Techniques

The UTC UC3842B’s shutdown can be accomplished by two ways: raise pin 3 above 1V; or pull pin 1 below a

voltage two diode drops above ground. Either method can cause the PWM comparator’s output to be high. Because

the PWM latch is reset dominant, the output will remain low until the next clock cycle after the shutdown condition at

pins 1 and/or 3 is removed.

Slope Compensation

UNISONIC TECHNOLOGIES CO., LTD 8 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

TYPICAL CHARACTERISTICS

Percent Output Deadtime, %DT.

Timing Resistor, RT (KΩ)

CT

=2

0

0p

F

CT

=5

.0

nF

CT

=1

0n

F

CT

=1

.0

nF

Maximum Output Duty Cycle, Dmax (%)

Discharge Current, Idischg (mA)

20mV/DIV

UNISONIC TECHNOLOGIES CO., LTD 9 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

TYPICAL CHARACTERISTICS(Cont.)

UNISONIC TECHNOLOGIES CO., LTD 10 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

TYPICAL CHARACTERISTICS(Cont.)

Output Saturation Voltage, Vsat (V)

Output Voltage, Vo

Supply Current, Icc (mA)

20V/DIV

Supply Current, Icc

UC3843B

UC3842B

100mA/DIV

UTC assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or

other parameters) listed in products specifications of any and all UTC products described or contained

herein. UTC products are not designed for use in life support appliances, devices or systems where

malfunction of these products can be reasonably expected to result in personal injury. Reproduction in

whole or in part is prohibited without the prior written consent of the copyright owner. The information

presented in this document does not form part of any quotation or contract, is believed to be accurate

and reliable and may be changed without notice.

UNISONIC TECHNOLOGIES CO., LTD 11 of 11

www.unisonic.com.tw QW-R103-012.D

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- INTEK HR-2040 Block DiagramDocument1 pageINTEK HR-2040 Block DiagramChris GuarinNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Measure PLL jitter using Cadence simulation toolsDocument34 pagesMeasure PLL jitter using Cadence simulation toolsAustin ShiNo ratings yet

- LefdefrefDocument32 pagesLefdefrefSandesh Kumar B VNo ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Topik 6 - ConverterDocument20 pagesTopik 6 - ConverterKartini M. Yusof NanaNo ratings yet

- Unisonic Technologies Co., LTD: High Performance Current Mode PWM ControllersDocument7 pagesUnisonic Technologies Co., LTD: High Performance Current Mode PWM ControllersCesra HMNo ratings yet

- Current Mode PWMDocument9 pagesCurrent Mode PWMluis albertoNo ratings yet

- Unisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitDocument8 pagesUnisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitallendohorizontNo ratings yet

- Uc3842b 3843BDocument10 pagesUc3842b 3843Bbob75No ratings yet

- Unisonic Technologies Co., LTD: Switching Regulator Controller (Low Voltage)Document7 pagesUnisonic Technologies Co., LTD: Switching Regulator Controller (Low Voltage)Tahir HussainNo ratings yet

- Unisonic Technologies Co., LTD: DC To DC Converter ControllerDocument10 pagesUnisonic Technologies Co., LTD: DC To DC Converter ControllerAbel RodriguezNo ratings yet

- UC3848Document12 pagesUC3848isaiasvaNo ratings yet

- DD Microtech Corp.: AMC3842B/43BDocument10 pagesDD Microtech Corp.: AMC3842B/43BDahlanNo ratings yet

- RP108J Series: Low Input Voltage 3A LDO Regulator OutlineDocument29 pagesRP108J Series: Low Input Voltage 3A LDO Regulator OutlineArie DinataNo ratings yet

- soldadora UTC3843DDocument9 pagessoldadora UTC3843DChristian ormeñoNo ratings yet

- Bay Linear Current Mode PWM Controller SpecificationsDocument11 pagesBay Linear Current Mode PWM Controller SpecificationsShashikant PatilNo ratings yet

- DatasheetDocument9 pagesDatasheetjim campbellNo ratings yet

- UC3842/UC3843/UC3844/UC3845: SMPS ControllerDocument12 pagesUC3842/UC3843/UC3844/UC3845: SMPS ControllerMohamed HaddadNo ratings yet

- Unisonic Technologies Co., LTD: 4 Pin Dip Phototransistor PhotocouplerDocument7 pagesUnisonic Technologies Co., LTD: 4 Pin Dip Phototransistor PhotocouplerAbdul Rauf MughalNo ratings yet

- 3842a DatasheetDocument8 pages3842a DatasheetVịnh DemoNo ratings yet

- AZ3842 PWM Controller Data Sheet SummaryDocument13 pagesAZ3842 PWM Controller Data Sheet SummaryEngr Khalid IqbalNo ratings yet

- Unisonic Technologies Co., LTD: Telephone Tone RingerDocument5 pagesUnisonic Technologies Co., LTD: Telephone Tone Ringerzero cloudNo ratings yet

- BL0940 APPNote TSSOP14 V1.04 ENDocument6 pagesBL0940 APPNote TSSOP14 V1.04 ENGeorgi IlievNo ratings yet

- Operacional de Alto GanhoDocument11 pagesOperacional de Alto Ganhorogerio pessanha dos santosNo ratings yet

- ULN2804Document5 pagesULN2804vka_princeNo ratings yet

- TL1451Document14 pagesTL1451Teyfik koyuncuNo ratings yet

- Unisonic Technologies Co., LTD: PWM Control 3A Step-Down ConverterDocument8 pagesUnisonic Technologies Co., LTD: PWM Control 3A Step-Down ConverterLyw LywNo ratings yet

- IP4002CR DatasheetDocument7 pagesIP4002CR DatasheetJose BenavidesNo ratings yet

- 3842Document12 pages3842luisNo ratings yet

- UTC TL1451 Linear Integrated Circuit: Dual Pulse-Width-Modulation Control CircuitsDocument5 pagesUTC TL1451 Linear Integrated Circuit: Dual Pulse-Width-Modulation Control CircuitsMarcos Gomes MisselNo ratings yet

- LOW POWER QUAD OP AMPSDocument11 pagesLOW POWER QUAD OP AMPSАлександрNo ratings yet

- Unisonic Technologies Co., LTD: Eight High Voltage, High Current Darlington ArraysDocument5 pagesUnisonic Technologies Co., LTD: Eight High Voltage, High Current Darlington ArraysTojo BasheerNo ratings yet

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerDocument15 pagesUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllertoajuiceNo ratings yet

- SMPS Controller: Features DescriptionDocument11 pagesSMPS Controller: Features DescriptionAdah BumboneNo ratings yet

- UC3846Document10 pagesUC3846Polo Soldas Polo SoldasNo ratings yet

- DP8600C YwDocument9 pagesDP8600C YwSURESH CHANDRA ROUTNo ratings yet

- SE8117TADocument7 pagesSE8117TAdavid.gjeorgevskiNo ratings yet

- Uc3863 Utc U863 PDFDocument9 pagesUc3863 Utc U863 PDFShailesh VajaNo ratings yet

- Telefono l3240b Twotone RingerDocument6 pagesTelefono l3240b Twotone Ringerblackbeast79No ratings yet

- PD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Document5 pagesPD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Osama YaseenNo ratings yet

- Dual Operational Amplifier: Features DescriptionDocument6 pagesDual Operational Amplifier: Features DescriptionAmin MahfudiNo ratings yet

- Low Power Dual Operational Amplifiers Az358/358CDocument13 pagesLow Power Dual Operational Amplifiers Az358/358CMarissa ValdezNo ratings yet

- AT2596-IATDocument13 pagesAT2596-IATlaboratorio eletronicoNo ratings yet

- 8205Document16 pages8205sonytinNo ratings yet

- Unisonic Technologies Co., LTD: Vertical Deflection Output CircuitDocument5 pagesUnisonic Technologies Co., LTD: Vertical Deflection Output CircuitNerza ElectronicsNo ratings yet

- CR 6848 TDocument14 pagesCR 6848 Tndc20002003No ratings yet

- Novel Low Cost Green-Power PWM Controller: FeaturesDocument15 pagesNovel Low Cost Green-Power PWM Controller: FeaturesmehmoodNo ratings yet

- MC34063AB - MC34063AC MC34063EB - MC34063EC: DC/DC Converter Control CircuitsDocument23 pagesMC34063AB - MC34063AC MC34063EB - MC34063EC: DC/DC Converter Control CircuitsBoglárka TurcsánNo ratings yet

- SK6406 PDFDocument6 pagesSK6406 PDFjddgNo ratings yet

- 5-Channel Driver (BTL:4ch, H-Bridge:1ch) : For CD and DVD PlayersDocument8 pages5-Channel Driver (BTL:4ch, H-Bridge:1ch) : For CD and DVD PlayersSony KusumoNo ratings yet

- APW7159ADocument23 pagesAPW7159AVoicu AdrianNo ratings yet

- Precision Waveform Generator/Voltage Controlled Oscillator FeaturesDocument12 pagesPrecision Waveform Generator/Voltage Controlled Oscillator FeaturesCharles Tineo0% (1)

- CT5503SDocument12 pagesCT5503SSubhash Digambar VisalNo ratings yet

- Linear Integrated Circuit: Current Mode PWM ControllerDocument6 pagesLinear Integrated Circuit: Current Mode PWM ControllernermeenelnaggarNo ratings yet

- KA3842A IC Datasheet PDFDocument5 pagesKA3842A IC Datasheet PDFagarcosNo ratings yet

- FP5139 Ic Dao Dong Bost NguonDocument14 pagesFP5139 Ic Dao Dong Bost Nguondinh vinh nguyenNo ratings yet

- UC3843 ChipsWinnerDocument11 pagesUC3843 ChipsWinnerPareNo ratings yet

- UC3845ANDocument15 pagesUC3845ANMiloud ChouguiNo ratings yet

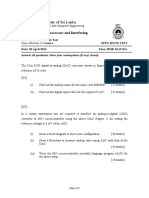

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerDocument16 pagesUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaNo ratings yet

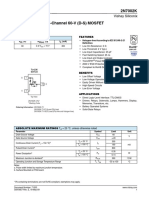

- 2n7002k Sot-23 VishayDocument9 pages2n7002k Sot-23 VishayKST5No ratings yet

- APM4305KDocument10 pagesAPM4305KvannadioNo ratings yet

- 2n7002k Sot-23 VishayDocument9 pages2n7002k Sot-23 VishayKST5No ratings yet

- Tps 51225Document31 pagesTps 51225AENo ratings yet

- Features General Description: 5A Low Dropout Fast Response Positive Adjustable Regulator and Fixed 3.3VDocument13 pagesFeatures General Description: 5A Low Dropout Fast Response Positive Adjustable Regulator and Fixed 3.3VchoppersureNo ratings yet

- SM3317NSQA: Features Pin DescriptionDocument13 pagesSM3317NSQA: Features Pin DescriptionvannadioNo ratings yet

- A04d1 SW9Document41 pagesA04d1 SW9iskenderbeyNo ratings yet

- PCF 817Document12 pagesPCF 817claudiocbamtNo ratings yet

- Datasheet DIODOSDocument6 pagesDatasheet DIODOSvannadioNo ratings yet

- UC3842B/3843B: Unisonic Technologies Co., LTDDocument11 pagesUC3842B/3843B: Unisonic Technologies Co., LTDvannadioNo ratings yet

- Sw-P201 Block DiagramDocument1 pageSw-P201 Block DiagramFausto PillajoNo ratings yet

- Voltage Shunt Feedback AmplifierDocument4 pagesVoltage Shunt Feedback Amplifierersan turkmanNo ratings yet

- Switch Level ModelingDocument14 pagesSwitch Level Modelingvenkatesh kumarNo ratings yet

- Gateeasy D To A PDFDocument3 pagesGateeasy D To A PDFShubham kumarNo ratings yet

- Icom Ic 2800HDocument50 pagesIcom Ic 2800HradioclubcopiapoNo ratings yet

- Ecx4236 Cat 2013Document2 pagesEcx4236 Cat 2013Isuru BuddikaNo ratings yet

- 99.smith CH05BDocument52 pages99.smith CH05BAbdullah Ashraf ElkordyNo ratings yet

- Linear Wave ShapingDocument29 pagesLinear Wave Shapingapnrao100% (6)

- 4-20ma 2 - 3 WireDocument31 pages4-20ma 2 - 3 WireLawrence Okyere OforiNo ratings yet

- DR D JacksonDocument3 pagesDR D JacksonAmnaMaqboolNo ratings yet

- Motorola - MC14053B PDFDocument9 pagesMotorola - MC14053B PDFVieira BrunoNo ratings yet

- NCP 81174Document18 pagesNCP 81174techgamebr85No ratings yet

- Mbed Course Notes - Analog Input and OutputDocument24 pagesMbed Course Notes - Analog Input and Outputamhosny64No ratings yet

- Design and Implementation of Four Quadrant DC Drive Using ChopperDocument5 pagesDesign and Implementation of Four Quadrant DC Drive Using ChopperDayguel EvansNo ratings yet

- V-F / F-V Convertor: General Description Package OutlineDocument14 pagesV-F / F-V Convertor: General Description Package OutlineIlyes KHOUILDINo ratings yet

- Lab Report 5 - The Triangular Waveform Generator and The Astable MultivibratorDocument5 pagesLab Report 5 - The Triangular Waveform Generator and The Astable MultivibratorYasmim de SouzaNo ratings yet

- Digital Logic and Microprocessor: Dr.M.Sindhuja Assistant Professor (Senior Grade) School of Electronics VIT, ChennaiDocument42 pagesDigital Logic and Microprocessor: Dr.M.Sindhuja Assistant Professor (Senior Grade) School of Electronics VIT, ChennaiNithish Kumar A NNo ratings yet

- Lecture 2 IO Ports and 8051 CircuitDocument3 pagesLecture 2 IO Ports and 8051 Circuit12343567890No ratings yet

- MIT2 14S14 Prob Archive PDFDocument674 pagesMIT2 14S14 Prob Archive PDFKamal PatelNo ratings yet

- Exercise On Analog Circuits: PHYS 331: Junior Physics Laboratory IDocument6 pagesExercise On Analog Circuits: PHYS 331: Junior Physics Laboratory Iviso167No ratings yet

- Assignment 1Document4 pagesAssignment 1azimNo ratings yet

- Cascade Amplifier CircuitDocument4 pagesCascade Amplifier Circuit4011 Harshada MohiteNo ratings yet

- FM transmitter direct reactance methodDocument2 pagesFM transmitter direct reactance methodnirmal_inboxNo ratings yet

- ULN2801A, ULN2802A, ULN2803A, ULN2804A: DescriptionDocument14 pagesULN2801A, ULN2802A, ULN2803A, ULN2804A: DescriptionAnh ĐườngNo ratings yet

- Analog Circuits & DesignDocument2 pagesAnalog Circuits & Designlalitkumar bannagareNo ratings yet

- Wien Bridge.Document11 pagesWien Bridge.Enock OmariNo ratings yet