Professional Documents

Culture Documents

GPIO Interrupt

Uploaded by

keyboard2014Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

GPIO Interrupt

Uploaded by

keyboard2014Copyright:

Available Formats

Signal flow/setup for External Interrupt EXTIx, x = 0...

15

SYSCFG module GPIO module

PAx mode Pin

0

1 PBx PAx

EXTIx 2 PCx Configure PAx

: : as input (00)

:

Select source for EXTIx 15

: GPIOA –> MODER

4

4 bits each

0000 = PAx

0001 = PBx EXTI3 EXTI2 EXTI1 EXTI0

: SYSCFG –> EXTICR[0]

EXTI module

CPU NVIC

For all EXTIx registers: Bit n controls EXTIn

Enable NVIC_EnableIRQ(n); EXTI –> IMR

interrupt mask interrupt mask

EN EN (enable) EXTI –> FTSR

EN EXTI –> RTSR

IRQ EXTI –> PR

Pending EXTIx Pending EXTIx

EXTIx

flag flag edge

_ _ enable_irq( ); EXTIx

_ _ disable_irq( ); Set when EXTIx activates Set by HW enable select falling

Clear when intr. handler exits Clear by SW this and/or

-------------- interrupt rising edge

NVIC_ClearPendingIRQ(n);

1 of 45, passed

clear pending flag

by NVIC to CPU

NVIC_SetPriority(intr. #, value);

value = priority of intr. #

You might also like

- STM32Document33 pagesSTM32Irshan NazirNo ratings yet

- External InterruptDocument4 pagesExternal Interruptsiva kumaarNo ratings yet

- 10 Interrupt v22Document29 pages10 Interrupt v22Pipat NakasenoNo ratings yet

- 04 - Cortex-M0 & NUC029 IntroductionDocument65 pages04 - Cortex-M0 & NUC029 IntroductionDharmendra SavaliyaNo ratings yet

- RFNoC Tutorial: FPGA DesignDocument64 pagesRFNoC Tutorial: FPGA DesignmateusmaxiNo ratings yet

- PCF8574 Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionDocument41 pagesPCF8574 Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionAndre BinaknasanaNo ratings yet

- Pcf8574 DatasheetDocument44 pagesPcf8574 DatasheetSütő László BalázsNo ratings yet

- PCF8574 Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionDocument41 pagesPCF8574 Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 Descriptionzbhp z100% (1)

- Atmel 0053Document1 pageAtmel 0053namerNo ratings yet

- ARM STM32F407 InterruptsDocument38 pagesARM STM32F407 Interruptsronaldo008100% (2)

- I2C To Parallel Port Converter For 7-Segment Interface Pcf8574Document36 pagesI2C To Parallel Port Converter For 7-Segment Interface Pcf8574DHANAPRAKAASHNo ratings yet

- ARM Based MicrocontrollersDocument19 pagesARM Based MicrocontrollersNavin KhatriNo ratings yet

- 7KE85 ConfigDocument4 pages7KE85 ConfigAldo Bona HasudunganNo ratings yet

- Golam Mostafa: Atmega8 Risc Microcontroller Interfacing and System DesignDocument60 pagesGolam Mostafa: Atmega8 Risc Microcontroller Interfacing and System DesignRuchit SankhesaraNo ratings yet

- 4 IO - MUX and GPIO Matrix (GPIO, IO - MUX) : 4.1 OverviewDocument42 pages4 IO - MUX and GPIO Matrix (GPIO, IO - MUX) : 4.1 OverviewDooLooNo ratings yet

- Sattcon 05Document8 pagesSattcon 05simon.nordanclub.managementNo ratings yet

- 10주차 - 2차시 - ARM을 이용한 7-Segment 제어 실습Document52 pages10주차 - 2차시 - ARM을 이용한 7-Segment 제어 실습kimms99No ratings yet

- Fpga InterruptDocument22 pagesFpga InterruptAkhil K RNo ratings yet

- Low-Cost One-Chip Multi-Effects DSP V1000: 1. General DescriptionDocument13 pagesLow-Cost One-Chip Multi-Effects DSP V1000: 1. General DescriptionHermanherdiantoNo ratings yet

- PCF8574A Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionDocument38 pagesPCF8574A Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionmercyjohnNo ratings yet

- PCF 8574 ADocument38 pagesPCF 8574 ADilu_VarmaNo ratings yet

- IchipDocument137 pagesIchipSivaraman AlagappanNo ratings yet

- PCF 8574 ADocument41 pagesPCF 8574 ADecastel GompouNo ratings yet

- Micro ControllerDocument21 pagesMicro Controllerkrishn_blazeNo ratings yet

- Features... : Programmable Logic Device FamilyDocument46 pagesFeatures... : Programmable Logic Device FamilyrolandseNo ratings yet

- 16C550 UartDocument18 pages16C550 UartChilly KewlNo ratings yet

- Gigabyte Ga-Z87x-D3h Rev 1.0 - Structure Introductions Power Sequence Measure PointsDocument18 pagesGigabyte Ga-Z87x-D3h Rev 1.0 - Structure Introductions Power Sequence Measure PointsJerzy LisowskiNo ratings yet

- InterruptDocument21 pagesInterruptpriyanka100% (2)

- P1N26239 Min PorPosDocument3 pagesP1N26239 Min PorPosjosseNo ratings yet

- CreatorDocument19 pagesCreatorAhmad ZakiNo ratings yet

- Tca9555 Low-Voltage 16-Bit I C and Smbus I/O Expander With Interrupt Output and Configuration RegistersDocument46 pagesTca9555 Low-Voltage 16-Bit I C and Smbus I/O Expander With Interrupt Output and Configuration RegistersLuiz LuizNo ratings yet

- United International University: Use of External InterruptDocument8 pagesUnited International University: Use of External InterruptNura Alam ProtikNo ratings yet

- Satellite Transceiver: Stid337Document2 pagesSatellite Transceiver: Stid337Hakan SyblNo ratings yet

- Crash Course: 3 Hours Introduction To Pic Microcontroller byDocument43 pagesCrash Course: 3 Hours Introduction To Pic Microcontroller bysadariahNo ratings yet

- ARM7Document76 pagesARM7Bajrang sisodiyaNo ratings yet

- ARM STM32F407 InterruptsDocument39 pagesARM STM32F407 InterruptsmoeinNo ratings yet

- Siprotec 5 Configuration Nov 18, 2020 3:09 AMDocument4 pagesSiprotec 5 Configuration Nov 18, 2020 3:09 AMPằngPằngChiuChiuNo ratings yet

- U3 PIC 18F Microcontroller InterruptsDocument59 pagesU3 PIC 18F Microcontroller Interruptsmadhukar v nimbalkarNo ratings yet

- Lec 8 NotesDocument9 pagesLec 8 NotesAlan BensonNo ratings yet

- 22a Lab5 IntroDocument6 pages22a Lab5 Introkarthikp207No ratings yet

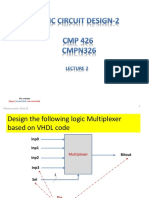

- Logic Lec - 2 - 2022Document20 pagesLogic Lec - 2 - 2022Ahmed eltookhyNo ratings yet

- en sc05 Slimline v4.0 Data SheetDocument8 pagesen sc05 Slimline v4.0 Data SheetKyung-Rok OhNo ratings yet

- 6MD85 PDFDocument4 pages6MD85 PDFGanesh DuraisamyNo ratings yet

- Lec5 InterruptsDocument23 pagesLec5 Interruptsassala benmalekNo ratings yet

- Fifo Controller PresentationDocument26 pagesFifo Controller PresentationthemikulNo ratings yet

- 8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT89S51Document30 pages8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT89S51Arif Febrian MuhammadNo ratings yet

- ESD NPTEL SummaryDocument35 pagesESD NPTEL SummaryrahulpikaleNo ratings yet

- C Sec Eiot Unit 2Document32 pagesC Sec Eiot Unit 2209X1A0467 KOTLA ANUSHANo ratings yet

- Understanding InterruptsDocument21 pagesUnderstanding InterruptsArun Nath K SNo ratings yet

- SYS3041 Cours Microprocesseur Part2Document40 pagesSYS3041 Cours Microprocesseur Part2mathiasdimeglio58No ratings yet

- O (PLC) - T (Robot)Document6 pagesO (PLC) - T (Robot)Gabriel GarciaNo ratings yet

- rm0455-STM32H7A3 - 7B3 및 STM32H7B0 Value line 고급 Arm® 기반 32비트 MCU7-14Document269 pagesrm0455-STM32H7A3 - 7B3 및 STM32H7B0 Value line 고급 Arm® 기반 32비트 MCU7-14임대진No ratings yet

- Output Devices Supported by Xitron: 2 2 2 2 Made in The UsaDocument2 pagesOutput Devices Supported by Xitron: 2 2 2 2 Made in The UsaFelipe VasquezNo ratings yet

- FPGA Summer ReportDocument18 pagesFPGA Summer ReportAbhishek RajNo ratings yet

- PIC24FJ64GA002 Interrupt VectorsDocument10 pagesPIC24FJ64GA002 Interrupt Vectorsocelot_and_allNo ratings yet

- LogicDesign 8 2Document21 pagesLogicDesign 8 2hwangmbwNo ratings yet

- mcs7840 DatasheetDocument41 pagesmcs7840 DatasheetDenis KalabinNo ratings yet

- BRKDCN 3040Document105 pagesBRKDCN 3040Tomas MigilinskasNo ratings yet

- 08 - Lecture8Document26 pages08 - Lecture8adeelNo ratings yet

- EK-RA6M4 - Evaluation Kit For RA6M4 MCU Group - RenesasDocument6 pagesEK-RA6M4 - Evaluation Kit For RA6M4 MCU Group - Renesaskeyboard2014No ratings yet

- An Easy Way To Build A Tree in JavaScript Using Object References - TypeOfNaNDocument6 pagesAn Easy Way To Build A Tree in JavaScript Using Object References - TypeOfNaNkeyboard2014No ratings yet

- Ces 2017Document32 pagesCes 2017keyboard2014No ratings yet

- Release NoteDocument28 pagesRelease Notekeyboard2014No ratings yet

- Bootloader Design Considerations 90003207ADocument12 pagesBootloader Design Considerations 90003207Akeyboard2014No ratings yet

- Concurrency Freaks - Interrupt Handler in C11 With AtomicsDocument4 pagesConcurrency Freaks - Interrupt Handler in C11 With Atomicskeyboard2014No ratings yet

- Start Here NXP MFS 1.5.1.1 PDFDocument24 pagesStart Here NXP MFS 1.5.1.1 PDFkeyboard2014No ratings yet

- BSP Porting Guide L3.0.35 1.1.0Document63 pagesBSP Porting Guide L3.0.35 1.1.0keyboard2014No ratings yet

- US4903192 PID Fuzzy LogicDocument25 pagesUS4903192 PID Fuzzy Logickeyboard2014No ratings yet

- Nonlinear System Identification of Rapid Thermal ProcessingDocument7 pagesNonlinear System Identification of Rapid Thermal Processingkeyboard2014No ratings yet

- Tutorialv0 4Document11 pagesTutorialv0 4keyboard2014No ratings yet

- Setup of Rotary Flexible LinkDocument4 pagesSetup of Rotary Flexible Linkkeyboard2014No ratings yet

- Tutorial EZ430-RF2500Document112 pagesTutorial EZ430-RF2500Paulo L. MuñozNo ratings yet

- D3 PrefsDocument1 pageD3 PrefsfreebookmanNo ratings yet

- Test #1 AMATYC Student Mathematics League October/November 2006Document3 pagesTest #1 AMATYC Student Mathematics League October/November 2006keyboard2014No ratings yet

- Homotopy Perturbation Based Linearization of Nonlinear Heat Transfer Dynamic PDFDocument14 pagesHomotopy Perturbation Based Linearization of Nonlinear Heat Transfer Dynamic PDFkeyboard2014No ratings yet

- 042 DOWNLOAD P1.1 Push Button Lab ManualDocument29 pages042 DOWNLOAD P1.1 Push Button Lab Manualkeyboard2014No ratings yet

- 066 DOWNLOAD Using Two General Purpose Timers Lab ManualDocument8 pages066 DOWNLOAD Using Two General Purpose Timers Lab Manualkeyboard2014No ratings yet

- AMATYC2003 FallDocument2 pagesAMATYC2003 FallleonutdoughNo ratings yet

- Timers 1Document22 pagesTimers 1keyboard2014No ratings yet

- AN4345Document12 pagesAN4345keyboard2014No ratings yet

- SML Fa05Document3 pagesSML Fa05keyboard2014No ratings yet

- Pt100 Transmitter MicrochipDocument8 pagesPt100 Transmitter Microchipem01803257No ratings yet

- AMATYC Student Msthematics League: I + Atcsec: + Arccot: + Arccot I ? 4 4 4 5 21Document3 pagesAMATYC Student Msthematics League: I + Atcsec: + Arccot: + Arccot I ? 4 4 4 5 21keyboard2014No ratings yet

- ECP Lab2 First Order r6Document5 pagesECP Lab2 First Order r6keyboard2014No ratings yet

- ECP Lab1 Simulink Intro r4Document6 pagesECP Lab1 Simulink Intro r4keyboard2014No ratings yet

- SML Fa01Document2 pagesSML Fa01keyboard2014No ratings yet

- SML Fa01Document2 pagesSML Fa01keyboard2014No ratings yet

- AN3905Document24 pagesAN3905keyboard2014No ratings yet

- Asmg1025 PDFDocument102 pagesAsmg1025 PDFJackson SilvaNo ratings yet

- Best 59 Hardware Interview QuestionsDocument2 pagesBest 59 Hardware Interview QuestionsKhogen MairembamNo ratings yet

- ThinkCentre M70q Gen 3 11T4003RFJDocument2 pagesThinkCentre M70q Gen 3 11T4003RFJhugoriverap09No ratings yet

- CategoryDocument590 pagesCategoryFail ProjectNo ratings yet

- High Performance Computing-1 PDFDocument15 pagesHigh Performance Computing-1 PDFPriyanka JadhavNo ratings yet

- DSE 18.1F Computer Architecture and NetworkingDocument3 pagesDSE 18.1F Computer Architecture and Networkingpakaya tamaNo ratings yet

- 70534BIR Form 1921 - Annex B PDFDocument1 page70534BIR Form 1921 - Annex B PDFJunar MadaliNo ratings yet

- FChapter 9 - Memory Design in 68KDesignDocument22 pagesFChapter 9 - Memory Design in 68KDesignShashitharan PonnambalanNo ratings yet

- Chapter 9. Embedded Systems: Computer OrganizationDocument20 pagesChapter 9. Embedded Systems: Computer Organizationapi-3723664No ratings yet

- c6h Xoc Guide v05Document7 pagesc6h Xoc Guide v05jac1kNo ratings yet

- Ryans Product Book-June 2016-Issue 89Document52 pagesRyans Product Book-June 2016-Issue 89Ryans Computers Ltd.No ratings yet

- Paper SizeDocument27 pagesPaper SizemdeenkNo ratings yet

- Sata 6G Not Working in Asus Bios - (Solved) - StorageDocument26 pagesSata 6G Not Working in Asus Bios - (Solved) - StorageBoboNo ratings yet

- Inglés Técnico CFGM SMR - Unit3Document16 pagesInglés Técnico CFGM SMR - Unit3Jesús GómezNo ratings yet

- Automatic Leveling Tutorial - NEP2Document3 pagesAutomatic Leveling Tutorial - NEP2ptrovNo ratings yet

- Canon MP150 Service ManualDocument25 pagesCanon MP150 Service ManualSeena ZharaaNo ratings yet

- ECE 4006 Project Proposal and Presentation: Group Name: Altera NIOS Robot GroupDocument6 pagesECE 4006 Project Proposal and Presentation: Group Name: Altera NIOS Robot GroupLuela Del Rosario CabreraNo ratings yet

- Blinking Lights On The HP LaserJet 1018 and 1020 Printer Series - HP® Customer SupportDocument7 pagesBlinking Lights On The HP LaserJet 1018 and 1020 Printer Series - HP® Customer SupportRaghuSrinivasanNo ratings yet

- SVT Programming Manual - tx57Document202 pagesSVT Programming Manual - tx57DjuricaPrcomanNo ratings yet

- 11-3-2019 001 Bizgram Daily DIY PricelistDocument14 pages11-3-2019 001 Bizgram Daily DIY PricelistSaasidharan SaasiNo ratings yet

- List Lelang Salvage PT Harrisma Informatika JayaDocument9 pagesList Lelang Salvage PT Harrisma Informatika JayaRandy IranggaNo ratings yet

- IoregDocument310 pagesIoregPFENo ratings yet

- PsDocument324 pagesPsuturn87No ratings yet

- GPIB-PCII-IIA Data Sheet 4gpib681Document1 pageGPIB-PCII-IIA Data Sheet 4gpib681PeterNo ratings yet

- Input/Output: William Stallings, Computer Organization and Architecture, 9 EditionDocument35 pagesInput/Output: William Stallings, Computer Organization and Architecture, 9 EditionVũ Tâm MinhNo ratings yet

- Software For Educators and StudentsDocument8 pagesSoftware For Educators and StudentsAivie ManaloNo ratings yet

- William Stallings Computer Organization and Architecture 8th Edition Cache MemoryDocument71 pagesWilliam Stallings Computer Organization and Architecture 8th Edition Cache MemoryRehman HazratNo ratings yet

- Org Four: Int 21H and INT 10H Programming and MacrosDocument31 pagesOrg Four: Int 21H and INT 10H Programming and MacrosBuket CüvelenkNo ratings yet

- What Are Peripheral Devices??Document57 pagesWhat Are Peripheral Devices??Mainard LacsomNo ratings yet

- Dell Precision T5500 BrochureDocument2 pagesDell Precision T5500 BrochurePablo Ardiand GilbertoNo ratings yet