Professional Documents

Culture Documents

Analog Design Techniques

Uploaded by

Shiva RamOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analog Design Techniques

Uploaded by

Shiva RamCopyright:

Available Formats

Analog Circuit Design Techniques

for Low-Temperature

Mixed-Signal CMOS Systems

Benjamin J. Blalock & Stephen C. Terry

bblalock@ece.utk.edu

INSYTE Lab

(Integrated Circuits & Systems Laboratory)

www.ece.utk.edu/insyte

May 14, 2003

The University of Tennessee

Knoxville, Tennessee

B. Blalock & S. Terry - 1

Low Temperature Analog Overview

• Commercial, discrete electronics vs. Custom,

monolithic systems

• System level design of low temperature analog

filters and data converters

• CMOS modeling for low temperature

• Circuit topologies for low temperature analog

B. Blalock & S. Terry - 2

Commercial vs. Custom Electronics

• Commercial electronics generally perform well

over a large temperature range

• Custom electronics allow high levels of

integration, thus the number of individual chips is

reduced and reliability is increased

• Might make sense to use some commercial

electronics for some specialized functions (e.g.

voltage reference)

B. Blalock & S. Terry - 3

System Level Design Considerations

• Data converter design for mixed-signal systems

for low temperature environments is a challenge

for several reasons:

– Transistor characteristics change significantly with

temperature (VTO !, µ !)

– 1/f noise may be constant with temperature

– Difficult to match a large number of passive devices

over a wide range of temperatures

– Standard reference circuits generally don’t operate well

over a large temperature range

B. Blalock & S. Terry - 4

System Level Design Considerations

• General data converter design approach – minimize the

number of passive components required for matching

Comparison of Popular Data Converter Architectures

Architecture Number of components required to

match one another

Flash 2n resistors, 2n – 1 comparators

Successive Approximation 3n + 1 resistors (assuming R-2R DAC)

Pipeline/Recirculating 4 capacitors in DAC/Gain Block (assumes

fully differential & 1.5 bit/stage)

Sigma-delta 4 capacitors in S.C. integrator (assumes

fully differential)

• Key trade-off – pipeline and sigma-delta trade component matching for

high performance op-amps – thus the converter design becomes an op-

amp design problem

B. Blalock & S. Terry - 5

Pipeline ADC

• Pipeline ADC ideal for high-speed, moderate resolution extreme

environment applications

– Very tolerant of comparator offsets when redundancy is used

– Matching is only required within each pipeline stage, not across the

entire pipeline

– With redundancy, resolution generally limited by noise for moderate

accuracy (≤ 10 bit) applications

Stage 1 Stage 2 Stage 3 Stage N

Digital Error Correction Digital

Out

Analog

In Residue

Out

S/H + G=2

ADC DAC

Digital

Out

B. Blalock & S. Terry - 6

Sigma-Delta ADC

• Sigma-delta ADC is ideal for low-speed, high resolution extreme

environment applications

– H(z) implemented as a switched-capacitor integrator

– Very tolerant to comparator offset

– Decimation filter required to convert digital output stream to digital words

Analog

In Digital

+ H(z) + Out

• Bottom line: Sigma-Delta & Pipeline ADCs suitable for extreme

environment applications require high-performance OTAs

B. Blalock & S. Terry - 7

CMOS Analog Design for Low Temp

• Important Considerations:

– Vendor models not specified at cryogenic temperatures

– Standard circuit topologies may not work over large

temperature range

– Standard design equations not valid for large

temperature range

B. Blalock & S. Terry - 8

Low Temperature CMOS Modeling

• Vendor supplied models generally not specified at

cryogenic temperatures

• Options for low temperature modeling:

– Extract model parameters at low temperatures (EKV

might be a good option)

– Extract critical device parameters (VTO, µ) at different

temperatures and create ‘binned’ model

B. Blalock & S. Terry - 9

CMOS Analog Design for Low Temp

• Analog CMOS design methods normally focus on one operating region

(weak, moderate, or strong inversion)

• However for a fixed bias current, operating region will change with

temperature

kT

UT =

q

−1

T

µ p = µ0 p

300

−1.4

T

µ n = µ0n

300

B. Blalock & S. Terry - 10

OTA Design – Constant gm Biasing

• Constant gm biasing is critical for regulating bandwidth and

noise floor over a wide temperature range

VBIAS

• The Beta-multiplier is a popular constant gm bias

1:1

circuit, however the standard analysis assumes

either strong or weak inversion

VCASP • Analysis of this circuit using the EKV model

provides a design equation that describes

operation at any inversion level (IC)

− 1

( )

IC

1 2 e −

gm = ⋅ ln 1 − e IC

(W/L) K(W/L) n ⋅ R IC e IC / K − 1

R • Choose K ≤ 2 for low temperature sensitivity

B. Blalock & S. Terry - 11

OTA Design – Constant gm Biasing

• An important limitation of the resistively biased

beta-multiplier is that the bias current is first order

dependent on the absolute value of a resistor

VBIAS • Switched capacitor beta-

1:1 (W/L) << 1

multipliers have two key

advantages over their resistive

VCASP counterparts

– Absolute accuracy of

1 monolithic capacitors better

R AV =

(W/L) K(W/L)

f CLK ⋅ C than resistors

– Monolithic capacitors have

almost zero temperature

coefficient

B. Blalock & S. Terry - 12

OTA Design – LVCCM Biasing

• Biasing of LVCCMs is very difficult over a wide

temperature range because of:

– Threshold and mobility shift with temperature

– Constant gm bias circuits adapt bias current to

temperature – thus the LVCCM must remain in

saturation over a wide range of currents

– Most LVCCM bias techniques assume either weak or

strong inversion operation, in reality one often wishes to

operate in moderate inversion

B. Blalock & S. Terry - 13

OTA Design – LVCCM Biasing – 1

• The VGS-multiplier is a new LVCCM bias technique developed at UT

• The salient feature of the VGS-multiplier is that it is guaranteed to

maximize the VDS on both the top and bottom device in the mirror –

independent of bias current, temperature, or any other circuit or

environmental characteristics, therefore maximizing rout

IBIAS

R

R

- IOUT

+

R

R

M1

R

R

M2

VGS-Multiplier Concept Transistor Level VGS-Multiplier

B. Blalock & S. Terry - 14

OTA Design – LVCCM Biasing – 2

• Minch1 recently presented a cascode bias circuit that guarantees

maximum output swing at any current level and temperature

• This circuit sets the ratio between the

forward (gate & source controlled) and

1/n

1 1 reverse (gate & drain controlled) MOS

currents in the bottom-most transistor

where ID = IF – IR

Ibias VCAS

n-1 1

IF

= n2

1

IR

1 B.A. Minch, “A Low-Voltage MOS Cascode Bias Circuit for All Current Levels,” Proc.

IEEE Int. Sym. On Circuits and Systems, Scotsdale, AZ, 2002, pp. 619 – 622

B. Blalock & S. Terry - 15

OTA Design – Full Picture

• OTA design showing core OTA, constant gm biasing, and

adaptive LVCCM biasing

Constant Adaptive

gm LVCCM

Biasing Biasing

B. Blalock & S. Terry - 16

Recent Work – 1/f Noise Reduction

• White noise is reduced at low

temperatures, however 1/f

noise is only weakly dependent

on temperature, therefore the

noise corner will increase with

reduced temperature

• Ping-pong op-amps reduce 1/f

noise by using auto-zeroing –

thus they can significantly

increase dynamic range for

systems with a high noise

corner

B. Blalock & S. Terry - 17

Recent Work – 1/f Noise Reduction

Ping-Pong Op-Amp: Measured Noise Spectrum

10000

Fpp = 100kHz

T = 25C

Input Referred Noise (nV/rtHz)

Noise spectrum w/o

Auto-zero

1000

Noise spectrum w/

Auto-zero

100

1.0E+01 1.0E+02 1.0E+03 1.0E+04 1.0E+05

Frequency (Hz)

B. Blalock & S. Terry - 18

Recent Work – 0.35µm SOI Op-Amp

• General Purpose Op-Amp in commercially available SOI

process:

– Fabricated in 0.35um/3.3V MOI5 process (commercial/non-radhard)

– Rail-to-Rail I/O

– Unity Gain Stable w/ RL||CL = 100kΩ || 20pF

– High current capability (e.g. can drive 5kΩ at 2.5Vpp)

– Room Temperature Characteristics:

Small-Signal Bandwidth 4 MHz

Unity Gain P.M. (CL = 20pF) 60 degrees

Large-Signal Bandwidth 500 kHz

Thermal Noise Floor 40 nV/rtHz

B. Blalock & S. Terry - 19

Recent Work – 0.35µm SOI Op-Amp

• Design Highlights

– 1st stage is fully differential, rail-to-rail ICMR w/ regulated gm and

constant slew rate, CT CMFB

– 2nd stage is a Class-AB driver with low quiescent current for good

power efficiency

VMID

VMID

VMID

VID

+

MOI5 Op-Amp Schematic (LVCCM biasing not shown)

B. Blalock & S. Terry - 20

Recent Work – MOI5 Op Amp

MOI5 Op-Amp : Measured THD vs. Temperature

75

12 Bit Linearity

70

65

THD (dB)

60 10 Bit Linearity

55

50

8 Bit Linearity Measurement Notes:

Av = +1

Vin = 3V p-p @ 8kHz

45 11 Harmonics Measured

40

113 133 153 173 193 213 233 253 273 298

Temperature (K)

B. Blalock & S. Terry - 21

Conclusions

• Low temperature analog CMOS presents challenges and

opportunities

• Challenges

– Modeling

– Robust design techniques

• Opportunities

– High bandwidth

– Reduced power dissipation

– Reduced thermal noise

B. Blalock & S. Terry - 22

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Nevada Reply BriefDocument36 pagesNevada Reply BriefBasseemNo ratings yet

- THE MEDIUM SHAPES THE MESSAGEDocument56 pagesTHE MEDIUM SHAPES THE MESSAGELudovica MatildeNo ratings yet

- DEC LAB REPORT-06Document9 pagesDEC LAB REPORT-06anon_776365175No ratings yet

- CIS2103-202220-Group Project - FinalDocument13 pagesCIS2103-202220-Group Project - FinalMd. HedaitullahNo ratings yet

- Contract of Lease-Water Refilling StationDocument4 pagesContract of Lease-Water Refilling StationEkeena Lim100% (1)

- A Practical Activity Report Submitted For Engineering Design Project - II (UTA024) byDocument31 pagesA Practical Activity Report Submitted For Engineering Design Project - II (UTA024) byTania CENo ratings yet

- 91 SOC Interview Question BankDocument3 pages91 SOC Interview Question Bankeswar kumarNo ratings yet

- Zaranda Finlay 684 Manual Parts CatalogDocument405 pagesZaranda Finlay 684 Manual Parts CatalogRicky Vil100% (2)

- Willie Chee Keong Tan - Research Methods (2018, World Scientific Publishing Company) - Libgen - Li PDFDocument236 pagesWillie Chee Keong Tan - Research Methods (2018, World Scientific Publishing Company) - Libgen - Li PDFakshar pandavNo ratings yet

- Porsche Scheduled Maintenance Plan BrochureDocument2 pagesPorsche Scheduled Maintenance Plan BrochureDavid LusignanNo ratings yet

- Finesse Service ManualDocument34 pagesFinesse Service ManualLuis Sivira100% (1)

- DLC LAB - 10 - Student - ManualDocument8 pagesDLC LAB - 10 - Student - ManualImtiaj SajinNo ratings yet

- Analysis and Design of Analog Integrated Circuits Analog To Digital ConversionDocument32 pagesAnalysis and Design of Analog Integrated Circuits Analog To Digital ConversionAndrea FasatoNo ratings yet

- Dec Exp 6 Student ManualDocument5 pagesDec Exp 6 Student ManualSakib MahmudNo ratings yet

- Dac ArchitectureDocument17 pagesDac ArchitectureSagar MaruthiNo ratings yet

- Tutorial T1 PresentationDocument96 pagesTutorial T1 Presentationsykimk8921No ratings yet

- ,dynamic Element Matching For High-Accuracy Monolithic WA ConvertersDocument6 pages,dynamic Element Matching For High-Accuracy Monolithic WA ConvertersMEHDI ABDOUNo ratings yet

- Latched Comparator: ADC Converters (Continued)Document28 pagesLatched Comparator: ADC Converters (Continued)shriniwas ghadyaljiNo ratings yet

- Introduction To A/D ConversionDocument20 pagesIntroduction To A/D ConversionWala SaadehNo ratings yet

- Dac Ad7541Document8 pagesDac Ad7541api-26783388No ratings yet

- A 12-Bit: Two-Step FlashDocument6 pagesA 12-Bit: Two-Step FlashSankar SaroNo ratings yet

- REPORTFINALDocument21 pagesREPORTFINALReal HumanityNo ratings yet

- Tas 5713Document71 pagesTas 5713Nelson BorgesNo ratings yet

- NCV7351, NCV7351F High Speed CAN, CAN FD Transceiver: Marking DiagramDocument17 pagesNCV7351, NCV7351F High Speed CAN, CAN FD Transceiver: Marking DiagramJose Otilio Chavez CantuNo ratings yet

- NCV7351-D CAN TransceiverDocument13 pagesNCV7351-D CAN TransceiverahmedNo ratings yet

- DATA Converter CircuitsDocument31 pagesDATA Converter CircuitsCharefNo ratings yet

- ELEN 689 -603 Pipeline ADC’s PerformanceDocument29 pagesELEN 689 -603 Pipeline ADC’s PerformanceInJune YeoNo ratings yet

- DLC Lab - 10Document7 pagesDLC Lab - 10Didarul Alam AlifNo ratings yet

- 2Document10 pages2Marcelo OemNo ratings yet

- Asymmetrical IGBT Design For Three-Level NPC1 Converter in A Bi-Directional Power Conversion SystemDocument7 pagesAsymmetrical IGBT Design For Three-Level NPC1 Converter in A Bi-Directional Power Conversion SystemARINDA DENISENo ratings yet

- Aaic Adc Casestudy NoteDocument37 pagesAaic Adc Casestudy NoteNidhin KNo ratings yet

- D/A Converters: Digital to Analog Conversion TechniquesDocument14 pagesD/A Converters: Digital to Analog Conversion Techniquesjonathan stevenNo ratings yet

- Flash ADC Design Challenges and MethodologyDocument15 pagesFlash ADC Design Challenges and MethodologyJagadeep KumarNo ratings yet

- Stm32f3 AdcDocument65 pagesStm32f3 AdcJisNo ratings yet

- The Flash ADC A Circuit For All SeasonsDocument5 pagesThe Flash ADC A Circuit For All Seasons于富昇No ratings yet

- Analog To Digital Converter in Wireless Local Area NetworkDocument29 pagesAnalog To Digital Converter in Wireless Local Area Networkkumarbsnsp0% (1)

- MAX22530 Isolated ADCDocument37 pagesMAX22530 Isolated ADCRoy ChaiNo ratings yet

- Design of A New 3 Bit Flash Analog To DiDocument11 pagesDesign of A New 3 Bit Flash Analog To DisayemeeceNo ratings yet

- Module 7Document72 pagesModule 7sai manikantaNo ratings yet

- MT-091 Tutorial: Digital PotentiometersDocument10 pagesMT-091 Tutorial: Digital PotentiometersPrashant RajaNo ratings yet

- Switched-Capacitor Circuits FundamentalsDocument50 pagesSwitched-Capacitor Circuits FundamentalsRaneforyon100% (1)

- Digital-to-Analog Analog-to-Digital Conversions: Microprocessor InterfaceDocument34 pagesDigital-to-Analog Analog-to-Digital Conversions: Microprocessor Interfaceeugen lupuNo ratings yet

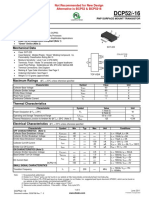

- Features: Not Recommended For New Design Alternative Is BCP52 & BCP5216Document5 pagesFeatures: Not Recommended For New Design Alternative Is BCP52 & BCP5216Yeiner Smith Polo MercadoNo ratings yet

- A 10-Bit 5 Msample/s ADC: Two-Step FlashDocument9 pagesA 10-Bit 5 Msample/s ADC: Two-Step FlashRaghav ChaudharyNo ratings yet

- Ads 8509Document34 pagesAds 8509KoldodeRostovNo ratings yet

- Dac 80Document10 pagesDac 80sunhuynhNo ratings yet

- MSME Tool Room Diploma in Tool and Die Making Mechatronics CourseDocument160 pagesMSME Tool Room Diploma in Tool and Die Making Mechatronics CourseShivam SinghNo ratings yet

- Lec05 Ad Da ConversionDocument10 pagesLec05 Ad Da ConversionWill BlackNo ratings yet

- Importance of Adcs and DesignDocument17 pagesImportance of Adcs and DesignsadiqueNo ratings yet

- Lecture 5Document33 pagesLecture 5hoa nguyen dinhNo ratings yet

- Linkswitch-Xt Family: Energy Effi Cient, Low Power Off-Line Switcher IcDocument16 pagesLinkswitch-Xt Family: Energy Effi Cient, Low Power Off-Line Switcher IcClaudio PrataNo ratings yet

- LNK362 PDFDocument16 pagesLNK362 PDFJose BenavidesNo ratings yet

- Modeling of Sigma Delta Modulator Non Idealities With Two Step Quantization in MATLAB SIMULINK PDFDocument6 pagesModeling of Sigma Delta Modulator Non Idealities With Two Step Quantization in MATLAB SIMULINK PDFeditor_ijcatNo ratings yet

- LNK362 PGDocument16 pagesLNK362 PGCarlos RobertoNo ratings yet

- Design Optimization For Power-Supplying The Nodes of WSNs - Master Thesis Presentation - Ioannis MandourarakisDocument51 pagesDesign Optimization For Power-Supplying The Nodes of WSNs - Master Thesis Presentation - Ioannis MandourarakisIoannis MandourarakisNo ratings yet

- LNK362 PowerIntegrationsDocument16 pagesLNK362 PowerIntegrationsAhmed LidaNo ratings yet

- Tiducv 9Document24 pagesTiducv 9zizouhicheNo ratings yet

- Importance of Adcs and DesignDocument17 pagesImportance of Adcs and DesignMansunder SinghNo ratings yet

- MJD31 D 90514Document11 pagesMJD31 D 90514MaxNo ratings yet

- DAC&ADC (EngineeringDuniya - Com)Document24 pagesDAC&ADC (EngineeringDuniya - Com)ramanaidu10% (1)

- Can Driver Ram 2005 Ecus Marco EsteliDocument27 pagesCan Driver Ram 2005 Ecus Marco EsteliautocomputerNo ratings yet

- TMC1175A 8-bit 50 Msps Video A/D ConverterDocument19 pagesTMC1175A 8-bit 50 Msps Video A/D ConverterCharbel TadrosNo ratings yet

- Embedded Systems: Prepared By: Team " X "Document46 pagesEmbedded Systems: Prepared By: Team " X "yuosef hababa100% (1)

- A8298 DatasheetDocument28 pagesA8298 Datasheetsharklink blackNo ratings yet

- BJT - JFET Frequency ResponseDocument39 pagesBJT - JFET Frequency ResponseGem Raymund CastroNo ratings yet

- CP Exit Srategy Plan TemplateDocument4 pagesCP Exit Srategy Plan TemplateKristia Stephanie BejeranoNo ratings yet

- Capital Asset Pricing ModelDocument11 pagesCapital Asset Pricing ModelrichaNo ratings yet

- Corvette Stingray - Papercraft Sports Car: Food Living Outside Play Technology WorkshopDocument22 pagesCorvette Stingray - Papercraft Sports Car: Food Living Outside Play Technology WorkshopStylus ClearingNo ratings yet

- QA InspectionDocument4 pagesQA Inspectionapi-77180770No ratings yet

- Accor vs Airbnb: Business Models in Digital EconomyDocument4 pagesAccor vs Airbnb: Business Models in Digital EconomyAkash PayunNo ratings yet

- SS Corrosion SlidesDocument36 pagesSS Corrosion SlidesNathanianNo ratings yet

- Kinds of ObligationDocument50 pagesKinds of ObligationKIM GABRIEL PAMITTANNo ratings yet

- Household Budget Worksheet - Track Income & ExpensesDocument1 pageHousehold Budget Worksheet - Track Income & ExpensesJohn GoodenNo ratings yet

- Banaue Rice Terraces - The Eighth WonderDocument2 pagesBanaue Rice Terraces - The Eighth Wonderokloy sanchezNo ratings yet

- SSPC Paint 25 BCSDocument6 pagesSSPC Paint 25 BCSanoopkumarNo ratings yet

- Chapter FiveDocument12 pagesChapter FiveBetel WondifrawNo ratings yet

- Reason Document 0n Rev.3Document58 pagesReason Document 0n Rev.3d bhNo ratings yet

- 1Z0-062 Exam Dumps With PDF and VCE Download (1-30)Document6 pages1Z0-062 Exam Dumps With PDF and VCE Download (1-30)Humberto Cordova GallegosNo ratings yet

- Secure Access Control and Browser Isolation PrinciplesDocument32 pagesSecure Access Control and Browser Isolation PrinciplesSushant Yadav100% (1)

- DPD 2Document1 pageDPD 2api-338470076No ratings yet

- Maximum Yield USA 2013 December PDFDocument190 pagesMaximum Yield USA 2013 December PDFmushroomman88No ratings yet

- COA (Odoo Egypt)Document8 pagesCOA (Odoo Egypt)menams2010No ratings yet

- G.R. No. L-54171 October 28, 1980 JEWEL VILLACORTA, Assisted by Her Husband, GUERRERO VILLACORTA, COMPANY, Respondents. TEEHANKEE, Acting C.J.Document6 pagesG.R. No. L-54171 October 28, 1980 JEWEL VILLACORTA, Assisted by Her Husband, GUERRERO VILLACORTA, COMPANY, Respondents. TEEHANKEE, Acting C.J.Lyra Cecille Vertudes AllasNo ratings yet

- DX DiagDocument31 pagesDX DiagJose Trix CamposNo ratings yet

- Supplement - 7 Procurement Manual: Democratic Socialist Republic of Sri LankaDocument8 pagesSupplement - 7 Procurement Manual: Democratic Socialist Republic of Sri LankaDinuka MalinthaNo ratings yet

- Flex VPNDocument3 pagesFlex VPNAnonymous nFOywQZNo ratings yet