Professional Documents

Culture Documents

E 95 A 050

Uploaded by

Ag CristianOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

E 95 A 050

Uploaded by

Ag CristianCopyright:

Available Formats

THE DIGITAL SOLUTION

Part 10 (final) - Back to the real world

By Owen Bishop q = 50 pA, which is 128 (Z1

A. 11 t h e articles of this se-

les have demonstrated

that there is generally an ad-

times) the current through Do.

In Fig. 78, the digital

vantage to be gained In this series we look closely at digital electronics, '"put 'S show" be fed di-

storing, transmitting a n d rectly to the resistors. This is '

Drocessine data in what it is, what it does, how it works, and its a workable circuit, but relies

i o m . Maybe there are dGad- promise for the future. on the individual bits of the

vantages. too, a n d analogue digital inputs all having pre- ,

data may sometimes be more cisely the same voltage levels

easily handled, but the over- for '0' and 'l'. It is more usual

all preference is for digital for the digital input to he fed

representation. This prefer- to an array of analogue

ence endures for a s long a s ! switches, each connected as in

d a t a is being handled by Fig. 79. If the input hit is 'W,

electronic devices. But ulti- i the switch connects the re-

mately, the d a t a h a s to be ! sistor to 0 V. If the bit is 'l',

presented to a human for as- :' the switch connects the re-

sessment, a s tnformation, or sistor to an accurate reference

even simply for entertain- voltage, VEf, which is used for

ment, a n d h u m a n s operate all resistors.

in a n essentially analogue This converter relies on the

-

'virtual earth' property of the

- ~~ p ~

manner. Maybe we can cope

if the decimal number 1 2 is Fig. 78 inverting input of the op amp.

presented to u s in binary Current flows to the inverting

form a s 1110, b u t few would input a s if this is a t ground

recognize t h a t the number (0 V) potential. If two or more 1

DIGITAL IN PUT inputs are at 5 V, the current

1 1 1 l l 0 0 1011 represents C,ONTROLS SWITCH

/ flowing through one resistor is

the year 1995. Fewer still

would recognize a certain se-

quence of bytes a s one of the

- 1 ,/, - ' independent of the current

flowing through the others. As

TO

themes from Beethoven's OPAMI a result, the current reaching

Ninth Symphony. Before it the inverting input is the sum

c a n have much meaning to of the individual currents.

h u m a n s . digital d a t a nearly #d012&?0-78 When two or more inputs re-

always needs to he converted ceive a logic 1 input, the cur-

back to analogue form. In rents are summed, just as the

this final p a r t of the series. Fig. 79 value of a binary number

we consider some of the equal to the sum of the values

many techniques of digital-to- 7, , , ~ - .,L . ~ -,I,-

~ ~.

,,,--_C_____J_

~ - ~ ~ ~ ,. ,? ,,,m =

of the '1' digits it contains.

analcgue- conversion . ' VREF

-

.- ~.. Suppose both Do and D, are at

.5 V. The sum of the currents

p ~ -

+~ - R ~ - T ~ P - ~ - - - - - - - - ~ R T?R=L 1

Weighted resistors E rr 5, 'i ,-.

,=

l 1s 11.71875 pA, which corre-

sponds to the the binary value

,

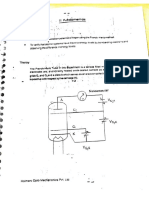

One of the simplest DACs ; l1 (decimal 3) and is three

makes use of the summing ,, times the current flowing

abilities of a n o ~ e r a t i o n a l r_R=- when Dn alone is s u.~. ~ l i eIf d.

amplifier. In Fig. 78, the in- I I 1 I l f- all eight inputs are high, the

verting input of the amplifier ,

~ ~

total current is 1111 1111 (255

receives current from a num- ; I I NALOGUE decimal) times the Do current,

her of sources throunh senar.

n .

9-57 = OlolTAL INPUT CONTROLS SWITCHES A OUTPUT or a .~.~ r o x i m a t e996

l v u ~ The

.

ate resistors. Assuming t h a t inputs of an opgmp have ex-

this is an 8-bit converter, the p

tremely high impedance, so

digital value to he converted all the current flows on

is applied to the eight inputs, Fig. 80 through the 1 kR resistor, cre-

Do-D7. The input is a logic ating a p.d. of 1V across it.

level, either 0 V (equivalent to The output voltage swings

logic O), or 5 V (equivalent to when 5 V is applied to i t is to the amplifier from Do is negative of the inverting input

logic 1). The resistors a r e double t h a t flowing through 511280000 = 3.90625 pA. If by 0.996 V. As the binary

weighted, so that each one has the preceding resistor. Thus, 5 V is applied to D,, the cur- input ranges from 0 to

a value half t h a t of the one the currents are in proportion rent is 51640000 = 7.8125 pA, 1111 1111, the analogue out-

preceding i t in the sequence. to the values of successive dig- exactly double (21 times). At put ranges from 0 V to

Correspondingly, the current its in a binary number. For the other extreme, the current -0.996 V.

flowing through each resistor example, the current flowing flowing from D? is 5110000 The output is now on a n

ELEKTOR ELECTRONICS OCTOBER 1995

... . -- - - -. . . ---,.

.

r

. .- ,, - .

TBe DIGITAL SOLUTION -PART 10 m)

the switch is in position 1). In

either case, the current flows

to a line at zero potential If a

switch is a t position 0 [corre-

sponding to a 'V in the data

byte), the current is lost to

gmund.Ifamikhisat 1,the

cmrent flows to the op amp

and is summed with other

currents from switches a t po-

sition 1. This is another type

of multiplying MC.

In Fi.81 we build up an

R-!?R ladder in stages, to see

what potentiala are pt- at

its rungs. In the network of

Fig. Ola, the potential a t

pointAisVmThetwoRre-

sistors divide the potential

exactly in half, no the poten-

W. 81 tial at point B is V&. In

Fig. 80b, the single R resistor

on the right of Fig. 8Oa has

analogue scale and can, if de- ever, in many application., put voltnge, can be aet to to been replaced by two 2R re-

sired, be fed to a voltmeter the output is fed to a low-pass different levels. In either ver- sistor~in parallel, both of

calibrated from 0 to 255 to filter and, if the output is con- mon, the chief disadvantage is which are connected to 0 V.

give a direct reading. More tinually changing, the filter that the values of all the Two 2R resistors in parallel

often it might be used to pto- smoothes out the steps, pro- larger resistors must be very are exactly equivalent to a

vide an analogue input to a ducing an e l k t i d y analogue precise. For example, if the single R resistm, so the poten-

device such am a motor, con- output. 10M is precise to within 10% tial at point B remains a t

trolling its speed, or to aloud- This type of DAC is simple (*l M), oll redstots must be V&. In Fig. 8Oc, the 2R re-

speaker, determining the posi- in principle and produce~ precise to within +lM. This s i d r at the right of 6g. 80b ia

tion of the cone. The output is rapid conversions. Another means that the 1280 M r e replaced by its equivalent, two

said to be analogue, but this i8 version has the weighted re- aistor must be precise to R resistors in series. They di-

not quite true. An analogue sistors in the feedback posi- within 0.078%. A converter of vide the potential at B eraetly

output could take any value in tion. These cau be switched in more than 8-bit precision is in half, so the potential a t

the range 0-0.996 V, but the or out of circuit by analogue not really a practioal propod- point C is V d 4 . In B'ig. 80dd

output of this circuit is one of switches controlled by the tion. the R resistor a t the right of

256 stepe, spaced 3.90625 mV digital input. The input to the A digital-to-analogue con- Fig. 8Oc is replaced by two 2R.

apart. The reoolubion of the op amp is at a fixed level, but verter of this type in which resistors in parallel, and the

converter is 3.90626 mV. How- the gain, and hence the out- the output is the product of potential a t C remains a t

the digital input and a refer- V d 4 . Thin p-B cau be re-

ence voltage source is often peated indefinitely, producing

known as a multiplying DAC. more and more 2R runge, the

chain of R resistors always

Switched current- ending in a 2R resistor tied to

0 V. At each rung, the poten-

SOUK8 DAC tial is exactly half that of the

This type of converter also rung above it. Since the 2R re-

uses the current-summing sistors are cennected to 0 V

I property of an op amp, but the whatever the position of the

circuit for producing the cur- switches, the switch positions

rents is entirely different h have no effect on the poten-

the weighted resistors used in tial. When a switch is set to

the previous converter. In position 1, a corresponding

Fig. 80, the current sources current flows to the op amp.

are provided by what is This current is V&m,

known as an R2R ladder, be- V&4R. VBBP/8R,and so on

earn it consists af resistors of along the ladder to V&56R

only two values, R and 2R. a t the last rung of an 8-bit

Current flows from the volt- chain. It is feasible to con-

age reference along the chain tinue the ladder to give 12-bit

of R resistoFs (except the one m 16Et mwlution. Whatever

a t the end, which is 2R) and the length of the ladder, the

JP JP- aemss the 2R resistors, which op amp snme the current flow-

= T- form the rungs of the ladder. ing through the 1 switches,

The current flows through producing an output ranging

switches controlled by the from 0 V to -V& as the

digital input and then goes input (in an 8-hit converter)

either to ground (if the swich ranges from 0 to 11111111.

is in position 0) or to the in- This is one of the most pop

341-89 W- 84 verting input of the op amp (if ular types of converter. It is

ELEKmRELEmROMLS~ER19M

m GENERAL INTEREST

easv to produce i n integrated I I

clrcuit form, mainly because i t

requires on-chip resistors of 1 SUMMER 1

only two values. More signifi- OUTPUTTO DAC

cant i s t h e fact t h a t i t i s not ro 1151 I-ORATOR OUINTIZER

t h e absolute values of t h e re-

sistors t h a t matter, only their

relative values. This is easy to

achieve, allowing high preci-

sion a t low cost.

Switched capacitor

-1 FEEOBACX

1

DAC 9LW. - ..-..

One of the newer forms of DAC L ~ ~- -~ P-P ~ ~ ~ ~

relies on switched weighted

capacitors. Instead of using a Fig. 85 <

chain of resistors connected in

series a s a potential divider,

,

these DACs use a ladder of ca- SUMMER

pacitors connected in parallel.

The principle of the technique ONE sn OUTPUTTO

i s illustrated i n Fig. 82. LOW - P A S S

ouANnzER

F,,,,

which for simplicity is ahown (bit $,,ell

a s a 4-hit DAC. The analoeue U

switches are controlled by two

clocks, which in t u r n produce I

high pulses. When clock 1 DELAYED

goes high, all switches a r e

~

FEEDBACK

connected to t h e 0 V line, so

all capacitors a r e discharged. i

Next, clock 2 goes high a n d 1

t h i s operates i n conjunction l

with t h e dieital inout so t h a t

only those switches corre- Fig. 86

sponding to a 'l' input bit a r e

connected to the V.,c.L, line. The l 1

switches corresponding to a VOLT= VREFxCB/(Ca+CB).

digital '0'remain connected to

t h e 0 V line. However, t h i s Given t h a t

does not mean t h a t they re- CA= 3Cl4 and CB= 5C14, FROM

m,TcTm=a,

- . TO ANA LOGUE

-....

",a",,". ..

main uncharged. To see what

happens, suppose t h a t t h e VOW= VREF~[3C1411([3C141t[5C141) OAC

digital input is 0110. Switches

Do and D3 remain switched to = VREFx3/(3+51

t h e 0 V line, while D1and D2

1 ,

become switched to t h e VREF =VREFx3I8. ,A, <X

line. I t makes t h e situation

easier to understand if the cir- The input is 0110 (decimal 6 )

940120-10-86

cuit i s redrawn a s in Fig. 83. and t h e output is 318 of VKEp

The two capacitors on the left T h e relationship between - -- --- -

i 4

a r e those switched to VREF. input and output becomes

T h e t h r e e capacitors a t t h e clearer if we express the out- Fig. 87

right a r e those switched to the put i n sixteenths, since there

0 V line, and include the non- a r e sixteen possible switching

switchable Cl8 capacitor a t combinations with four capac- on fewer bits but to take sam- duction of audible sound,

t h e end of the ladder. itors. Then, t h e output is writ- ples more frequently. Taking though i t has t h e advantage

The two groups of capaci- t e n a s 6116. If t h e binary samples more frequently than t h a t i t is easier to filter out

tors in Fig. 8 3 a r e capacitors i n p u t i s n, t h e output is "116 i s required to represent t h e t h e quantization noise which

in parallel, so they can be of VREpThis can be confirmed analogue d a t a accurately i s results from t h e fact t h a t , a s

thought of a s being replaced by working out t h e effects of known a s ouersampling. For mentioned earlier, the output

by a single capacitor for each other binary inputs. Note that example, digital audio re- from a DAC i s stepped, not

group. Since they are in paral- since this DAC has no op amp, quires sampling a t a little continuous. T h e frequency of

lel, their equivalent values are the maximum output is VREp over 40 kHz (usually 44.1 kHz) this noise extends around the

found by adding their capaci- i n order to represent all fre- sampling frequency, so i s

tances. Figure 84 shows the usingfewer bits quencies in the audio range much easier to remove when

equivalent circuit a s a capaci- up to 20 kHz, t h e highest fre- t h e sampling frequency i s

tive potential divider. I t can We have mentioned t h e prob- quency t h a t can be detected higher, well separated from

be shown t h a t when two ca- lem of obtaining the required by t h e human ear. Sampling t h e audio frequencies. There

pacitors CAa n d CB form a po- degree of precision in the most a t a higher rate, such a s a r e practical problems i n

tential divider (Fig. 841, t h e significant bits. An entirely 88.2 kHz, i s oversampling. I t taking advantage of oversam-

output V,, is different approach is to rely does not improve t h e repro- pling when producing CDs,

ELEKTOR ELECTRONICS OCTOBER 1995

-

-

THE D I G W SOLUTION PART 10 W A L )

output, follow the stages in

but it is podble to effectively

double the sampling rate on converting a &bit digital Input + ficedb.elr -m Fndb.cL

replay by interpolating a sam-

value, reducing it to l-bit out-

ple between each of the put. Given that the 4bit input 0101+0000=0101 1 0101-1000=-0011

recorded samples. The value has 1000 (decimal 8) as its 0101-0011=0010 0 001(M000=+0010

of each interpolated sample is

maximum value, the quan- 0101+0010=0111 1 0111-1ooO-OOO1

calculated as the mean of the

tizer gives an output '0' for 0101-0001=0100 1 0100-1ooO-0100

two recorded samples on values OO00-0011 and an o u t 0101-0100=0001 0 OOO1-0000=+0001

either aide of it. Interpolation

put 'l' for values 0100-1000. 0101+0001=0110 1 011&1000=-0010

was widely used in earlier Because it drops three bits, 0101-0010=0011 0 0011-0011

the M C cycles at 8 (-29) times

digital audio systems, but in 0101+0011=1OOO 1 1000-1000= 0000

now largely replaced by sys-the initial eampling frequency.

terns that rely on fewer bits.

What happens is shown in

Figure 86 is a block dia-

Table 8. -8

gram of a circuit that reduces At the fist cycle, there is

no existing feedbaeh, the total

the number of bits in the sam-

ples by 2. The digital inputis between 0100 and 1000, so

consists of samples, each of n

the output is '1'. This 'l' is beset analogue circuits. It Converted?

bits, taken a t the sampling

really a 'l' plus three follow- might be objected that the nig- In this series we have de-

rate f (say, 44.1 kHz). The ing bits which have been dis- nal is still digital after it scribed and explained many

sample is fed to an integrator,

carded, so it is equivalent to leaves the converter, but aU aspects of digital electronics

which digitally adds the sam-

1000. Thie is subtracted from that is now needed is a low- and we have attempted to

ple ta the value alreadythere.

the input+feedback value to pass filter of simple design to show that digital techniques

The sum is then requantized,

give the feedback (-0011) for wnvert the stream of bits (re- have many benetits. Analogue

that is, the final two bitsare

the sewnd cycle. In the secxlnd member, these are wming at a techniques have a lot to offer

cycle, the feedback is added ta

removed from it. In effect, it is very high rate) into an ana- and may be preferable in

the input (which is held at the

divided by 4 and the remain- logue signal. No further con- many situations but, on the

der discarded. This becomessame value as before). The uersion, as such, is needed. whole, the author believes

feedback value is negative so

the output of the circuit. The Assuming, for the sake of sim- that ultimately the practition-

output is also fed back andwe show this as a subtraction, plifyiug the explanation tbat ers of electronica, professional

subtracted from the incoming

giving 0010. This is between we use the simplest possible and amateur, will be drawn

signal to compensate for the

0000 and 0011, so the output kind of low-pass filter--see increasingly toward The Disi-

is '0'. Subtracting thia (=OOOO)

loss of the remainder. Thehey Fig.87, each 'l' pulse places a tal Solution.

to the action of the circuit is

from 0010 leaves +0010, unit charge on the capacitor. [940120-XI

that it operates at four times

which becomes the feedback A continuous series of 'l's

the sampling frequency, so for the third cycle. This rapidly charges the capacitor A~~~~~ to

that each input sample is held

process is repeated until, at to the maximum voltage and

for four cycles. Note that this

the end of eight cycles, the the output signal reaches this Ted Y O U ~ B (9)

(~

process is entirely digital. The

feedback ie zero. The input level. With a continuous series 1. Active high.

output from this circuit mayhaa been completely converted of '0'8, no charge is supplied to Q,, R S Qn+l

then be fed to a DAC with two

into a series of Os and 1s with- the capacitor and the output L L L i

fewer bits, and hence greater

out any remainder. rapidly falls to zero. In the in- L L B H

precision than would other- In the above example, the termediate situations in L B L L

wise be required. input value is decimal 5, and which between one and seven L L R

A similar principle may be

the output has five 'l' bits in pulses are produced for each L A B

used to build a l-bit DAC asit out of eight bits. Thus, the sample, the capacitor is A A L L

output is 518 of the possible

shown in Fig. 86. In this, the charged to a greater or lesser

quantizer' has only hlevels maximum of 8. The reader degree and an intermediate 2

of output, '0' and 'l', and is

might try this routine for output voltage is generated Latch No XOR Output

known as a l-bit quantizer. If

other inputs to confirm that, accordingly. 1 2 3 4 (of 3&4) (4)

it receives a sample with a for any input between 0000 Bit stream technology is fed back

value up to but not including

and 1000, the number of 'l's one of the newer develop- 0 1 1 0 1 0

0.5 of the maximum value, its

produced in eight cycles al- meuts of digital electronics 1 0 1 1 0 1

output is 'W. If the sample haa

ways equals the value of the and bas special applications 0 1 0 1 1 1

a value of 0.5 or more of the

input. This procedure can be in audio electronic%such as in 1 0 l 0 1 0

maximum value, its output isextended to any number of CD players. It has its limita- 1 1 0 1 1 1

'l. As before, the operation is

input bits and always the pm- tions, the primarp one being 1 1 1 0 1 0

repeated several times for portion of 'l' bits in the output tbat to convert a 16-bit sam- 1 1 1 1 repeats

each input sample. However, equals the proportion of the ple requires a bit stream DAC

in this case, we do not feed iuput value to the maximum cycling a t about 3 GHz. This Sa 4095

back the output signal, but value. is not easy to achieve in the

the difference between the The output of a DAC such present state of circuit fabri- 3b 16777215

output signal and the sample,as this is a stream of 'l' bits cation, so hybrid techniques

(high logic level) interspersed

so as to allow for the loss of are used, such as reduciug the

information stored in the dis-

with '0' bits (low logic level) number of bits by using cir-

carded bits. To see how this and is known as a bit stream. cuits such as that in Fig. 85

works and the nature of its The bit stream is produced and completing the process

wholly by digital circuits, with conventional DACs, or

which means that there are combining bit stream tech-

'to quantlze = to digitize = no problems with precision, niques with interpolation.

to convert an analogue sig- ageing of components, noise,

nal to a digital slgnal. or any of the other snags that

ELEKTOB ELECTRONICS OCFOBER 1995

You might also like

- Student Record Management SystemDocument23 pagesStudent Record Management SystemKamna Jadhav67% (9)

- Sfantul Ioan Gura de Aur - Omilii La Matei (PSB 23)Document1,054 pagesSfantul Ioan Gura de Aur - Omilii La Matei (PSB 23)hooria85100% (1)

- Clement Alexandrinul - Scrieri IDocument431 pagesClement Alexandrinul - Scrieri IBadarau Catalin100% (1)

- P.S.B Vol3Document508 pagesP.S.B Vol3Dorel DanielNo ratings yet

- Distortion in PIN Diode Control Circuits - HillerDocument10 pagesDistortion in PIN Diode Control Circuits - HillerSinisa HristovNo ratings yet

- Tmag 1983 1062474Document4 pagesTmag 1983 1062474George AcostaNo ratings yet

- Planck's Constant Photoelectric ExperimentDocument4 pagesPlanck's Constant Photoelectric ExperimentgeetishaNo ratings yet

- RadCom 200104 pp17 21Document4 pagesRadCom 200104 pp17 21qweasd22No ratings yet

- Load BalancingDocument11 pagesLoad BalancingVarada J TambeNo ratings yet

- Microwave and RaderDocument22 pagesMicrowave and Radershobhit90075% (12)

- 73 Magazine 04 April 1977 OCR Page 0126Document1 page73 Magazine 04 April 1977 OCR Page 0126Polo OsornioNo ratings yet

- 2-Pound RLC Meter Measures Impedance Using Sound CardDocument5 pages2-Pound RLC Meter Measures Impedance Using Sound Cardlm741No ratings yet

- Capacitor in The AC Circuit With Cobra3Document12 pagesCapacitor in The AC Circuit With Cobra3Hamdani BenhacineNo ratings yet

- Updated H12 891 V1.0 ENU Study Guide Killtest Free H12 891 V1.0 ENU Demo Questions Online.pdfDocument12 pagesUpdated H12 891 V1.0 ENU Study Guide Killtest Free H12 891 V1.0 ENU Demo Questions Online.pdfaripangNo ratings yet

- AD - DA WordDocument24 pagesAD - DA WordRockNo ratings yet

- Solar Cell and ApplicationsDocument13 pagesSolar Cell and ApplicationsKalp PatelNo ratings yet

- NE570 ApplicationsDocument6 pagesNE570 ApplicationsAbcd9032100% (1)

- Chap 3 CNDocument25 pagesChap 3 CN48Nara Amit GopalNo ratings yet

- Littelfuse Capacitance and Signal Integrity Application NoteDocument2 pagesLittelfuse Capacitance and Signal Integrity Application Notesujeet kumarNo ratings yet

- Adobe Scan 06 Oct 2023Document8 pagesAdobe Scan 06 Oct 2023navya guptaNo ratings yet

- Parasitic Capacitances in Magnetic Components: DK4141 - C07.fm Page 289 Wednesday, January 19, 2005 1:43 PMDocument11 pagesParasitic Capacitances in Magnetic Components: DK4141 - C07.fm Page 289 Wednesday, January 19, 2005 1:43 PMdorin serbanNo ratings yet

- UOM Electromagnetic Induction Notes 7Document6 pagesUOM Electromagnetic Induction Notes 7Arctic TurtleNo ratings yet

- Definitions and Explanations For OCR Physics G482Document77 pagesDefinitions and Explanations For OCR Physics G482k1ng_k3m1xNo ratings yet

- On Diode ApplicationsDocument13 pagesOn Diode ApplicationsBelen SeptianNo ratings yet

- Measuring an Audio Transformer's Electrical CharacteristicsDocument4 pagesMeasuring an Audio Transformer's Electrical Characteristicsjimmy67music100% (2)

- 10 Dollar Phone Patch PDFDocument2 pages10 Dollar Phone Patch PDFblesk2hotNo ratings yet

- Dielectric Constant Tan Delta & Resistivity Test Set: FeaturesDocument2 pagesDielectric Constant Tan Delta & Resistivity Test Set: FeaturesAnandNo ratings yet

- Effects of Package Parasitics on Crosstalk in Mixed-Signal ICsDocument5 pagesEffects of Package Parasitics on Crosstalk in Mixed-Signal ICsDavid DobrinNo ratings yet

- Compensator Design for AVP VRMsDocument7 pagesCompensator Design for AVP VRMsadolfNo ratings yet

- Figuring It OutDocument77 pagesFiguring It OutGoranNo ratings yet

- Ppings of 4: SwitchesDocument2 pagesPpings of 4: SwitchesDeepanshu ChaudharyNo ratings yet

- 2 - Analog Signal ProcessingDocument22 pages2 - Analog Signal ProcessingTuanHungNo ratings yet

- Adobe Scan Jul 07, 2021Document23 pagesAdobe Scan Jul 07, 2021ChristianNo ratings yet

- Grid Dip MeterDocument4 pagesGrid Dip MeterChris Osea AlvarezNo ratings yet

- Detector For Alternating Magnetic Fields: GeotechDocument6 pagesDetector For Alternating Magnetic Fields: GeotechMultiAbderrahmaneNo ratings yet

- Code Division Multiple AccessDocument10 pagesCode Division Multiple AccessvatsalamNo ratings yet

- Romeo Jose C. Purificando PT in Electronics Week 5 ND 6Document3 pagesRomeo Jose C. Purificando PT in Electronics Week 5 ND 6aeronh john PurificandoNo ratings yet

- 2011-10-12 Assignment 3Document2 pages2011-10-12 Assignment 3Rory Cristian Cordero RojoNo ratings yet

- Ehv Ac & DC Unit 3&4 PDFDocument20 pagesEhv Ac & DC Unit 3&4 PDFAnubhav AggarwalNo ratings yet

- KMC EE 2022 JuneDocument10 pagesKMC EE 2022 JuneDIPNo ratings yet

- The Flash ADC A Circuit For All SeasonsDocument5 pagesThe Flash ADC A Circuit For All Seasons于富昇No ratings yet

- Precision RectifierDocument5 pagesPrecision RectifierSoo BabyNo ratings yet

- Spen Eaflet: Transformer Damage Curve Made EasyDocument2 pagesSpen Eaflet: Transformer Damage Curve Made Easyshyam_krishnan_16No ratings yet

- Manual Mikro PFRNXDocument6 pagesManual Mikro PFRNXAriful IslamNo ratings yet

- DVR2000E TroubleShooting 1Document2 pagesDVR2000E TroubleShooting 1Yasin Noer Huda PNo ratings yet

- Compel 2015 7236460Document8 pagesCompel 2015 7236460salemg82No ratings yet

- Slave Mains On-Off Control: Amplificationj Attenuation SelectorDocument3 pagesSlave Mains On-Off Control: Amplificationj Attenuation SelectorTariq Zuhluf100% (2)

- Simulation Research of The Diode Characteristics Based On Mulitisim and ExcelDocument4 pagesSimulation Research of The Diode Characteristics Based On Mulitisim and ExcelDavid Rogelio Alvarez ReyesNo ratings yet

- Bird 2009Document2 pagesBird 2009kamran ashrafNo ratings yet

- Adobe Scan Jan 05, 2021Document6 pagesAdobe Scan Jan 05, 2021VLSS Phani REDDYNo ratings yet

- UOM Electromagnetic Induction Notes 2Document5 pagesUOM Electromagnetic Induction Notes 2Arctic TurtleNo ratings yet

- ML Unit-5Document22 pagesML Unit-5Mohammed Amir ShaikhNo ratings yet

- Some Timeless Ideas For Designs - Walt JungDocument3 pagesSome Timeless Ideas For Designs - Walt JungGiandomenico CicchettiNo ratings yet

- 2 ChapterDocument42 pages2 Chaptersunil kumarNo ratings yet

- EE 419 BEE Lec Module 8Document3 pagesEE 419 BEE Lec Module 8Jhun Lucky SadsadNo ratings yet

- Frank HertzDocument4 pagesFrank HertzKabeerNo ratings yet

- Nodal HandoutDocument2 pagesNodal Handoutmlj8753No ratings yet

- Effect of Restriking On Recovery VoltageDocument6 pagesEffect of Restriking On Recovery Voltagealex696No ratings yet

- Analysis and Design of Regenerative Comparators For Low Offset and NoiseDocument14 pagesAnalysis and Design of Regenerative Comparators For Low Offset and Noiseantonio ScacchiNo ratings yet

- Microwave Resistance of Gallium Arsenide and Silicon P-I-N DiodesDocument4 pagesMicrowave Resistance of Gallium Arsenide and Silicon P-I-N DiodesSinisa HristovNo ratings yet

- PSP Unit 3,4&5 PDFDocument25 pagesPSP Unit 3,4&5 PDFAnubhav AggarwalNo ratings yet

- Passive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2From EverandPassive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2No ratings yet

- PSB 57 Sf. Ioan Casian - Scrieri AleseDocument908 pagesPSB 57 Sf. Ioan Casian - Scrieri Alesealbugeorge100% (2)

- 53 AmbrozieDocument424 pages53 Ambrozieapi-19781457100% (1)

- PSB Vol. 17 - Sfantul Vasile Cel MareDocument652 pagesPSB Vol. 17 - Sfantul Vasile Cel MareFlorentin Duban100% (6)

- Long Document SummaryDocument455 pagesLong Document SummaryCristian Anca100% (2)

- PSB Vol 29-Grigorie de NyssaDocument496 pagesPSB Vol 29-Grigorie de NyssaAndrei RaduNo ratings yet

- 11-Actele Martirice (PSB, Vol. 11)Document372 pages11-Actele Martirice (PSB, Vol. 11)FlorinNo ratings yet

- 40 Sf. Chiril Al Alexandriei, Scrieri, Partea A III-A, Despre Sfânta Treime, Col. PSB 40Document311 pages40 Sf. Chiril Al Alexandriei, Scrieri, Partea A III-A, Despre Sfânta Treime, Col. PSB 40LucaOvidiuNo ratings yet

- PSB 34 - Sfantul Macarie Egipteanul - ScrieriDocument404 pagesPSB 34 - Sfantul Macarie Egipteanul - ScrieriGabrielNo ratings yet

- SF - Ioan Gura de Aur - Omilii La Facere - Vol. IDocument444 pagesSF - Ioan Gura de Aur - Omilii La Facere - Vol. IMarkTM100% (12)

- PSB 14 Eusebiu de Cezareea II Viata SF ConstantinDocument295 pagesPSB 14 Eusebiu de Cezareea II Viata SF ConstantinGheorgheNo ratings yet

- PSB Vol. 15 - Sfantul Atanasie Cel MareDocument416 pagesPSB Vol. 15 - Sfantul Atanasie Cel MareFlorentin Duban100% (5)

- SF Grigorie Taumaturgul Si Metodiu de Olimp - ScrieriDocument252 pagesSF Grigorie Taumaturgul Si Metodiu de Olimp - Scrieriandr3y7No ratings yet

- PSB Vol. 12 Sfantul Vasile Cel MareDocument644 pagesPSB Vol. 12 Sfantul Vasile Cel MareFlorentin Duban100% (5)

- PSB 8 Origen Scrieri Alese Partea IIIDocument408 pagesPSB 8 Origen Scrieri Alese Partea IIIraisa_peNo ratings yet

- PSB 09 Origen Contra Lui Celsus IVDocument586 pagesPSB 09 Origen Contra Lui Celsus IVGheorghe100% (3)

- PSB 06 - Origen - Scrieri Alese I PDFDocument472 pagesPSB 06 - Origen - Scrieri Alese I PDFGiorgianaStoicaNo ratings yet

- PSB 07 - Origen - Scrieri Alese, Partea A DouaDocument528 pagesPSB 07 - Origen - Scrieri Alese, Partea A DouaGabriel100% (4)

- 05 Clement Alexandrinul, Scrieri, Partea A II-A, Stromatele, Col. PSB 5Document592 pages05 Clement Alexandrinul, Scrieri, Partea A II-A, Stromatele, Col. PSB 5LucaOvidiuNo ratings yet

- Ise Tutorial Ug695Document150 pagesIse Tutorial Ug695Swapnil NagareNo ratings yet

- Car Theft Deterrent: by David ButlerDocument3 pagesCar Theft Deterrent: by David ButlerAg CristianNo ratings yet

- PSB Vol 2 Apologeti de Limba GreacaDocument391 pagesPSB Vol 2 Apologeti de Limba GreacaBoată GeaninaNo ratings yet

- Basic Pic ProgrammingDocument163 pagesBasic Pic ProgrammingJosue ZunigaNo ratings yet

- Hcmos Oscillators: J. RuffellDocument3 pagesHcmos Oscillators: J. RuffellAg CristianNo ratings yet

- Ayahuasca: Spiritual: Pharmacology & Drug InteractionsDocument39 pagesAyahuasca: Spiritual: Pharmacology & Drug InteractionsAg CristianNo ratings yet

- Save Decoder: Part 1: Operation and Technical BackgroundDocument6 pagesSave Decoder: Part 1: Operation and Technical BackgroundAg CristianNo ratings yet

- Capacitance Meter: D. FolgerDocument4 pagesCapacitance Meter: D. FolgerAg CristianNo ratings yet

- Initialization Aid For Printers: A. RigbyDocument4 pagesInitialization Aid For Printers: A. RigbyAg CristianNo ratings yet

- Saurabh CV FormatDocument3 pagesSaurabh CV FormatJane MooreNo ratings yet

- Ion Luca Caragiale, ReferatDocument2 pagesIon Luca Caragiale, ReferatComan DanielNo ratings yet

- Pervasive Healthcare Computing: EMR/EHR, Wireless and Health MonitoringDocument3 pagesPervasive Healthcare Computing: EMR/EHR, Wireless and Health MonitoringPajak RedikonNo ratings yet

- Marantz SR 4000 User GuideDocument30 pagesMarantz SR 4000 User Guidekeerthipinnawala6498100% (1)

- Winter 2009Document48 pagesWinter 2009ed bookerNo ratings yet

- Database Assignment OverviewDocument5 pagesDatabase Assignment Overviewitzaz yousafNo ratings yet

- Ih 03Document138 pagesIh 03Rocio MardonesNo ratings yet

- 60b69a03609f7bbbbb86ea8b - IoT Architecture White Paper - HologramDocument10 pages60b69a03609f7bbbbb86ea8b - IoT Architecture White Paper - HologramMike HollandNo ratings yet

- Banlga Text To Bangla Sign Language Parvez For ConferenceDocument6 pagesBanlga Text To Bangla Sign Language Parvez For ConferenceDr. Muhammad Aminur RahamanNo ratings yet

- Raspberry Pi Projects Book PDFDocument204 pagesRaspberry Pi Projects Book PDFstanchan82100% (1)

- UntitledDocument2 pagesUntitledmoch bagas setya rahmanNo ratings yet

- Data Guard PerformanceDocument39 pagesData Guard Performancesrevenco srevencoNo ratings yet

- Mary PowellDocument53 pagesMary PowellAnonymous HZgwzwNo ratings yet

- Berjuta Rasanya Tere Liye PDFDocument5 pagesBerjuta Rasanya Tere Liye PDFaulia nurmalitasari0% (1)

- DeterminantsDocument1 pageDeterminantsJanakChandPNo ratings yet

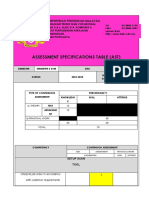

- Assessment Specifications Table (Ast) : Kementerian Pendidikan MalaysiaDocument6 pagesAssessment Specifications Table (Ast) : Kementerian Pendidikan MalaysiaMohd raziffNo ratings yet

- Characterization of SPT Grain Size Effects in GravDocument9 pagesCharacterization of SPT Grain Size Effects in Gravstefanus fendisaNo ratings yet

- C5G - R1C - Roboshop Program 2.0.0Document82 pagesC5G - R1C - Roboshop Program 2.0.0kukaNo ratings yet

- Image Classification With The MNIST Dataset: ObjectivesDocument21 pagesImage Classification With The MNIST Dataset: ObjectivesPraveen SinghNo ratings yet

- Fertilizer Information System For Banana PlantatioDocument5 pagesFertilizer Information System For Banana PlantatioHazem EmadNo ratings yet

- Teach Yourself Logic 2020 - Peter SmithDocument99 pagesTeach Yourself Logic 2020 - Peter SmithPaolo Pagliaro100% (1)

- Assignment 4Document2 pagesAssignment 4Priya RadhakrishnanNo ratings yet

- DX5 EuserguideDocument20 pagesDX5 Euserguidegabriel ferreyraNo ratings yet

- EWFC 1000: "Quick-Chill and Hold" Cold ControlDocument5 pagesEWFC 1000: "Quick-Chill and Hold" Cold ControlGede KusumaNo ratings yet

- Rancang Bangun Sistem Informasi Penjualan Toko Kelontong Winda SlemanDocument16 pagesRancang Bangun Sistem Informasi Penjualan Toko Kelontong Winda Slemanpetty riantiNo ratings yet

- Soltek SL 65meDocument88 pagesSoltek SL 65meBernardo AntunesNo ratings yet

- BGP 080uDocument394 pagesBGP 080uSameer PatelNo ratings yet

- ANSYS Parametric Design Language Guide 18.2Document110 pagesANSYS Parametric Design Language Guide 18.2Panda HeroNo ratings yet

- Artificial Intelligence Adversarial Search TechniquesDocument62 pagesArtificial Intelligence Adversarial Search TechniquesKhawir MahmoodNo ratings yet