Professional Documents

Culture Documents

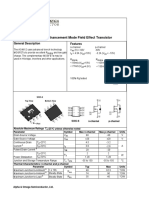

Field Effect Transistors

Uploaded by

Abdel Hamied EbrahemCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Field Effect Transistors

Uploaded by

Abdel Hamied EbrahemCopyright:

Available Formats

Field Effect Transistors (FETs)

FET has a very high input impedance (100 Mega ohm in case of

JFETs and 10 4 to 109 Mega Ohm in case of MOSFETs), the major

shortcomings of an ordinary transistor i.e. low input impedance

with consequent of loading of signal source is eliminated in FET.

Hence FET is an ideal device for use in almost every application in

which transistors can be used. FETs are widely used as input

amplifiers in oscilloscopes, electronic voltmeters, and other

measuring and testing equipment because of their high input

impedance.

Applications of FET:

1. Phase Shift Oscillators. JFET can

incorporate the amplifying action as

well as feedback action. It, therefore,

acts well as a phase shift oscillator.

The high input impedance of FET is

especially very valuable in phase-shift

oscillators in order to minimize the

loading effect. A typical phase shift

oscillator employing N channel JFET

is shown in figure.

2. Buffer Amplifier: A buffer amplifier is a stage of

amplification that isolates the preceding stage from the

following stage. Source follower (common drain) is used as a

buffer amplifier. Because of the high input impedance and

low output impedance a FET acts an excellent buffer

amplifier, as shown in figure. Owing to high input impedance

almost all the output voltage of the preceding stage appears

at the input of the buffer amplifier and owing to low output

impedance all the output voltage from the buffer amplifier

reaches the input of the

following stage, even there

may be a small load

resistance.

3. Cascode Amplifier: Circuit diagram for a

cascode amplifier using FET is shown in

figure. A common source amplifier drives a

common gate amplifier in it. The cascode

amplifier has the same voltage gain as a

common source (CS) amplifier. The main

advantage of cascode connection is its low

input capacitance which is considerably less

than the input capacitance of a CS

amplifier. It has high input resistance which

is also a desirable feature.

4. Analog Switch: FET as an analog switch is shown in

figure. When no gate voltage is applied to the FET i.e. V = 0,

FET becomes saturated and it behaves like a

small resistance usually of the value of less than

100 ohm and, therefore, output voltage becomes

equal to

Vout = {Rds/(Rd+Rds(ON))}*Vin

When a negative voltage equal to VGS(OFF) is

applied to the gate, the FET operates in the cut-

off region and it acts like a very high resistance

usually of some mega ohms. Hence output

voltage becomes nearly equal to input voltage.

5. Multiplexer: An analog multiplexer, a circuit that steers

one of the input signals to the output line, is shown in figure.

In this circuit each JFET acts as a single pole single-throw

switch. When the control signals (Vv, V2 and V3 ) are more

negative than VGS(OFF) all input signals are blocked. By

making any control voltage equal to zero, one of the inputs

can be transmitted to the output. For instance, when V is

zero, the signal obtained at the output will be sinusoidal.

Similarly when V is zero, the signal obtained at the output will

be triangular and when V is zero, the output signal will be

square-wave one. Normally, only one of the control signals is

zero.

Bipolar Junction Transistor (BJT )

A bipolar junction transistor is a three terminal semiconductor

device consisting of two p-n junctions which is able to amplify or

“magnify” a signal. It is a current controlled device. The three

terminals of the BJT are the base, the collector and the emitter. A

signal of small amplitude if applied to the base is available in the

amplified form at the collector of the transistor. This is the

amplification provided by the BJT. Note that it does require an

external source of DC power supply to carry out the amplification

process.

Applications of BJT:

1. Switches: control input flows into the base, the output is

tied to the collector, and the emitter is kept at a fixed voltage.

While a normal switch would require an actuator to be

physically flipped, this switch is controlled by

the voltage at the base pin. A microcontroller

I/O pin, like those on an Arduino, can be

programmed to go high or low to turn the

LED on or off. When the voltage at the base

is greater than 0.6V the transistor starts

saturating and looks like a short circuit

between collector and emitter. When the

voltage at the base is less than 0.6V the

transistor is in cut-off mode – no current

flows because it looks like an open circuit

between C and E.

2. Digital Logic: Transistors can be combined to create all

our fundamental logic gates: AND, OR, and NOT.

NOT: a high voltage into the base will turn

the transistor on, which will effectively

connect the collector to the emitter. Since

the emitter is connected directly to ground,

the collector will be as well (though it will be

slightly higher, somewhere around

VCE(sat) ~ 0.05-0.2V). If the input is low,

on the other hand, the transistor looks like

an open circuit, and the output is pulled up

to VCC.

AND: a pair of transistors used to create a

2- input AND gate, If either transistor is

turned off, then the output at the second

transistor’s collector will be pulled low. If both

transistors are “on” (bases both high), then

the output of the circuit is also high.

OR: In this circuit, if either (or both) A or B

are high, that respective transistor will turn

on, and pull the output high. If both

transistors are off, then the output is pulled

low through the resistor.

3. H-Bridge: An H-bridge is a transistor-based circuit capable of

driving motors both clockwise and counter-clockwise. It’s an

very popular circuit – the driving force behind countless

robots that must be able to move both forward and

backward. Fundamentally, an H-bridge is a combination of

four transistors with two inputs lines and two outputs.

If both inputs are the same voltage, the outputs to the motor

will be the same voltage, and the motor won’t be able to spin.

But if the two inputs are opposite, the motor will spin in one

direction or the other.

Photovoltaic (PV) Cell Structure and Operation

The photovoltaic impact is the essential physical process by

which a solar cell changes over daylight into power. Daylight

contains photons or "parcels" of vitality adequate to make

electron-holes in the n and p areas. Electrons gather in the

n-district and holes in the p area, creating a potential contrast

(voltage) over the cell. At the point when an outer load is

associated, the electrons move through the semiconductor

material and give current to the outer load.

The Solar Cell Structure:

Despite the fact that there are different sorts of sun oriented

cells and proceeding look into guarantees new

improvements later on, the crystalline silicon solar cell is by a

wide margin the most generally utilized. A silicon solar cell

comprises of a thin layer or wafer of silicon that has been

doped to make a pn junction. The profundity and dispersion

of polluting influence molecules can be controlled absolutely

amid the doping procedure. The most normally utilized

process for making a silicon ingot, from which a silicon wafer

is cut, is known as the Czochralski strategy. In this

procedure, a seed gem of silicon is plunged into softened

polycrystalline silicon. As the seed precious stone is pulled

back and pivoted, a barrel shaped ingot of silicon is framed.

Operation of a Solar Cell:

The n-sort layer is thin contrasted with the p locale to

permit light infiltration into the p area. The thickness of the

whole cell is really about the thickness of an eggshell. At

the point when a photon enters either the n district or the

p-sort area and strikes a silicon particle close to the pn

junction with adequate vitality to thump an electron out of

the valence band, the electron turns into a free electron

and leaves a gap in the valence band, making an electron-

hole combine. The measure of vitality required to free an

electron from the valence band of a silicon molecule is

known as the band-gap energy and is 1.12 eV (electron

volts). In the p locale, the free electron is cleared over the

exhaustion district by the electric field into the n area. In

the n area, the hole is cleared over the consumption locale

by the electric field into the p district. Electrons aggregate

in the n locale, making a negative charge; what's more,

holes aggregate in the p locale, making a positive charge.

A voltage is created between the n district and p locale

contacts.

At the point when a load is associated with a solar cell

through the top and base contacts, the free electrons

stream out of the n locale to the grid contacts on the top

surface, through the negative contact, through the heap

and once more into the positive contact on the base

surface, and into the p locale where they can recombine

with holes. The daylight vitality proceeds to make new

electron-opening sets and the procedure goes on

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Abs WorkoutDocument2 pagesAbs WorkoutAbdel Hamied EbrahemNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Oa6nn0 526Document1 pageOa6nn0 526Abdel Hamied EbrahemNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Abdel Ha Me Ed IbrahimDocument1 pageAbdel Ha Me Ed IbrahimAbdel Hamied EbrahemNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Abdel Hamed Ibrahim Abdel Hamed PDFDocument1 pageAbdel Hamed Ibrahim Abdel Hamed PDFAbdel Hamied EbrahemNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Sheet - 1Document2 pagesSheet - 1Abdel Hamied EbrahemNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- PLCDocument9 pagesPLCAbdel Hamied EbrahemNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- 8086 Microprocessor Instruction Set GuideDocument49 pages8086 Microprocessor Instruction Set GuideAbdel Hamied EbrahemNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Full Page PhotoDocument3 pagesFull Page PhotoAbdel Hamied EbrahemNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- 8086 MicroprocessorDocument8 pages8086 MicroprocessordiNo ratings yet

- AlphaDocument2 pagesAlphaAbdel Hamied EbrahemNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- PLC 2Document7 pagesPLC 2Abdel Hamied EbrahemNo ratings yet

- Elliptical Trammel Mechanism FinalDocument4 pagesElliptical Trammel Mechanism FinalAbdel Hamied Ebrahem100% (1)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Sheet - 2Document3 pagesSheet - 2Abdel Hamied EbrahemNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Sheet - 3Document2 pagesSheet - 3Abdel Hamied EbrahemNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- TOT RequirementDocument4 pagesTOT RequirementAbdel Hamied EbrahemNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Check your charging system for proper operationDocument16 pagesCheck your charging system for proper operationAbu AliNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Solution ManualDocument42 pagesSolution ManualAbdel Hamied EbrahemNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- CHPT 1Document47 pagesCHPT 1Herb Johnson100% (1)

- Solution ManualDocument42 pagesSolution ManualAbdel Hamied EbrahemNo ratings yet

- Fundamentals of Stress Analysis ConclusionDocument11 pagesFundamentals of Stress Analysis ConclusionAbdel Hamied EbrahemNo ratings yet

- 1 - 1 - 11 Schematic Drawing-EHDocument2 pages1 - 1 - 11 Schematic Drawing-EHWahyu SaputraNo ratings yet

- 60V Complementary Enhancement Mode FET FeaturesDocument9 pages60V Complementary Enhancement Mode FET FeaturesAhmad MaufiqNo ratings yet

- 1209B 1221B 1221C 1231C CurtisDocument56 pages1209B 1221B 1221C 1231C CurtiscristiancerdaNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Troubleshooting: 5.1 Troubleshooting For Circuit-Breaker Proper (MCCB/ELCB)Document6 pagesTroubleshooting: 5.1 Troubleshooting For Circuit-Breaker Proper (MCCB/ELCB)ARUNPRASADEEENo ratings yet

- Unit 3Document62 pagesUnit 3KruthiKolliNo ratings yet

- Arcode Error Descriptions.V211.EnDocument27 pagesArcode Error Descriptions.V211.EnЕкатерина АндрееваNo ratings yet

- Oti & Wti: Salient FeaturesDocument3 pagesOti & Wti: Salient FeaturesKarthik_Govind_6702No ratings yet

- Power System: DPS 2400B-48-12Document2 pagesPower System: DPS 2400B-48-12Salvatore BasileNo ratings yet

- Catalog - Wastewater DuplexDocument2 pagesCatalog - Wastewater DuplexYohemir MarinNo ratings yet

- U440/441 - Matched N Channel JFET PairsDocument7 pagesU440/441 - Matched N Channel JFET PairsGuillermo HernandezNo ratings yet

- Digsilent GMBH: P1843 - Optimization of The Protection Settings For The 115 KV Electrical Power System of PEA in ThailandDocument22 pagesDigsilent GMBH: P1843 - Optimization of The Protection Settings For The 115 KV Electrical Power System of PEA in ThailandGIngaa100% (1)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- General Check List - ElectricalDocument2 pagesGeneral Check List - ElectricalSanthoshNo ratings yet

- Introduction To Nanoscience and Nanotechnology (ECE1006)Document13 pagesIntroduction To Nanoscience and Nanotechnology (ECE1006)Dhruv KapadiaNo ratings yet

- FB 17000Document2 pagesFB 17000Ren MatNo ratings yet

- PDFDocument15 pagesPDFronnymareNo ratings yet

- 30 3001 837 B Link Installation InstructionsDocument2 pages30 3001 837 B Link Installation InstructionsMark Izsm AmersonNo ratings yet

- KA7500 DatasheetDocument6 pagesKA7500 DatasheetSergio Daniel BarretoNo ratings yet

- Flow Switches PMDocument4 pagesFlow Switches PMudayNo ratings yet

- Data Sheet MX 1800 4Document7 pagesData Sheet MX 1800 4Edgar Bonilla MuñozNo ratings yet

- Overveiw and Operation ProcessDocument34 pagesOverveiw and Operation ProcessSoeAyeNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- CMOS Logic FamilyDocument16 pagesCMOS Logic FamilyAditya SahareNo ratings yet

- 465 Lab 2Document11 pages465 Lab 2Young Muller MotlhobogwaNo ratings yet

- Planos de Interruptor 60kVDocument22 pagesPlanos de Interruptor 60kVLuis VasquezNo ratings yet

- 35422-75 Product SpecificationsDocument5 pages35422-75 Product SpecificationsPhi FeiNo ratings yet

- ABB Price Book 455Document1 pageABB Price Book 455EliasNo ratings yet

- 24-27 - Ac Generation Monitoring and Indicating PDFDocument19 pages24-27 - Ac Generation Monitoring and Indicating PDFMohammad NorouzzadehNo ratings yet

- KNXDocument24 pagesKNXGabetsos KaraflidisNo ratings yet

- Tmdrive: Ac/Dc Drive SeriesDocument8 pagesTmdrive: Ac/Dc Drive SeriesEliasNo ratings yet

- Dieseal Level ControllerDocument1 pageDieseal Level ControllersanjaybmscseNo ratings yet

- Penn Commercial Refrigeration: Transducers and SensorsDocument3 pagesPenn Commercial Refrigeration: Transducers and SensorsRonNo ratings yet

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeFrom EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeRating: 5 out of 5 stars5/5 (8)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionFrom EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionRating: 4.5 out of 5 stars4.5/5 (542)

- High Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsFrom EverandHigh Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsRating: 4 out of 5 stars4/5 (1)