Professional Documents

Culture Documents

Digital Logic Design Course Outline 3rd Year

Uploaded by

kibrom atsbha0 ratings0% found this document useful (0 votes)

25 views2 pagescoure outline 3rd 1st semister

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentcoure outline 3rd 1st semister

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

25 views2 pagesDigital Logic Design Course Outline 3rd Year

Uploaded by

kibrom atsbhacoure outline 3rd 1st semister

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 2

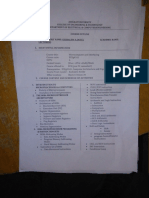

COLLEGE OF ENGINEERING & TECHNOLOGY

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

COURSE PLAN

COURSE TITLE & CODE: Digital Logic Design (ECE3141)

‘Academic year: 2010 EG Semester:

Instructors’ name:

|. BisrarK. (Ass Lecturer). Mebrahtu ¥.(Ass Lecturer), Abrehet G. (Ass. Lecturer)

L.tdentifying Information

Coursetite: DigitaLLogic Design

Coursecode: ECEG3141

EcTSCredits: 6

Contact hours: (LECHR + Tut. HR + Lab. HR)/WEEK: (7)

Course offered to Electrical & Computer Engineering (year Ill,semester 1)

Prerequisites: ECEg2113: Applied Electronics I

Course team leader: —_Bisrat Kahsay

Office location: Block 1 Room 31

Telephone 0914180668, Email: bisatkahsay@zmallcom

“Teaching team members & their e-mail:

i) Bisrat Kahsay, bisratkahsay@gmail.com

Mebrahtu Yohannes, mebrahtuyonni@smailcom

il) Abvehet Gebreslassie, abrhten27@emal.com

2, course Description

‘This course provides an overview of the principles underying Number systems, arithmetic operafions, decimal

codes, alphanumeric codes, Boolean algebra, Karsugh maps, implementation of dial lop ates sing universal

fates (NAND and NOR gates), exclusive-OR gates, iterated circuits, combinational cies, decoders, ender

aliplexers, Demitpleses, adders, sub actor, mulipir, sequential circuits, latches, lips, se

“reuts analysis and counts, Finally, nder tis cours, Analysis and design of combinational and sequent logic

systems wil be done

'B. Course Content and Schedule of Activities

‘Week | Content Testu Turon, Wests, assignments

ee

Weck] I> Introduction to Digital Systems > Lectures 1&2

1 Digital and analogue guantt

1.2 Binary digit, logic evel and digital waveform

‘Number stems, operations and codes = Lectures 34

2.1, Decimal Numbers é ‘+ Tutorials 1.2

22. Binary Numbers

2.3. Decimal to | Number Conversion

own a ay Nunbes

5 fiitions

5.2. Axiomatic Definition of Boolean Algebra

33. Boolean Functions

34 Canonial and Standard Forms

4.5, Other Lape Operations

36, Digtal Logie Gates

27, Simplification of Boolean Functions

{Combinational loge

4.1 ttrdution

42. Base Combinational Loge Circuits

‘43. implementing Combinational Logie

‘14, Unvversal property of NAND and NOR gates

445. Adders and Subractors

46, Decoders and Encoders

445. Muniplexer and Demutipleves __

Sequential Loge

si nioduetion

52. Flip-Flops

53 Tiggering of Flip-Flops

$8, Anayss af Clocked Sequential Circuits

|. 35. SateRedrtion an Assament

56, Flip-Flop Exiaton Tables

| | See

[wea] Conners and Regier

| week 13 | 6.1. tntroduetion

2. Repaer

| | 63 shitresisers

|) G4 Ripe counters

\ |, G5: Synchronous Counters

| 66 Ting Seances

| WeacTa—}7. Memory and storage onions

[Nexis |" 21'Beses orsemconectr nemon

75: Ransom sree memory (RAND

| 73. Rend only memory (ROM)

| 72. Progammat ROM PRON

[| 1s rashimemori iti

A, Assessment

eeesainuous Assessment 60% and Final exam 40%:

15, Texts and Supporting Materials

+ Textbook:

LI. Mons M.Mano: Digi! Lops and Computer Desien

+ References

1], Mano, M- Mon Chas R. Kime and Martin. To

sorgial Fundamental, edition Prentice Hal

B). TL Foy

{BYR Pa: Moser Digital etnies

Logic & Computer Design uname

T= tecture 36,7

1 Turia 3,4, 5.86

|

res 10

1 Tutorial 7 8

1b 82

+ Test #2(05%)

1 Lab Report #1 (5%)

> Lectures 11 12

{Tutor 9 & 10

rere)

+ Test 3 (100)

Lab Report 2 (5%)

[> Cetus 18

{Toto 10. 1

fuses

sea, 2015

Hl SiencelEnginering Math edition, 2006

You might also like

- SSC English Topic-Wise LATEST 35 Solved PapersDocument139 pagesSSC English Topic-Wise LATEST 35 Solved Paperskibrom atsbha100% (1)

- 1000 Electronic Devices & Circuits MCQsDocument467 pages1000 Electronic Devices & Circuits MCQskibrom atsbha67% (3)

- 1000 Electrical Machines MCQsDocument458 pages1000 Electrical Machines MCQskibrom atsbha100% (4)

- Pe Tutorial 7 PDFDocument14 pagesPe Tutorial 7 PDFkibrom atsbhaNo ratings yet

- Pe Tutorial 2 PDFDocument10 pagesPe Tutorial 2 PDFkibrom atsbhaNo ratings yet

- 1000 Digital Signal Processing MCQsDocument405 pages1000 Digital Signal Processing MCQskibrom atsbha42% (12)

- 1000 Electric Circuits MCQsDocument100 pages1000 Electric Circuits MCQskibrom atsbhaNo ratings yet

- Pe Tutorial 5 PDFDocument9 pagesPe Tutorial 5 PDFkibrom atsbhaNo ratings yet

- 1000 Electromagnetic Theory MCQsDocument369 pages1000 Electromagnetic Theory MCQskibrom atsbha50% (14)

- Three-Phase Controlled Rectifier TutorialDocument7 pagesThree-Phase Controlled Rectifier Tutorialkibrom atsbhaNo ratings yet

- Pe Tutorial 8 PDFDocument3 pagesPe Tutorial 8 PDFkibrom atsbhaNo ratings yet

- Pe Tutorial 9 PDFDocument5 pagesPe Tutorial 9 PDFkibrom atsbhaNo ratings yet

- Introduction To ComputingDocument3 pagesIntroduction To Computingkibrom atsbhaNo ratings yet

- Power Electronics Controlled RectificationDocument13 pagesPower Electronics Controlled Rectificationkibrom atsbhaNo ratings yet

- Power Electronics Controlled RectificationDocument13 pagesPower Electronics Controlled Rectificationkibrom atsbhaNo ratings yet

- Microcomputer and Interfacing Course OutlineDocument2 pagesMicrocomputer and Interfacing Course Outlinekibrom atsbhaNo ratings yet

- Pe Tutorial 6 PDFDocument12 pagesPe Tutorial 6 PDFkibrom atsbhaNo ratings yet

- Pe Tutorial 1Document8 pagesPe Tutorial 1kibrom atsbhaNo ratings yet

- Electrical Measurement and Instrumentation Course OutlineDocument2 pagesElectrical Measurement and Instrumentation Course Outlinekibrom atsbhaNo ratings yet

- Applied Electronics 1Document4 pagesApplied Electronics 1kibrom atsbha83% (6)

- Electrical Material and Technology Course OutlineDocument3 pagesElectrical Material and Technology Course Outlinekibrom atsbha50% (2)

- Fundamental of Electrical EngineeringDocument4 pagesFundamental of Electrical Engineeringkibrom atsbhaNo ratings yet

- Introduction To Electrical MachinesDocument3 pagesIntroduction To Electrical Machineskibrom atsbhaNo ratings yet

- Electrical Installation Course OutlineDocument3 pagesElectrical Installation Course Outlinekibrom atsbhaNo ratings yet

- Modern Control System Course OutlineDocument2 pagesModern Control System Course Outlinekibrom atsbhaNo ratings yet

- Work ShopDocument2 pagesWork Shopkibrom atsbhaNo ratings yet

- Process Control Fundamental Course OutlineDocument3 pagesProcess Control Fundamental Course Outlinekibrom atsbhaNo ratings yet

- Computer ArictectureDocument2 pagesComputer Arictecturekibrom atsbhaNo ratings yet

- Communication SystemDocument2 pagesCommunication Systemkibrom atsbhaNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)