Professional Documents

Culture Documents

E 02 CH 04

Uploaded by

Tariq ZuhlufOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

E 02 CH 04

Uploaded by

Tariq ZuhlufCopyright:

Available Formats

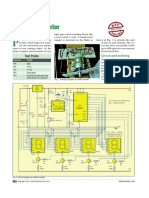

SMALL CIRCUITSCOLLECTION

ferent gain levels, namely 0 dB (1 ×), 5 dB (1.778 ×), 6 dB (2 ×), necting two E96 values in parallel.

10 dB (3.162 ×), 14 dB (5 ×) and 20 dB (10 ×). The first table is At the higher gain levels, and particularly at high frequencies,

also necessary if you want to convert the filter from low-pass a very fast type of opamp must be used to avoid having it

to high-pass. affect the signal transfer. In order to keep deviations (in fre-

Table 2 shows more practical component values for the same quency and amplitude) as small as possible, the use of 1%

gains. Exact E12 values have been used for the capacitors, components is highly recommended (especially at higher

and we have calculated the theoretical values of the resistors gains).

for you so they can be implemented very accurately by con- (024115-1)

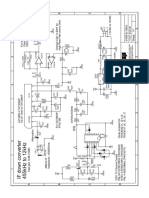

Long-Interval Timer 004

G. Ruschitzka

+5V

Occasionally there is a need for a timer circuit for tasks such as C2 C3

switching off a circuit element (such as an LC display) after a R4

47µ 100n IC1 16

given interval or generating a time delay for an application. 27k

16V

7

Short intervals can be conveniently generated using a 555 CTR14 3

5

4

timer, but if the switch-off time lies in the range of minutes or R3

4

470k 5

!G

longer, a 555 is no longer suitable due to the large value R1

11

RCX 6

6

10 14

required for the capacitor, which leads to inaccuracies or insta- 220k RX + 7

9 CT 13

R2 C1 CX 8

bility. In such cases, a digital counter circuit with an oscillator 2k2 9

15

1

is a better solution. TRIGGER 220n 11

2 TIMEOUT

12

The 74HCT4060 IC, with its built-in oscillator, can cover a wide 12

CT=0 3

13

range of frequencies in a simple and reliable manner and can

T1 D1 R5 8

also generate very low frequencies. The 14-bit divider chain

27k

74HCT4060N

can divide the oscillator frequency by up to 16,384, which

BC237 BAT48

makes it easy to obtain long time intervals.

024065 - 11

The circuit presented here acts like a digital monostable. The

timeout time starts when the system is switched on, since a

Low level is initially present on the selected output of the ON TRIGGER TRIGGER

counter IC (Q13 or any other desired output Q2–Q12). This

represents the active (On) state for the connected circuit. After TRIGGER

the counter chain has counted up enough for the selected out-

put to switch to the High state, the oscillator is cut off by tran-

OUTPUT

sistor T1 so that no further counting pulses can be generated.

TIMEOUT TIMEOUT TIMEOUT

The circuit thus remains in this state. The High signal level rep-

024065 - 12

resents a ‘rest state’ for the connected circuit.

In order to reactive the timeout, a positive pulse is applied to

the Reset input (pin 12). The circuit re-triggers, the Q output following circuit.

goes Low immediately (active) and a new timeout starts. The timeout interval is given by the formula

To make the selection of counter outputs flexible, a DIP switch

can be used as long as only one switch at a time is activated, timeout = 2n ÷ fosc

since otherwise short circuits will be created between the with

counter outputs. It is also useful to connect one of the n = selected output stage (n = 3–13)

switches to Vcc via a small resistance. If this switch is acti- fosc = 1 ÷ (2.5⋅(R1⋅C1))

vated, the connected circuit is permanently disabled, while if

neither this switch nor any of the other switches is activated, With the indicated component values (R1 = 220 kΩ, C1 =

the circuit is permanently enabled. This covers all possible 220 nF), the frequency is 8.3 Hz and the timeout interval at Q13

operating situations. It is important to keep the load small. If is 16.5 minutes.

necessary, a CMOS gate (inverter) can be used to buffer the (024065-1)

12/2002 Elektor Electronics 23

You might also like

- Cyclic Timer Using 555 1 PDFDocument1 pageCyclic Timer Using 555 1 PDFNguyen Phuoc HoNo ratings yet

- Aplicaciones Con El Ne - 558Document5 pagesAplicaciones Con El Ne - 558julio_m_pNo ratings yet

- Optimise Your PC Soundcard 2003Document3 pagesOptimise Your PC Soundcard 2003Peeters GuyNo ratings yet

- Closed Loop Brushless Motor Adapter: Semiconductor Technical DataDocument8 pagesClosed Loop Brushless Motor Adapter: Semiconductor Technical DataVictor HemzNo ratings yet

- AT89C2051-based Countdown TimerDocument3 pagesAT89C2051-based Countdown TimerKumawat ArunNo ratings yet

- Slua 253Document4 pagesSlua 253armin rahmatiNo ratings yet

- RF Remote Control Receiver Circuit Extends RangeDocument2 pagesRF Remote Control Receiver Circuit Extends RangeTariq ZuhlufNo ratings yet

- NCP1396A, NCP1396B Controller, High Performance Resonant Mode, With High and Low Side DriversDocument26 pagesNCP1396A, NCP1396B Controller, High Performance Resonant Mode, With High and Low Side DriversMaria VaccarielloNo ratings yet

- Replacing Electromechanical SwitchesDocument12 pagesReplacing Electromechanical Switchesccuenin777No ratings yet

- Easy Home Remote Control: Carlos FerreiraDocument3 pagesEasy Home Remote Control: Carlos FerreiraJohn SmithNo ratings yet

- Electronic Digital ClockDocument5 pagesElectronic Digital ClockRefaat RaslanNo ratings yet

- Internal Guide: R.Valarmathi M.E., Lecturer, Department of EEE, DsecDocument26 pagesInternal Guide: R.Valarmathi M.E., Lecturer, Department of EEE, Dsecsetsindia3735No ratings yet

- Isolated Continuous Conduction Mode Flyback Using The TPS55340Document16 pagesIsolated Continuous Conduction Mode Flyback Using The TPS55340pietisc pietiscNo ratings yet

- Practical-Electronics-1973-09 Phase UnitDocument4 pagesPractical-Electronics-1973-09 Phase UnitJohan TaalanderwijsNo ratings yet

- Simple Tachometer Input Circuits for Ford SRF EngineDocument3 pagesSimple Tachometer Input Circuits for Ford SRF EngineSơn PhạmNo ratings yet

- If 455 To 12khzDocument5 pagesIf 455 To 12khzarg0nautNo ratings yet

- D D D D D D: NE556, SA556, SE556 Dual Precision TimersDocument5 pagesD D D D D D: NE556, SA556, SE556 Dual Precision TimerssomtchekusNo ratings yet

- Simple Slave Flash: F RoeskyDocument1 pageSimple Slave Flash: F RoeskyJohn SmithNo ratings yet

- TC25C25 TC35C25 Bicmos PWM Controllers: General Description FeaturesDocument8 pagesTC25C25 TC35C25 Bicmos PWM Controllers: General Description Featuresparsa mahvisNo ratings yet

- Universal Thermostat: Ruud Van SteenisDocument2 pagesUniversal Thermostat: Ruud Van Steeniscsaba1111No ratings yet

- D D D D: SN54ACT374, SN74ACT374 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsDocument22 pagesD D D D: SN54ACT374, SN74ACT374 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsMarta_d_eNo ratings yet

- DVD Noblex Dvd-1350: 3828 Control Borad SechmaticDocument15 pagesDVD Noblex Dvd-1350: 3828 Control Borad SechmaticMariano Ohienart100% (1)

- CDC2510Document9 pagesCDC2510terry panNo ratings yet

- To Study On-Time Delay Relay & Off-Time Delay Relay: Operating ManualDocument16 pagesTo Study On-Time Delay Relay & Off-Time Delay Relay: Operating ManualSharib JalisNo ratings yet

- 99 Seconds TimerDocument2 pages99 Seconds Timernexsait naranjoNo ratings yet

- Half Bridge Driver With IR2153 IGBT PDFDocument4 pagesHalf Bridge Driver With IR2153 IGBT PDFShibu Kumar SNo ratings yet

- Switch AmplifierDocument6 pagesSwitch AmplifierRamesh KumarNo ratings yet

- Esq Eletrico Nav PDFDocument5 pagesEsq Eletrico Nav PDFLuiz Guilherme Rodrigues BrandãoNo ratings yet

- ElectronicsForYou201401 Rotation CounterDocument2 pagesElectronicsForYou201401 Rotation CounterAnonymous JoB5ZxgNo ratings yet

- MC34163-D Switching RegulatorDocument16 pagesMC34163-D Switching RegulatorEdgar DauzonNo ratings yet

- Upto 36kV 25/31.5kA 630A...2500A GAS INSULATED SWITCHGEAR (Plugin type busbar segregationDocument4 pagesUpto 36kV 25/31.5kA 630A...2500A GAS INSULATED SWITCHGEAR (Plugin type busbar segregationWHad SRabutNo ratings yet

- 6.002 Demo# 26 RC Response Agarwal Fall 00Document3 pages6.002 Demo# 26 RC Response Agarwal Fall 00MitpdfNo ratings yet

- Circuito de FuenteDocument8 pagesCircuito de FuenteEmer nelsonNo ratings yet

- ADC and UART Data ConversionDocument9 pagesADC and UART Data ConversionTrần Ngọc Thiên DiNo ratings yet

- In-Plug Series: IPS201: Revision 4Document10 pagesIn-Plug Series: IPS201: Revision 4chafic WEISSNo ratings yet

- Analog-to-Digital Conversion Utilizing The AT89CX051 MicrocontrollersDocument6 pagesAnalog-to-Digital Conversion Utilizing The AT89CX051 MicrocontrollersJuan Jose MendozaNo ratings yet

- Clap SwitchDocument1 pageClap SwitchSaravana_Kumar_4984No ratings yet

- Black Light PCB Dash 2500Document4 pagesBlack Light PCB Dash 2500Théu CastroNo ratings yet

- CedricDocument11 pagesCedricenhle100% (1)

- Flyback transformer specification and circuit diagramDocument2 pagesFlyback transformer specification and circuit diagramRodrigoNo ratings yet

- The 555 TimerDocument14 pagesThe 555 Timergurudatha265100% (4)

- Test 777888 PPPQQQDocument3 pagesTest 777888 PPPQQQLeonard GržetićNo ratings yet

- Irjet V8i5487Document3 pagesIrjet V8i5487Sado HusseinYusufNo ratings yet

- Tpic6595 PDFDocument9 pagesTpic6595 PDFljNo ratings yet

- Stepper Motor Driver: Semiconductor Technical DataDocument6 pagesStepper Motor Driver: Semiconductor Technical Dataالكترونيات يافاNo ratings yet

- Practical Treatise on the Tow-Thomas Biquad Active FilterDocument4 pagesPractical Treatise on the Tow-Thomas Biquad Active FilterPaul Shine EugineNo ratings yet

- Power Switching Regulators: Semiconductor Technical DataDocument16 pagesPower Switching Regulators: Semiconductor Technical DataAkramNo ratings yet

- Buffer, Driver & RelayDocument6 pagesBuffer, Driver & RelayramNo ratings yet

- 4-bit analogue-to-digital converter circuit and bi-directional I2C level shifter explainedDocument1 page4-bit analogue-to-digital converter circuit and bi-directional I2C level shifter explainedNaur AvilaNo ratings yet

- ISL95813HRZDocument26 pagesISL95813HRZVasanth KumarNo ratings yet

- 555 Timer Ic - An170Document19 pages555 Timer Ic - An170acidreign100% (1)

- Speakers CircuitDocument3 pagesSpeakers CircuitSantosh TalankarNo ratings yet

- Inverse-Time Overcurrent & E/F Relay GuideDocument8 pagesInverse-Time Overcurrent & E/F Relay Guiderkanth3203No ratings yet

- Barijera 1Document6 pagesBarijera 1proba.probic.32No ratings yet

- KCD2 RR Ex1Document5 pagesKCD2 RR Ex1anon_291507036No ratings yet

- DC Motor Speed & Direction Controller With Brake Using Mc33035Document3 pagesDC Motor Speed & Direction Controller With Brake Using Mc33035Mile MartinovNo ratings yet

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- E 905030Document4 pagesE 905030Tariq ZuhlufNo ratings yet

- Practical Neural Networks (3) : Part 3 - Feedback Nets and Competitive NetsDocument5 pagesPractical Neural Networks (3) : Part 3 - Feedback Nets and Competitive NetsTariq Zuhluf100% (2)

- Main voltage monitor provides emergency lighting under 40 charactersDocument1 pageMain voltage monitor provides emergency lighting under 40 charactersTariq Zuhluf100% (2)

- Design Ideas: Keyboard CircuitDocument2 pagesDesign Ideas: Keyboard CircuitTariq Zuhluf100% (3)

- Ensors FOR Humans: Sensor Technology at MITDocument4 pagesEnsors FOR Humans: Sensor Technology at MITTariq ZuhlufNo ratings yet

- E 037028Document1 pageE 037028Tariq Zuhluf100% (2)

- Slave Mains On-Off Control: Amplificationj Attenuation SelectorDocument3 pagesSlave Mains On-Off Control: Amplificationj Attenuation SelectorTariq Zuhluf100% (2)

- E 01 C 093Document5 pagesE 01 C 093Tariq ZuhlufNo ratings yet

- E 05 B 040Document7 pagesE 05 B 040Tariq Zuhluf100% (2)

- E 055077Document1 pageE 055077Tariq ZuhlufNo ratings yet

- Seven-Eleven: Ir NVDocument3 pagesSeven-Eleven: Ir NVTariq Zuhluf100% (2)

- Psd3Xx Chips: by A. Riet JensDocument3 pagesPsd3Xx Chips: by A. Riet JensTariq Zuhluf100% (1)

- REMOTE CONTROL CIRCUIT BY MOBILE PHONEDocument4 pagesREMOTE CONTROL CIRCUIT BY MOBILE PHONETariq Zuhluf100% (2)

- In Questof A PangramDocument5 pagesIn Questof A PangramTariq Zuhluf100% (1)

- PC Interface For The CAN Bus: With New SoftwareDocument5 pagesPC Interface For The CAN Bus: With New SoftwareTariq Zuhluf100% (2)

- Noise of The The V /115.: R.rn.sDocument1 pageNoise of The The V /115.: R.rn.sTariq Zuhluf100% (1)

- Current Probe: Parts ListDocument1 pageCurrent Probe: Parts ListTariq Zuhluf100% (2)

- Universal Power-On Delay: by J. RuffellDocument1 pageUniversal Power-On Delay: by J. RuffellTariq Zuhluf100% (2)

- Digital Bechtop Power Supply (2) : Part 2: Soldering, Sawing and DrillingDocument5 pagesDigital Bechtop Power Supply (2) : Part 2: Soldering, Sawing and DrillingTariq ZuhlufNo ratings yet

- Token Number Display: Small CircuitscollectionDocument1 pageToken Number Display: Small CircuitscollectionTariq Zuhluf100% (2)

- E 02 CH 43Document1 pageE 02 CH 43Tariq Zuhluf100% (2)

- E051042 PDFDocument2 pagesE051042 PDFTariq ZuhlufNo ratings yet

- Wireless Museum: Components ListDocument1 pageWireless Museum: Components ListTariq Zuhluf100% (1)

- Stereo Peak Indicator: Small CircuitscollectionDocument1 pageStereo Peak Indicator: Small CircuitscollectionTariq Zuhluf100% (1)

- Speed-Up For Darlingtons: Small CircuitscollectionDocument1 pageSpeed-Up For Darlingtons: Small CircuitscollectionTariq Zuhluf100% (1)

- E 986024Document1 pageE 986024Tariq Zuhluf100% (1)

- E 03 B 035Document1 pageE 03 B 035Tariq Zuhluf100% (1)

- Measuring current with three external componentsDocument4 pagesMeasuring current with three external componentsTariq Zuhluf100% (1)

- Idc To Box Header Adaptor: ReferenceDocument2 pagesIdc To Box Header Adaptor: ReferenceTariq Zuhluf100% (1)

- Vestel 17mb37 SMDocument110 pagesVestel 17mb37 SMvideosonNo ratings yet

- Senring H Series SlipRing Catalog PDFDocument74 pagesSenring H Series SlipRing Catalog PDFremeenNo ratings yet

- Mixed Signal Power Manager For Smartfusion Reference Design: User'S GuideDocument80 pagesMixed Signal Power Manager For Smartfusion Reference Design: User'S GuideFajar SantosoNo ratings yet

- Flexible AC Transmission Systems (FACTS) : Nawazish Ali 12063122-047Document18 pagesFlexible AC Transmission Systems (FACTS) : Nawazish Ali 12063122-047Muntasir AnwarNo ratings yet

- Synchronization PCB: This Module Is One of A Series of Modules That Describe The Components of The M SystemDocument12 pagesSynchronization PCB: This Module Is One of A Series of Modules That Describe The Components of The M SystemSatyajit KhuntiaNo ratings yet

- Full Custom IC Design Flow TutorialDocument101 pagesFull Custom IC Design Flow TutorialharivarahiNo ratings yet

- Urit 3000 Plus InstrumentDocument2 pagesUrit 3000 Plus InstrumentBilogba Alex67% (3)

- Onkyo Onwer's Manual TX-SR803 703 PDFDocument96 pagesOnkyo Onwer's Manual TX-SR803 703 PDFVidiNo ratings yet

- Toshiba & Beko 26WL46, 27WL46, 30WL46, 32WL46 LCD TV PDFDocument107 pagesToshiba & Beko 26WL46, 27WL46, 30WL46, 32WL46 LCD TV PDFGursharan SinghNo ratings yet

- I 6 o 6 NDDocument2 pagesI 6 o 6 NDFathur RachmanNo ratings yet

- Simulation of EMI Filters Using Matlab: M.Satish Kumar, Dr.A.JhansiraniDocument4 pagesSimulation of EMI Filters Using Matlab: M.Satish Kumar, Dr.A.JhansiraniDhanush VishnuNo ratings yet

- Models - Acdc.inductor in CircuitDocument14 pagesModels - Acdc.inductor in CircuitneomindxNo ratings yet

- Generator Set Iso8528!5!2005 Operating LimitsDocument1 pageGenerator Set Iso8528!5!2005 Operating Limitsswsw2011No ratings yet

- WiFi TechnologyDocument35 pagesWiFi TechnologySmitesh MukaneNo ratings yet

- Cao Question Bank Unit 1-5 BT Format 2020-2021Document4 pagesCao Question Bank Unit 1-5 BT Format 2020-2021Nikhil TiruvaipatiNo ratings yet

- 76 - 8271423M - B FGTM-MDocument32 pages76 - 8271423M - B FGTM-MHamza_yakan967No ratings yet

- Dynamics of DC Drives: Professor Damir Zarko Associate Professor Igor ErcegDocument39 pagesDynamics of DC Drives: Professor Damir Zarko Associate Professor Igor Ercegts45306No ratings yet

- X5-400M Matlab BSP ManualDocument71 pagesX5-400M Matlab BSP Manualmidlopez83No ratings yet

- TK100 GPS Tracker User ManualDocument12 pagesTK100 GPS Tracker User ManualEdris K Pagocag100% (2)

- Qam ReportDocument12 pagesQam ReportJAwad HAmeedNo ratings yet

- Enutv-3 Um enDocument25 pagesEnutv-3 Um enKelly Carolina VianaNo ratings yet

- Statement of PurposeDocument2 pagesStatement of Purposesamytoosexy100% (2)

- Antennas - IntroductionDocument54 pagesAntennas - IntroductionAbhishek VarmaNo ratings yet

- Avr-S640h Eng SM v01Document140 pagesAvr-S640h Eng SM v01Toshio HirahataNo ratings yet

- Yaesu ft897 ManualDocument72 pagesYaesu ft897 ManualAndy100% (1)

- Ec 8001 Unit 3Document26 pagesEc 8001 Unit 3AlibabaNo ratings yet

- Guide to Using the Satmotion Pocket App for PCDocument25 pagesGuide to Using the Satmotion Pocket App for PCHans Michael Estay JaraNo ratings yet

- Computer Organization and Architecture - Basic Processing Unit (Module 5)Document76 pagesComputer Organization and Architecture - Basic Processing Unit (Module 5)Shrishail BhatNo ratings yet

- Gaopeng enDocument14 pagesGaopeng enGeorge HNo ratings yet

- Long Range Narrow Field Security Sensor Data SheetDocument13 pagesLong Range Narrow Field Security Sensor Data SheetEleazar DavidNo ratings yet