Professional Documents

Culture Documents

Psd3Xx Chips: by A. Riet Jens

Uploaded by

Tariq ZuhlufOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Psd3Xx Chips: by A. Riet Jens

Uploaded by

Tariq ZuhlufCopyright:

Available Formats

M icrOPl'ocessors are power-

ful devices and it is,

therefore, not to be wondered

PSD3XX CHIPS known as Address Strobe 01'

AS). The polarity ofthe inputs

is deterrnined by the operator

at that their popularity has as required. As lang as the

grown so fast in such a short ALE 01' AS signals is valid, the

time. A disadvantage remain- input stage is transparent.

ing until recently was the

By A. Riet jens When this signal becomes in-

need of several more les to active, the data are stored in

design a complete micro- the latches.

processor system. Since more The Programmable Ad-

cornponents require more dress Decoder (PAD) plays an

space and result in higher CENTRAL PROCESSING UNIT important role. It will be seen

casts, a demand arose for CPU in Fig. 2 that address Iiues

more powerful system compo- ADDRESS DATA I CONTROL An-AI5 and, if desired,

nents to simp1ify the design of A16~A19' are connected di-

a microprocessor circuit. US

PSD3XX I rectly to the PAD. Other input

chip manufacturer Wafer I

PAGING

I signals applied to the decoder

I

Scale has responded to this are RD(E), WR(R!W) and ALE

LOOIC

need with the introduction of CIRCUlTRY

DECODED (AS). Programming of the

.~

OUTPUTS

its PSD3xxx family. PAD gives tbe user the oppor-

The chips in the PSD3xxx tunity of selecting EPROM

family contain flexible 110 banks internalJy via the

ports, a PLD, Page Registers, ESo-ES7 !ines.

~

EPROM (choice of 32 kbyte, Also, there is a selection

64 kbyte, 0]' 128 kbyte), EPROM SRAM INPUT/OUTPUT signal for the static memory,

2 kbyte static RAM and some RSo·

logic circuitry to make connec- Port C is a 3-bit 1/0 port

tion with the microprocessor-

INPUT/OUTPUT

0 PORTS

with two functions: it can take

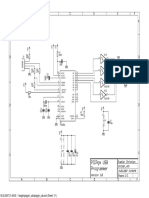

see Fig. 1. Because of the 940110 -11

internal signal CSs-CSlO out-

power of the new chips, the side, 01' it can receive address

design of a microprocessor lines A16-AIB and pass these

system 1Sbrought down to two Fig. 1. Functions that can be assumed by a PSD3xxx chip. to the PAD. Moreover, address

components (since the latch line A 19 can be passed directly

for demultiplexing of the ad- to the PAD. This shows that

dress and data buses is no the PAD 18 capable of ar-rang-

I PAGE lQGIC

longer needed). A similar "-" Al6--A18 ing an entire address decoding

• Fr

function would until recently - Al1 AlS PROG. up to 1 MHz without any ex-

have required 8 to 12 discrete

les. The chips have been de-

,~

t,

r m

CS~f'{)RT

m d LOGICIN

-

eoer

EXP. temal components.

.=:~" c '0'- Ports A and Bare 8-bit

signed to work with a variety

of microprocessor les, irrelud-

ing, for example, the 68HCll

~

~

~

I

~

I:SET

ÄLElAS

PACA

13 P.T.

I~

~

I

ÄlEIAS

I:

IRESET

PAC B

27P.T. -

,,~

CS10_

soar

c ~ ports that can be used by the

operator as conventional 1/0

pcrts. Figure 3 shows the

as weil as the Z80. The f---- • -- EPROM special mode in which 1/0

, ,,

256 K BIT·' MBIT

PSD3xxx farnily may be split ports A, Band C may be used.

into two branches: the

~AC

'I· r

'"

co,

co, This is especially useful if an

t....

c CO'

PSD31x, intended for 8-bit 8-bit processor system uses a

.-

-"

CO,

processors, and the PSD3x for I-'

CO, PRQG,

multiplexed address and data

-

eonr

16-bit processors. ~ bus (ADo-AD7)' Address lines

..

CSO- EXP.

CS7 I---

A block diagram of one of " Ag-AI5 are then available as

rr

PORT ~

the new chips, the Iß-bi t .Q!;QJ.l .- ~ BLOCK rr ~ normal and may be applied to

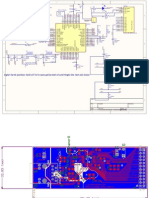

PSD30x, is given in Fig. 2. At

~~~

the address inputs. Ports B

the left are all the functions r- .- I ~ 0>0"

and C are then available as

needed to make connection 110 functions or for passing

-~ --- CSI(JPOIU

with a microprocessor; and at oo-os

~-A7 01' ADO-AD7Iines (track

the right, the 1/0 functions. I- -- mode) respectively,

The memory banks are in the 1- ~'- Apart from functioning as

centre.

Inputs ADo-AD7 reach the

'-

~~

--.. SRAM

16KBIT

TRACK MODE

"00

PORT

EXP.

an rio port, port B can also

take the chip-select signals of

SELECTS f--

nucleus of the IC via latches, ,~, "0- the PAD outside. Port C can

which can be arranged to AOO-AD71OO-07

eoat

, ~ then be used to obtain more

store data. This obviates the AlEf"'S

~ inputs, 01' for writing addi-

need of a separate register

such as a 74HCT373 or

'"',

WAIRIW

• I

PROG.CHIP

CONFIGUAATION

SECURrTY

tose tional address lines AlB-AlS,

or for taking chip-select lines

PROG. XB,X16

BHEJP EN

74HCT573. In the transparent , 00'""'"

SIGNALS

MUX '" NON--MUX BUSSES

CSa-CSIO outside.

mode, the latches function as A'91C t 940110--12

buffers. However, the latched

Address lines

mode is more usual, for exam-

pIe, with the 8031. Data stor- The 16 address lines of a mul-

age in the latches at the input tiplexed bus are stored in one

of the circu it is then accom- Fig. 2. Block diagram 01 the 16-bit PSD30x; in the B-btt or two 8-b-it wide latches, de-

plished by an ALE instruction PSD31x the 16/B demultiplexer and associated buffer pending on the type of proces-

(in Motorola processors better are not used. SOl'. With non-mul tiplexed

ELEKTOR ELECrRONICS DECEMßER 1994

-- PSO.lXX CHIPS

,~

V

ese

~

A8-AlS [110] er [AC - A7J er [ADO - AD7) ~

'"

"

, ese

~ 8 EPI'ICIM BlOCK

SEI.ECT L1NE5

ess PAD

[1/0] or [eSO - CS7] .lLE ot"'S

ese

A

~O",E

~

~ Sf1AM BtOCI( SB.ECT

~ ro_~

~.~

WlIorllM

A16, An, AlB er CS8, CS9, csro es ••• }

...

TRACKIoIC!DIO

CSAOO\JT'I CONmOl SIGNALS

940110 -13

... cso.'PBO

.., CS11P1I'

Fig. 3. The ports in the PSD3xx may have several lunctions.

... ~~~

buses, the inputs rematn the 16-bit mode, the da ta in

... C5:III'83

transparent. Address Iines the two blocks (Do-D7 and ... ~c~.

PAD

AI-AlO go direct1y to the static DS-D'5) are buffered. If it is ~CSIJl'85 B

."

memory, while address lines set to the byte-wide mode, the

Al-AU are applied to the S-bit wide data stream 18con- .., =L> CMtPIO

EPROM. The EPROM banks trolled with BHE and AO'

are selected via selection lines Which of the two bytes is ad- ." =L> CS1IPB7

ESO-ES7• which originate in

the PAD. The statie memory 1S

dressed depends on the level

of An. -"'--- --J?o csesce

CSg'PC,

AESET • ~

selected by the RSo signal that The EPROM section is di- , , , V

CS'(lIfIC<!

15 also generated by the PAD. vided into eigbt banks., which 940110-14

Address lines An-A 15and op- are selected by ESo-ES7.

tional address lines A16-A19 These signals originate in the Fig. 4. The array with which the PAD is programmed.

are used in the PAD array. PAD.

In ternallv, the memory Figure 4 shows a detailed

banks are ward wide (16 bits); sketch of the construction of grammable fuse array with an and E are used. Inputs es!

provision is made by an isola- the PAD. Depending on the EPROM-like structure. Used and Reset are used to deselect

tion buffer for splitting th is choice of the user, this seetion with Intel rnicroprocessors, the PAD, astate that is de-

into two bytes. The operation of the PSD generates the se- the PAD employs, apart from sired during power-down and

of the buffer is enabled by the lection signals from the ad- inputs Au-A19, signals ALE, initializa tion.

configuration of the PSD. If dress signals and some control RD and WR. With Motorola In the PSD301, signals

this is eonfigured to work in signals. The PAD is a repro- processors, signals RfW, AS ESo-ES7 are used 10 address

A1A2 WR RD CSIOPORT

A1 A2 WR AC CSIOPORT

CSO-CS7

REAO'----

PIN

MUX

MUX BPORT Oi

APORT Oi

0

PORT

0

WRITE Ai PIN ~:ft..E RES 01

DATA

aes Aal

CMOS OPEN csr

Ai DRAIN

o 0 CONTROL

G

aes OUTPUT

ENABLE

MULTIPLEX

MULTIPLEX REAO DIRECTION

SELECT REGISTER

I. _J.-----1-:::!-" SELECT

OPTiON

OPTION

CONFIGURATION

CONAGURATION

WAlTE RES

D1RECTION L_~

PORT B STRUCTURE

PORT A STRUCTURE ANYONEOFI",OT07

08- 015

AOO ·A07 ANYONEOFi"OT07

940110-16

940110·15 RESET

ALE RESET

Fig. 5. Structure behind a single 110 line 01 port A. Fig. 6. Structure behind a single 110 line 01 port B.

ELEKTOR ELECTRONlCS DECEMllER 1994

COMPONENTS

Two new books from Elektor Electronics

Build gOUT own Electronic Test

Instruments

In the testing and inspection of

I Build your own

Short course 8051/8032

Microncontrollers and assem-

bler

electrical and electronic equipment

a vartety of elcctronrc test Instru-

Electronic test This book prescnts a course which

descrtbes the hardware and the

ments is required. Most ofthese in-

struments are, of course, commer-

instruments software (assembler code) to make

a complete rnicrocontroller system.

cially available. However, Ior all The controller used is selected

kinds ofreason [cost, challenge) from the MCS-51 farruly produced

many researchers. enthusiasts and by Intel and others.

experimenters like to build such in- In addition to an extensive descrtp-

struments themselves. tion ofthe eontrollerboard and its

This book may heip them: it con- anctllanes, this book teaches you

tatns destgns for 17 measurtng to program MCS-51 mtcrocon-

instruments. seven generators and trollers in assembly code. ustng a

analysers, ten mtscellaneous large number oftested and exten-

instruments arid a number of an- sively documented examples.

cülanes and auxtlianes. The From the contents:

designs range from a simple multi- • low-cost controller eard

core cable tester to a • hardware extensions

sophtsucated legte analyser. Most • 8051 instruction set

of the destgns contain a spectal • programming

prtnted ctrcutt, full-scale drawings • analogue stgnal processing

[with a Iew exceptions) of wluch are • port programming

given in an appendix to atd the con-

struction. ISBN 0 905705 38 6

Beginncrs in electronics may find Price il9,95

the first chapter, dealing with mea- Published November 1994

surement techniques, a good introduction to the fasctnatrng

worlds of electronic test and measurement. Others may find Orders other than from private customers, for instanee,

in thts chapter many worthwhile refreshers on measure- bookshops, schools, colleges. ete. should be sent to

ment techniques. Gazelle Book Services Ltd, Falcon House, Queen Square,

Lancaster, England LAllRN.

ISBN 0 905705 37 8

Price il 15,95

Published December 1994

Elektor Electronics (Publishing), PO Box 1414, Dorchester, Dorset, England DT2 8YH.

the EPROM banks. There is this division. puts (for example, PAO-PAS the I/O pins of port A and/or

always one produet term input and Pi\o and PA7 output) port B.

available per EPROM bank. A is thus possible. After a reset, all bits in the

produet term, RSO, ts also Port structure Whether an 1/0 pin is data direetion register are low

used for seleeting the statie The eomplete port section of arranged as an input or an level, that is, the ports are set

memory. tbe PSD3xx chips eontains output can be determined as inputs. If in the applieation

The address and eontrol three registers: A (8 bits), B (8 with the data direction regis- only inputs are used, nothing

lines of the EPROM are split bits), and C [3 bits). These ter. Sinee this register oper- more needs to be done. If out-

irrte a block capacity of 4 to registers support various 1/0 ates dynatnically, it is possible puts are wanted, the assoei-

16 kbyte. The exaet locaticn of fuuctions. For example, ports during the exeeution of a pro- ated bits must be made high.

the bloek in the address range A and B may be arranged as gram to adapt the function of [940110)

of the proeessor can be deeided 8-bit VO ports tb at send data

freely by the user. The 2 kbyte to, and reeeive data from, ex-

available for the static RAM ternal eomponents. Figure 5 Name ofregister Offset w.r.t. base address

can be seleeted in a aimilar shows the structure of a single

manner. eell in port A, while Figure 6 Pin register port A +2 (byte)

Other produet terms pro- shows that of a single eell in Pin register port B +3 (byte)

vided by the PAD are CSIO- port B. Writing data to a port Diraction register port A +4 (byte)

PORT, CSADIN, CSADOUTl is the same as writing data to Direction register port B +5 (byte)

and CSADOUT2. The single a RAM location. Data register port A +6 (byte)

product term CSIOPORT de- Although a port ean not be Data register port B +7 (byte)

termines the base address of addressed at bit level , it is Pin register ports A and B +2 (word

ports A and B. An offset must possible to determine of each Directionregister ports Aand B +4 (word)

be added to this base address I/O line whether it is arranged Data register ports A and B +6 (word)

to reaeh the various registers. as input or as output. Any

'Table 1 shows the structure of eombination of inputs and out- Table 1, Addressing 01 Ihe ports.

ELEKTOR ELECTRONICS DECEMBER 1994

You might also like

- Design and Functional Verification of I2C Master Core Using OVMDocument6 pagesDesign and Functional Verification of I2C Master Core Using OVMPraveen Kumar100% (1)

- Make The Smartpic Serial Programmer: Feature ArticleDocument5 pagesMake The Smartpic Serial Programmer: Feature Articlersanchez-100% (1)

- SCHEMATIC2 LedDriverDocument1 pageSCHEMATIC2 LedDriverthanhlinh9191100% (1)

- DS3231 Extremely Accurate I C-Integrated RTC/TCXO/Crystal: General Description Benefits and FeaturesDocument20 pagesDS3231 Extremely Accurate I C-Integrated RTC/TCXO/Crystal: General Description Benefits and Featuresalfian100% (1)

- Advance Screen Operation I. Objectives: Computer System Organization With Assembly LanguageDocument8 pagesAdvance Screen Operation I. Objectives: Computer System Organization With Assembly LanguageJohn Paulo Ganado100% (1)

- PIC Microcontroller ArchitectureDocument20 pagesPIC Microcontroller ArchitecturePeeyush Kp100% (1)

- ArduiTouch ESP Schematic V01!03!00Document1 pageArduiTouch ESP Schematic V01!03!00nhan tt100% (1)

- Self Balancing Robot Circuit DiagramDocument1 pageSelf Balancing Robot Circuit DiagramCalin Popescu100% (1)

- Lpi Nano DockDocument2 pagesLpi Nano Dockmundomusicalmeria100% (1)

- Scala 14L PDFDocument1 pageScala 14L PDFkuvalda2000100% (1)

- Oled 12832Document1 pageOled 12832jonathan081986@gmail.com100% (2)

- LG 47LS5700 UA - 47LS579C - Chasis LA22E PDFDocument1 pageLG 47LS5700 UA - 47LS579C - Chasis LA22E PDFjose4445100% (1)

- USB Chip - Choices Jul2000Document5 pagesUSB Chip - Choices Jul2000Jameskrazy100% (1)

- Invertor LCD OZ9601SDocument1 pageInvertor LCD OZ9601SRenatoMaia100% (1)

- LCD InfDocument1 pageLCD Infkottee1977100% (2)

- Seven-Eleven: Ir NVDocument3 pagesSeven-Eleven: Ir NVTariq Zuhluf100% (2)

- 8ch Telemetry Receiver PDFDocument1 page8ch Telemetry Receiver PDFJúlio Ghigiarelli Majeau100% (1)

- 3V 5V USB to TTL Serial Adapter CircuitDocument1 page3V 5V USB to TTL Serial Adapter Circuitname100% (1)

- Voltage converters and modules circuit diagramDocument2 pagesVoltage converters and modules circuit diagramardiboy100% (1)

- схема TP.VST59.PA502 PDFDocument7 pagesсхема TP.VST59.PA502 PDFFernando Guerrero100% (1)

- Noise of The The V /115.: R.rn.sDocument1 pageNoise of The The V /115.: R.rn.sTariq Zuhluf100% (1)

- GND connector for LTE moduleDocument1 pageGND connector for LTE modulesyaiful100% (2)

- w5500 Ref Rj45with20150406 PDFDocument1 pagew5500 Ref Rj45with20150406 PDFTrần Linh100% (1)

- Atmel 2575 C Functions For Reading and Writing To Flash Memory ApplicationNote AVR106Document14 pagesAtmel 2575 C Functions For Reading and Writing To Flash Memory ApplicationNote AVR106Avadhesh100% (1)

- Instructions Assembler DirectivespptDocument22 pagesInstructions Assembler DirectivespptAntra Gurain100% (1)

- Electronic Meters: Topic 4Document12 pagesElectronic Meters: Topic 4ltfadhil100% (1)

- 2-CH RS485 HAT SchDocDocument2 pages2-CH RS485 HAT SchDocgino ginelli100% (1)

- YT8511 DemoDocument3 pagesYT8511 Demo周勇100% (1)

- PIC Introduction PDFDocument46 pagesPIC Introduction PDFPeeyush Kp100% (1)

- ADC Through SPIDocument4 pagesADC Through SPIChiquita White100% (1)

- PDF Created With Pdffactory Pro Trial Version: St72C334J4Document1 pagePDF Created With Pdffactory Pro Trial Version: St72C334J4José Lanza100% (1)

- Autosteer ESP V1.2 SchematicsDocument1 pageAutosteer ESP V1.2 SchematicsŽivoin Bogdanov100% (1)

- Nec Ir For PicDocument14 pagesNec Ir For Picsudhakar5472100% (1)

- CB2 1516 CEP0365 OACircuits PDFDocument2 pagesCB2 1516 CEP0365 OACircuits PDFAgila Panneerselvam100% (1)

- Power supply and RF module control circuitDocument1 pagePower supply and RF module control circuitalo 247100% (1)

- 4.6.2 Universal Serial Bus (USB)Document18 pages4.6.2 Universal Serial Bus (USB)kollavivek_534195858100% (2)

- Picpgm Usb v1.0Document1 pagePicpgm Usb v1.0Yudi Ananta Rangkuti100% (1)

- 8086 PPTDocument30 pages8086 PPTKavitha Subramaniam100% (1)

- PIR1 01 circuit diagram analysisDocument3 pagesPIR1 01 circuit diagram analysismohammadyou100% (2)

- C++ - When To Use The Brace-Enclosed Initializer - Stack OverflowDocument5 pagesC++ - When To Use The Brace-Enclosed Initializer - Stack OverflowFrankie Liu100% (1)

- Jeu D'instructions Des Microcontrôleurs PICDocument17 pagesJeu D'instructions Des Microcontrôleurs PICzabderrezzak100% (1)

- Send arbitrary Ethernet frame using libpcap in CDocument9 pagesSend arbitrary Ethernet frame using libpcap in CAl Gambardella100% (1)

- I2C Protocol in Fpga Using VHDL: Main Project Interim Report As A Partial Fullment of The CurriculumDocument18 pagesI2C Protocol in Fpga Using VHDL: Main Project Interim Report As A Partial Fullment of The CurriculumShuvra Saha100% (1)

- MSP430G2553 microcontroller circuit diagramDocument2 pagesMSP430G2553 microcontroller circuit diagramNguyễn Văn Dũng100% (1)

- Nxbyte Arm-Legv8Document15 pagesNxbyte Arm-Legv8Jonathan Manzaki100% (1)

- Komunikasi Usart (Atmega8535)Document1 pageKomunikasi Usart (Atmega8535)istiqomah100% (1)

- M CoreDocument1 pageM CoreJancso Gellert100% (1)

- Document Mini Project No 1.117Document8 pagesDocument Mini Project No 1.117rahmat100% (1)

- Pic202 Pir301 Pir302 Pir302 Pir301 Pic201 Pic202Document1 pagePic202 Pir301 Pir302 Pir302 Pir301 Pic201 Pic202indranil100% (1)

- ISIS Professional - D - PICs - Proteus - CLK - Clock - DSN PDFDocument1 pageISIS Professional - D - PICs - Proteus - CLK - Clock - DSN PDFManuel Eduardo Estrella Polanco100% (1)

- Lora G v1.3.schDocument2 pagesLora G v1.3.schamy iny100% (2)

- Rs 485Document1 pageRs 485Umair100% (1)

- DFR0535 (V1.0) SchematicDocument1 pageDFR0535 (V1.0) SchematicJanVanderstoel100% (1)

- Design Logo With ESP32Document1 pageDesign Logo With ESP32alex smuck kamus100% (1)

- Stepper SchematicDocument1 pageStepper SchematicAdriano Araujo100% (1)

- Spi and I2cDocument11 pagesSpi and I2cAbhay Tomar100% (1)

- Bascom and AVR, RS-232Document10 pagesBascom and AVR, RS-232akbar100% (1)

- Overview of The Inter-Integrated Circuit (I C) Bus: 2 ECPE 4536 Microprocessor System Design II Virginia TechDocument7 pagesOverview of The Inter-Integrated Circuit (I C) Bus: 2 ECPE 4536 Microprocessor System Design II Virginia Techdineshvhaval100% (1)

- 3.3 Times Improvement in Switching Speed in Driving ADocument3 pages3.3 Times Improvement in Switching Speed in Driving AMario GlezPNo ratings yet

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- E 905030Document4 pagesE 905030Tariq ZuhlufNo ratings yet

- Practical Neural Networks (3) : Part 3 - Feedback Nets and Competitive NetsDocument5 pagesPractical Neural Networks (3) : Part 3 - Feedback Nets and Competitive NetsTariq Zuhluf100% (2)

- Main voltage monitor provides emergency lighting under 40 charactersDocument1 pageMain voltage monitor provides emergency lighting under 40 charactersTariq Zuhluf100% (2)

- Design Ideas: Keyboard CircuitDocument2 pagesDesign Ideas: Keyboard CircuitTariq Zuhluf100% (3)

- Ensors FOR Humans: Sensor Technology at MITDocument4 pagesEnsors FOR Humans: Sensor Technology at MITTariq ZuhlufNo ratings yet

- E 05 B 040Document7 pagesE 05 B 040Tariq Zuhluf100% (2)

- Slave Mains On-Off Control: Amplificationj Attenuation SelectorDocument3 pagesSlave Mains On-Off Control: Amplificationj Attenuation SelectorTariq Zuhluf100% (2)

- E 01 C 093Document5 pagesE 01 C 093Tariq ZuhlufNo ratings yet

- REMOTE CONTROL CIRCUIT BY MOBILE PHONEDocument4 pagesREMOTE CONTROL CIRCUIT BY MOBILE PHONETariq Zuhluf100% (2)

- E 055077Document1 pageE 055077Tariq ZuhlufNo ratings yet

- E 037028Document1 pageE 037028Tariq Zuhluf100% (2)

- Seven-Eleven: Ir NVDocument3 pagesSeven-Eleven: Ir NVTariq Zuhluf100% (2)

- Universal Power-On Delay: by J. RuffellDocument1 pageUniversal Power-On Delay: by J. RuffellTariq Zuhluf100% (2)

- Noise of The The V /115.: R.rn.sDocument1 pageNoise of The The V /115.: R.rn.sTariq Zuhluf100% (1)

- In Questof A PangramDocument5 pagesIn Questof A PangramTariq Zuhluf100% (1)

- E 02 CH 04Document1 pageE 02 CH 04Tariq Zuhluf100% (2)

- Current Probe: Parts ListDocument1 pageCurrent Probe: Parts ListTariq Zuhluf100% (2)

- PC Interface For The CAN Bus: With New SoftwareDocument5 pagesPC Interface For The CAN Bus: With New SoftwareTariq Zuhluf100% (2)

- Digital Bechtop Power Supply (2) : Part 2: Soldering, Sawing and DrillingDocument5 pagesDigital Bechtop Power Supply (2) : Part 2: Soldering, Sawing and DrillingTariq ZuhlufNo ratings yet

- Token Number Display: Small CircuitscollectionDocument1 pageToken Number Display: Small CircuitscollectionTariq Zuhluf100% (2)

- E 02 CH 43Document1 pageE 02 CH 43Tariq Zuhluf100% (2)

- E051042 PDFDocument2 pagesE051042 PDFTariq ZuhlufNo ratings yet

- Wireless Museum: Components ListDocument1 pageWireless Museum: Components ListTariq Zuhluf100% (1)

- Stereo Peak Indicator: Small CircuitscollectionDocument1 pageStereo Peak Indicator: Small CircuitscollectionTariq Zuhluf100% (1)

- Speed-Up For Darlingtons: Small CircuitscollectionDocument1 pageSpeed-Up For Darlingtons: Small CircuitscollectionTariq Zuhluf100% (1)

- E 986024Document1 pageE 986024Tariq Zuhluf100% (1)

- E 03 B 035Document1 pageE 03 B 035Tariq Zuhluf100% (1)

- Measuring current with three external componentsDocument4 pagesMeasuring current with three external componentsTariq Zuhluf100% (1)

- Idc To Box Header Adaptor: ReferenceDocument2 pagesIdc To Box Header Adaptor: ReferenceTariq Zuhluf100% (1)

- Revision Notes - HardwareDocument18 pagesRevision Notes - HardwaremuhammadNo ratings yet

- Combined Deterministic-Stochastic Frequency-Domain Subspace Identification For Experimental and Operational Modal AnalysisDocument11 pagesCombined Deterministic-Stochastic Frequency-Domain Subspace Identification For Experimental and Operational Modal AnalysismasoudNo ratings yet

- U.S. Pat. 6,114,618, Plek Guitar System, 2000.Document9 pagesU.S. Pat. 6,114,618, Plek Guitar System, 2000.Duane BlakeNo ratings yet

- CIM Standards Overview Layers 2 and 3Document80 pagesCIM Standards Overview Layers 2 and 3AweSome, ST,MTNo ratings yet

- Class quiz answer sheet templateDocument1 pageClass quiz answer sheet templateNenbon NatividadNo ratings yet

- Business Level Strategy of GrameenphoneDocument11 pagesBusiness Level Strategy of GrameenphoneummahshafiNo ratings yet

- Experiment No.1: Design All Gates Using VHDLDocument38 pagesExperiment No.1: Design All Gates Using VHDLashutoshdabas17No ratings yet

- Jeannette Tsuei ResumeDocument1 pageJeannette Tsuei Resumeapi-282614171No ratings yet

- Tactical Buyer - SpanishDocument4 pagesTactical Buyer - SpanishCata VarticNo ratings yet

- CV of Fairuz Areefin KhanDocument2 pagesCV of Fairuz Areefin KhanAbu SaleahNo ratings yet

- nRF52832 NFC Antenna Tuning: White PaperDocument15 pagesnRF52832 NFC Antenna Tuning: White PaperCanNo ratings yet

- Datasheet - Netscout-Tap-FamilyDocument5 pagesDatasheet - Netscout-Tap-FamilyKelvin PattyNo ratings yet

- Tutorial - AlphaGo PDFDocument27 pagesTutorial - AlphaGo PDFZe Wei NgNo ratings yet

- Neuromeasure 5 User'S ManualDocument14 pagesNeuromeasure 5 User'S ManualGokulNo ratings yet

- Door Locks ServiceDocument12 pagesDoor Locks ServiceRepuesto GeneralNo ratings yet

- GD&T WikipediaDocument4 pagesGD&T WikipediaJayesh PatilNo ratings yet

- PF 320 FS 2100N 4x00DN PL UKDocument9 pagesPF 320 FS 2100N 4x00DN PL UKChad HicksNo ratings yet

- Drivers For Vostro 1450Document12 pagesDrivers For Vostro 1450cpatra77No ratings yet

- Threat Hunting With SplunkDocument122 pagesThreat Hunting With SplunkJesus MoraNo ratings yet

- Implementing Aia Osb 11g 349389Document114 pagesImplementing Aia Osb 11g 349389ptameb1No ratings yet

- 1794 FLEX I/O Analog, TC and RTD Modules Specifications: Technical DataDocument28 pages1794 FLEX I/O Analog, TC and RTD Modules Specifications: Technical DataKelly Johana Moreno MendozaNo ratings yet

- SAP EWM DeconsolidationDocument2 pagesSAP EWM DeconsolidationS BanerjeeNo ratings yet

- Mobile MarketingDocument9 pagesMobile MarketingGianiCristeaNo ratings yet

- Fractal Robots Seminar ReportDocument27 pagesFractal Robots Seminar ReportAkhil ThomasNo ratings yet

- Agency and Empowerment: A Proposal For Internationally Comparable IndicatorsDocument60 pagesAgency and Empowerment: A Proposal For Internationally Comparable IndicatorsClaudia LyNo ratings yet

- Onvif: ONVIF Specification Version 18.12 Release NotesDocument22 pagesOnvif: ONVIF Specification Version 18.12 Release NotesS M HADIUZZAMANNo ratings yet

- Unit2 Ass1 NewDocument3 pagesUnit2 Ass1 Newmaurice007No ratings yet

- Telit GL865-DUAL-QUAD Hardware User Guide r7Document76 pagesTelit GL865-DUAL-QUAD Hardware User Guide r7salasugo5751No ratings yet

- Generator Auto Start Mod Rolando Mod 8 ChokeDocument3 pagesGenerator Auto Start Mod Rolando Mod 8 Chokeali mohammedNo ratings yet

- Context Diagram DFD For (Existing) Billing SystemDocument3 pagesContext Diagram DFD For (Existing) Billing SystemDanna ClaireNo ratings yet