Professional Documents

Culture Documents

Lab H3

Uploaded by

MuhammadAtifOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab H3

Uploaded by

MuhammadAtifCopyright:

Available Formats

Introduction to DSP Kit Lab h-2

Designing a single echo effect in real time

In the previous lab, a basic I/O system for audio was built, compiled and run. This

section investigates data manipulation and representation on the DSK by

designing a single echo filter.

In this section, an echo filter is designed. An echo is a delayed, attenuated

version of the original signal. The difference equation describing a system with a

single echo is defined as

y[n] = x[n] + ax[n − D],

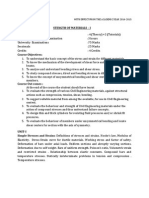

where a is the gain and D is the delay. Figure 1 shows the Simulink block

diagram that implements this filter.

1. Build and run the model in figure 1(using the Incremental Build button on the

model toolbar).

2. Add the C6711DSK target preferences block from the TI C6000 Target

Preferences block library. This block is not connected to any other block in the

model.

3. Test the model using the microphone (Mic In) and a pair of headphones

(Headphone).

4. Change the delay and gain by double clicking on the desired block and explore

the effect of each on the output signal.

Line In

C6711 DSK Z-40 C6711 DSK

ADC DAC

Figure 1: Real time single echo filter

Introduction to DSP Kit Lab h-2

Real time audio reverberation model

In this section a model that simulates audio reverberation is created and built.

Reverberation is the result of an infinite number of echoes added together, and

can be represented mathematically as

y[n] = x[n]+ax[n−D]−bx[n−D],

where a and b are the gains and D is the delay.

For this experiment, a microphone is connected to the Mic In connector on the

C6711 DSK and speakers (and an oscilloscope) connected to the Line Out

connector on the C6711 DSK. To test the model, speak into the microphone and

listen to the output from the speakers.

1. Open Simulink.

2. Create a new model by selecting File > New > Model from the Simulink

menu bar.

3. Use Simulink blocks to create the model shown in figure 2.

4. The Integer Delay block is in Discrete library of the Simulink blockset.

The Gain block is in the Commonly Used library of the simulink blockset.

The Line In and Line Out block for the C6711 DSK are in the C6711

Board Support library of the Embedded Target for TIC6000 blockset.

5. From the TI C6000 Target Preferences block library, add the C6711DSK

target preferences block. This block is not connected to any other block

in the model.

6. Click the C6711 DSK ADC block to select it. Select Block Parameters

from the Simulink Edit menu. Set the following parameters for the block:

• Select the +20 dB mic gain boost check box

• For Output data type, select Double from the list

• Set Scaling to Normalize

• Set Source gain to 0.0

• Enter 64 for Samples per frame

7. For ADC source, select Mic In.

8. Click OK to close the Block Parameters: ADC dialog.

9. Now set the options for the C6711 DSK DAC block.

• Set Scaling to Normalize

• For DAC attenuation, enter 0.0

• Set Overflow mode to Saturate.

10. Click OK to close the dialog.

Introduction to DSP Kit Lab h-2

11. Open the Configuration Parameters dialog, select Solver on the Select tree,

and set the appropriate options on the Solver pane for your model and for the

target.

• Under Solver options, select the fixed-step and discrete settings from the lists.

• Set the Fixed step size to auto and select Single Tasking for the Tasking mode.

12. Build and run the model (using the Incremental Build button on the model

toolbar).

13. Speak into the microphone connected to the board. The model should

generate a reverberation effect out of the speakers, delaying and echoing the

words you speak into the mic.

Audio Reverberation C6711 DSK Implementation

C6711 DSK

Line In DAC

C6711 DSK Z-20

ADC

Reset

C6711 DSK

Figure 2: Real time reverberation filter

Introduction to DSP Kit Lab h-2

Real time audio flange model

A flange effect is a (time domain) audio effect, which is achieved by combining to

identical signal with each other, with one signal delayed by a gradually changing

amount. The difference equation for the flange effect is given by,

y[n] = x[n] + ax[n − d(n)],

where the time varying delay is given by,

d(n) = D + D2 (1 −sin( 2_fdnfs))

where D is a fixed delay, fd is the flanging frequency, and fs is the sampling rate.

Figure 3 shows the Simulink block diagram that implements this system.

1. Build and run the model in figure 3 (using the Incremental Build button on the

model toolbar).

2. Add the C6711DSK target preferences block from the TI C6000 Target

Preferences block library. This block is not connected to any other block in the

model.

3. Test the system using recorded music or speech played through the Line In

connector of the DSK and a pair of headphones connected to the Headphone

connector.

Line In

C6711 DSK C6711 DSK

ADC DAC

Reset

C6711 DSK

Figure 3: Real time flange filter

Task:

Write a brief report (2 to 3 pages) about what do you learn, observe and

understand from this lab.

You might also like

- CQU Elicos Application FormDocument4 pagesCQU Elicos Application FormMuhammadAtifNo ratings yet

- Charles Darwin MelbourneDocument45 pagesCharles Darwin MelbourneMuhammadAtifNo ratings yet

- Dual Channel Optocoupler IL74Document5 pagesDual Channel Optocoupler IL74MuhammadAtifNo ratings yet

- v23 5Document6 pagesv23 5MuhammadAtifNo ratings yet

- GRE PatternDocument1 pageGRE PatternMuhammadAtifNo ratings yet

- Subject: Digital Signal Processing (TE321) Test # 2: - Sec 1mDocument1 pageSubject: Digital Signal Processing (TE321) Test # 2: - Sec 1mMuhammadAtifNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Earthquake Geotechnical Engineering PDFDocument339 pagesEarthquake Geotechnical Engineering PDFLj JeanNo ratings yet

- Detailed Lesson Plan About Normal DistributionDocument11 pagesDetailed Lesson Plan About Normal DistributionMai LaNo ratings yet

- Analyzing River Discharge DataDocument26 pagesAnalyzing River Discharge DataMiera SaidNo ratings yet

- Precalculus Prerequisites A.K.A. Chapter 0' Creative Commons Attribution-Noncommercial-Sharealike 3.0 LicenseDocument16 pagesPrecalculus Prerequisites A.K.A. Chapter 0' Creative Commons Attribution-Noncommercial-Sharealike 3.0 LicensejakeNo ratings yet

- Problem Description: Problem 1: Deflection of A BeamDocument22 pagesProblem Description: Problem 1: Deflection of A BeamCerita dan BeritaNo ratings yet

- ASC Sublord/MOON Starlord Connection - A Revised StudyDocument3 pagesASC Sublord/MOON Starlord Connection - A Revised StudyMadhavaKrishnaNo ratings yet

- PE20M002 Seismic MigrationDocument18 pagesPE20M002 Seismic MigrationNAGENDR_006No ratings yet

- PEC Presentation LSA 2022Document35 pagesPEC Presentation LSA 2022Wahaaj AhmadNo ratings yet

- Cbot-Unit 1-LPPDocument23 pagesCbot-Unit 1-LPPJaya SuryaNo ratings yet

- Theory in GrammarDocument47 pagesTheory in GrammarJulia CareyNo ratings yet

- Engineering Mathematics For Gate Chapter1Document1 pageEngineering Mathematics For Gate Chapter1Sai VeerendraNo ratings yet

- MiniTest 230304Document2 pagesMiniTest 230304Osama MaherNo ratings yet

- CE214Document2 pagesCE214Mujammil ChoudhariNo ratings yet

- CBSE - PHYSICS - Mensuration DPPDocument6 pagesCBSE - PHYSICS - Mensuration DPPAncha RambabuNo ratings yet

- 209 - 2017 Regulation SyllabusDocument107 pages209 - 2017 Regulation SyllabussivakumarNo ratings yet

- Subjective Sm015 PelajarDocument23 pagesSubjective Sm015 PelajarWAN NUR ALEEYA TASNIM BINTI WAN MOHAMED HAZMAN MoeNo ratings yet

- 04 - 05 SequencesDocument12 pages04 - 05 SequencesHaidee VenturilloNo ratings yet

- bài tập 8Document3 pagesbài tập 8Đức MạnhNo ratings yet

- Machine Learning: An Introduction to Predicting the Future from Past ExperienceDocument65 pagesMachine Learning: An Introduction to Predicting the Future from Past ExperienceAnilNo ratings yet

- Specimen MADocument20 pagesSpecimen MAYousif OmerNo ratings yet

- FIR FilterDocument32 pagesFIR FilterWan TingNo ratings yet

- Remarksonmulti FidelitysurrogatesDocument23 pagesRemarksonmulti FidelitysurrogateskkaytugNo ratings yet

- Examen Soa PDFDocument49 pagesExamen Soa PDFAnonymous Nu2bPH3No ratings yet

- Alpha Beta Pruning Lecture-23: Hema KashyapDocument42 pagesAlpha Beta Pruning Lecture-23: Hema KashyapAKSHITA MISHRANo ratings yet

- Biomechanics of HipDocument6 pagesBiomechanics of HipChristina SuppiahNo ratings yet

- Scientific Poster Ballistic Pendulum FinalDocument3 pagesScientific Poster Ballistic Pendulum Finalapi-256048216No ratings yet

- New Microsoft Office Word Document PDFDocument5 pagesNew Microsoft Office Word Document PDFSubhash KNo ratings yet

- A Critique of The Crank Nicolson Scheme Strengths and Weaknesses For Financial Instrument PricingDocument9 pagesA Critique of The Crank Nicolson Scheme Strengths and Weaknesses For Financial Instrument PricingChris SimpsonNo ratings yet

- 19ce159 C++Document23 pages19ce159 C++kalpana yadavNo ratings yet

- Production: - Microeconomics - Pindyck/Rubinfeld, 7eDocument24 pagesProduction: - Microeconomics - Pindyck/Rubinfeld, 7eanon_946247999No ratings yet