Professional Documents

Culture Documents

Teaching Plan: RGM College of Engineering & Technology, Nandyal-518 501

Uploaded by

Tara GonzalesOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Teaching Plan: RGM College of Engineering & Technology, Nandyal-518 501

Uploaded by

Tara GonzalesCopyright:

Available Formats

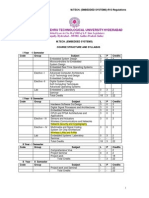

RGM COLLEGE OF ENGINEERING & TECHNOLOGY, NANDYAL-518 501.

AUTONOMOUS

RGMCET/ECE/HR/F-03

ACADEMIC YEAR: 2010-11 TEACHING PLAN RGMCET/ECE/TP/F-01

NAME OF THE FACULTY: Mr.M.Chennakesavulu

SUBJECT: EMBEDDED SYSTEM CONCEPTS

Branch & Year: M.Tech, I-Sem ES Total Hours: 49 Hours

Estimated

S.No Unit Topics to be covered

Periods

INTRODUCTION: Embedded system overview, embedded hardware units, embedded

1 I software in a system, embedded system on chip (SOC), design process, classification of 7

embedded systems.

EMBEDDED COMPUTING PLATFORM: CPU Bus, memory devices, component

2 II interfacing, networks for embedded systems, communication interfacings: RS232/UART, 7

RS422/RS485, IEEE 488 bus.

SURVEY OF SOFTWARE ARCHITECTURE: Round robin, round robin with interrupts,

3 III 6

function queue scheduling architecture, selecting an architecture saving memory space.

EMBEDDED SOFTWARE DEVELOPMENT TOOLS: Host and target machines, linkers,

4 IV locations for embedded software, getting embedded software into target system, 6

debugging technique.

RTOS CONCEPTS: Architecture of the kernel, interrupt service routines, semaphores,

5 V 6

message queues, pipes.

6 VI INSTRUCTION SETS: Introduction, preliminaries, ARM processor, SHARC processor. 5

SYSTEM DESIGN TECHNIQUES: Design methodologies, requirement analysis,

7 VII 5

specifications, system analysis and architecture design.

DESIGN EXAMPLES: Telephone PBX, ink jet printer, water tank monitoring system,

8 VIII 7

GPRS, Personal Digital Assistants, Set Top boxes.

FACULTY HOD PRINCIPAL

RGM COLLEGE OF ENGINEERING & TECHNOLOGY, NANDYAL-518 501.

AUTONOMOUS

RGMCET/ECE/HR/F-03

ACADEMIC YEAR: 2010-11 TEACHING PLAN RGMCET/ECE/TP/F-01

NAME OF THE FACULTY: Mr.C.Venkataiah

SUBJECT: ADVANCED COMPUTER ARCHITECTURE

Branch & Year: M.Tech, I-Sem ES Total Hours: 49 Hours

Estimated

S.No Unit Topics to be covered

Periods

FUNDAMENTALS OF COMPUTER DESIGN: Technology trends, cost- measuring

1 I 6

and reporting performance quantitative principles of computer design.

INSTRUCTION SET PRINCIPLES AND EXAMPLES: classifying instruction set,

memory addressing, type and size of operands, addressing modes for signal

2 II 7

processing, operations in the instruction set- instructions for control flow- encoding

an instruction set.-the role of compiler.

INSTRUCTION LEVEL PARALLELISM (ILP): overcoming data hazards, reducing

3 III branch costs, high performance instruction delivery, hardware based speculation, 7

limitation of ILP.

ILP SOFTWARE APPROACH: Compiler Techniques, Static Branch Protection, VLIW

4 IV 6

Approach, H.W support for more ILP at compile time- H.W verses S.W solutions.

MEMORY HIERARCHY DESIGN: cache performance, reducing cache misses

5 V 6

penalty and miss rate, virtual memory, protection and examples of VM

MULTIPROCESSORS AND THREAD LEVEL PARALLELISM: symmetric shared

6 VI 6

memory architectures, distributed shared memory, Synchronization, multi threading.

STORAGE SYSTEMS: Types, Buses, RAID, errors and failures, bench marking a storage

7 VII 6

device, designing a I/O system

INTER CONNECTION NETWORKS AND CLUSTERS: Interconnection network media,

8 VIII 5

practical issues in interconnecting networks, examples, clusters, designing a cluster.

FACULTY HOD PRINCIPAL

RGM COLLEGE OF ENGINEERING & TECHNOLOGY, NANDYAL-518 501.

AUTONOMOUS

RGMCET/ECE/HR/F-03

ACADEMIC YEAR: 2010-11 TEACHING PLAN RGMCET/ECE/TP/F-01

NAME OF THE FACULTY: Mr.D.Raghunatha Rao

SUBJECT: ADVANCED DSP & APPLICATIONS

Branch & Year: M.Tech, I-Sem ES Total Hours: 54 Hours

Estimated

S.No Unit Topics to be covered

Periods

LTI DISCRETE-TIME SYSTEMS IN THE TRANSFORM DOMAIN: Types of Linear-

1 I Phase transfer functions, Complementary Transfer Functions, Inverse Systems, System 8

identification, Digital Two-Pairs.

DIGITAL FILTER STRUCTURE AND DESIGN: All pass filters, Tunable IIR Digital

2 II filter, IIR & FIR tapped Cascaded Lattice Structures, Parallel All pass realization of IIR 8

Transfer Functions, Digital Sine-Cosine generator

Computational Complexity of Digital filter Structures, Design of IIR filter using pade’

3 III approximation, Least square design methods, Design of computationally efficient FIR 4

filters.

DSP ALGORITHMS: FFT, Sliding Discrete Fourier transform, DFT Computation

4 IV Over a narrow Frequency Band, Split Radix FFT, Linear filtering approach to Computation 6

of DFT using Chirp Z-Transform.

ANALYSIS OF FINITE WORD LENGTH EFFECTS: The Quantization Process and

5 V errors, Quantization of fixed-point Numbers, Analysis of Coefficient quantization effects, 8

A/D conversion Noise Analysis, Analysis of Arithmetic Round of errors.

ADAPTIVE FILTERS

FIR adaptive filters – Adaptive filter based on steepest descent method – Widrow-Hoff

6 VI LMS adaptive algorithms, normalized LMS. Adaptive channel equalization – adaptive echo 8

cancellation – Adaptive noise cancellation – Adaptive recursive (IIR) filters. RLS adaptive

filters – Exponentially weighted RLS – Sliding window RLS.

APPLICATIONS OF DIGITAL SIGNAL PROCESSING: Dual Tone Multi-frequency

Signal Detection, Spectral Analysis of Sinusoidal Signals, Spectral Analysis of

7 VII 8

Nonstationary Signals, Musical Sound Processing, Over Sampling A/D Converter, Over

Sampling D/A Converter.

Applications, architecture, Addressing modes, instruction set of TMS 320 C54XX

8 VIII 4

Processors , simple programmes.

FACULTY HOD PRINCIPAL

RGM COLLEGE OF ENGINEERING & TECHNOLOGY, NANDYAL-518 501.

AUTONOMOUS

RGMCET/ECE/HR/F-03

ACADEMIC YEAR: 2010-11 TEACHING PLAN RGMCET/ECE/TP/F-01

NAME OF THE FACULTY: Mr.N.Ramanjaneyulu

SUBJECT: MICROCONTROLLERS & INTERFACING

Branch & Year: M.Tech, I-Sem ES Total Hours: 56 Hours

Estimated

S.No Unit Topics to be covered

Periods

INTEL 8051: Architecture of 8051, Memory Organization, Register banks, Bit addressing

1 I 10

media, SFR area, addressing modes, Instruction set, Programming examples.

8051 Interrupt structure, Timer modules, Serial Features, Port structure, Power saving

2 II 6

modes.

MOTOROLA 68HC11: Controllers features, Different modes of operation and memory

3 III map, Functions of I/O ports in single chip and expanded multiplexed mode, Timer 6

system.

Input capture, Output compare and pulsed accumulator features of 68HC11, Serial

4 IV 6

peripherals, Serial Communication interface, Analog to digital conversion features.

PIC MICROCONTROLLERS: Program memory, CPU registers, Register file structure,

5 V Block diagram of PIC 16C74, I/O ports. Timer 0,1 and 2 features, Interrupt logic, serial 8

peripheral interface, I2C bus, ADC, UART, PIC family parts.

MICROCONTROLLER INTERFACING: 8051, 68HC11, PIC-16C6X and External

Memory Interfacing – Memory Management Unit, Instruction and data cache, memory

6 VI 8

controller. On Chip Counters, Timers, Serial I/O, Interrupts and their use. PWM, Watch

dog, ISP, IAP features.

INTERRUPT SYNCHRONIZATION: Interrupt vectors & priority, external interrupt

7 VII design. Serial I/O DevicesRS232 Specifications, RS422/Apple Talk/ RS 423/RS435 & other 8

communication protocols. Serial Communication Controller

CASE STUDIES: Design of Embedded Systems using the micro controller 8051, 68HC11,

8 VIII PIC-16C6X for applications in the area of Communications, Automotives, industrial 4

control.

FACULTY HOD PRINCIPAL

RGM COLLEGE OF ENGINEERING & TECHNOLOGY, NANDYAL-518 501.

AUTONOMOUS

RGMCET/ECE/HR/F-03

ACADEMIC YEAR: 2010-11 TEACHING PLAN RGMCET/ECE/TP/F-01

NAME OF THE FACULTY: Mr.G.Kishore Kumar

SUBJECT: OPERATING SYSTEMS

Branch & Year: M.Tech, I-Sem ES Total Hours: 49 Hours

Estimated

S.No Unit Topics to be covered

Periods

INTRODUCTION: Operating system definition, Objective and functions, types, different

1 I parts, Structure of operating system, trends- parallel computing, distributed computing; 5

Open systems, Hardware, software, firmware.

PROCESS SCHEDULING: Definition of a process; process states, transitions, process

control, suspend and process, interrupt processing, nucleus of an operating system;

2 II 10

parallel processing; Mutual exclusion, Critical Section; Solution of mutual exclusion;

Semaphores; Deadlock- occurrence, prevention, detection and recovery

STORAGE MANAGEMENT: Storage organization, management strategies, hierarchy;

3 III 5

virtual storage, paging, segmentation

FILE SYSTEM MANAGEMENT: File system (function of a file system)- data hierarchy,

4 IV blocking and buffering, file organization, queued and basic access methods, backup and 5

recovery

I/O MANAGEMENT: (functions of I/O management subsystem), Distributed computing-

5 V 6

OSI view, OSI network management, MAP, TOP, GOSIP, TCP/IP

OS SECURITY: Requirements, external security, operational security, surveillance,

6 VI 6

threat monitoring; Introduction to Cryptography

CASE STUDIES: UNIX- Shell, Kernel, File System, Process Management, Memory

7 VII 6

Management, I/O System, Distributed UNIX

CASE STUDIES: Example of operating system-MS-DOS, Windows, OS/2, Apple

8 VIII 6

Macintosh & Linux

FACULTY HOD PRINCIPAL

RGM COLLEGE OF ENGINEERING & TECHNOLOGY, NANDYAL-518 501.

AUTONOMOUS

RGMCET/ECE/HR/F-03

ACADEMIC YEAR: 2010-11 TEACHING PLAN RGMCET/ECE/TP/F-01

NAME OF THE FACULTY: Mr.A.Sathish

SUBJECT: VLSI TECHNOLOGY

Branch & Year: M.Tech, I-Sem ES Total Hours: 50 Hours

Estimated

S.No Unit Topics to be covered

Periods

INTRODUCTION TO MOS TECHNOLOGY: Overview of VLSI Design Methodologies,

1 I VLSI Design flow, Styles of VLSI Design, CAD Technology, MOS Transistors and its 5

Trends.

BASIC ELECTRICAL PROPERTIES OF MOS: Ids-Vds Relationships, Threshold voltage

2 II 6

Vt, gm, gds and Wo, Pass Transistor, MOS Zpu/Zpd, MOS Transistor circuit model.

CMOS Design: CMOS Logic, CMOS Gate Design, Transmission Gate Logic Design, Bi-

3 III 6

CMOS Inverters, Latch-up in CMOS circuits.

LAYOUT DESIGN AND TOOLS: Transistor structures, Wires and Vias, Scalable Design

4 IV 7

rules, Layout Design tools.

LOGIC GATES & LAYOUTS: Static Complementary Gates, Switch Logic, Alternative

5 V 7

Gate Circuits, Low Power Gates, Resistive and Inductive Interconnect Delays.

COMBINATIONAL LOGIC NETWORKS: Layouts, Simulation, Network Delay,

6 VI Interconnect Design, Power Optimization, Switch Logic Networks, Gate and Network 6

Testing.

SEQUENTIAL SYSTEMS: Memory Cells and Arrays, Clocking Disciplines, Design, Power

7 VII 7

Optimization, Design Validation and Testing.

FLOOR PLANNING & ARCHITECTURE DESIGN: Floor Planning Methods, Off-Chip

8 VIII Connections, High level Synthesis, Architecture for Low Power, SOCs and Embedded CPU 6

Architecture Testing.

FACULTY HOD PRINCIPAL

You might also like

- Teaching Plan: RGM College of Engineering & Technology, Nandyal-518 501Document6 pagesTeaching Plan: RGM College of Engineering & Technology, Nandyal-518 501Tara GonzalesNo ratings yet

- Software Engineering for Embedded Systems: Methods, Practical Techniques, and ApplicationsFrom EverandSoftware Engineering for Embedded Systems: Methods, Practical Techniques, and ApplicationsRating: 2.5 out of 5 stars2.5/5 (2)

- JNTU Anantapur M.tech Syllabus For Embedded Systems 2009 10Document19 pagesJNTU Anantapur M.tech Syllabus For Embedded Systems 2009 10RajeshNo ratings yet

- Embedded Systems Design with Platform FPGAs: Principles and PracticesFrom EverandEmbedded Systems Design with Platform FPGAs: Principles and PracticesRating: 5 out of 5 stars5/5 (1)

- C CC C CC C CCCCCCC ! "! #C#CC C$$C%$$%C %&C' ( + (C C CCCC C CDocument24 pagesC CC C CC C CCCCCCC ! "! #C#CC C$$C%$$%C %&C' ( + (C C CCCC C CSyed AshmadNo ratings yet

- Pipelined Processor Farms: Structured Design for Embedded Parallel SystemsFrom EverandPipelined Processor Farms: Structured Design for Embedded Parallel SystemsNo ratings yet

- Design Embedded SystemsDocument2 pagesDesign Embedded SystemsvinothNo ratings yet

- Microcontroller Architecture and Organization: Unit IDocument6 pagesMicrocontroller Architecture and Organization: Unit IhemanthdreamzNo ratings yet

- High-Performance Embedded Computing: Applications in Cyber-Physical Systems and Mobile ComputingFrom EverandHigh-Performance Embedded Computing: Applications in Cyber-Physical Systems and Mobile ComputingNo ratings yet

- VLSI, VLSI System & VLSI System DesignDocument26 pagesVLSI, VLSI System & VLSI System Designrohit_sreerama4040No ratings yet

- Embedded Deep Learning: Algorithms, Architectures and Circuits for Always-on Neural Network ProcessingFrom EverandEmbedded Deep Learning: Algorithms, Architectures and Circuits for Always-on Neural Network ProcessingNo ratings yet

- Chapter 1 Introduction To Computing NewDocument41 pagesChapter 1 Introduction To Computing NewSama A ShurrabNo ratings yet

- Open-Source Robotics and Process Control Cookbook: Designing and Building Robust, Dependable Real-time SystemsFrom EverandOpen-Source Robotics and Process Control Cookbook: Designing and Building Robust, Dependable Real-time SystemsRating: 3 out of 5 stars3/5 (1)

- Ee8691 - Syllabus - Embedded System - R2017Document2 pagesEe8691 - Syllabus - Embedded System - R2017AishwaryaNo ratings yet

- Embedded System (9168)Document5 pagesEmbedded System (9168)Victoria FrancoNo ratings yet

- Computer-Aided Design TechniquesFrom EverandComputer-Aided Design TechniquesE. WolfendaleNo ratings yet

- ME VLSI & EmdDocument58 pagesME VLSI & EmdAnil V. WalkeNo ratings yet

- Advance Computer Architecture Fundamentals and TrendsDocument69 pagesAdvance Computer Architecture Fundamentals and TrendsAnees Ahmed ANNo ratings yet

- Computer Organization DFDocument3 pagesComputer Organization DFIMRAN PATELNo ratings yet

- White Papers On Ieee 802.19Document33 pagesWhite Papers On Ieee 802.19JAUNITHANo ratings yet

- Embedded Systems Design ProcessDocument20 pagesEmbedded Systems Design ProcessVIGNESH L RNo ratings yet

- Cse Viii Advanced Computer Architectures 06CS81 Notes PDFDocument156 pagesCse Viii Advanced Computer Architectures 06CS81 Notes PDFHarshith HarshiNo ratings yet

- Embedded and Realtime Operating SystemsDocument2 pagesEmbedded and Realtime Operating SystemsRensiNo ratings yet

- CSE322 SyllabusDocument2 pagesCSE322 SyllabusAakashRajNo ratings yet

- Data Structures and Algorithms SyllabusDocument64 pagesData Structures and Algorithms SyllabusMarimuthu MuthaiyanNo ratings yet

- EMBEDDED SYSTEM DESIGN-IDocument2 pagesEMBEDDED SYSTEM DESIGN-IMaha Lakshmi ShankarNo ratings yet

- Vlsi System DesignDocument12 pagesVlsi System DesignMahender GoudNo ratings yet

- 11L504 EMBEDDED SYSTEMS SyllabusDocument2 pages11L504 EMBEDDED SYSTEMS SyllabusveerakumarsNo ratings yet

- Vlsi DesignDocument12 pagesVlsi DesignTanveer AhmedNo ratings yet

- ARM Processor Embedded Systems DesignDocument6 pagesARM Processor Embedded Systems Designjayarajan0% (1)

- Course Plan EsdDocument3 pagesCourse Plan Esdsaravanaeee2004No ratings yet

- NPTEL Microprocessor SyllabusDocument2 pagesNPTEL Microprocessor SyllabusNidhi MishraNo ratings yet

- Dpco Unit-1 NotesDocument52 pagesDpco Unit-1 NotesSyed Z100% (1)

- Es IiDocument16 pagesEs IiSivasankar YalavarthyNo ratings yet

- SECA1606Document1 pageSECA1606S NitheshNo ratings yet

- Cse-Vii-Advanced Computer Architectures Notes PDFDocument156 pagesCse-Vii-Advanced Computer Architectures Notes PDFTanay BalrajNo ratings yet

- (1964) Architecture of The IBM System360Document15 pages(1964) Architecture of The IBM System360Davi FernandesNo ratings yet

- Embedded Syllabus 2013Document23 pagesEmbedded Syllabus 2013Mohammad SalmanNo ratings yet

- ES Syllabus ECE PDFDocument12 pagesES Syllabus ECE PDFramanaidu1No ratings yet

- Vlsi Mtech Jntu Kakinada II Sem SyllabusDocument16 pagesVlsi Mtech Jntu Kakinada II Sem Syllabusrv prasad50% (2)

- Rajeev Gandhi Memorial College of Engineering & Technology Rajeev Gandhi Memorial College of Engineering & TechnologyDocument5 pagesRajeev Gandhi Memorial College of Engineering & Technology Rajeev Gandhi Memorial College of Engineering & Technologyknk761987No ratings yet

- Microprocessor and Microcontroller FundamentalsDocument6 pagesMicroprocessor and Microcontroller Fundamentalsgoons7777No ratings yet

- Me SyllabusDocument3 pagesMe SyllabusPrabhu SubramaniamNo ratings yet

- B.E. ECE FinalDocument45 pagesB.E. ECE FinalKesav RameshKumarNo ratings yet

- Resume Arvind ShrivastavaDocument2 pagesResume Arvind ShrivastavaArvind ShrivastavaNo ratings yet

- Embedded System DesignDocument2 pagesEmbedded System DesignChethan DbNo ratings yet

- CSE2006 Microprocessor and InterfacingDocument10 pagesCSE2006 Microprocessor and InterfacingAyyeeeeNo ratings yet

- EI 6702-Logic and Distributed Control SystemDocument2 pagesEI 6702-Logic and Distributed Control SystemMnskSaro50% (2)

- Jawaharlal Nehru Technological University Hyderabad M.Tech. Degree COURSE STRUCTURE in Vlsi I YEAR - I Semester Code Group Subject L P CreditsDocument12 pagesJawaharlal Nehru Technological University Hyderabad M.Tech. Degree COURSE STRUCTURE in Vlsi I YEAR - I Semester Code Group Subject L P Creditsshaker423No ratings yet

- Microcontrollers 4 Sem ECE NotesDocument19 pagesMicrocontrollers 4 Sem ECE NotesVigneshwar DhamodharanNo ratings yet

- Gujarat Technological UniversityDocument4 pagesGujarat Technological UniversityArunmetha SundaramoorthyNo ratings yet

- IBM360-Amdahl April64Document15 pagesIBM360-Amdahl April64THIAGO LIMANo ratings yet

- 6th Sem SyllabusDocument11 pages6th Sem SyllabusRahul SheikhNo ratings yet

- Rajiv Gandhi Proudyogiki Vishwavidyalaya, Bhopal Diploma in Computer Science & EngineeringDocument31 pagesRajiv Gandhi Proudyogiki Vishwavidyalaya, Bhopal Diploma in Computer Science & Engineeringshreyash vishwakarmaNo ratings yet

- C3351 CopoDocument2 pagesC3351 CopoAmarkavi Balu supper childNo ratings yet

- Embedded - Systems - II SemDocument24 pagesEmbedded - Systems - II SemravinarsingojuNo ratings yet

- Embedded System DesignDocument2 pagesEmbedded System DesignspveceNo ratings yet

- Professional Chapter Kit 2014 PDFDocument13 pagesProfessional Chapter Kit 2014 PDFTara GonzalesNo ratings yet

- Ic Technology CourseDocument2 pagesIc Technology CourseTara GonzalesNo ratings yet

- Iot Based Interactive Smart Refrigerator: December 2017Document8 pagesIot Based Interactive Smart Refrigerator: December 2017Tara GonzalesNo ratings yet

- Research GuidelinesDocument2 pagesResearch GuidelinesTara GonzalesNo ratings yet

- Centre of Excellence in Disaster Management: JNTUH College of Engineering Kukatpally, Hyderabad, Andhra PradeshDocument60 pagesCentre of Excellence in Disaster Management: JNTUH College of Engineering Kukatpally, Hyderabad, Andhra PradeshTara GonzalesNo ratings yet

- Introduction to IoT FundamentalsDocument1 pageIntroduction to IoT FundamentalsBala KumarNo ratings yet

- 2313 25-MAR-2019 12:54AM 45439868: Word Count Time Submitted Paper IdDocument10 pages2313 25-MAR-2019 12:54AM 45439868: Word Count Time Submitted Paper IdTara GonzalesNo ratings yet

- Introduction to IoT FundamentalsDocument1 pageIntroduction to IoT FundamentalsBala KumarNo ratings yet

- 3 DipoleDocument45 pages3 DipoleMiguel SanchezNo ratings yet

- 33IEC Call For Papers PDFDocument7 pages33IEC Call For Papers PDFvamsiNo ratings yet

- El Shay Al Smart Gis CourseDocument33 pagesEl Shay Al Smart Gis CourseTara GonzalesNo ratings yet

- Predicting The Features Affecting The Helpfulness of Online Customer ReviewsDocument22 pagesPredicting The Features Affecting The Helpfulness of Online Customer ReviewsTara GonzalesNo ratings yet

- Understanding Covariance of Random VariablesDocument14 pagesUnderstanding Covariance of Random VariablesTara GonzalesNo ratings yet

- Amity School of Engineering and Technology, KolkataDocument2 pagesAmity School of Engineering and Technology, KolkataTara GonzalesNo ratings yet

- Secondorderresponse Calculation PDFDocument5 pagesSecondorderresponse Calculation PDFTara GonzalesNo ratings yet

- 1.isca Irjes 2014 019Document5 pages1.isca Irjes 2014 019Tara GonzalesNo ratings yet

- 09 Heike Online How To Write Research Proposal OctoberDocument6 pages09 Heike Online How To Write Research Proposal Octoberrazta35No ratings yet

- Site Response Analysis (SRA) : A Practical Comparison Among Different Dimensional ApproachesDocument8 pagesSite Response Analysis (SRA) : A Practical Comparison Among Different Dimensional ApproachesTara GonzalesNo ratings yet

- Alumni Meet: S.No Regd - No Name of The Student Working Where As Designation Per Annam E.mail Cell NoDocument1 pageAlumni Meet: S.No Regd - No Name of The Student Working Where As Designation Per Annam E.mail Cell NoTara GonzalesNo ratings yet

- India ReportDocument9 pagesIndia ReportTara GonzalesNo ratings yet

- Frequency Ratio Model For Groundwater Potential Mapping and Its Sustainable Management in Cold Desert, IndiaDocument16 pagesFrequency Ratio Model For Groundwater Potential Mapping and Its Sustainable Management in Cold Desert, IndiaTara GonzalesNo ratings yet

- Perfectionism and Stuttering Rio SummaryDocument3 pagesPerfectionism and Stuttering Rio SummaryTara GonzalesNo ratings yet

- Web of Science BrochureDocument8 pagesWeb of Science BrochureTara GonzalesNo ratings yet

- 121 How To Build A TM ClubDocument38 pages121 How To Build A TM ClubHemanshuNo ratings yet

- NCIRDocument3 pagesNCIRTara GonzalesNo ratings yet

- Colored Petri Net Used To Model Flexible Manufacturing Cell 0Document6 pagesColored Petri Net Used To Model Flexible Manufacturing Cell 0Tara GonzalesNo ratings yet

- Twidosuite Manual For TWIDO PLCDocument752 pagesTwidosuite Manual For TWIDO PLCArif AliNo ratings yet

- Romania Risk PerceptionDocument12 pagesRomania Risk PerceptionTara GonzalesNo ratings yet

- Sampling PlanDocument11 pagesSampling PlanARIFNo ratings yet

- Authorization LetterDocument4 pagesAuthorization LetterCherry Mae CarredoNo ratings yet

- Omron Sysmac WayDocument40 pagesOmron Sysmac WayAurellioNo ratings yet

- Earn BTC Daily From Freebitco - in With Bot Script 100% Working Updated 2017Document4 pagesEarn BTC Daily From Freebitco - in With Bot Script 100% Working Updated 2017Anderson64% (22)

- Curriculum Vitae DimposDocument4 pagesCurriculum Vitae DimposLala LuluNo ratings yet

- Jura J9.3 Wiring DiagramDocument4 pagesJura J9.3 Wiring DiagramGrom NeposedaNo ratings yet

- Steganography Project ReportDocument40 pagesSteganography Project ReportArunangshu Sen100% (1)

- Ujian SPSS TatiDocument21 pagesUjian SPSS TatiLina NaiwaNo ratings yet

- Kerio Control Adminguide en 9.2.8 3061Document352 pagesKerio Control Adminguide en 9.2.8 3061Nushabe CeferovaNo ratings yet

- Visual C++ NET TutorialsDocument39 pagesVisual C++ NET Tutorialspgoyal10No ratings yet

- IEWB-RS Technology Labs Eigrp: Brian Dennis, CCIE # 2210 (R&S / ISP Dial / Security / Service Provider)Document51 pagesIEWB-RS Technology Labs Eigrp: Brian Dennis, CCIE # 2210 (R&S / ISP Dial / Security / Service Provider)Nandan BishtNo ratings yet

- CH 31Document58 pagesCH 31Jeffrey KankwaNo ratings yet

- WDV Dep MethodDocument24 pagesWDV Dep Methodsudershan9No ratings yet

- OJT AtTRACK - On The Job Trainee Remote Attendance Monitoring System Using Face Recognition SystemDocument6 pagesOJT AtTRACK - On The Job Trainee Remote Attendance Monitoring System Using Face Recognition SystemIOER International Multidisciplinary Research Journal ( IIMRJ)No ratings yet

- Book S Curve For Construction Sample Excel Bing PDFDocument4 pagesBook S Curve For Construction Sample Excel Bing PDFmy.nafi.pmp5283No ratings yet

- UX Case Study - Streaming App (Next TV)Document30 pagesUX Case Study - Streaming App (Next TV)Thanh Huy ĐoànNo ratings yet

- HP LoadRunner Mobile Recorder tutorial captures Android app trafficDocument3 pagesHP LoadRunner Mobile Recorder tutorial captures Android app trafficPriyank AgarwalNo ratings yet

- Unit2 Ass1 NewDocument3 pagesUnit2 Ass1 Newmaurice007No ratings yet

- Most Common Linux Root User PasswordsDocument190 pagesMost Common Linux Root User PasswordsMihai-Antonio GarvanNo ratings yet

- Liebert Ita 16kva and 20kva - User Manual PDFDocument72 pagesLiebert Ita 16kva and 20kva - User Manual PDFSatheesh Kumar NatarajanNo ratings yet

- Unlock Business Growth with Data AnalyticsDocument56 pagesUnlock Business Growth with Data AnalyticsAizel AlmonteNo ratings yet

- Manual Roland Xp-30Document212 pagesManual Roland Xp-30Jose Luis Rojas Flores100% (1)

- Optimize your SEO with the STT Series 2V220AH tubular flooded battery specificationsDocument1 pageOptimize your SEO with the STT Series 2V220AH tubular flooded battery specificationsPedro A Ocanto BNo ratings yet

- Acoustic Surveillance Device Comparative Assessment Report: BackgroundDocument8 pagesAcoustic Surveillance Device Comparative Assessment Report: BackgroundmultihumanNo ratings yet

- Wooldridge 2002 Rudiments of StataDocument11 pagesWooldridge 2002 Rudiments of StataDineshNo ratings yet

- Instruction Manual: Portable Vibrometer: VM-4424S/HDocument35 pagesInstruction Manual: Portable Vibrometer: VM-4424S/HKitti BoonsongNo ratings yet

- Calculus Optimization Problems SolutionsDocument3 pagesCalculus Optimization Problems SolutionsDonnabell PagaraNo ratings yet

- Drivers For Vostro 1450Document12 pagesDrivers For Vostro 1450cpatra77No ratings yet

- Single Sign-On: Integrating Aws, Openldap, and Shibboleth: A Step-By-Step WalkthroughDocument33 pagesSingle Sign-On: Integrating Aws, Openldap, and Shibboleth: A Step-By-Step WalkthroughSpit FireNo ratings yet

- Philips Pm3295 Service ManualDocument322 pagesPhilips Pm3295 Service Manualglu7833No ratings yet