Professional Documents

Culture Documents

161 5 003187 FDD6685

Uploaded by

Marcos Paulo FariaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

161 5 003187 FDD6685

Uploaded by

Marcos Paulo FariaCopyright:

Available Formats

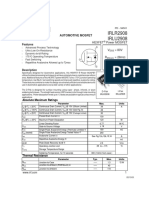

FDD6685

February 2004

FDD6685

30V P-Channel PowerTrench MOSFET

General Description Features

This P-Channel MOSFET is a rugged gate version of • –40 A, –30 V. RDS(ON) = 20 mΩ @ VGS = –10 V

Fairchild Semiconductor’s advanced PowerTrench RDS(ON) = 30 mΩ @ VGS = –4.5 V

process. It has been optimized for power management • Fast switching speed

applications requiring a wide range of gave drive • High performance trench technology for extremely

low RDS(ON)

voltage ratings (4.5V – 25V).

• High power and current handling capability

• Qualified to AEC Q101

D

G G

S

TO-252

D

Absolute Maximum Ratings TA=25oC unless otherwise noted

Symbol Parameter Ratings Units

VDSS Drain-Source Voltage –30 V

VGSS Gate-Source Voltage ±25 V

ID Continuous Drain Current @TC=25°C (Note 3) –40

@TA=25°C (Note 1a) –11 A

Pulsed, PW ≤ 100µs (Note 1b)

–100

PD Power Dissipation for Single Operation (Note 1) 52 W

(Note 1a) 3.8

(Note 1b) 1.6

TJ, TSTG Operating and Storage Junction Temperature Range –55 to +175 °C

Thermal Characteristics

RθJC Thermal Resistance, Junction-to-Case (Note 1) 2.9 °C/W

RθJA Thermal Resistance, Junction-to-Ambient (Note 1a) 40 °C/W

RθJA Thermal Resistance, Junction-to-Ambient (Note 1b) 96 °C/W

This product has been designed to meet the extreme test conditions and environment demanded by the automotive industry.

For a copy of the requirements, see AEC Q101 at http://www.aecouncil.com/

Reliability data can be found at: http://www.fairchildsemi.com/products/discrete/reliability/index.html.

All Fairchild Semiconductor products are manufactured, assembled and tested under ISO9000 and QS9000 quality systems

certification.

2004 Fairchild Semiconductor Corporation FDD6685 Rev D (W)

FDD6685

Package Marking and Ordering Information

Device Marking Device Reel Size Tape Width Quantity

FDD6685 FDD6685 13” 12mm 2500 units

Electrical Characteristics TA = 25°C unless otherwise noted

Symbol Parameter Test Conditions Min Typ Max Units

Drain-Source Avalanche Ratings (Note 4)

EAS Single Pulse Drain-Source ID = –11 A 42 mJ

Avalanche Energy

IAS Maximum Drain-Source –11 A

Avalanche Current

Off Characteristics

BVDSS Drain–Source Breakdown Voltage VGS = 0 V, ID = –250 µA –30 V

∆BVDSS Breakdown Voltage Temperature

ID = –250 µA, Referenced to 25°C –24 mV/°C

∆TJ Coefficient

IDSS Zero Gate Voltage Drain Current VDS = –24 V, VGS = 0 V –1 µA

IGSS Gate–Body Leakage VGS = ±25V, VDS = 0 V ±100 nA

On Characteristics (Note 2)

VGS(th) Gate Threshold Voltage VDS = VGS, ID = –250 µA –1 –1.8 –3 V

∆VGS(th) Gate Threshold Voltage ID = –250 µA, Referenced to 25°C 5 mV/°C

∆TJ Temperature Coefficient

RDS(on) Static Drain–Source VGS = –10 V, ID = –11 A 14 20 mΩ

On–Resistance VGS = –4.5 V, ID = –9 A 21 30

VGS = –10 V,ID = –11 A,TJ=125°C 20

ID(on) On–State Drain Current VGS = –10 V, VDS = –5 V –20 A

gFS Forward Transconductance VDS = –5 V, ID = –11 A 26 S

Dynamic Characteristics

Ciss Input Capacitance VDS = –15 V, V GS = 0 V, 1715 pF

Coss Output Capacitance f = 1.0 MHz 440 pF

Crss Reverse Transfer Capacitance 225 pF

RG Gate Resistance VGS = 15 mV, f = 1.0 MHz 3.6 Ω

Switching Characteristics (Note 2)

td(on) Turn–On Delay Time VDD = –15 V, ID = –1 A, 17 31 ns

tr Turn–On Rise Time VGS = –10 V, RGEN = 6 Ω 11 21 ns

td(off) Turn–Off Delay Time 43 68 ns

tf Turn–Off Fall Time 21 34 ns

Qg Total Gate Charge VDS = –15V, ID = –11 A, 17 24 nC

Qgs Gate–Source Charge VGS = –5 V 9 nC

Qgd Gate–Drain Charge 4 nC

Drain–Source Diode Characteristics and Maximum Ratings

VSD Drain–Source Diode Forward VGS = 0 V, IS = –3.2 A (Note 2) –0.8 –1.2 V

Voltage

Trr Diode Reverse Recovery Time IF = –11 A, 26 ns

Qrr Diode Reverse Recovery Charge diF/dt = 100 A/µs 13 nC

FDD6685 Rev D (W)

FDD6685

Electrical Characteristics TA = 25°C unless otherwise noted

Notes:

1. RθJA is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of

the drain pins. RθJC is guaranteed by design while RθCA is determined by the user's board design.

a) RθJA = 40°C/W when mounted on a b) RθJA = 96°C/W when mounted

1in2 pad of 2 oz copper on a minimum pad.

Scale 1 : 1 on letter size paper

2. Pulse Test: Pulse Width < 300µs, Duty Cycle < 2.0%

PD

3. Maximum current is calculated as: RDS(ON) where PD is maximum power dissipation at TC = 25°C and RDS(on) is at TJ(max) and VGS = 10V.

4. Starting TJ = 25°C, L = 0.69mH, IAS = –11A

FDD6685 Rev D (W)

FDD6685

Typical Characteristics

40 2.4

VGS = -10V -4.5V

-4.0V VGS = -3.5V

2.2

DRAIN-SOURCE ON-RESISTANCE

-6.0V -5.0V

-ID, DRAIN CURRENT (A)

30 2

NORMALIZED

1.8

-4.0V

-3.5V 1.6

20

-4.5V

1.4 -5.0V

-6.0V

10 1.2

-3.0V -8.0V

1 -10V

0 0.8

0 1 2 3 0 2 4 6 8 10

-VDS, DRAIN-SOURCE VOLTAGE (V) -ID, DRAIN CURRENT (A)

Figure 1. On-Region Characteristics. Figure 2. On-Resistance Variation with

Drain Current and Gate Voltage.

1.6 0.08

ID = -11.0A

ID = -5.5A

DRAIN-SOURCE ON-RESISTANCE

VGS = -10V

RDS(ON), ON-RESISTANCE (OHM)

1.4

0.06

NORMALIZED

1.2

0.04

o

TA = 125 C

1

0.02 o

0.8 TA = 25 C

0.6 0

-50 -25 0 25 50 75 100 125 150 175 2 4 6 8 10

TJ, JUNCTION TEMPERATURE (oC) -VGS, GATE TO SOURCE VOLTAGE (V)

Figure 3. On-Resistance Variation with Figure 4. On-Resistance Variation with

Temperature. Gate-to-Source Voltage.

40 100

TA = -55oC VGS = 0V

VDS = -5V o

-IS, REVERSE DRAIN CURRENT (A)

125 C

10

-ID, DRAIN CURRENT (A)

30 o

TA = 125 C

o 1

25 C

25oC

20 0.1

-55oC

0.01

10

0.001

0 0.0001

1 2 3 4 5 0 0.2 0.4 0.6 0.8 1 1.2 1.4

-VGS, GATE TO SOURCE VOLTAGE (V) -VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 5. Transfer Characteristics. Figure 6. Body Diode Forward Voltage Variation

with Source Current and Temperature.

FDD6685 Rev D (W)

FDD6685

Typical Characteristics

10 2400

ID = -11.0 A f = 1MHz

-VGS, GATE-SOURCE VOLTAGE (V)

VDS = 10V VGS = 0 V

8

1800

CAPACITANCE (pF)

30V

Ciss

6

20V 1200

4

Coss

600

2

Crss

0 0

0 5 10 15 20 25 30 0 5 10 15 20 25 30

Qg, GATE CHARGE (nC) VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Gate Charge Characteristics. Figure 8. Capacitance Characteristics.

1000 100

SINGLE PULSE

P(pk), PEAK TRANSIENT POWER (W)

RθJA = 96°C/W

100 80 TA = 25°C

ID, DRAIN CURRENT (A)

100µs

1ms

RDS(ON) LIMIT

10ms

10 100ms 60

1

10s

1 DC 40

VGS = 10V

SINGLE PULSE

0.1 RθJA = 96oC/W 20

TA = 25oC

0.01 0

0.01 0.10 1.00 10.00 100.00 0.01 0.1 1 10 100 1000

VDS, DRAIN-SOURCE VOLTAGE (V) t1, TIME (sec)

Figure 9. Maximum Safe Operating Area. Figure 10. Single Pulse Maximum

Power Dissipation.

1

TRANSIENT THERMAL RESISTANCE

D = 0.5

r(t), NORMALIZED EFFECTIVE

RθJA(t) = r(t) * RθJA

0.2

RθJA = 96 °C/W

0.1 0.1

0.05

P(pk)

0.02

0.01

t1

0.01 t2

TJ - TA = P * RθJA(t)

SINGLE PULSE

Duty Cycle, D = t1 / t2

0.001

0.001 0.01 0.1 1 10 100 1000

t1, TIME (sec)

Figure 11. Transient Thermal Response Curve.

Thermal characterization performed using the conditions described in Note 1b.

Transient thermal response will change depending on the circuit board design.

FDD6685 Rev D (W)

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is

not intended to be an exhaustive list of all such trademarks.

ACEx™ FACT Quiet Series™ ISOPLANAR™ POP™ Stealth™

ActiveArray™ FAST LittleFET™ Power247™ SuperFET™

Bottomless™ FASTr™ MICROCOUPLER™ PowerSaver™ SuperSOT™-3

CoolFET™ FPS™ MicroFET™ PowerTrench SuperSOT™-6

CROSSVOLT™ FRFET™ MicroPak™ QFET SuperSOT™-8

DOME™ GlobalOptoisolator™ MICROWIRE™ QS™ SyncFET™

EcoSPARK™ GTO™ MSX™ QT Optoelectronics™ TinyLogic

E2CMOSTM HiSeC™ MSXPro™ Quiet Series™ TINYOPTO™

EnSignaTM I2C™ OCX™ RapidConfigure™ TruTranslation™

FACT™ ImpliedDisconnect™ OCXPro™ RapidConnect™ UHC™

Across the board. Around the world.™ OPTOLOGIC SILENT SWITCHER UltraFET

The Power Franchise™ OPTOPLANAR™ SMART START™ VCX™

Programmable Active Droop™ PACMAN™ SPM™

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY

ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT

CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant into support device or system whose failure to perform can

the body, or (b) support or sustain life, or (c) whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can be effectiveness.

reasonably expected to result in significant injury to the

user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or This datasheet contains the design specifications for

In Design product development. Specifications may change in

any manner without notice.

Preliminary First Production This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete Not In Production This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

Rev. I8

You might also like

- Right To Resist Unlawful ArrestDocument1 pageRight To Resist Unlawful ArrestThoth AtlanteanNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Integrated Project Management in SAP With Noveco EPMDocument34 pagesIntegrated Project Management in SAP With Noveco EPMrajesh_das3913No ratings yet

- Progress ReportDocument5 pagesProgress Reportapi-394364619No ratings yet

- Restructuring The Circular Economy Into The Resource Based Economy (Michaux, 2021)Document126 pagesRestructuring The Circular Economy Into The Resource Based Economy (Michaux, 2021)CliffhangerNo ratings yet

- Fdd5614P: 60V P-Channel Powertrench MosfetDocument6 pagesFdd5614P: 60V P-Channel Powertrench MosfetAmaury jrNo ratings yet

- CBE6030LDocument8 pagesCBE6030LgdiliogNo ratings yet

- Fdd6680 / Fdu6680: 30V N-Channel Powertrench MosfetDocument6 pagesFdd6680 / Fdu6680: 30V N-Channel Powertrench Mosfetmarcelo giussaniNo ratings yet

- FDD6680ADocument6 pagesFDD6680AEdson HenriqueNo ratings yet

- Fdd9407L - F085: N-Channel Logic Level Powertrench MosfetDocument7 pagesFdd9407L - F085: N-Channel Logic Level Powertrench Mosfetonis1 onis1No ratings yet

- Fdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MDocument11 pagesFdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MSukandar TeaNo ratings yet

- NVHL025N065SC1 D-3326403Document9 pagesNVHL025N065SC1 D-3326403Andrey VulfovichNo ratings yet

- N-Channel Powertrench Mosfet 150V, 21A, 66M: September 2002Document11 pagesN-Channel Powertrench Mosfet 150V, 21A, 66M: September 2002curzNo ratings yet

- Nds 9435 ADocument5 pagesNds 9435 Ajonathan ramos lopezNo ratings yet

- P-Channel 2.5V Specified Powertrench Mosfet: General Description FeaturesDocument5 pagesP-Channel 2.5V Specified Powertrench Mosfet: General Description FeaturesNagaraju NSNo ratings yet

- Fdn358P: Single P-Channel, Logic Level, Powertrench MosfetDocument5 pagesFdn358P: Single P-Channel, Logic Level, Powertrench MosfetAlex KarimNo ratings yet

- Si4435Dy: 30V P-Channel Powertrench MosfetDocument5 pagesSi4435Dy: 30V P-Channel Powertrench MosfetBedjo TjahmricanNo ratings yet

- N-Channel Power Trench Mosfet: Features General DescriptionDocument8 pagesN-Channel Power Trench Mosfet: Features General DescriptionRicardo VieiraNo ratings yet

- FDD6637 888878 PDFDocument11 pagesFDD6637 888878 PDFRED KaromiNo ratings yet

- STP40NF10 STB40NF10 - STB40NF10-1Document12 pagesSTP40NF10 STB40NF10 - STB40NF10-1Anca SterianNo ratings yet

- Onsemiconductor Nds8410a Datasheets 3577Document5 pagesOnsemiconductor Nds8410a Datasheets 3577Google EyeNo ratings yet

- NCE8295A: Enhancement Mode Power MOSFETDocument7 pagesNCE8295A: Enhancement Mode Power MOSFETDarknezzNo ratings yet

- FQP12P10: P-Channel QFET MosfetDocument8 pagesFQP12P10: P-Channel QFET MosfetCrdz LouisNo ratings yet

- TK11A65D Datasheet en 20131225Document9 pagesTK11A65D Datasheet en 20131225Iliescu CristianNo ratings yet

- NVHL040N120SC1 D-2319550Document8 pagesNVHL040N120SC1 D-2319550Luis EduardoNo ratings yet

- Mosfet: NTD5802N, NVD5802N - Power, Single, N-Channel, DPAKDocument7 pagesMosfet: NTD5802N, NVD5802N - Power, Single, N-Channel, DPAKPusong BatoNo ratings yet

- Advanced Power Electronics Corp.: AP9997GH/J-HFDocument4 pagesAdvanced Power Electronics Corp.: AP9997GH/J-HFWelly CahyadiNo ratings yet

- Fds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesDocument6 pagesFds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesEdgxr DxnielNo ratings yet

- Advanced Power MOSFET with low gate charge and RDS(ONDocument4 pagesAdvanced Power MOSFET with low gate charge and RDS(ONJose M PeresNo ratings yet

- Irlr 29056Document11 pagesIrlr 29056JORGENo ratings yet

- TPC8064-H: DescriptionDocument5 pagesTPC8064-H: DescriptionBari ShobariNo ratings yet

- 4435 FairchildSemiconductorDocument6 pages4435 FairchildSemiconductorYared TarikuNo ratings yet

- MDS3604 P-Channel Trench MOSFET -30V -11A 12.1mΩDocument6 pagesMDS3604 P-Channel Trench MOSFET -30V -11A 12.1mΩjay rNo ratings yet

- FDP 5800Document8 pagesFDP 5800Khalid JakirNo ratings yet

- Data SheetDocument6 pagesData SheetAlberto IsmaelNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument5 pagesAdvanced Power Electronics Corp.: DescriptionkalanghoNo ratings yet

- Is Now Part ofDocument10 pagesIs Now Part ofMatias GonzalezNo ratings yet

- Datasheet - HK Fds9431a10 4643859Document5 pagesDatasheet - HK Fds9431a10 4643859jim campbellNo ratings yet

- Onsemiconductor Fds6679az Datasheets 0664Document6 pagesOnsemiconductor Fds6679az Datasheets 0664Yohandris FernandezNo ratings yet

- 72T02GH AdvancedPowerElectronicsDocument6 pages72T02GH AdvancedPowerElectronicsjose jesus arteaga gomezNo ratings yet

- Advanced Power Electronics Corp.: AP72T02GH/JDocument6 pagesAdvanced Power Electronics Corp.: AP72T02GH/JFrancisco MataNo ratings yet

- FDD8447LDocument6 pagesFDD8447Lsorsa1No ratings yet

- RF Power Field Effect Transistors: N-Channel Enhancement-Mode Lateral MosfetsDocument18 pagesRF Power Field Effect Transistors: N-Channel Enhancement-Mode Lateral MosfetsdanawayanNo ratings yet

- Ap9997gh-Hf Power Mosfet NDocument4 pagesAp9997gh-Hf Power Mosfet NVictorManuelBernalBlancoNo ratings yet

- FTK 7002 KDocument6 pagesFTK 7002 K100ASSUKANo ratings yet

- P-CH fdd4685 - 2Document6 pagesP-CH fdd4685 - 2Ahmed Sherif CupoNo ratings yet

- NDF08N60Z, NDP08N60Z N-Channel Power MOSFET 600 V, 0.95 WDocument6 pagesNDF08N60Z, NDP08N60Z N-Channel Power MOSFET 600 V, 0.95 WCHERPINNo ratings yet

- IRF840 AdvancedPowerElectronicsDocument4 pagesIRF840 AdvancedPowerElectronicssheikh sheharyarNo ratings yet

- Irf 634 BDocument8 pagesIrf 634 BAhmed ShagidullinNo ratings yet

- P06VDocument7 pagesP06VMauro BusciglioNo ratings yet

- B 812 Cfa 38Document8 pagesB 812 Cfa 38Sajid AliNo ratings yet

- FDN352 ApDocument5 pagesFDN352 ApTecnicos SlotsNo ratings yet

- NDS332PDocument6 pagesNDS332PmitrakaryaNo ratings yet

- MTP3055VLDocument3 pagesMTP3055VLsybiantechnologies2009No ratings yet

- IRLR2908 IRLU2908: Automotive MosfetDocument11 pagesIRLR2908 IRLU2908: Automotive MosfetAnhVũNo ratings yet

- Fdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MDocument5 pagesFdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MKakatuar KakatuaNo ratings yet

- Nce 8295 AkDocument7 pagesNce 8295 Akandre kressnerNo ratings yet

- FDS9435A FairchildSemiconductorDocument6 pagesFDS9435A FairchildSemiconductormuhammad FikriNo ratings yet

- 83T03GH HF AdvancedPowerElectronicsDocument4 pages83T03GH HF AdvancedPowerElectronicsАлексей ГомоновNo ratings yet

- 20N50EDocument8 pages20N50EFernando SimãoNo ratings yet

- Hoja de Datos 10n65kDocument6 pagesHoja de Datos 10n65kleamxi777No ratings yet

- Project Description and DefinitionDocument7 pagesProject Description and DefinitionAlbert Jonnel DomingoNo ratings yet

- Coronary artery diseases reviewDocument43 pagesCoronary artery diseases reviewKeputrian FKUPNo ratings yet

- Supplement - 7 Procurement Manual: Democratic Socialist Republic of Sri LankaDocument8 pagesSupplement - 7 Procurement Manual: Democratic Socialist Republic of Sri LankaDinuka MalinthaNo ratings yet

- MEETING OF THE BOARD OF GOVERNORS Committee on University Governance April 17, 2024Document8 pagesMEETING OF THE BOARD OF GOVERNORS Committee on University Governance April 17, 2024Jamie BouletNo ratings yet

- Machine Problem 6 Securing Cloud Services in The IoTDocument4 pagesMachine Problem 6 Securing Cloud Services in The IoTJohn Karlo KinkitoNo ratings yet

- Group Assignment: Consumer Buying Behaviour Towards ChipsDocument3 pagesGroup Assignment: Consumer Buying Behaviour Towards ChipsvikasNo ratings yet

- CASE FLOW AT REGIONAL ARBITRATIONDocument2 pagesCASE FLOW AT REGIONAL ARBITRATIONMichael Francis AyapanaNo ratings yet

- Dues+&+Bylaws+Committee+Packet ICPI John@bestadmix Com Tholyfield@Document52 pagesDues+&+Bylaws+Committee+Packet ICPI John@bestadmix Com Tholyfield@Greefield JasonNo ratings yet

- Kinds of ObligationDocument50 pagesKinds of ObligationKIM GABRIEL PAMITTANNo ratings yet

- M88A2 Recovery VehicleDocument2 pagesM88A2 Recovery VehicleJuan CNo ratings yet

- Black Box Components and FunctionsDocument9 pagesBlack Box Components and FunctionsSaifNo ratings yet

- COA (Odoo Egypt)Document8 pagesCOA (Odoo Egypt)menams2010No ratings yet

- PH Measurement TechniqueDocument5 pagesPH Measurement TechniquevahidNo ratings yet

- Flex VPNDocument3 pagesFlex VPNAnonymous nFOywQZNo ratings yet

- Torta de Riso Business PlanDocument25 pagesTorta de Riso Business PlanSalty lNo ratings yet

- Engineering Ethics in Practice ShorterDocument79 pagesEngineering Ethics in Practice ShorterPrashanta NaikNo ratings yet

- Midterm Exam SolutionsDocument11 pagesMidterm Exam SolutionsPatrick Browne100% (1)

- CIGB B164 Erosion InterneDocument163 pagesCIGB B164 Erosion InterneJonathan ColeNo ratings yet

- 2019-03-30 New Scientist PDFDocument60 pages2019-03-30 New Scientist PDFthoma leongNo ratings yet

- Claim Form - Group Health InsuranceDocument5 pagesClaim Form - Group Health Insurancevizag mdindiaNo ratings yet

- Grid Xtreme VR Data Sheet enDocument3 pagesGrid Xtreme VR Data Sheet enlong bạchNo ratings yet

- Chapter 6 Performance Review and Appraisal - ReproDocument22 pagesChapter 6 Performance Review and Appraisal - ReproPrecious SanchezNo ratings yet

- Merging - Scaled - 1D - & - Trying - Different - CLassification - ML - Models - .Ipynb - ColaboratoryDocument16 pagesMerging - Scaled - 1D - & - Trying - Different - CLassification - ML - Models - .Ipynb - Colaboratorygirishcherry12100% (1)

- Mercedes B-Class Accessories ListDocument34 pagesMercedes B-Class Accessories ListmuskystoatNo ratings yet

- Ge Dir ReportsDocument1 pageGe Dir Reportsselvam chidambaramNo ratings yet

- Culture GuideDocument44 pagesCulture GuideLeonardo TamburusNo ratings yet