Professional Documents

Culture Documents

Op Amp Design

Uploaded by

Sermalingam ChandrasekarOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Op Amp Design

Uploaded by

Sermalingam ChandrasekarCopyright:

Available Formats

Lecture 160 MOSFET Op Amp Design (1/30/04)

Page 160-1

LECTURE 160 MOSFET OP AMP DESIGN

(READING: GHLM 472-480, AH 269-286) INTRODUCTION Objective The objective of this presentation is: 1.) Develop the design equations for a two-stage CMOS op amp 2.) Illustrate the design of a two-stage CMOS op amp Outline Design relationships Design of Two Stage CMOS Op Amp Summary

ECE 6412 - Analog Integrated Circuit Design - II Lecture 160 MOSFET Op Amp Design (1/30/04)

P.E. Allen - 2002 Page 160-2

OP AMP DESIGN

Unbuffered, Two-Stage CMOS Op Amp

VDD M6 M3 M4

Cc

vout

vin +

M1

M2

CL

+ VBias -

M5 VSS

M7

Fig. 160-01

Notation: Wi Si = L = W/L of the ith transistor i

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 160 MOSFET Op Amp Design (1/30/04)

Page 160-3

Design Relationships for the Two-Stage Op Amp I5 Slew rate SR = Cc (Assuming I7 >>I5 and CL > Cc) gm1 2gm1 First-stage gain Av1 = gds2 + gds4 = I5(2 + 4) gm6 gm6 Second-stage gain Av2 = gds6 + gds7 = I6(6 + 7) gm1 Gain-bandwidth GB = Cc gm6 Output pole p2 = CL gm6 RHP zero z1 = Cc 60 phase margin requires that gm6 = 2.2gm2(CL/Cc) if all other roots are 10GB. I5 Positive ICMR Vin(max) = VDD 3 |VT03|(max) + VT1(min)) I5 Negative ICMR Vin(min) = VSS + 1 + VT1(max) + VDS5(sat) 2IDS (all transistors are saturated) Saturation voltageVDS(sat) =

ECE 6412 - Analog Integrated Circuit Design - II Lecture 160 MOSFET Op Amp Design (1/30/04) P.E. Allen - 2002 Page 160-4

Op Amp Specifications The following design procedure assumes that specifications for the following parameters are given. 1. Gain at dc, Av(0) Max. ICMR and/or p3 2. Gain-bandwidth, GB VDD Vout(max) + + VSG6 3. Phase margin (or settling time) VSG4 M6 gm6 or 4. Input common-mode range, ICMR M3 M4 Proper Mirroring Cc I6 5. Load Capacitance, CL VSG4=VSG6 gm1 GB = vout Cc 6. Slew-rate, SR CL Cc 0.2CL vin M1 M2 7. Output voltage swing (PM = 60) + 8. Power dissipation, Pdiss I5 Min. ICMR I5 = SRCc

Vout(min) + VBias -

M5 VSS

M7

Fig. 160-02

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 160 MOSFET Op Amp Design (1/30/04)

Page 160-5

Unbuffered Op Amp Design Procedure This design procedure assumes that the gain at dc (Av), unity gain bandwidth (GB), input common mode range (Vin(min) and Vin(max)), load capacitance (CL), slew rate (SR), settling time (Ts), output voltage swing (Vout(max) and Vout(min)), and power dissipation (Pdiss) are given. Choose the smallest device length which will keep the channel modulation parameter constant and give good matching for current mirrors. 1. From the desired phase margin, choose the minimum value for Cc, i.e. for a 60 phase margin we use the following relationship. This assumes that z 10GB. Cc > 0.22CL 2. Determine the minimum value for the tail current (I5) from the largest of the two values. VDD + |VSS| .Cc or I5 10 I5 = SR 2 .Ts 3. Design for S3 from the maximum input voltage specification. I5 S3 = K'3[VDD Vin(max) |VT03|(max) + VT1(min)]2 4. Verify that the pole of M3 due to Cgs3 and Cgs4 (= 0.67W3L3Cox) will not be dominant by assuming it to be greater than 10 GB gm3 2Cgs3 > 10GB.

ECE 6412 - Analog Integrated Circuit Design - II Lecture 160 MOSFET Op Amp Design (1/30/04) P.E. Allen - 2002 Page 160-6

Unbuffered Op Amp Design Procedure - Continued 5. Design for S1 (S2) to achieve the desired GB. gm22 gm1 = GB . Cc S2 = K'2I5 6. Design for S5 from the minimum input voltage. First calculate VDS5(sat) then find S5. 2I5 I5 VDS5(sat) = Vin(min) VSS 1 VT1(max) 100 mV S5 = K'5[VDS5(sat)]2 7. Find S6 by letting the second pole (p2) be equal to 2.2 times GB and assuming that VSG4 = VSG6. gm6 gm6 = 2.2gm2(CL/Cc) S6 = S4 gm4 8. Calculate I6 from gm62 I6 = 2K'6S6 Check to make sure that S6 satisfies the Vout(max) requirement and adjust as necessary. 9. Design S7 to achieve the desired current ratios between I5 and I6. S7 = (I6/I5)S5 (Check the minimum output voltage requirements)

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 160 MOSFET Op Amp Design (1/30/04)

Page 160-7

Unbuffered Op Amp Design Procedure - Continued 10. Check gain and power dissipation specifications. 2gm2gm6 Av = I5(2 + 3)I6(6 + 7) Pdiss = (I5 + I6)(VDD + |VSS|) 11. If the gain specification is not met, then the currents, I5 and I6, can be decreased or the W/L ratios of M2 and/or M6 increased. The previous calculations must be rechecked to insure that they are satisfied. If the power dissipation is too high, then one can only reduce the currents I5 and I6. Reduction of currents will probably necessitate increase of some of the W/L ratios in order to satisfy input and output swings. 12. Simulate the circuit to check to see that all specifications are met.

ECE 6412 - Analog Integrated Circuit Design - II Lecture 160 MOSFET Op Amp Design (1/30/04)

P.E. Allen - 2002 Page 160-8

Example 1 - Design of a Two-Stage Op Amp Using the material and device parameters given in Tables 3.1-1 and 3.1-2, design an amplifier similar to that shown in Fig. 6.3-1 that meets the following specifications. Assume the channel length is to be 1m. VSS = -2.5V 60 phase margin Av > 3000V/V VDD = 2.5V GB = 5MHz CL = 10pF SR > 10V/s Vout range = 2V ICMR = -1 to 2V Pdiss 2mW Solution 1.) The first step is to calculate the minimum value of the compensation capacitor Cc, Cc > (2.2/10)(10 pF) = 2.2 pF 2.) Choose Cc as 3pF. Using the slew-rate specification and Cc calculate I5. I5 = (3x10-12)(10x106) = 30 A 3.) Next calculate (W/L)3 using ICMR requirements. 30x10-6 (W/L)3 = (50x10-6)[2.5 2 .85 + 0.55]2 = 15 (W/L)3 = (W/L)4 = 15

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 160 MOSFET Op Amp Design (1/30/04)

Page 160-9

Example 1 - Continued 4.) Now we can check the value of the mirror pole, p3, to make sure that it is in fact greater than 10GB. Assume the Cox = 0.4fF/m2. The mirror pole can be found as -gm3 - 2KpS3I3 p3 2C = 2(0.667)W L C = 2.81x109(rads/sec) gs3 3 3 ox or 448 MHz. Thus, p3, is not of concern in this design because p3 >> 10GB. 5.) The next step in the design is to calculate gm1 to get gm1 = (5x106)(2)(3x10-12) = 94.25S Therefore, (W/L)1 is gm12 (94.25)2 (W/L)1 = (W/L)2 = 2K I = 211015 = 2.79 3.0 (W/L)1 = (W/L)2 = 3 N 1 6.) Next calculate VDS5, 30x10-6 VDS5 = (1) (2.5) 110x10-63 - .85 = 0.35V Using VDS5 calculate (W/L)5 from the saturation relationship. 2(30x10-6) (W/L)5 = 4.5 (W/L)5 = (110x10-6)(0.35)2 = 4.49 4.5

ECE 6412 - Analog Integrated Circuit Design - II Lecture 160 MOSFET Op Amp Design (1/30/04)

P.E. Allen - 2002 Page 160-10

|Example 1 - Continued 7.) For 60 phase margin, we know that gm6 10gm1 942.5S Assuming that gm6 = 942.5S and knowing that gm4 = 150S, we calculate (W/L)6 as 942.5x10-6 (W/L)6 = 15 (150x10-6) = 94.25 94 8.) Calculate I6 using the small-signal gm expression: (942.5x10-6)2 I6 = (2)(50x10-6)(94.25) = 94.5A 95A If we calculate (W/L)6 based on Vout(max), the value is approximately 15. Since 94 exceeds the specification and maintains better phase margin, we will stay with (W/L)6 = 94 and I6 = 95A. With I6 = 95A the power dissipation is Pdiss = 5V(30A+95A) = 0.625mW.

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 160 MOSFET Op Amp Design (1/30/04)

Page 160-11

Example 1 - Continued 9.) Finally, calculate (W/L)7

95x10-6 (W/L)7 = 4.5 30x10-6 = 14.25 14

(W/L)7 = 14

Let us check the Vout(min) specification although the W/L of M7 is so large that this is probably not necessary. The value of Vout(min) is 295 11035 = 0.351V which is less than required. At this point, the first-cut design is complete. 10.) Now check to see that the gain specification has been met (92.45x10-6)(942.5x10-6) Av = 15x10-6 (.04 + .05)95x10-6 (.04 + .05) = 7,697V/V which exceeds the specifications by a factor of two. .An easy way to achieve more gain would be to increase the W and L values by a factor of two which because of the decreased value of would multiply the above gain by a factor of 20. Vout(min) = VDS7(sat) =

ECE 6412 - Analog Integrated Circuit Design - II Lecture 160 MOSFET Op Amp Design (1/30/04)

P.E. Allen - 2002 Page 160-12

Incorporating the Nulling Resistor into the Miller Compensated Two-Stage Op Amp Circuit:

VDD

M11 VA M10 VC

IBias

M3 CM vin-

M4 V B M8 vin+ M1 M2 Cc

M6 vout

CL

M12

M9

M5

VSS

M7

Fig. 160-03

We saw earlier that the roots were: gm2 gm1 gm6 p2 = CL p1 = AvCc = AvCc 1 1 p4 = RzCI z1 = RzCc Cc/gm6 where Av = gm1gm6RIRII. (Note that p4 is the pole resulting from the nulling resistor compensation technique.)

ECE 6412 - Analog Integrated Circuit Design - II P.E. Allen - 2002

Lecture 160 MOSFET Op Amp Design (1/30/04)

Page 160-13

Design of the Nulling Resistor (M8) In order to place the zero on top of the second pole (p2), the following relationship must hold 1 CL + Cc Cc+CL 1 Rz = gm6 Cc = C c 2KPS6I6 The resistor, Rz, is realized by the transistor M8 which is operating in the active region because the dc current through it is zero. Therefore, Rz, can be written as vDS8 1 Rz = iD8 = KPS8(VSG8-|VTP|) VDS8=0 The bias circuit is designed so that voltage VA is equal to VB. W 11 I10 W 6 |VGS10| |VT| = |VGS8| |VT| VSG11 = VSG6 L =I L 11 6 6 In the saturation region 2(I10) |VGS10| |VT| = K'P(W10/L10) = |VGS8| |VT| KPS10 1 S10 1 = S8 Rz = K S 2I10 2KPI10 P 8 W 8 S10S6I6 Cc Equating the two expressions for Rz gives L8 = CL + Cc I10

ECE 6412 - Analog Integrated Circuit Design - II Lecture 160 MOSFET Op Amp Design (1/30/04) P.E. Allen - 2002 Page 160-14

Example 2 - RHP Zero Compensation Use results of Ex. 1 and design compensation circuitry so that the RHP zero is moved from the RHP to the LHP and placed on top of the output pole p2. Use device data given in Ex. 1. Solution The task at hand is the design of transistors M8, M9, M10, M11, and bias current I10. The first step in this design is to establish the bias components. In order to set VA equal to VB, then VSG11 must equal VSG6. Therefore, S11 = (I11/I6)S6 Choose I11 = I10 = I9 = 15A which gives S11 = (15A/95A)94 = 14.8 15. The aspect ratio of M10 is essentially a free parameter, and will be set equal to 1. There must be sufficient supply voltage to support the sum of VSG11, VSG10, and VDS9. The ratio of I10/I5 determines the (W/L) of M9. This ratio is (W/L)9 = (I10/I5)(W/L)5 = (15/30)(4.5) = 2.25 2 Now (W/L)8 is determined to be

3pF (W/L)8 = 3pF+10pF

19495A = 5.63 6 15A

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 160 MOSFET Op Amp Design (1/30/04)

Page 160-15

Example 2 - Continued It is worthwhile to check that the RHP zero has been moved on top of p2. To do this, first calculate the value of Rz. VSG8 must first be determined. It is equal to VSG10, which is VSG10 = Next determine Rz. 1 106 Rz = KPS8(VSG10-|VTP|) = 505.63(1.474-.7) = 4.590k The location of z1 is calculated as 1 6 z1 = 3x10-12 = -94.46x10 rads/sec (4.590 x 103)(3x10-12) 942.5x10-6 The output pole, p2, is 942.5x10-6 p2 = 10x10-12 = -94.25x106 rads/sec Thus, we see that for all practical purposes, the output pole is canceled by the zero that has been moved from the RHP to the LHP. The results of this design are summarized below. W9 = 2 m W10 = 1 m W11 = 15 m W8 = 6 m

ECE 6412 - Analog Integrated Circuit Design - II Lecture 160 MOSFET Op Amp Design (1/30/04) P.E. Allen - 2002 Page 160-16

2I10 KPS10 + |VTP| =

215 501 + 0.7 = 1.474V

SUMMARY Programmability of the Two-Stage Op Amp The following relationships depend on the bias current, Ibias, in the following manner and allow for M3 programmability after fabrication. 1 Av(0) = gmIgmIIRIRII I M1 Bias vin gmI + GB = Cc IBias IBias Pdiss = (VDD+|VSS|)(1+K1+K2)IBias Ibias K1IBias SR = Cc IBias 1 1 Rout = 2K2IBias IBias 103 |p1| Pdiss and SR 102 IBias2 1 |p1| = gmIIRIRIICc I IBias1.5 101 Bias GB and z 100 gmII |z| = Cc IBias 10-1 Ao and Rout 10-2 Illustration of the Ibias dependence

10-3 1 10 IBias IBias(ref)

ECE 6412 - Analog Integrated Circuit Design - II

VDD M6 M4

vout

M2

K2IBias K1IBias M5 VSS M7

Fig. 160-04

100

Fig. 160-05

P.E. Allen - 2002

You might also like

- Adv CKT Technique Using GmIdDocument35 pagesAdv CKT Technique Using GmIdnarashimarajaNo ratings yet

- Bandgap 2009Document27 pagesBandgap 2009jjloksNo ratings yet

- Design of PVT Tolerant Bandgap Reference Circuit For Low Noise and Low CurrentDocument66 pagesDesign of PVT Tolerant Bandgap Reference Circuit For Low Noise and Low CurrentManraj Gujral100% (1)

- Bandgap Reference, Schematic and Performance Parameter: by Vikram Dhole Under The Guidance of Dr.M.B.MaliDocument11 pagesBandgap Reference, Schematic and Performance Parameter: by Vikram Dhole Under The Guidance of Dr.M.B.MaliShaikh NadeemNo ratings yet

- Band Gap ReferencesDocument115 pagesBand Gap ReferencesNam Luu Nguyen NhatNo ratings yet

- Design of Two Stage Op-AmpDocument4 pagesDesign of Two Stage Op-AmpWARSE JournalsNo ratings yet

- Cadence Manual PDFDocument96 pagesCadence Manual PDFfaltuNo ratings yet

- VHDL Coding Tips and Tricks - VHDL Code For BCD To 7-Segment Display ConverterDocument4 pagesVHDL Coding Tips and Tricks - VHDL Code For BCD To 7-Segment Display Convertermrithyunjaysiv100% (1)

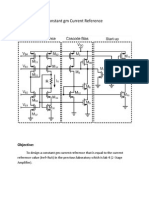

- Constant GM Current ReferenceDocument4 pagesConstant GM Current ReferenceGp GonzalesNo ratings yet

- Ethics Position PaperDocument8 pagesEthics Position Papercwise2100% (1)

- CST DipoleDocument3 pagesCST DipoleDipen K. DasNo ratings yet

- Self-Sufficient Guide To Electronics Engineering by JASON AMPOLOQUIODocument14 pagesSelf-Sufficient Guide To Electronics Engineering by JASON AMPOLOQUIOGemalyn NacarioNo ratings yet

- Cmos Op - AmpDocument289 pagesCmos Op - AmpMiraju B Mirajub0% (1)

- 7-Element Yagi REPORTDocument13 pages7-Element Yagi REPORTbashir abdirahman husseinNo ratings yet

- 65 NMDocument5 pages65 NMDamodar TeluNo ratings yet

- 4-8-16 B Tech ECE Revised Batch 2011 3-8Document72 pages4-8-16 B Tech ECE Revised Batch 2011 3-8Zlatan Deric AturindaNo ratings yet

- Bb101 Chapter 1 Physical Quantities and MeasurementDocument14 pagesBb101 Chapter 1 Physical Quantities and MeasurementAidi AmarNo ratings yet

- VLSI Design TechniquesDocument119 pagesVLSI Design Techniquesrajesh26julyNo ratings yet

- Lesson 11 DC Transient AnalysisDocument81 pagesLesson 11 DC Transient AnalysisJoshua JapitanNo ratings yet

- France Grading SystemDocument6 pagesFrance Grading SystemClara AlbertNo ratings yet

- Ahuja CompensationDocument5 pagesAhuja CompensationCem ÇakırNo ratings yet

- MSC 07Document136 pagesMSC 07Ebenezer Amoah-KyeiNo ratings yet

- Design of A Fully Differential High-Speed High-Precision AmplifierDocument10 pagesDesign of A Fully Differential High-Speed High-Precision Amplifierkirkland1337No ratings yet

- Physics (Linear Momentum)Document19 pagesPhysics (Linear Momentum)slim_101No ratings yet

- Lect08 GM ID Sizing MethodDocument55 pagesLect08 GM ID Sizing MethodAmith NayakNo ratings yet

- Qualitative Analysis 2Document81 pagesQualitative Analysis 2nateq oikNo ratings yet

- Chapter 10 PDFDocument26 pagesChapter 10 PDFPugazhendhi MuthuNo ratings yet

- Two-Stage CMOS Op-Amp Circuit Design - Jianfeng SunDocument17 pagesTwo-Stage CMOS Op-Amp Circuit Design - Jianfeng Sunjianfeng sun100% (2)

- Current Mirror RefDocument23 pagesCurrent Mirror Refkishore_beerakaNo ratings yet

- Matching LayoutDocument41 pagesMatching Layoutvarun186No ratings yet

- Vga BookDocument81 pagesVga BookManju BhargaviNo ratings yet

- Lab 8 - Current MirrorDocument18 pagesLab 8 - Current MirrorKram Nhoj TabatabNo ratings yet

- Eric Thesis SlidesDocument43 pagesEric Thesis SlidesHumberto JuniorNo ratings yet

- Nucleic Acids ExamDocument3 pagesNucleic Acids ExamAlbert TayagNo ratings yet

- Physics and Modelling of Microelectronic Devices: BITS PilaniDocument31 pagesPhysics and Modelling of Microelectronic Devices: BITS PilaniSmriti RaiNo ratings yet

- ThrowAwayYourSpreadsheetsWorkShopSlides PDFDocument77 pagesThrowAwayYourSpreadsheetsWorkShopSlides PDFBudavarapu MaheshNo ratings yet

- Abp Dynamics Multiple Choice 2016-02-24Document10 pagesAbp Dynamics Multiple Choice 2016-02-24artsidartsyNo ratings yet

- CadenceVirtuosoTutorial CSU2020Document25 pagesCadenceVirtuosoTutorial CSU2020sadjkfhasdNo ratings yet

- Design of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTADocument22 pagesDesign of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTAZarion JacobsNo ratings yet

- Cmos ReportDocument25 pagesCmos ReportNaveen KumarNo ratings yet

- Creating An Inverter Layout Using L-EditDocument9 pagesCreating An Inverter Layout Using L-EditVinod MannNo ratings yet

- Comparator Kick Back Noise PaperDocument8 pagesComparator Kick Back Noise Papergr8minds4allNo ratings yet

- PHD Thesis Template NIT KurukshetraDocument27 pagesPHD Thesis Template NIT KurukshetraNikhitaNo ratings yet

- Genetics Lesson PlanDocument4 pagesGenetics Lesson Plankayla08No ratings yet

- 65nm Signoff: Proprietary & Confidential CDocument20 pages65nm Signoff: Proprietary & Confidential Cravishoping100% (1)

- VerilogDocument30 pagesVerilogindrajeet4saravananNo ratings yet

- Sesq PDFDocument11 pagesSesq PDFClint CamNo ratings yet

- BJT DC Parameter EstractionDocument67 pagesBJT DC Parameter EstractionJuan R Ayala-OlivaresNo ratings yet

- 3-Frequency Dependent CircuitsDocument63 pages3-Frequency Dependent CircuitsDaisy PriyaNo ratings yet

- Digital Control Board For Phased Array Antenna Beam Steering in ADocument115 pagesDigital Control Board For Phased Array Antenna Beam Steering in AJaime LazoNo ratings yet

- Lecture1 IntroDocument35 pagesLecture1 Introapi-3834272No ratings yet

- Cmos Funda Full CourseDocument365 pagesCmos Funda Full CourseKumar BsnspNo ratings yet

- Montecarlo PDFDocument7 pagesMontecarlo PDFSougata GhoshNo ratings yet

- HFIC Chapter 4 HF TransistorsDocument77 pagesHFIC Chapter 4 HF TransistorsYosra Be100% (1)

- Lect2UP240 (100328)Document16 pagesLect2UP240 (100328)Lorenzo CaNo ratings yet

- Two Stage OpampDocument17 pagesTwo Stage OpampMac YuNo ratings yet

- Lect15 AnalogICDocument15 pagesLect15 AnalogICsayemeeceNo ratings yet

- OTA ComparatorsDocument41 pagesOTA ComparatorsPedro Aaron Saldaña100% (1)

- L330 LowPowerOpAmps 2UPDocument7 pagesL330 LowPowerOpAmps 2UPVan Nguyen Huu VanNo ratings yet

- Birla Institute of Technology & Science, Pilani: Analog AssignmentDocument24 pagesBirla Institute of Technology & Science, Pilani: Analog AssignmentRahamtulla MohammadNo ratings yet

- Essay, How Microscopes Have Contributed To Our Understanding of Living OrganismsDocument2 pagesEssay, How Microscopes Have Contributed To Our Understanding of Living Organismslinanqikiki82% (11)

- Designpro V3 - Gas Lift Design Tutorial: Return To Main - NextDocument81 pagesDesignpro V3 - Gas Lift Design Tutorial: Return To Main - NextAli AliNo ratings yet

- Animal Instinct (Em, Original) Acordes GuitarraDocument2 pagesAnimal Instinct (Em, Original) Acordes GuitarraGustavoNo ratings yet

- Clover by The RiverDocument24 pagesClover by The RiverE. PoornimaNo ratings yet

- Speaking With Confidence: Chapter Objectives: Chapter OutlineDocument12 pagesSpeaking With Confidence: Chapter Objectives: Chapter OutlinehassanNo ratings yet

- British Vs American English - CrosswordDocument3 pagesBritish Vs American English - Crosswordlkham enkhsaikhanNo ratings yet

- Atomic Structure RevisionDocument4 pagesAtomic Structure RevisioncvNo ratings yet

- 4.5.redistrribution - PBR Quiz AnswersDocument4 pages4.5.redistrribution - PBR Quiz AnswersffbugbuggerNo ratings yet

- CBSE Sample Paper Class 9 Science SA2 Set 7Document13 pagesCBSE Sample Paper Class 9 Science SA2 Set 7PALAK SHARMANo ratings yet

- Whitepaper - Loadspreading and SeafasteningDocument3 pagesWhitepaper - Loadspreading and SeafasteningtyuNo ratings yet

- Transes - Male & Female GenitaliaDocument10 pagesTranses - Male & Female GenitaliacamatoviancaNo ratings yet

- SWOT Analysis Textile IndustryDocument23 pagesSWOT Analysis Textile Industrydumitrescu viorelNo ratings yet

- Opti-Cal TPS1200 Terminal Mode QuickguideDocument4 pagesOpti-Cal TPS1200 Terminal Mode QuickguideClaudiu OvidiuNo ratings yet

- Q4 Lesson 3 Hinge Theorem and Its ConverseDocument36 pagesQ4 Lesson 3 Hinge Theorem and Its ConverseZenn Tee100% (1)

- Class VII Half Yearly Maths, M.junaidDocument4 pagesClass VII Half Yearly Maths, M.junaidmohd junaidNo ratings yet

- Introducing RS: A New 3D Program For Geotechnical AnalysisDocument4 pagesIntroducing RS: A New 3D Program For Geotechnical AnalysisAriel BustamanteNo ratings yet

- My 6-Step Plan For Diagnosing & Managing The Pruritic DogDocument6 pagesMy 6-Step Plan For Diagnosing & Managing The Pruritic DogAnonymous TDI8qdYNo ratings yet

- Animal Cells PDFDocument4 pagesAnimal Cells PDFFalah HabibNo ratings yet

- Bergeron Et Al 2023 Use of Invasive Brain Computer Interfaces in Pediatric Neurosurgery Technical and EthicalDocument16 pagesBergeron Et Al 2023 Use of Invasive Brain Computer Interfaces in Pediatric Neurosurgery Technical and EthicalPriscilla MelindaNo ratings yet

- BJ SurfactantsDocument2 pagesBJ SurfactantsAquiles Carrera100% (2)

- Literature ReviewDocument3 pagesLiterature ReviewAina Reyes100% (1)

- 100G OTN Muxponder: Cost-Efficient Transport of 10x10G Over 100G in Metro NetworksDocument2 pages100G OTN Muxponder: Cost-Efficient Transport of 10x10G Over 100G in Metro NetworkshasNo ratings yet

- Shipping Agents in SGDocument3 pagesShipping Agents in SGeason insightsNo ratings yet

- Comsol ProfileDocument4 pagesComsol ProfilePrashant KumarNo ratings yet

- Discussion 2 Module 2 - Paronda PDFDocument1 pageDiscussion 2 Module 2 - Paronda PDFAlvanna ParondaNo ratings yet

- NCERT Class 7 English Part 1 PDFDocument157 pagesNCERT Class 7 English Part 1 PDFVvs SadanNo ratings yet

- Distribution System ReliabilityDocument8 pagesDistribution System Reliabilityabera alemayehuNo ratings yet

- Photovoltaic Water Heater: The Ecological Revolution MADE IN ITALYDocument4 pagesPhotovoltaic Water Heater: The Ecological Revolution MADE IN ITALYDani Good VibeNo ratings yet

- Site Survey - ReportDocument22 pagesSite Survey - Reportmubashar_6186144No ratings yet