Professional Documents

Culture Documents

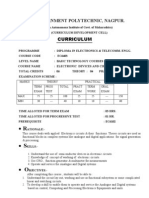

25510-A New Calculation For Designing Multi Layer Planar Spiral Inductors PDF

Uploaded by

kiband1Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

25510-A New Calculation For Designing Multi Layer Planar Spiral Inductors PDF

Uploaded by

kiband1Copyright:

Available Formats

By J on se n se r Z hao P u ls e

A new calculation for designing multilayer planar spiral inductors

A new, simple, And AccurAte expression lets you cAlculAte the coupling fActor between multilAyer pcb inductors.

lanar spiral inductors are less expensive than ei- depending on layout (Table 1). Figure 2 defines DIN (inner ther chip or coil inductors for PCB (printed-cir- diameter) and DOUT. A multilayer inductor creates mutual inductance, howcuit-board)-based designs. Accuracy in designing a spiral inductor is important because it is ever, so 3-D-magnetic-simulation software cannot simulate difficult to modify the inductor once you have a multilayer inductor. Even if it could, the process would take built it on the PCB. Some formulas are avail- a long time, and the results would be inconsistent. Therefore, able for calculating the spiral inductor for RF-IC applications you must use the following two equations for the coupling with inductance of less than 100 nH on a single-layer design. value, KC, to obtain the total inductor value with a mutual inductance: LTOTAL=L1+L22M, For the application of HPNA (Home and M=2KCL1L2. Phoneline Networking Alliance) or RFYou can obtain another simtelecom designs, which need inductances ple and accurate expression for of more than 10 H, no published paper or report accurately calculates spiral inthe inductance of a planar spiductors with a large value in multiple ral by approximating the sides layers. of the spirals using symmetriThree options exist for designing large cal current sheets of equivaplanar spiral inductors on a PCB: Inlent current densities (Refercrease the number of turns; increase the ence 1). Although the accuinner diameter, DIN; or add layers and racy of Equation 1 decreases increase the coupling between multilayas the ratio of space between ers. The first two options occupy more traces to the trace width inarea on the PCB, so the third option is creases, it exhibits a maximum the best way to accommodate a large inerror of 8% for a space less ductor when there is limited PCB area. than or equal to three times Multilayer planar spiral inductors of- figure 1 the traditional formula for calculating inductor the width. Note that designfer several advantages over other induc- size is accurate for single-layer planar spiral inductors ers typically build practical intors. They have stable inductance, for ex- but does not calculate the inductance of those that tegrated spiral inductors with ample, and, if the PCB has a fixed layout, employ multiple layers and connect with via holes. space less than or equal to the their inductance tolerance is less than width because smaller spacing 2%. Further, spiral inductors cost less than chip inductors and improves the interwinding magnetic coupling and reduces require a less complex manufacturing process, making them the area the spiral consumes. In PCB design, this practice is easier to manufacture with low yield loss. not a concern because the intertrace spacing is normally less The traditional formula for calculating inductor size is ac- than the trace width. curate for single-layer planar spiral inductors, but it does not Analysis of these equations and experimenting with large calculate the inductance for planar spiral inductors built on inductors shows that Equation 1 is accurate, and the increasmultilayers and connected with via holes (Figure 1). ing value of the inductor does not affect the accuracy of these You can calculate a single-layer inductors value using equations. The result shows an inductance close to the calEquation 1: culated value, with the difference at high frequency due to the actual distribution of parameters throughout the circuit (1) rather than the lumped-parameter analysis of the model (FigL=[(0N2DAVGC1)/2][ln(C2/)+C3+C42)], ure 3). Thus, you can use Equation 1 to calculate a large, where N is the number of turns; 0 is the vacuum permeabil- single-layer inductor. ity, 4107; is the fill ratio, (DOUTDIN)/(DOUT+DIN); DAVG Calculations for a multilayer coupled planar spiral inductor is the average diameter, (DIN+DOUT)/2; and C1C2 are factors are more complex than those for a single-layer spiral inductor.

JULY 29, 2010 | EDN 37

tAble 1 Layoutdependent coefficientS

Layout square hexagonal octagonal circle C1 1.27 1.09 1.07 1 C2 2.07 2.23 2.29 2.46 C3 0.18 0 0 0 C4 0.13 0.17 0.19 0.2

DIN DOUT

W S S W

DIN

tAble 2 inductor turnS

A 0.184 B 0.525 C 1.038 D 1.001

(a) W S (b)

DOUT

The coupling between the inductors on each layer is difficult to simulate because the coupling value depends on the number of turns of the inductor and the distance between the two layers. Experimenting over the range of inductor turns, N, with N equal to a 5- to 20-turns ratio, and the distance between the inductors on the two layers, X, with X equal to a 0.75- to 2-mm distance, yields Equation 2 to calculate the coupling factor: KC=[N2/(AX3+BX2+CX+D) (1.67N25.84N+65)0.64],

DIN S W DOUT DIN

DOUT

(2)

(c)

(d)

where X is the distance in millimeters between the inductors on the two layers and N is the number of inductor turns that Figure 2 defines. The inductor turns of both layers must be the same (Table 2). With the coupling factor from Equation 2 and the single planar-spiral-inductor calculation from Equation 1, you can figure the total inductance of a two-layer inductor by using the mutual-inductance formula (Reference 2). On a two-layer coupled inductor, you can calculate the total inductance with the following layout information: 15.75 turns, 0.127-mm (5-mil) width and trace

figure 2 the c1c4 factors depend on layout: square (a), hexagonal (b), octagonal (c), and circle (d).

spacing, 1.0922-mm (43-mil) DIN, and 0.75-mm interlayer distance. First, you must analyze the circular layout to find DOUT and DAVG to obtain the single-layer inductance, LS, and the coupling factor, KC: DOUT=DIN+2 W+(W+S)(2N1)=8.9972; DAVG=(DIN+DOUT)/2=5.0927; =(DIN+DOUT)/(DOUT+DIN)=0.7855; LS=[(N2DAVGC1)/2]

CH1 LS 10.01 H/REF 0H

0 52.772 H

113.359120598 MHz

COR

4 5 6 7

4.1 3.1 INDUCTANCE (H) 2.1 1.1 0.1 0.1 HLD IF BW 300 Hz POWER 0 dBm START 100 kHz NO. FREQUENCY 0 113.359120598 MHz 1 100 kHz 2 1 MHz 3 5 MHz 4 10 MHz 5 15 MHz 6 20 MHz 7 30 MHz SWP 12.04 SEC STOP 500 MHz VALUE 52.772 H 1.1618 H 1.1197 H 1.108 H 1.1071 H 1.1137 H 1.1267 H 1.1703 H

1 10 BANDWIDTH (MHz) MEASURED CALCULATED

100

figure 3 An analysis of the equations shows an inductance close to the calculated value.

figure 4 the measured inductors frequency response is close to the theoretical calculation to a frequency as high as 100 mhz.

38 EDN | JULY 29, 2010

tAble 3 four-Layer-Stack Structure

layer 1 layer 2 layer 3 layer 4 spiral inductor substrate spiral inductor substrate spiral inductor substrate spiral inductor 1 mil 34 mils 1 mil 34 mils 1 mil 34 mils 1 mil 0.025 mm 0.85 mm 0.025 mm 0.85 mm 0.025 mm 0.85 mm 0.025 mm

CH1 Q

20 U/REF 200 U

921.51 m 113.359120598 MHz

COR

HLD

6 7 4 5 0

SWP 12.04 SEC STOP 500 MHz VALUE 921.51 m 1.1373 m 10.032 m 31.196 m 45.67 m 55.195 m 61.729 m 71.491 m

(ln(C2/)+C3+C42)]=106H=1 H; KC=0.64. Per the mutual-inductance connection equations, the total inductance is L1+L2+2KC=L1L2=3.28 H. In a design with more than two layers, there are more coupling factors between any two layers. You can use the same method to obtain each coupling factor and then use the total inductance per the mutual-inductance connection formulas. You can also calculate a four-layer spiral inductor with 15.75 turns, a 5-mil-wide trace, a 5-mil trace spacing, and a 43-mil circular inner diameter. Table 3 shows the stack structure of the PCB. You must first calculate the single-layer inductance, LS, which is 1 H. It has six coupling factors: KC12, KC13, KC14, KC23, KC24, and KC34. KC12=KC23=KC34=0.618, KC13=KC24=0.459, and KC14=0.294. So the total inductance is: L1+L2+L3+L4+(2KC12+2KC13+2KC14+2KC23+2KC24+ 2KC34)L1=10.132 H. The four-layer inductor has a 10.1H inductance.

IF BW 300 Hz POWER 0 dBm START 100 kHz NO. FREQUENCY 0 113.359120598 MHz 1 100 kHz 2 1 MHz 3 5 MHz 4 10 MHz 5 15 MHz 6 20 MHz 7 30 MHz

figure 5 the self-resonant frequency is better than that of a chip inductor with the same value.

Several samples with different sizes and structures verify the new calculation and measure and compare samples. To perform the verification, you must first increase the size of the single-layer planar inductor and then increase the number of turns from four or five to 15. You must also increase the track width from 4 to 200 microns and increase DIN from 100 to 2400 microns. The inductance calculated using Equation 1 is 1.1 H. Figure 4 shows the measured inductor frequency

JULY 29, 2010 | EDN 39

CH1 LS

10.01 H/REF 0H

29.403 H

0

COR

40 MHz

4 56 7

HLD IF BW 300 Hz START 100 kHz NO. 0 1 2 3 4 5 6 7 POWER 0 dBm FREQUENCY 40 MHz 100 kHz 1 MHz 5 MHz 10 MHz 15 MHz 20 MHz 30 MHz SWP 12.04 SEC STOP 500 MHz VALUE 29.403 H 3.8144 H 3.7903 H 3.7677 H 3.8956 H 4.1822 H 4.6846 H 7.1989 H

figure 6 the frequency response for the spiral inductor is better than that of a chip inductor with the same value.

figure 8 you can build a fifth-order, lowpass filter with a twolayer, coupled spiral inductor.

CH2 S21 LOG 20 dB/REF 60 dB CH4 MEM LOG 5 dB/REF 15 dB * 5: 71.551 dB 5: 0.03330 dB 50 MHz CH2 MARKERS 1: .47690 dB 30 kHz 5 2: .40430 dB 2 MHz 3: .45610 dB 2.2 MHz 4: 67.072 dB 12 MHz

CH1 Q

5 U/REF 20 U

4 5 3

6 7

160.95 m 42.668537658 MHz

COR

3 2

2 1

IF BW 300 Hz POWER 0 dBm START 100 kHz NO. FREQUENCY 0 42.668537658 MHz 1 100 kHz 2 1 MHz 3 5 MHz 4 10 MHz 5 15 MHz 6 20 MHz 7 30 MHz

0 4

SWP 12.04 SEC STOP 500 MHz VALUE 160.95 m 2.0236 m 16.411 m 34.595 m 42.162 m 42.886 m 38.899 m 22.878 m PRM COR COR

3 2

START .030 MHz 2 INSERTION LOSS

STOP 100 MHz 4 RETURN LOSS

CH4 MARKERS 1: 30.965 dB 30 kHz 2: 23.042 dB 2 MHz 3: 21.310 dB 2.2 MHz 4: .14550 dB 12 MHz

figure 7 two-layer planar spiral inductors have better Q and self-resonant frequency than does a chip inductor.

figure 9 the performance of the filter matches the simulation result.

response, which is close to the theoretical calculation to a frequency as high as 100 MHz. The Q value and self-resonant frequency in figures 4 and 5 are better than that of the same-value chip inductor. Normally, the chip inductors Q value is only 15 to 20. To verify the coupling factor, you build two equally sized, 1.1-H planar spiral inductors on a two-layer PCB substrate with a thickness of 0.8 mm. The calculated inductor value using Equation 2 is 3.8 H. Figures 6 and 7 show the frequency response. The two-layer planar spiral inductors Q and self-resonant frequency are better than that of a chip inductor with the same value. Figure 8 shows a fifth-order lowpass filter with two-layer coupled planar spiral inductors using the new calculation for the design of this filter. The performance of the filter matches the simulation result and works for HPNA and other telecommunication applications (Figure 9). The simplicity and robustness of these calculations simplify circuit design and optimization applications, which you can incorporate into the computer-circuit model for spiral inductors.EDN

40 EDN | JULY 29, 2010

ACKNOWLEDGMENT The author would like to thank Homer Feng, KB Ong, Paul Doyle, Andrew Zhang, and Bino Zhu for their valuable input and technical support during this project. REFERENCES

rosa, edward b, calculation of the self-inductances of single-layer coils, Bulletin of the Bureau of Standards, Volume 2, no. 2, 1906, pg 161, http://bit.ly/9ypeex. 2 nilsson, James w, and susan A riedel, Electric Circuits, seventh edition, prentice hall, may 17, 2004, isbn 0131465929.

1

AuThORS biOGRAphy Jonsenser Zhao is a senior design engineer at the network division of Pulses Chinese development center, where he is responsible for transformer, filter, and splitter design. Zhao has a bachelors degree in electronics from the Air Force Missile College (Shaanxi, China). His interests include developing designs for telecommunications applications.

You might also like

- SIwave Training 2016 - Signal and Power Integrity Analysis For Complex PCBs and IC PackagesDocument153 pagesSIwave Training 2016 - Signal and Power Integrity Analysis For Complex PCBs and IC Packagesrey_hadesNo ratings yet

- Power Electronics Devices LectureDocument78 pagesPower Electronics Devices LectureM Waqar ZahidNo ratings yet

- DC-DC Part 6 DoubleDocument18 pagesDC-DC Part 6 DoubleDefne AktemizNo ratings yet

- DDR Routing GuidelinesDocument14 pagesDDR Routing GuidelinesNarayanan MayandiNo ratings yet

- 01050528Document12 pages01050528Mohanavelu SadasivamNo ratings yet

- LearnEMC - Magnetic-Field Coupling (Inductive Coupling)Document3 pagesLearnEMC - Magnetic-Field Coupling (Inductive Coupling)danitranoster8512No ratings yet

- Length Matching for High-Speed PairsDocument2 pagesLength Matching for High-Speed PairsNarayanan MayandiNo ratings yet

- An Introduction To S-ParametersDocument43 pagesAn Introduction To S-ParametersRajeev KumarNo ratings yet

- Ibis Behavioral Models Technical NoteDocument3 pagesIbis Behavioral Models Technical NoteAnonymous T9zQADFxZRNo ratings yet

- Time - Frequency Domain Representation of SignalsDocument9 pagesTime - Frequency Domain Representation of SignalsSuyog KulkarniNo ratings yet

- The Transmission-Line Modeling (TLM) Method in ElectromagneticsDocument132 pagesThe Transmission-Line Modeling (TLM) Method in ElectromagneticsRafael CoelhoNo ratings yet

- Precision Curvature-Compensated CMOS Bandgap ReferenceDocument10 pagesPrecision Curvature-Compensated CMOS Bandgap ReferenceAnonymous TPVfFif6TONo ratings yet

- Ammeter DesignDocument17 pagesAmmeter Designnord2500No ratings yet

- Online Documentation For Altium Products - ( (High Speed Design in Altium Designer) ) - AD - 2018-10-26Document27 pagesOnline Documentation For Altium Products - ( (High Speed Design in Altium Designer) ) - AD - 2018-10-26Marco I100% (1)

- High-Speed (MHZ) Series Resonant Converter (SRC)Document12 pagesHigh-Speed (MHZ) Series Resonant Converter (SRC)teomondoNo ratings yet

- FM - PM Demodulation - The Phase Lock LoopDocument5 pagesFM - PM Demodulation - The Phase Lock LoopSunit Kumar Sharma100% (1)

- Switch Mode Power Supplies: SPICE Simulations and Practical DesignsDocument9 pagesSwitch Mode Power Supplies: SPICE Simulations and Practical Designscms124dNo ratings yet

- Noise Sources of MOSFETDocument11 pagesNoise Sources of MOSFETDerunNo ratings yet

- Ibis Switch ModelingDocument122 pagesIbis Switch ModelingteomondoNo ratings yet

- A CMOS Bandgap Reference Circuit With Sub-1V OperationDocument5 pagesA CMOS Bandgap Reference Circuit With Sub-1V Operationbooky_mookyNo ratings yet

- Ece Ade Manual 500 CopiesDocument79 pagesEce Ade Manual 500 CopiesRajkumarNo ratings yet

- Sar Adc 65nm PHD PDFDocument87 pagesSar Adc 65nm PHD PDFLex LutherNo ratings yet

- Awr-Axiem - Understanding Grounding Concepts in em SimulatorsDocument11 pagesAwr-Axiem - Understanding Grounding Concepts in em Simulatorsagmnm1962No ratings yet

- Simulazioni RF With LTSpiceDocument38 pagesSimulazioni RF With LTSpiceCarloNo ratings yet

- State Space Averaging Model of Boost ConvDocument60 pagesState Space Averaging Model of Boost ConvBharti Thakur100% (1)

- 10ESL37 - Analog Electronics Lab ManualDocument69 pages10ESL37 - Analog Electronics Lab ManualVinita AgrawalNo ratings yet

- Ec8353electronicdevicesandcircuitsunit2 180711152109Document126 pagesEc8353electronicdevicesandcircuitsunit2 180711152109dhivyaNo ratings yet

- EE2207 Lab ManualDocument72 pagesEE2207 Lab ManualgowthamveluNo ratings yet

- Basic VLSI SlidesDocument91 pagesBasic VLSI SlidesDivya AhujaNo ratings yet

- LTspice 4 E2Document155 pagesLTspice 4 E2Ruud van TarunNo ratings yet

- Wave Shaping and Swiching CircuitsDocument3 pagesWave Shaping and Swiching Circuitskaran007_mNo ratings yet

- 9086 CMOS Analog Design Chapter 6Document24 pages9086 CMOS Analog Design Chapter 6Yogindr SinghNo ratings yet

- Layout 02Document38 pagesLayout 02Bulcea PaulNo ratings yet

- Microwave Imaging and Electromagnetic Inverse Scattering ProblemsDocument172 pagesMicrowave Imaging and Electromagnetic Inverse Scattering ProblemsChinaski BukowskiNo ratings yet

- Antenna Matching Within An EnclosureDocument5 pagesAntenna Matching Within An EnclosureNitin PatelNo ratings yet

- Alejandrino, Michael S. Bsee-3ADocument14 pagesAlejandrino, Michael S. Bsee-3AMichelle AlejandrinoNo ratings yet

- A New Low Voltage, High PSRR, Cmos Bandgap Voltage ReferenceDocument4 pagesA New Low Voltage, High PSRR, Cmos Bandgap Voltage ReferenceBodhayan PrasadNo ratings yet

- Chapter 7. Switched-Inductor Regulators With Design Insight and Intuition (Power IC Design)Document119 pagesChapter 7. Switched-Inductor Regulators With Design Insight and Intuition (Power IC Design)Minh Hai RungNo ratings yet

- Owner's Manual for 150-In-One Block Electronic Experiment KitDocument163 pagesOwner's Manual for 150-In-One Block Electronic Experiment KitpkrajniNo ratings yet

- Low Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsDocument11 pagesLow Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsIJAR JOURNALNo ratings yet

- Tia Eia 613Document19 pagesTia Eia 613NeatMarineNo ratings yet

- Design of Analog CMOS Integrated Circuits: (1st Edition)Document4 pagesDesign of Analog CMOS Integrated Circuits: (1st Edition)Himaja DasariNo ratings yet

- Class12 15 HSPICEDocument59 pagesClass12 15 HSPICEKavicharan MummaneniNo ratings yet

- TKBDocument134 pagesTKBVictor TolentinoNo ratings yet

- Discrete FET - PHEMT DevicesDocument65 pagesDiscrete FET - PHEMT DevicesNarasimha SunchuNo ratings yet

- Analog ElectronicsDocument390 pagesAnalog ElectronicsAnthony Robert XNo ratings yet

- Colour Television NTSC Carnt Wireless World 1961Document518 pagesColour Television NTSC Carnt Wireless World 1961Fredji82No ratings yet

- An32f PDFDocument12 pagesAn32f PDFPaulo MonteiroNo ratings yet

- Eca Lab ManualDocument78 pagesEca Lab ManualNageswariah.MNo ratings yet

- Electric Power Engineering Lecture NotesDocument209 pagesElectric Power Engineering Lecture NotesRaj Boda0% (1)

- Inductor Loss Calcs VishayDocument12 pagesInductor Loss Calcs VishayealbinNo ratings yet

- Chapter 7 Passive DevicesDocument72 pagesChapter 7 Passive DevicessvijiNo ratings yet

- Electrical Overstress (EOS): Devices, Circuits and SystemsFrom EverandElectrical Overstress (EOS): Devices, Circuits and SystemsNo ratings yet

- Digital Signal Processing Systems: Implementation Techniques: Advances in Theory and ApplicationsFrom EverandDigital Signal Processing Systems: Implementation Techniques: Advances in Theory and ApplicationsNo ratings yet

- High Efficiency RF and Microwave Solid State Power AmplifiersFrom EverandHigh Efficiency RF and Microwave Solid State Power AmplifiersRating: 1 out of 5 stars1/5 (1)

- A Review Paper On Smart Antenna For Mobile Communication IJERTCONV5IS23014Document2 pagesA Review Paper On Smart Antenna For Mobile Communication IJERTCONV5IS23014Sanjana RameshNo ratings yet

- Analysis and Testing of Shaft Current Measurement DevicesDocument48 pagesAnalysis and Testing of Shaft Current Measurement DevicesRigoberto UrrutiaNo ratings yet

- Repair Plasma TV GuideDocument30 pagesRepair Plasma TV GuideMecael Desuyo100% (4)

- Aerohive HiveManager centralized WLAN managementDocument2 pagesAerohive HiveManager centralized WLAN managementMichele BrunelliNo ratings yet

- ZTU-G800/ZTU-G810 UHF Wireless Tuner Module: External DC 10-16VDocument11 pagesZTU-G800/ZTU-G810 UHF Wireless Tuner Module: External DC 10-16VMitha Wahyu PangestiNo ratings yet

- WCDMA Refarming Solution: SVU, October 2007Document61 pagesWCDMA Refarming Solution: SVU, October 2007Anonymous g8YR8b9No ratings yet

- An7511 PDFDocument10 pagesAn7511 PDFVenancio GutierrezNo ratings yet

- Goubau - 1981 - in Memoriam Dr. George GoubauDocument1 pageGoubau - 1981 - in Memoriam Dr. George GoubauAhmed AbdelraheemNo ratings yet

- Multi-Rate OC-48/STM-16 LR-2/L-16.2 SFP DWDM Transceivers With Digital DiagnosticsDocument7 pagesMulti-Rate OC-48/STM-16 LR-2/L-16.2 SFP DWDM Transceivers With Digital DiagnosticsMaster22No ratings yet

- Eia 481 Carrier Tape Manufacturing StandardDocument31 pagesEia 481 Carrier Tape Manufacturing StandardSopyanThamrin100% (1)

- Test 1 2021 Sem2Document7 pagesTest 1 2021 Sem2Zahid ElectronNo ratings yet

- Chapter 1 - Pic16f887 OverviewDocument38 pagesChapter 1 - Pic16f887 OverviewTung NguyenNo ratings yet

- LNCT Group 1Document38 pagesLNCT Group 1Anonymous icFaZnMNo ratings yet

- Unit-5 EE3402 LIC (R-2021)Document84 pagesUnit-5 EE3402 LIC (R-2021)Jishnuraj KubandrarajNo ratings yet

- Horizontal Loop AntennaDocument3 pagesHorizontal Loop Antennagutentag.266No ratings yet

- Ansys Siwave Brochure 14.0Document12 pagesAnsys Siwave Brochure 14.0mohsenniayeshNo ratings yet

- Introduction to Erbium Doped Fiber Amplifier (EDFA) DesignDocument16 pagesIntroduction to Erbium Doped Fiber Amplifier (EDFA) DesignArifiana Satya NastitiNo ratings yet

- Basic Principles of Fiber Optic CommunicationDocument3 pagesBasic Principles of Fiber Optic CommunicationHumayra Anjumee100% (2)

- A Survey On Security For Mobile DevicesDocument26 pagesA Survey On Security For Mobile DevicesBijal PatelNo ratings yet

- Gojan School of Business and Technology Satellite Communication Important Questions Part-A UNIT-1Document3 pagesGojan School of Business and Technology Satellite Communication Important Questions Part-A UNIT-1Dharani KumarNo ratings yet

- Eurotherm 818p PDFDocument2 pagesEurotherm 818p PDFKris0% (1)

- Universal Collection of JNTU MaterialsDocument6 pagesUniversal Collection of JNTU MaterialsKrishna ReddyNo ratings yet

- TPC817Document10 pagesTPC817Felipe CostaNo ratings yet

- 3-Phase grid connected PV Inverter design simulationDocument9 pages3-Phase grid connected PV Inverter design simulationNguyen KhoaNo ratings yet

- 289206183 SID 409 B型 英文技术说明书 V1 42Document78 pages289206183 SID 409 B型 英文技术说明书 V1 42jayapalNo ratings yet

- Wireless Communication Electronics by Example: Robert SobotDocument391 pagesWireless Communication Electronics by Example: Robert Sobotzhoushuguang100% (1)

- ArmDocument32 pagesArmSaraschandraa NaiduNo ratings yet

- Basic 2G Parameter TrainingDocument18 pagesBasic 2G Parameter TrainingambroserfNo ratings yet

- RF Plan Tables iPASOLINKDocument31 pagesRF Plan Tables iPASOLINKEr Praveen ThakurNo ratings yet

- Transient in RC and RL CircuitsDocument10 pagesTransient in RC and RL CircuitsHenok BelaynehNo ratings yet