Professional Documents

Culture Documents

Nvidia Placement Paper

Uploaded by

Saurabh VermaOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Nvidia Placement Paper

Uploaded by

Saurabh VermaCopyright:

Available Formats

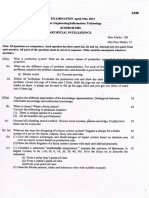

Nvidia Placement Paper there were 10 questions.. 4 X 3 marks *********** 1. room lighting..

room with 100 bulbs and switches.. 100 people goes in one by one. 1st person toggles all switches 2nd person toggles all switeches which r multiles of 2 ( 2,4,6..) and so on ( till 100th person toggling only 100th switch) once finished with all , which all bulbs r on.. 2. ieee single precision format for 1/5. form : 1 signbit, 8 bits for exponent, 23 bits for mantissa 3. elevator of 60 steps, one kid going up also climbs 15 steps during the upward motion. another kid runs up in the downward elevator and reaches top along with the first kid ?? how many steps are covered by second kid (answer = 45 + 60 = 105) 4. find the minimal exp for a > b, where a=a0a1 and b=b0b1. 5 X 6 marks.. ********** 5. find an fsm for any no which is divide by 3. 6. one c ++ class prog.. i don't remember it.. 7. one digital logic ckt problem. in signal , clk and out signal are given.. give the ckt.. 8. one cpu-cache hitting problem.. 9. shift register.. (b0b1 selection bits.. 00 - shift lft 01 - shift right 10 11 - toggles q1 q2 ( hint : uinversal shift register) 10th question (8 marks, true or false) total of 12 questions or so.. questions included on ASIC, HDL, TCP etc..

#############################################################################

Hi guys this is nVIDIA paper nVIDIA is a Graphics solutions ( HARDWARE ) provider and it also does Chipsets and chips for handheld devices for media processing. It has started a new design centre in Bangalore this year.

This is the paper of written test conducted by "nVIDIA" at IIT Kharagpur on AUG 10th 2004. Total 10 Qs ( 1st aptitude and remaining technical ) Questions carry variable marks. I could not remember the weightage . Duration: 1 Hr. 1. Question on clocks ---see R.S.Aggarwal ( 3m ) Between 4:00 pm and 5:00 pm at what time will the hours and minutes hand be 10 degrees apart for the first time.......???? ans: 4:20 p.m. 2.a)Data compression is used for information storage and transmission . you are to use encryption along with data compression. What will u do i)Data compression first and then encrypt the compressed data OR ii)encrypt the data and then compress the encrypted data Justify ur answer. ans : Compress the data and then encrypt the data. Reason : 1) Encryption time is proportional to data size. Compressed data size will be less than normal data size. 2) It also hinders cryptanalysis because there's less chance of repeating patterns and moreover, cryptanalysis is always harder when there is less ciphertext to chew on. b)Give Binary representation of -125.375 in fixed point 2C notation with 3 bits for fractional part and 8 bits for integer part. (4m)

3.Given a 4 bit binary number design a circuit that gives square of the number. 4.Given a 7 bit binary number design a circuit to find the number of 1s (Binary digit 1s) in the number using only Half Adders and Full Adders. 5.write a C functon IsLittleEndian() to return true if the machine stores LSB of a Multibyte number in Highest Address and false if it is the other way ( Iam not sure whether it is LSB in Highet addr or MSB in highest Address ,check what is LittleEndian and BigEndian ). 6.A question on FSM ( lengthy Question 8 lines ) I don't remember it . 7.A question on FF timing Two FFs with combo logic blocks in B/w FF1 and FF2 with different delays and combo block b/w o/p of 2nd FF and i/p of 1st FF (feedback). setup time ,hold time clock-to-Q delay were given a)with a SKEW of "DELTA" what will be the maximum clock frequency ( numerical values were given ). b)for a hold time of "HOLD" ns what will be the maximum SKEW allowed????

8.A question on FSM design ( it's a ARBITER problem Problem statement was given along with waveforms describing the function ) You are required to draw the FSM showing expressions for state changes and output. 9.a) A binary number is enormously large, so it is divided by a fixed number and the remainder is used.What is this called and why it is called so???? b)Give two advantages and one disadvantege of Latch based designs over register based designs. 10.This is a Q from Low power design ( circuits ) The technology used for a design is changed from 0.13 Um to 0.09 Um and VDD from 1.2v to 1.0 v. If Area of a chip is 81mm2 and Power consumed is 1w and maximum frequency is 500 MHz,in the earlier 0.13 Um technology, what will be the Power consumed in the new Technology of 0.09Um and Vdd of 1.0v? what will be the area of the chip? What will be the maximum frequency if the Power consumed is kept same ???

Out of 50 members ( attended written test) 8 were shortlisted for interview and 5 were selected for the job. Interview was cool. Basics of comp Architecture (those who said that they have learnt Compu arch were asked Qs on Compu arch ) , CMOS circuits ( transistor realization of Boolean functions), concepts of Pipelining, RC delay calculation, VERILOG ( simple no need to panic , just want to know whether you know verilog or not. --------------------------------------------------------------------------------------------------------------------to the bulbs question the answer is 10. the analysis is as follows; consider the factors of particular bulb excluding 1. first factor represents turning it OFF second factor represents turning it ON third factor represents turning it OFF fourth represents ON and so on. 1) bulb one is always ON. 2) bulb 2 factors are 2 only. so it is OFF forever. 3)bulb 3 factors are 3 so OFF forever 4) bulb 4 factors are 2 4. so it is ON forever. like wise if we continue we notice that bulbs which are perfect squares are ON. so bulbs which are ON at the end are 1 4 9 16 ...100. so total 10 bulbs. if i am wrong plzz correct me frnds.

You might also like

- NVIDIA interview and technical questions paper from 2004Document3 pagesNVIDIA interview and technical questions paper from 2004Yitzak ShamirNo ratings yet

- NVIDIA QuestionsDocument5 pagesNVIDIA QuestionsJibin P John0% (1)

- IntelDocument5 pagesIntelrAM50% (2)

- Interviews Question For Physical Design: Digital Design Interview QuestionsDocument44 pagesInterviews Question For Physical Design: Digital Design Interview QuestionsPavan Raj100% (1)

- Digital Design Interview Questions & AnswersDocument5 pagesDigital Design Interview Questions & AnswersSahil KhanNo ratings yet

- VLSI Interview QuestionsDocument112 pagesVLSI Interview QuestionsrAM100% (10)

- Qualcomm Interview ProcessDocument3 pagesQualcomm Interview ProcessPratikshaKhade0% (1)

- Digital Logic RTL & Verilog Interview Questions PreviewDocument34 pagesDigital Logic RTL & Verilog Interview Questions PreviewNhật Trung33% (6)

- Digital Design Interview QuestionsDocument2 pagesDigital Design Interview QuestionsSharif ShahadatNo ratings yet

- VLSI Interview QuestionsDocument70 pagesVLSI Interview QuestionsRohith Raj60% (5)

- VLSI Interview Questions With Answers - Ebook - VLSI Design Interview Questions With Answers - Ebook PDFDocument4 pagesVLSI Interview Questions With Answers - Ebook - VLSI Design Interview Questions With Answers - Ebook PDFnaveen silveri50% (4)

- CMOS Interview QuestionsDocument4 pagesCMOS Interview QuestionsLuca Reni100% (1)

- Vlsi FaqsDocument29 pagesVlsi Faqsanon-417212100% (4)

- VerilogDocument5 pagesVerilogChandru Ramaswamy100% (2)

- VLSI CMOS Interview Questions and AnswersDocument67 pagesVLSI CMOS Interview Questions and AnswersrAM95% (85)

- Questions On Logic SynthesisDocument11 pagesQuestions On Logic SynthesisrAM89% (9)

- VLSI Made Easy - VLSI Interview QuestionsDocument21 pagesVLSI Made Easy - VLSI Interview QuestionsAnupam DubeyNo ratings yet

- DG Iqs FullDocument126 pagesDG Iqs FullShyamala Venkataramani100% (2)

- AMD Previous Int QuestionsDocument9 pagesAMD Previous Int QuestionsMahmood VdnNo ratings yet

- Answer: Q1Document46 pagesAnswer: Q1amar2k904100% (3)

- VLSI Interview QuestionsDocument7 pagesVLSI Interview QuestionsVlsi GuruNo ratings yet

- PD Freshers - PD Interview Questions and Answers - Part 1 PDFDocument12 pagesPD Freshers - PD Interview Questions and Answers - Part 1 PDFsrajece0% (1)

- VLSI Test Principles and Architectures: Design for TestabilityFrom EverandVLSI Test Principles and Architectures: Design for TestabilityRating: 4.5 out of 5 stars4.5/5 (4)

- Formal Verification: An Essential Toolkit for Modern VLSI DesignFrom EverandFormal Verification: An Essential Toolkit for Modern VLSI DesignRating: 4 out of 5 stars4/5 (4)

- Find the performance impact of optimizing load-store instructions in a processorDocument2 pagesFind the performance impact of optimizing load-store instructions in a processormohitNo ratings yet

- What Are The Various Registers in 8085Document9 pagesWhat Are The Various Registers in 8085kunalsekhri123100% (1)

- What Are The Differences Between SIMULATION and SYNTHESISDocument12 pagesWhat Are The Differences Between SIMULATION and SYNTHESISiyanduraiNo ratings yet

- 7 Intel Paper - AlDocument11 pages7 Intel Paper - Alks25021995No ratings yet

- Questions 3Document28 pagesQuestions 3Anbarasan AnbuNo ratings yet

- Philips Placement Papers 1305641447Document16 pagesPhilips Placement Papers 1305641447Prateek Prabhash100% (1)

- Interview QuestionsDocument6 pagesInterview QuestionskiranvlsiNo ratings yet

- 2022A FE AM QuestionDocument27 pages2022A FE AM QuestionHtet MyatNo ratings yet

- Placement PapersDocument4 pagesPlacement PapersDivyam GargNo ratings yet

- MsDocument33 pagesMsmahimaNo ratings yet

- BOSCH Previous PapersDocument11 pagesBOSCH Previous Paperssubodh029No ratings yet

- VERIFONEDocument12 pagesVERIFONEsaumitra2No ratings yet

- 2013 April (Q)Document32 pages2013 April (Q)WachichaoOahcihawNo ratings yet

- Master SetDocument624 pagesMaster SetEr Lokesh MahorNo ratings yet

- Ilovepdf MergedDocument510 pagesIlovepdf MergedChristopher crNo ratings yet

- Intel Interview QuesDocument4 pagesIntel Interview QuesRobin Moore100% (1)

- Interview Questions-Digital Design PDFDocument9 pagesInterview Questions-Digital Design PDFradhakodirekka8732No ratings yet

- Verilog SV Interview QuestionsDocument21 pagesVerilog SV Interview QuestionsShakeel ScetNo ratings yet

- Interview QuestionsDocument23 pagesInterview QuestionsSumanth VarmaNo ratings yet

- Qualcomm QnsDocument9 pagesQualcomm QnsPrincy MurugesanNo ratings yet

- Exam #2 For Computer Networks (CIS 6930) SOLUTIONS : Problem #1Document4 pagesExam #2 For Computer Networks (CIS 6930) SOLUTIONS : Problem #1svahidsNo ratings yet

- AAI Previous Papers: Technical Questions from Electronics JE ExamsDocument14 pagesAAI Previous Papers: Technical Questions from Electronics JE ExamsSan DipNo ratings yet

- ECE 127 Homework 1: Moore's Law and Processor Design TrendsDocument2 pagesECE 127 Homework 1: Moore's Law and Processor Design TrendsRobin ScherbatskyNo ratings yet

- 2017A FE AM QuestionDocument30 pages2017A FE AM QuestionShah AlamNo ratings yet

- COBOL Matrix Addition ProgramDocument7 pagesCOBOL Matrix Addition ProgramNani ChowdaryNo ratings yet

- Cisco: Section 1 - Basic Digital SectionDocument3 pagesCisco: Section 1 - Basic Digital SectionboiroyNo ratings yet

- Interview QnsDocument5 pagesInterview Qnssaikirannani277No ratings yet

- UsefulDocument4 pagesUsefulSrikanth Raj KumarNo ratings yet

- Wipro SampleDocument8 pagesWipro SampleArghya GuhaNo ratings yet

- CS398 Exam 3, 2 Chance December 17th, 2012: Circle The Section That Attend (So We Can Hand Back Your Exam)Document7 pagesCS398 Exam 3, 2 Chance December 17th, 2012: Circle The Section That Attend (So We Can Hand Back Your Exam)vsNo ratings yet

- Exam #1 For Computer Networks SOLUTIONSDocument4 pagesExam #1 For Computer Networks SOLUTIONS87bbNo ratings yet

- Su 2011 Final SolDocument19 pagesSu 2011 Final SolmissionchocolateNo ratings yet

- IET DAVV 2014 ComDocument15 pagesIET DAVV 2014 Comjainam dudeNo ratings yet

- Digital System Design: Provided by Humayra JahanDocument5 pagesDigital System Design: Provided by Humayra JahanZabirNo ratings yet

- Instructions:: Q1. Answer The Following Questions: (Marks 10)Document3 pagesInstructions:: Q1. Answer The Following Questions: (Marks 10)Zoha MobinNo ratings yet

- CS211 Test 1 Solution S1 2022Document7 pagesCS211 Test 1 Solution S1 2022Jerold YangNo ratings yet

- Acquisition System For Smart Home Using LabVIEWDocument5 pagesAcquisition System For Smart Home Using LabVIEWDinh Truong TamNo ratings yet

- Self Cleaning NH4 N Modbus Instruction enDocument21 pagesSelf Cleaning NH4 N Modbus Instruction enkepyarNo ratings yet

- Introduction to Binary Numbers and Python BasicsDocument62 pagesIntroduction to Binary Numbers and Python BasicsChirag SoodNo ratings yet

- Lesson PlanDocument2 pagesLesson PlanOrlan LumanogNo ratings yet

- DB Sherlog CRX 052013 Eng PDFDocument4 pagesDB Sherlog CRX 052013 Eng PDFRuly FanuelNo ratings yet

- Memory and I/O Interfacing FundamentalsDocument14 pagesMemory and I/O Interfacing FundamentalsAKASH PALNo ratings yet

- Lecture 3Document39 pagesLecture 3Joseph AntoNo ratings yet

- User Manual of DYP-A01-V2.0: Waterproof Ultrasonic Distance Measuring ControllerDocument15 pagesUser Manual of DYP-A01-V2.0: Waterproof Ultrasonic Distance Measuring ControllerSantiago lealNo ratings yet

- Embedded System Design-NPTEL-NOTESDocument38 pagesEmbedded System Design-NPTEL-NOTESGulshan Upreti100% (1)

- Regent University College of Sci & Tech Mr. David Fiase Department of EngineeringDocument35 pagesRegent University College of Sci & Tech Mr. David Fiase Department of EngineeringKwameOpareNo ratings yet

- Design 4-Bit Binary Counter With Parallel Load Using Nanometric TechniqueDocument5 pagesDesign 4-Bit Binary Counter With Parallel Load Using Nanometric TechniqueRahul VermaNo ratings yet

- Number SystemDocument4 pagesNumber SystemJohn Mark MorallosNo ratings yet

- Teaching Guide: For Secondary ClassesDocument108 pagesTeaching Guide: For Secondary ClassesEMAAN TAYYAB Burki GirlsNo ratings yet

- Image Processing QBDocument29 pagesImage Processing QBsubramanyam62100% (1)

- History of ComputerDocument11 pagesHistory of ComputerBedul ParahNo ratings yet

- IEC 61850 Communication With GE Devices Rev1 - 01Document42 pagesIEC 61850 Communication With GE Devices Rev1 - 01Carlos Sulca NeiraNo ratings yet

- HV10 Serisi Klavuz V5.0Document67 pagesHV10 Serisi Klavuz V5.0daniel hughesNo ratings yet

- Computer ArchitectureDocument74 pagesComputer ArchitectureAkshat Singh100% (1)

- Networking Module 2Document18 pagesNetworking Module 2Augustus Ceasar Abo-aboNo ratings yet

- PLC Advanced Function Siemens PDFDocument114 pagesPLC Advanced Function Siemens PDFAlaa RamadanNo ratings yet

- Lecture 1 Introduction To DIP (10.1.19)Document54 pagesLecture 1 Introduction To DIP (10.1.19)Rajalakshmi MohandhossNo ratings yet

- Lm40 Hardware Monitor With Dual Thermal Diodes and Sensorpath BusDocument27 pagesLm40 Hardware Monitor With Dual Thermal Diodes and Sensorpath BusStuxnetNo ratings yet

- Ev Mc3301e1Document149 pagesEv Mc3301e1Md. Ameer HamjaNo ratings yet

- Nanovip Plus MemDocument11 pagesNanovip Plus MemDhrumil ModiNo ratings yet

- Chapter2PLC Hardware Components-2Document88 pagesChapter2PLC Hardware Components-2Fati AldNo ratings yet

- DI Module With RS485Document10 pagesDI Module With RS485Yasser RagabNo ratings yet

- BCD Code 1Document15 pagesBCD Code 1Ikah YuyuNo ratings yet

- Information Systems (Tc4) : Technician Diploma in AccountingDocument171 pagesInformation Systems (Tc4) : Technician Diploma in AccountingLucky Harvey BandaNo ratings yet

- MICROSOL XELL - CONITEL C300 SLAVE Config. Guide For DMTDocument32 pagesMICROSOL XELL - CONITEL C300 SLAVE Config. Guide For DMTIlaiyaa RajaNo ratings yet

- Graphics in Turbo C++Document5 pagesGraphics in Turbo C++DevN9100% (2)