Professional Documents

Culture Documents

Coded Ofdm Using VHDL

Uploaded by

Bibin Thomas MattaparampilOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Coded Ofdm Using VHDL

Uploaded by

Bibin Thomas MattaparampilCopyright:

Available Formats

International Journal of Computer Applications (0975 8887) Volume 5 No.

7, August 2010

Design of COFDM Transceiver Using VHDL

Hemant Kumar Sharma

Research Scholar C-DAC, Mohali

Sanjay P. Sood

HOD, ACS, HI & Electronics Division C-DAC, Mohali

Balwinder Singh

Design Engineer C-DAC, Mohali

ABSTRACT

OFDM is combined with channel coding scheme i.e. FEC (Forward Error Correction) called CODED OFDM or COFDM is especially suitable for high speed environment because it provides data transfer at higher speed with reliable transmission. Main focus of this paper is to design COFDM transceiver which operates with FEC, scrambling, block interleaver with conventional OFDM system to overcome the problem in wireless link i.e. ISI, ICI, fading etc. In this paper, COFDM transceiver designing details and simulation results are discussed after that COFDM modulator is compared with previous work which ensures present work is better than previous work. COFDM Transceiver is designed and synthesized using Xilinx Project Navigator XILINX ISE 9.1i and simulated using ModelSim 5.8c simulator.

results are described in section 5. Section 6 includes conclusion of this work and in section 7 contains the references.

2. COFDM SYSTEM MODEL

OFDM is a wireless technology patented in 1970 that turns on principle of transmitting data by dividing the data stream into multiple parallel bit stream. OFDM transmits the data by using a large number of narrow bandwidth carriers. These carriers are regularly spaced in frequency. The carriers are sent in such a way that the carriers are orthogonal, meaning that they do not cause interference to each other. Currently there are two principle 4G development technologies contending for attention: CDMA (Code Division Multiplexing) and OFDM. CDMA is well known standard and has been used for several years, but OFDM is relatively new technology which is being used by Nokia, Cisco, Lucent and Philips Semiconductor etc. OFDM with particular channel coding scheme or with error control coding called COFDM provides the higher data rate environment with removing the effect of frequency fading and reliable data rate transmission. Thus COFDM is adopted by many wireless standards like DAB, DSL, WLAN, IEEE 802.11 a, IEEE 802.11 g, IEEE 802.11 n etc [12]. With increasing the data rate in wireless communication system time of each transmission becomes shorter. But delay time due to the multi-path fading remains constant, because of this ISI, ICI becomes main problems. COFDM avoids these problems by splitting the channel into sub-channels and transmitting the data using sub-channels in such a way that data are transmitted orthogonally so that 50% bandwidth is saved than conventional system as shown in Figure 1. Figure 1(a) shows the simple conventional method in which the bandwidth used to transmit the signal is more than COFDM as shown in Figure 1(b). COFDM technique is another form of multi-carrier modulation which basic principles is transmission of data with reliable and at higher data rate by converting data bit into several parallel bit streams and each of these bit are modulated by each sub-carrier. COFDM signal can be presented as shown in Figure 2.

General Terms

Digital System Design, Wireless Communication, Data and information system

Keywords

OFDM, COFDM, FEC, Convolution Encoder, Viterbi Decoder

1. INTRODUCTION

In the field of wireless communication OFDM (Orthogonal Frequency Division Multiplexing) is the suitable candidate to overcome the problems like multi-path fading, ISI (Inter Symbol Interference), ICI (Inter Carrier Interference), low bit rate capacity, need higher power to transfer the data etc [3] [4]. With increasing data transfer rate, it is very important that data must be transmitted with carefully and reliable transmission should be take place in wireless link. So OFDM is combined with suitable channel coding scheme to perform reliable transmission, when OFDM is combined with channel coding scheme then it is called CODED OFDM or COFDM [3]. Coding scheme must be chosen for any system which satisfies requirements of high data rate as well as good error capability and according to complexity, suitable delay and desired coding gain for system. The aim of this work to show the compatibility of designing and implementing a COFDM transceiver on FPGA. In this work COFDM transmitter and receiver is designed using VHDL after that results are verified then COFDM modulator is compared with previous work which shows the present work provides better performance than previous work and present work utilize less number of devices than previous work. This work can be organized as: In section 2 COFDM system is explained, section 3 describes the significance of FEC with Interleaving, design details or implementation details is covered in section 4, then simulation

Figure 1 Transmission Techniques 11

International Journal of Computer Applications (0975 8887) Volume 5 No.7, August 2010

Data Input Scra mbler FEC

Encoder

Puunct urer

Interle aver

Constell ation Mapper

IFFT

(a)

(b) Desc ramb ler

Data Output FEC

Decoder

Figure 2 Spectra of (a) COFDM sub-channel and (b) COFDM signal COFDM signal generation is presented in Figure 3. To generate COFDM successfully the relationship between all the carriers must be carefully controlled to maintain the orthogonality of the carriers. For this reason, COFDM is generated by firstly choosing the spectrum required, based on the input data, and modulation scheme used. The spectrum which is desired is then converted back to its time domain signal using an IFFT. The FFT converts a cyclic time domain signal into its equivalent frequency spectrum. After performing OFDM function using IFFT & FFT, signal is send to COFDM receiver where the data transmitted through COFDM transmitter is received.

Depun cturer

DeInterlea ver

Constella tion Demappe r

FFT

Figure 4 Basic block of COFDM Transceiver

3. FEC WITH INTERLEAVING

Interleaving is a powerful technique that is used to perform burst error correction in which the bit errors occur sequentially in time and as groups [5]. Interleaving is used in digital communications systems to enhance the random error correcting capabilities of error correcting codes to the point that they can be effective in a burst noise environment [11]. The interleaver subsystem rearranges the encoded symbols over multiple code blocks as shown in Figure 5. FEC process with interleaving enhances the performance of system with reasonable cost of price and hardware. Figure 5 shows that data is first encoded through FEC encoder then data is sent to interleaver after mapped using particular modulating scheme then transmitted, at receiving side data is first de-mapped using same modulating scheme that employed at transmitter side then sent to de-interleaver which performs reverse operation of interleaver and rearranges the data then data is decoded using FEC decoder [10]. Interleaving techniques are traditionally used to enhance the quality of digital transmission over the bursty radio channel. This is usually accomplished by scrambling successive symbols of the transmitted sequence into different time slots. A channel is considered fully interleaved when consecutive symbols of the received sequence appear to be independent not affect by the same burst error.

Figure 3 COFDM Generation Basic block of COFDM transmitter and receiver is shown in Figure 4 which consists of scrambler, convolution encoder as FEC encoder, puncturer, block interleaver, QPSK scheme as constellation mapper and IFFT (Inverse Fast Fourier Transform) at transmission side. While COFDM receiver includes FFT (Fast Fourier Transform), Constellation de-mapper, de-interleaver, depuncturer, FEC decoder and descrambler. FEC encoder and FEC decoder performs FEC process at transmitter and receiver side. An IFFT and FFT block performs OFDM process to map the QPSK value into OFDM symbol so that bandwidth forInput transmission of signals is saved. The COFDM transmitter block is divided into several parts with each block functioning differently and this is to ensure that the Output system works effectively. The Scrambler serializes input data and then performs an exclusive-OR operation on the data [6]. Data is then encoded by the convolution encoder which is used as FEC encoder to perform FEC scheme or to encode the data and passes through puncturer. Then interleaver rearranges the bit sequence and passed through mapper after it QPSK value bit is mapped into OFDM symbols using IFFT. IFFT is performed to represent the signal or data into time domain because when data is transmitted in analog form through transmitter and represented in time domain.

Encoder

Interleaver

Mapper

Decoder

De-interleaver

De-mapper

Figure 5 FEC with Interleaving FEC coding gives the best performance when it is used with interleaving with respect to the BER (Bit Error Rate), frequency diversity, fading environment, multi-path environment etc [2]. Due to the bursty nature of many radio interference sources and the characteristics of the demodulator, it is more likely that 12

International Journal of Computer Applications (0975 8887) Volume 5 No.7, August 2010 erroneous bits will clump together. To combat this problem interleaving of the coded data is performed after encoding in the transmitter and de-interleaving before decoding in the receiver. The main objective of interleaving is to ensure that adjacent symbols in the coded sequence are spaced out in the transmitted sequence, so that any clumps of bit errors in the received sequence are spread out more uniformly by the de-interleaver, letting the decoder work under optimum conditions [11]. Then comes to the constellation mapper which is used to mapped the interleaved bits into QPSK value. The mapper converts the input data into complexed valued constellation points, according to a given constellation. Some typical constellations for wireless applications are BPSK, QPSK and QAM [14], in this work QPSK mapper is used at transmitter side. At receiver side QPSK demapper is used as QPSK mapper is used at transmitter side. The constellation graph of QPSK can be shown in Figure 7 and carrier phase shift corresponding to various input bits can be shown in Table 1.

4. IMPLEMENTATION DETAILS

The basic design methodology to implement the COFDM transmitter and receiver is the divide and conquer scheme in which first COFDM transceiver is divided into two main parts: COFDM Transmitter and COFDM Receiver. After it COFDM transmitter block is further divided into sub-blocks and same in case of COFDM receiver is performed. Then sub-blocks of COFDM transmitter and receiver is designed and results are verified. After verification of each blocks result blocks are merged then COFDM transmitter and COFDM receiver are assembled which called COFDM Transceiver and then result of COFDM Transceiver is verified. Whole design is designed using Xilinx Project Navigator XILINX ISE 9.1i and result is verified using ModelSim XE 5.8c simulator. The device selected for this work is Virtex-5 XC5vlx30-3ff324. Basic functioning and main designing issues of each block is discussed in next. First block of COFDM transmitter is scrambler which serializes the input data bits and used to generate the random number of sequence and work as pseudo noise sequence (PN) generator. The PN generator has applications in communications in CDMA, system testing etc [6]. In this work M-length sequence generator is used for PAPR reduction and easiest way to generate bits. Descrambler is used to perform just reverse operation of scrambler at receiver side. Then data is encoded using convolution encoder which is used as FEC encoder to perform FEC process as shown in Figure 6. In this work convolution encoder of code rate and constraint length L=3 is used to encode the data stream generated by scrambler. Viterbi decoder is used as FEC decoder at receiver side to decode bit streams. This decoder is based on viterbi algorithm in which the possible received bit sequence form a tree structure and the viterbi tracks likely paths through the tree structure [7] [8]. After this data is punctured and rearranged using interleaver, in this work block interleaver is used to remove burst type errors and bit type errors. An Interleaver spreads the scrambled data in some deterministic manner. Interleaving is a process of rearranging the data symbols so that burst error can be overcome and corrected by means of FEC which is most effective technique for it. At receiving side reverse operation is performed using depuncturer and de-interleaver to recover the data. Data input

Figure 7 QPSK constellation graph [14] Table 1. Carrier Phase Shifts corresponding to various input bits Information bits 11 01 00 10 Phase change

/4

3/4

-3/4 -/4

To design FFT/IFFT DIT (Decimation in Time) radix-2 approach is used. FFT transforms the signals in time domain to frequency domain. In 1973 it was discovered that FFT could be used in multi carrier systems like OFDM. The equation can be written as follows

(1) The quantity WNnk is defined as below (2) This factor also called twiddle factor is calculated and put in a table in order to make the computation easier and can run simultaneously. The twiddle factor table is depending on the number of points used, here 8-point DIT radix-2 approach is used. During the computation of IFFT, the factor does not need to be recalculated since it can refer to the twiddle factor table thus it U1save time since calculation is done concurrently. IFFT is defined as the equation given below

1

1

2

1

3

1

U2

(3)

Figure 6 Convolution Encoder [7] 13

International Journal of Computer Applications (0975 8887) Volume 5 No.7, August 2010 A lot of devices are utilized by IFFT/FFT block than any other block. So design the FFT/IFFT block with minimum device utilization summary is main challenge.

5. SIMULATION RESULTS

COFDM Transceiver system is designed using VHDL and synthesized using Xilinx Projector navigator XILINX ISE 9.1i. Results are verified using ModelSim XE 5.8c simulator. The design is mapped on Virtex-5 XC5vlx30-3ff324. Internal RTL view of COFDM Transmitter, COFDM Receiver and COFDM Transceiver can be shown in Figure 8, Figure 9 and Figure 10 respectively.

Figure 10 Internal RTL View of COFDM Transceiver Figure 8 and Figure 9 shows the internal RTL view of COFDM transmitter and receiver which shows the combination of all blocks which are transmitter or receiver side respectively. In Figure 10 internal view of COFDM transceiver is shown which shows the combination of COFDM transmitter, COFDM receiver and OFDM blocks. Simulation results of COFDM transceiver is shown in Figure 11.

Figure 8 Internal RTL View of COFDM Transmitter

Figure 11 Simulation result of COFDM Transceiver Simulation results verified that the transceiver would perform with suitably low bit error for the full range of coding and modulation schemes and for variation of all the channel impairments. VHDL functional verification confirmed that the HDL design exhibited good performance. Figure 9 Internal RTL View of COFDM Receiver

14

International Journal of Computer Applications (0975 8887) Volume 5 No.7, August 2010

6. CONCLUSION

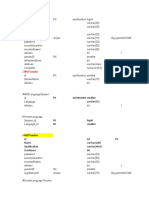

The main focus of this work is to shows the capability of designing and simulating COFDM system which includes OFDM integrated with FEC technique. This works main emphasis was on designing and simulation of synthesizable VHDL code of the COFDM transceiver using Xilinxs ISE 9.1i and simulated using ModelSim XE 5.8c simulator. Device Utilization summary of COFDM Transceiver is given in Table 2. Table 3 shows the total memory used by COFDM transceiver system. Resource Utilization of COFDM modulator is compared with previous work in Table 4 and results shows the present design utilizes the less number of devices. Table 2. Device Utilization Summary of COFDM Transceiver Logic Utilization Number of Slice Registers Number of fully used Bit Slices Number of bonded IOBs Number BUFG/BUFGCTLRs Number of DSP48Es of Used 9263 8191 9 17 24 Available 19200 61795 220 32 32 Utilization 48% 13% 4 53% 75%

devices to perform better than previous work. The timing analysis of COFDM Transceiver is presented as below Minimum period: 2.451ns (Maximum Frequency: 407.914MHz) Minimum input arrival time before clock: 2.056ns Maximum output required time after clock: 2.505ns Maximum combinational path delay: No path found

7. REFERENCES

[1] S. B Weinstein and P.M. Ebert, Data Transmission by Frequency Division Multiplexing Using the Discrete Fourier Transform, IEEE Transactions on Communication Technology, vol. com-19, pp. 628-634, October 1971. [2] S.A. Hanna, Convolution Interleaving for digital communications, 2nd International Conference on Universal Personal Communications: Gateway to 21st century, vol.1, pp. 443-447, 1993. [3] William Y. Zou and Yiyan Wu, COFDM: an overview, IEEE Transactions on broadcasting, vol.41, no.1, pp. 1-8, March 1995. [4] Neil Weste and David J. Skellern, VLSI for OFDM, IEEE Magazine on Communications, pp. 127-131, October 1998. [5] A.L.Intini, Orthogonal Frequency Division Multiplexing for Wireless Networks, Report, Standard IEEE 802.11 a, University of California, Santa Barbara, Dec. 2000. [6] Simon Haykin, Communication Systems, Jhon Wiley & Sons, Inc., 4th Edition, ISBN 0- 471-17869-1, 2001 [7] William Stalings, Wireless Communications and Networking, Pearson Education, Second Edition, 2002. [8] J.S.Reeve and K. Amarasinghe, A FPGA Implementation of a parallel viterbi decoder for a block cyclic and convolution codes, IEEE International Conference on Communications, vol. 5, pp. 2596-2599, 2004. [9] Joaquin Gracia and Rene Cumplido, On the design of an FPGA-based OFDM modulator for IEEE 802.11a, 2 nd International conference on Electrical and Electronics Engineering (ICEEE) and XI conference on Electrical Engineering (CIE), pp.114-117, Sep. 2005. [10] Jae-Kwon Lee, Jeong-Sang Park and Jin-Up Kim, A convolution coding scheme for PAR reduction in WLANOFDM system, IEEE International Conference on Intelligent Pervasive Computing, pp. 98-100, 2007. [11] Robin Hoel, FEC implementation, Texas Instruments, Design note DN504, 2007. [12] Ahmed Sghaier, Shawki Areibi and Bob Dony, A pipelined implementation of OFDM transmission on reconfigurable platforms, IEEE Canadian conference on Electrical and Computer Engineering, pp. 801-804, May 2008. [13] Bonghyunk Park, Jaeho Lee, Haewon Jung, Seongsu Park and Hyeong Ho Lee, Simulation results for FEC in 802.16 OFDM system, Report by IEEE 802.16 Broadband wireless access working group, IEEE 802.16abc-01/52, Nov 2001. [14] Intuitive guide to Principles of Communications, copyright 2002 Charan Langton, revised Dec 2005. www.complextoreal.com.

Table 3 Total Memory Used by COFDM Transceiver Total Memory Used 196572 Kb

Table 4 Comparison of Device Utilization Summary with previous work Logic Utilization No. of Slices No. of slices Flip Flop No. of 4 i/p LUTs Bonded IOB No. of GCLKS 782 518 1 2814 29 1 1241 2353 Present Work 754 Previous Work [9] 1678

COFDM Modulator is compare with previous work which shows the present work utilize the less number of devices than previous work. COFDM modulator design is targeted on Vertex 2. Area, power, cost is the main constraints to design any system. This works results shows that the presnt design utilizes less number of

15

You might also like

- Implementation of The OFDM Physical Layer Using FpgaDocument7 pagesImplementation of The OFDM Physical Layer Using FpgaĐỗ Hữu ToànNo ratings yet

- MIMO-OFDM High Data Rate Wireless System Using V-BLAST MethodDocument9 pagesMIMO-OFDM High Data Rate Wireless System Using V-BLAST MethodInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- OFDM in VerilogDocument6 pagesOFDM in VerilogMarwan AhmedNo ratings yet

- Design and Implementation of OFDM Trans-Receiver For IEEE 802.11 (WLAN)Document13 pagesDesign and Implementation of OFDM Trans-Receiver For IEEE 802.11 (WLAN)IJMERNo ratings yet

- A Novel Implementation of OFDM Using FPGA: M.A. Mohamed, A.S. Samarah, M.I. Fath AllahDocument6 pagesA Novel Implementation of OFDM Using FPGA: M.A. Mohamed, A.S. Samarah, M.I. Fath Allahtsk4b7No ratings yet

- Bit Error Rate Evaluation of IEEE 802.16 in OFDM SystemDocument4 pagesBit Error Rate Evaluation of IEEE 802.16 in OFDM Systemabhi_rules08No ratings yet

- Implementation of OFDM Transmitter and Receiver Using FPGA: Nasreen Mev, Brig. R.M. KhaireDocument4 pagesImplementation of OFDM Transmitter and Receiver Using FPGA: Nasreen Mev, Brig. R.M. Khaireankita6298No ratings yet

- A Study and Survey of OFDM Versus COFDMDocument4 pagesA Study and Survey of OFDM Versus COFDMahmedNo ratings yet

- BER Analysis of MIMO-OFDMDocument10 pagesBER Analysis of MIMO-OFDMAbhijeet KumarNo ratings yet

- Implementation and Performance Evaluation of OFDM System in Diverse Transmission Channel Using SimulinkDocument7 pagesImplementation and Performance Evaluation of OFDM System in Diverse Transmission Channel Using SimulinkAbdallah ToolmakerNo ratings yet

- Design and Simulation of COFDM For High PDFDocument7 pagesDesign and Simulation of COFDM For High PDFZain Alabeeden AlarejiNo ratings yet

- Project Task ReportDocument7 pagesProject Task ReportAfiq AbidinNo ratings yet

- Comparison of DCT and Wavelet Based Ofdm System Working in 60 GHZ BandDocument10 pagesComparison of DCT and Wavelet Based Ofdm System Working in 60 GHZ Bandsachin10dulkarNo ratings yet

- 1Document5 pages1sandeshwari yadavNo ratings yet

- Chapter-1: 1.1. Wireless Communication SystemsDocument28 pagesChapter-1: 1.1. Wireless Communication Systemskarthick_mariner92No ratings yet

- Project Report On Broadband MIMO-OFDM Wireless CommunicationsDocument10 pagesProject Report On Broadband MIMO-OFDM Wireless Communicationsanon_70493563No ratings yet

- OFDM Modulation Study For A Radio-over-Fiber System For Wireless LAN (IEEE 802.11a)Document5 pagesOFDM Modulation Study For A Radio-over-Fiber System For Wireless LAN (IEEE 802.11a)Muneeb Raees MalikNo ratings yet

- Project 121Document4 pagesProject 121Kishan NandakumarNo ratings yet

- Implementing OFDM Using SimulinkDocument8 pagesImplementing OFDM Using SimulinkDavid Solomon Raju YellampalliNo ratings yet

- A Review On OFDM: Concept, Scope & Its Applications: Manushree Bhardwaj, Arun Gangwar, Devendra SoniDocument5 pagesA Review On OFDM: Concept, Scope & Its Applications: Manushree Bhardwaj, Arun Gangwar, Devendra SonipankajmudgilNo ratings yet

- Efficient Model For OFDM Based IEEE 802.11 Receiver With Autocorrelation Technique and CORDIC AlgorithmDocument8 pagesEfficient Model For OFDM Based IEEE 802.11 Receiver With Autocorrelation Technique and CORDIC AlgorithmInternational Journal of computational Engineering research (IJCER)No ratings yet

- Report Project: Digital CommunicationDocument17 pagesReport Project: Digital CommunicationHoang AnhNo ratings yet

- GOYANI - A Review - Performance Comparison of Conventional and Wavelet Based OFDM SystemDocument4 pagesGOYANI - A Review - Performance Comparison of Conventional and Wavelet Based OFDM SystemAnonymous PsEz5kGVaeNo ratings yet

- Project Report On Broadband MIMO-OFDM Wireless CommunicationsDocument10 pagesProject Report On Broadband MIMO-OFDM Wireless CommunicationsPreetam PolakiNo ratings yet

- Ofdm Basics For Wirless Communications: AbstractDocument11 pagesOfdm Basics For Wirless Communications: AbstractRaji SharmiNo ratings yet

- Performance Analysis of MIMO-OFDM System Using QOSTBC Code Structure For M-QAMDocument12 pagesPerformance Analysis of MIMO-OFDM System Using QOSTBC Code Structure For M-QAMNoha HassanNo ratings yet

- 1.12 Mitigation of Narrow Band and Broadband FadingDocument11 pages1.12 Mitigation of Narrow Band and Broadband FadingchristienaNo ratings yet

- ECE - MIMO-An Evolution - Abdul RashidDocument6 pagesECE - MIMO-An Evolution - Abdul RashidTJPRC PublicationsNo ratings yet

- OFDM Simulator Using MATLAB: International Journal of Emerging Technology and Advanced EngineeringDocument4 pagesOFDM Simulator Using MATLAB: International Journal of Emerging Technology and Advanced Engineeringhungpm2013No ratings yet

- Researchpaper OFDM Modulator For Wireless LAN WLAN StandardDocument5 pagesResearchpaper OFDM Modulator For Wireless LAN WLAN Standardtsk4b7No ratings yet

- Design of OFDM Reciever: ISSN 2319-9725Document0 pagesDesign of OFDM Reciever: ISSN 2319-9725ohenri100No ratings yet

- Analysis of Wavelet Based OFDM SystemDocument8 pagesAnalysis of Wavelet Based OFDM Systemhk_sonuNo ratings yet

- Performance of Linear Block Coded OFDM System in Different ChannelsDocument7 pagesPerformance of Linear Block Coded OFDM System in Different Channelsnamhoa02No ratings yet

- Performance Comparison of Wavelet Based and Conventional OFDM Systems - A ReviewDocument4 pagesPerformance Comparison of Wavelet Based and Conventional OFDM Systems - A ReviewkiaraNo ratings yet

- Full Conference Paper1Document6 pagesFull Conference Paper1karthick_mariner92No ratings yet

- بحث 5Document6 pagesبحث 5hayderNo ratings yet

- Project Report 359Document12 pagesProject Report 359Sayeed Habeeb100% (1)

- Interleaved Orthogonal Frequency Division Multiplexing (IOFDM) SystemDocument11 pagesInterleaved Orthogonal Frequency Division Multiplexing (IOFDM) SystemAliAlissNo ratings yet

- BER of OFDM System Using Concatenated Forward Error Correcting Codes (FEC) Over Nakagami-M Fading ChannelDocument5 pagesBER of OFDM System Using Concatenated Forward Error Correcting Codes (FEC) Over Nakagami-M Fading Channelseventhsensegroup100% (1)

- OFDM Bhattacharya2017Document6 pagesOFDM Bhattacharya2017Syed Muneeb Ur RahmanNo ratings yet

- 1 PBDocument9 pages1 PBانا انت انت اناNo ratings yet

- Transmission of Voice Signal: BER Performance Analysis of Different FEC Schemes Based OFDM System Over Various ChannelsDocument12 pagesTransmission of Voice Signal: BER Performance Analysis of Different FEC Schemes Based OFDM System Over Various ChannelsAwais AhmedNo ratings yet

- An Experimental Study To Reduce The Effect of ICI in OFDM Based WLAN SystemDocument4 pagesAn Experimental Study To Reduce The Effect of ICI in OFDM Based WLAN SystemSandeep Kaur BhullarNo ratings yet

- Universal Filtered Multicarrier For 5GDocument5 pagesUniversal Filtered Multicarrier For 5GfatahNo ratings yet

- Master ThesisDocument80 pagesMaster ThesisRichard PottsNo ratings yet

- 5 Ofdm: 5.1 Overview About An OFDM SystemDocument9 pages5 Ofdm: 5.1 Overview About An OFDM SystemThehieu DangNo ratings yet

- Fpga Implementation of Ofdm Modem: Asst. Prof, Department of ECE, DBIT, Mysore Road, Bangalore-560074Document6 pagesFpga Implementation of Ofdm Modem: Asst. Prof, Department of ECE, DBIT, Mysore Road, Bangalore-560074lambanaveenNo ratings yet

- Introduction To OpdmDocument21 pagesIntroduction To OpdmEWUNETU TEKEBANo ratings yet

- Performance Evaluation of Wimax Physical Layer: Department of Electronics &communication, Sit, Tumkur, Karnataka, IndiaDocument4 pagesPerformance Evaluation of Wimax Physical Layer: Department of Electronics &communication, Sit, Tumkur, Karnataka, IndiaMannath SungarNo ratings yet

- Papr Reduction and Bit Error Rate Evaluation in Ofdm System Using Hybrid TechniquesDocument19 pagesPapr Reduction and Bit Error Rate Evaluation in Ofdm System Using Hybrid TechniquesijansjournalNo ratings yet

- Wireless and CELLULAR COMMUNICATION (18EC81) Module-4Document37 pagesWireless and CELLULAR COMMUNICATION (18EC81) Module-4Vishwanath DesaigoudarNo ratings yet

- Equalization On-Channel Repeater For Terrestrial Digital Multimedia Broadcasting SystemDocument9 pagesEqualization On-Channel Repeater For Terrestrial Digital Multimedia Broadcasting SystemAnusha ManiNo ratings yet

- Comparative Analysis of Ber Performance of DWT Based Ofdm System With Conventional FFT Based Ofdm SystemDocument6 pagesComparative Analysis of Ber Performance of DWT Based Ofdm System With Conventional FFT Based Ofdm Systemhk_sonuNo ratings yet

- Spectrum Analysis of OFDM Versus FBMC in 5G Mobile CommunicationsDocument8 pagesSpectrum Analysis of OFDM Versus FBMC in 5G Mobile CommunicationsTELKOMNIKANo ratings yet

- OFDM: High Speed Wireless CommunicationDocument57 pagesOFDM: High Speed Wireless CommunicationPankaj Pandey50% (2)

- Design of Proposed STBC-MC-DS - WIMAX Systems Based On DWT and Phase MatrixDocument10 pagesDesign of Proposed STBC-MC-DS - WIMAX Systems Based On DWT and Phase MatrixJournal of TelecommunicationsNo ratings yet

- Indoor Radio Planning: A Practical Guide for 2G, 3G and 4GFrom EverandIndoor Radio Planning: A Practical Guide for 2G, 3G and 4GRating: 5 out of 5 stars5/5 (1)

- Introduction to Mobile Network Engineering: GSM, 3G-WCDMA, LTE and the Road to 5GFrom EverandIntroduction to Mobile Network Engineering: GSM, 3G-WCDMA, LTE and the Road to 5GNo ratings yet

- Binder1 - Efic - Edit - 4 - Buku MKI Bhs Inggris UAD-2019Document116 pagesBinder1 - Efic - Edit - 4 - Buku MKI Bhs Inggris UAD-2019Arsefti melda100% (1)

- Jan Scholten Repertory of The Elements 5994eceb1723ddd169543dffDocument3 pagesJan Scholten Repertory of The Elements 5994eceb1723ddd169543dffUsman AnsariNo ratings yet

- Therigatha Pali EnglishDocument191 pagesTherigatha Pali EnglishAtma DevaNo ratings yet

- Thanksgiving Mass - Epong EdmundDocument3 pagesThanksgiving Mass - Epong EdmundHenry KaweesaNo ratings yet

- How To Write Minutes (Taken From OCR Level 3 Book)Document3 pagesHow To Write Minutes (Taken From OCR Level 3 Book)kr004k5356No ratings yet

- Balvatika, CL 1 Txtbooks & Jadui PitaraDocument8 pagesBalvatika, CL 1 Txtbooks & Jadui PitararajNo ratings yet

- Python Programming Language Individual Assignment Malaysian Bank Loan Management SystemDocument51 pagesPython Programming Language Individual Assignment Malaysian Bank Loan Management SystemD Nes GiriNo ratings yet

- Virtual Class ManagementDocument10 pagesVirtual Class ManagementGaurang MakwanaNo ratings yet

- Cambridge Global English 3 WBDocument118 pagesCambridge Global English 3 WBHan E-Books100% (4)

- Table of ContentDocument18 pagesTable of ContentThiện TrầnNo ratings yet

- Astpp FreeswitchDocument123 pagesAstpp Freeswitchaldo100% (2)

- K L University Freshman Engineering Department: A Project Based Lab Report On Divisibility RulesDocument19 pagesK L University Freshman Engineering Department: A Project Based Lab Report On Divisibility RulesMahima ChowdaryNo ratings yet

- Adjective or Adverb Worksheet With Grammar ExplanationDocument2 pagesAdjective or Adverb Worksheet With Grammar Explanationluu dinhNo ratings yet

- Basic English GrammarDocument22 pagesBasic English GrammarRani Purnama SariNo ratings yet

- Guess Bible CharacterDocument40 pagesGuess Bible CharacterBlibli EulishNo ratings yet

- Tugas Bahasa Inggris PidatoDocument3 pagesTugas Bahasa Inggris PidatoBagas Rizky PratamaNo ratings yet

- Installations OMSI 2Document3 pagesInstallations OMSI 2KapputNo ratings yet

- Past Tense - DeltaDocument8 pagesPast Tense - DeltaCareema ChoongNo ratings yet

- Dap An Chi Tiet Chuyen Bac NinhDocument18 pagesDap An Chi Tiet Chuyen Bac Ninhluong tranNo ratings yet

- Bits and Bytes - Lesson 2Document20 pagesBits and Bytes - Lesson 2miguelteixeiramaNo ratings yet

- Art Essence DebateDocument29 pagesArt Essence DebateasskelaNo ratings yet

- 2.7.2 Lab - Configure Single Area Ospfv2 EditadoDocument4 pages2.7.2 Lab - Configure Single Area Ospfv2 EditadoMaría ArmijosNo ratings yet

- Translation Evaluation - A State of The Art Survey: Alina Secară Leeds UniversityDocument20 pagesTranslation Evaluation - A State of The Art Survey: Alina Secară Leeds UniversityVinoth Ur FriendNo ratings yet

- General ReasoningDocument202 pagesGeneral Reasoningshikha sumanNo ratings yet

- Marie's 7th Birthday BashDocument3 pagesMarie's 7th Birthday BashJenny MercadoNo ratings yet

- Belief Systems and Their Inluence On Business Practices: Grade 12Document11 pagesBelief Systems and Their Inluence On Business Practices: Grade 12Joan Marie SalayogNo ratings yet

- Create A Mail ProfileDocument22 pagesCreate A Mail Profilesridhar_patojuNo ratings yet

- m2500 Modbus Memory Map Uk PDFDocument7 pagesm2500 Modbus Memory Map Uk PDFJandfor Tansfg ErrottNo ratings yet

- Cambridge IGCSE™: Biology 0610/62Document10 pagesCambridge IGCSE™: Biology 0610/62manar mohamedNo ratings yet