Professional Documents

Culture Documents

ADC

Uploaded by

madhavi1992Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ADC

Uploaded by

madhavi1992Copyright:

Available Formats

2008

IIT KHARAGPUR BITTU SARKAR

[ANALOG TO DIGITAL CONVERTER]

This is a brief overview of the built-in Analog to Digital Converter (ADC) of ATMEGA16 microcontroller produced by ATMEL.

ANALOG TO DIGITAL CONVERTER June 10, 2008

Introduction at a Glance

8 Single-ended Channels 7 Differential Channels in TQFP Package Only 2 Differential Channels with Programmable Gain at x1, x10, or x200

Important Points

The ADC has a separate analog supply voltage pin, AVCC. AVCC must not differ more than 0.3 V from VCC. The single-ended voltage inputs refer to 0V (GND). If x1 or x10 gain is used, 8-bit resolution can be expected. If x200 gain is used, 7-bit resolution can be expected. Internal reference voltages of nominally 2.56V or AVCC are provided On-chip. The external AREF pin is directly connected to the ADC, and the reference voltage can be made more immune to noise by connecting a capacitor (.1uF or .01uF) between the AREF pin and ground. VREF can also be measured at the AREF pin with a high impedant voltmeter. The ADC converts an analog input voltage to a 10-bit digital value. The minimum value represents GND and the maximum value represents the voltage on the AREF pin minus 1 LSB. If the user has a fixed voltage source connected to the AREF pin, the user may not use the other reference voltage options in the application, as they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch between AVCC and 2.56V as reference selection. The first ADC conversion result after switching reference voltage source may be inaccurate, and the user is advised to discard this result. After the conversion is complete (ADIF is high), the conversion result can be found in the ADC Result Registers (ADCL, ADCH). For single ended conversion, the result is

where VIN is the voltage on the selected input pin and VREF the selected voltage reference. 0x000 represents ground, and 0x3FF represents the selected reference voltage minus one LSB. If differential channels are used, the result is

where VPOS is the voltage on the positive input pin, VNEG the voltage on the negative input pin, GAIN the selected gain factor, and VREF the selected voltage reference. The Page 2 of 10

ANALOG TO DIGITAL CONVERTER June 10, 2008

result is presented in twos complement form, from 0x200 (-512d) through 0x1FF (+511d). Note that if the user wants to perform a quick polarity check of the results, it is sufficient to read the MSB of the result (ADC9 in ADCH). If this bit is one, the result is negative, and if this bit is zero, the result is positive. Example: ADMUX = 0xED (ADC3 - ADC2, 10x gain, 2.56V reference, left adjusted result) Voltage on ADC3 is 300 mV. Voltage on ADC2 is 500 mV. ADCR = 512 * 10 * (300 - 500) / 2560 = -400 = 0x270 ADCL will thus read 0x00, and ADCH will read 0x9C. Writing zero to ADLAR right adjusts the result: ADCL = 0x70, ADCH = 0x02.

THE DIFFERENTIAL INPUT CHANNELS ARE NOT TESTED FOR DEVICES IN PDIP PACKAGE. THIS FEATURE IS ONLY GUARANTEED TO WORK FOR DEVICES IN TQFP AND QFN/MLF PACKAGES.

Page 3 of 10

ANALOG TO DIGITAL CONVERTER June 10, 2008

ADC related registers

ADC Multiplexer Selection Register ADMUX

Bit 7:6 REFS1:0: Reference Selection Bits These bits select the voltage reference for the ADC. If these bits are changed during a conversion, the change will not go in effect until this conversion is complete (ADIF in ADCSRA is set). The internal voltage reference options may not be used if an external reference voltage is being applied to the AREF pin. Table 1: Voltage Reference Selections for ADC: REFS1 0 0 1 1 REFS0 0 1 0 1 Voltage Reference Selection AREF, Internal Vref turned off AVCC with external capacitor at AREF pin Reserved Internal 2.56V Voltage Reference with external capacitor at AREF pin

Bit 5 ADLAR: ADC Left Adjust Result The ADLAR bit affects the presentation of the ADC conversion result in the ADC Data Register. Write one to ADLAR to left adjust the result. Otherwise, the result is right adjusted. Changing the ADLAR bit will affect the ADC Data Register immediately, regardless of any ongoing conversions. Bits 4:0 MUX4:0: Analog Channel and Gain Selection Bits The value of these bits selects which combination of analog inputs is connected to the ADC. These bits also select the gain for the differential channels. If these bits are changed during a conversion, the change will not go in effect until this conversion is complete (ADIF in ADCSRA is set).

Table 2: Input Channel and Gain Selections: MUX4...0 00000 00001 00010 00011 00100 00101 00110 00111 01000 01001 01010 Single Ended Input ADC0 ADC1 ADC2 ADC3 ADC4 ADC5 ADC6 ADC7 Positive Differential Input Negative Differential Input Gain

N/A

ADC0 ADC1 ADC0

ADC0 ADC0 ADC0

x10 x10 x200

Page 4 of 10

ANALOG TO DIGITAL CONVERTER June 10, 2008

01011 01100 01101 01110 01111 10000 10001 10010 10011 10100 10101 10110 10111 11000 11001 11010 11011 11100 11101 11110 11111

N/A

ADC1 ADC2 ADC3 ADC2 ADC3 ADC0 ADC1 ADC2 ADC3 ADC4 ADC5 ADC6 ADC7 ADC0 ADC1 ADC2 ADC3 ADC4 ADC5

1.22V (VBG) 0V (GND)

ADC0 ADC2 ADC2 ADC2 ADC2 ADC1 ADC1 ADC1 ADC1 ADC1 ADC1 ADC1 ADC1 ADC2 ADC2 ADC2 ADC2 ADC2 ADC2 N/A

x200 x10 x10 x200 x200 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1

ADC Control and Status Register A ADCSRA

Bit 7 ADEN: ADC Enable Writing this bit to one enables the ADC. By writing it to zero, the ADC is turned off. Turning the ADC off while a conversion is in progress will terminate this conversion.

Bit 6 ADSC: ADC Start Conversion In Single Conversion mode, write this bit to one to start each conversion. In Free Running Mode, write this bit to one to start the first conversion. The first conversion after ADSC has been written after the ADC has been enabled, or if ADSC is written at the same time as the ADC is enabled, will take 25 ADC clock cycles instead of the normal 13. This first conversion performs the initialization of the ADC. ADSC will read as one as long as a conversion is in progress. When the conversion is complete, it returns to zero. Writing zero to this bit has no effect.

Page 5 of 10

ANALOG TO DIGITAL CONVERTER June 10, 2008

Bit 5 ADATE: ADC Auto Trigger Enable When this bit is written to one, Auto Triggering of the ADC is enabled. The ADC will start a conversion on a positive edge of the selected trigger signal. The trigger source is selected by setting the ADC Trigger Select bits, ADTS in SFIOR.

Bit 4 ADIF: ADC Interrupt Flag This bit is set when an ADC conversion completes and the Data Registers are updated. The ADC Conversion Complete Interrupt is executed if the ADIE bit and the I-bit in SREG are set. ADIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ADIF is cleared by writing a logical one to the flag. Beware that if doing a Read-Modify- Write on ADCSRA; a pending interrupt can be disabled. This also applies if the SBI and CBI instructions are used. Bit 3 ADIE: ADC Interrupt Enable When this bit is written to one and the I-bit in SREG is set, the ADC Conversion Complete Interrupt is activated. Bits 2:0 ADPS2:0: ADC Prescaler Select Bits These bits determine the division factor between the XTAL frequency and the input clock to the ADC.

Table 3: ADC Prescaler Selections: ADPS2 0 0 0 0 1 1 1 1 ADPS1 0 0 1 1 0 0 1 1 ADPS0 0 1 0 1 0 1 0 1 Division Factor 2 2 4 8 16 32 64 128

By default, the successive approximation circuitry requires an input clock frequency between 50 kHz and 200 kHz to get maximum resolution. If a lower resolution than 10 bits is needed, the input clock frequency to the ADC can be higher than 200 kHz to get a higher sample rate. The prescaler starts counting from the moment the ADC is switched on by setting the ADEN bit in ADCSRA. The prescaler keeps running for as long as the ADEN bit is set, and is continuously reset when ADEN is low.

Page 6 of 10

ANALOG TO DIGITAL CONVERTER June 10, 2008

The ADC Data Register ADCL and ADCH

ADLAR=0

ADLAR=1

ADC9:0: ADC Conversion Result These bits represent the result from the conversion. When an ADC conversion is complete, the result is found in these two registers. If differential channels are used, the result is presented in twos complement form. If the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the Data Registers belongs to the same conversion. Once ADCL is read, ADC access to Data Registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is read, neither register is updated and the result from the conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL Registers is re-enabled. The ADC has its own interrupt which can be triggered when a conversion completes. When ADC access to the Data Registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost.

Page 7 of 10

ANALOG TO DIGITAL CONVERTER June 10, 2008

Special Function IO Register SFIOR

Bit 7:5 ADTS2:0: ADC Auto Trigger Source If ADATE in ADCSRA is written to one, the value of these bits selects which source will trigger an ADC conversion. If ADATE is cleared, the ADTS2:0 settings will have no effect. A conversion will be triggered by the rising edge of the selected Interrupt Flag. Note that switching from a trigger source that is cleared to a trigger source that is set will generate a positive edge on the trigger signal. If ADEN in ADCSRA is set, this will start a conversion. Switching to Free Running mode (ADTS [2:0] =0) will not cause a trigger event, even if the ADC Interrupt Flag is set. Table 4: ADC Auto Trigger Source Selections: ADTS2 0 0 0 0 1 1 1 1 ADTS1 0 0 1 1 0 0 1 1 ADTS0 0 1 0 1 0 1 0 1 Trigger Source

Free Running mode Analog Comparator External Interrupt Request 0 Timer/Counter0 Compare Match Timer/Counter0 Overflow Timer/Counter1 Compare Match B Timer/Counter1 Overflow Timer/Counter1 Capture Event

In single conversion mode, ADSC is cleared simultaneously. The software may then set ADSC again, and a new conversion will be initiated on the first rising ADC clock edge. In Free Running mode, a new conversion will be started immediately after the conversion completes, while ADSC remains high. Bit 4 Res: Reserved Bit This bit is reserved for future use. To ensure compatibility with future devices, this bit must be written to zero when SFIOR is written.

Page 8 of 10

ANALOG TO DIGITAL CONVERTER June 10, 2008

Analog Noise Cancelling Techniques

Digital circuitry inside and outside the device generates EMI which might affect the accuracy of analog measurements. If conversion accuracy is critical, the noise level can be reduced by applying the following techniques: Keep analog signal paths as short as possible. Keep them well away from high speed switching digital tracks. The AVCC pin on the device should be connected to the digital VCC supply voltage via an LC network as shown below. Use the ADC noise canceller function to reduce induced noise from the CPU. If any ADC port pins are used as digital outputs, it is essential that these do not switch while a conversion is in progress.

Page 9 of 10

ANALOG TO DIGITAL CONVERTER June 10, 2008

Sample Codes using the ADC of ATMEGA16

#include <avr\io.h> #include <avr\interrupt.h> // Global variables char adc_data; setup_adc() { SREG = SREG | 0x80; ADMUX = (1<<REFS0) | (1<<ADLAR); ADCSRA = ADCSRA | (1<<ADEN) | (1<<ADIE) | (1<<ADPS2) | (1<<ADPS1) | (1<<ADPS0); } void ini_pwm() { TCCR0 = (1<<WGM00) | (1<<WGM01) | (1<<COM01) | (1<<CS00); } SIGNAL(SIG_ADC) // ADC EOC interrupt { adc_data = ADCH; ADCSRA = ADCSRA | (1<<ADSC); // restart conversion } // Main program int main(void) { DDRB = DDRB | (1<<PB3); // set PB3 as output. DDRA = DDRA | (0<<PA0); //set PA0 as Input. setup_adc(); //setup the ADC ini_pwm(); ADCSRA = ADCSRA | (1<<ADSC); //start ADC conversion while(1) { // Infinite loop OCR0 = adc_data; } }

Page 10 of 10

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- Electronic Ticket Receipt, November 03 For MR ARAYA GEBRESLASSIE BERHEDocument2 pagesElectronic Ticket Receipt, November 03 For MR ARAYA GEBRESLASSIE BERHEMengstu Gebreslassie50% (2)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Introduction To Windows PDFDocument24 pagesIntroduction To Windows PDFRaymoon Twopass DaysNo ratings yet

- Turkle Sherry What Does Simulation Want PDFDocument11 pagesTurkle Sherry What Does Simulation Want PDFmonterojuNo ratings yet

- Volume 1 Drafting Design and Presentation StandardsDocument328 pagesVolume 1 Drafting Design and Presentation StandardsAntonio Herrera PérezNo ratings yet

- Smart Payment MeterDocument2 pagesSmart Payment MeterJesus Castro OrozcoNo ratings yet

- Masterseal 550Document4 pagesMasterseal 550Arjun MulluNo ratings yet

- Stock Register StoreDocument1,218 pagesStock Register StoreSantanu Kumar SahuNo ratings yet

- CHEST Workout Structure and Training Log PREVIEWDocument3 pagesCHEST Workout Structure and Training Log PREVIEWgaurav singhNo ratings yet

- Atmel 42238 Uart Based Sam Ba Bootloader For Sam d20 AP Note At04189Document12 pagesAtmel 42238 Uart Based Sam Ba Bootloader For Sam d20 AP Note At04189manasaNo ratings yet

- Selection ToolsDocument13 pagesSelection ToolsDominador Gaduyon DadalNo ratings yet

- V 2172 0020 0031 - Rev - 6 (3458748) PDFDocument262 pagesV 2172 0020 0031 - Rev - 6 (3458748) PDFLG Milton LuisNo ratings yet

- Qcs 2010 Section 5 Part 8 Transportation and Placing of ConcreteDocument7 pagesQcs 2010 Section 5 Part 8 Transportation and Placing of Concretebryanpastor106No ratings yet

- IG 55 CalculationDocument11 pagesIG 55 CalculationNoridhamNo ratings yet

- Circular Tank Radius CalculationDocument25 pagesCircular Tank Radius CalculationQamar AbbasNo ratings yet

- BNF Syntax of Ruby - Less than 40 character title for Ruby BNF syntax documentDocument2 pagesBNF Syntax of Ruby - Less than 40 character title for Ruby BNF syntax documentChristian FerrazNo ratings yet

- Performance Estimation of Ofdm-Wimax Network: Vishal Sharma & Navneet KaurDocument8 pagesPerformance Estimation of Ofdm-Wimax Network: Vishal Sharma & Navneet KaurTJPRC PublicationsNo ratings yet

- Wa0001Document8 pagesWa0001varshasharma05No ratings yet

- Educational Technology & Education Conferences - January To June 2016 - Clayton R WrightDocument93 pagesEducational Technology & Education Conferences - January To June 2016 - Clayton R WrightEsperanza Román MendozaNo ratings yet

- Vantio CacheServe 7.2.0 Administrators Manual 20161208 PDFDocument577 pagesVantio CacheServe 7.2.0 Administrators Manual 20161208 PDFPaulette Servin100% (1)

- 21st Bomber Command Tactical Mission Report 146, OcrDocument54 pages21st Bomber Command Tactical Mission Report 146, OcrJapanAirRaidsNo ratings yet

- Geometric Design of Highways for EngineersDocument39 pagesGeometric Design of Highways for EngineersZeleke TaimuNo ratings yet

- Man Power PlanningDocument5 pagesMan Power PlanningKarthik AchinNo ratings yet

- Assessment of Groundwater Quality Using GIS - A Case Study of The Churu District of RajasthanDocument9 pagesAssessment of Groundwater Quality Using GIS - A Case Study of The Churu District of RajasthanSivaShankarNo ratings yet

- Ficha Tecnica 750 GPMDocument156 pagesFicha Tecnica 750 GPMByron Chele0% (2)

- Library Management System Project ReportDocument50 pagesLibrary Management System Project ReportSURAJ GAMINGNo ratings yet

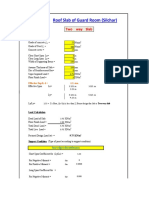

- Roof Slab of Guard RoomDocument3 pagesRoof Slab of Guard RoomAditya KumarNo ratings yet

- Inspection and Maintenance of Drillpipe Ebook PDFDocument39 pagesInspection and Maintenance of Drillpipe Ebook PDFAntónio OliveiraNo ratings yet

- IEC Certificate 1000V Single Glass 202304Document35 pagesIEC Certificate 1000V Single Glass 202304Marian ProzorianuNo ratings yet

- Rexroth电磁阀手册Document12 pagesRexroth电磁阀手册davidwang85120% (1)

- Geo-Informatics and Nano-Technology For Precision FARMING (AGRO-301) 5 SemesterDocument5 pagesGeo-Informatics and Nano-Technology For Precision FARMING (AGRO-301) 5 SemesterVinod Vincy67% (3)