Professional Documents

Culture Documents

S&H

Uploaded by

Ali AbdOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

S&H

Uploaded by

Ali AbdCopyright:

Available Formats

Analog Sample and Hold

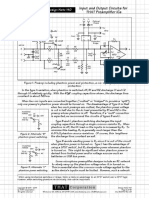

This Sample and Hold design incorporates quite a number of features while using only six active devices three general purpose opamps, one FET op amp, one N-FET and one PNP transistor. Here are some of the features: Voltage Controlled Sample Clock External Clock Input with Threshold Control Single Sample Pushbutton Wide Input Signal Range of 10 to +10volts Wide Sample Clock Rate of 0.5 Hz to 8 Khz Low Sample Droop Rate of less than 0.5% per second

The Sample and Hold

Referring now to the circuit diagram, the basic Sample and Hold Circuit is built around the op amp buffers labeled A and B, and the 2n5951 NFET switch. Op amp A can be any general purpose op amp such as a 741. It is used to buffer the input signal. Op amp B must be a FET type device, such as the LM351, used for its high input impedance. It acts as an output buffer for the sampled voltage held on the capacitor C1. The NFET serves as a switch that closes whenever op amp D outputs its 100 usec. pulse. During this 100useconds the NFET switch is closed and capacitor C1 charges or discharges to the input voltage level output from op amp A. At all other times the NFET switch is open so that the charge accumulated on C1 is effectively trapped between the two high FET resistances. Of course, nothing is perfect, so there is a slow leakage of C1s charge through op amp Bs input resistance. For an LM351 this droop rate is less than 0.5% drop in voltage for every second.

The Pulse Generator

The circuitry around op amp D forms a pulse generator. The op amp itself acts as a comparator. The op amp output normally rests at 15v with the negative input at a diode drop of about 0.6v and the positive input at 7.5v as determined by resistors R6 and R7. Any sufficiently large positive voltage transition at the pulse generators input will be coupled through capacitor C4 and diode D1 to drive the positive input above the negative inputs 0.6v. With this change in the op amps positive input, the output immediately goes high to +15v and the positive inputs rest voltage is brought to +7.5v. The negative input, in the meantime, reacts slower as capacitor C3 charges toward +15v through R5. After about 100 usec., the negative inputs voltage has risen to just above the positive inputs +7.5v. The output then goes low to its original state of 15v. The output pulse width is set by R6, R7, R5, and C3. The sampling time of 100us was chosen to be as short as possible while still allowing time for the holding capacitor

C1 to charge or discharge to the new input voltage. This pulse width limits the maximum sampling clock rate to about 8 KHz. A full 15v to +15v pulse was used to switch the NFET in order to accommodate a large input signal voltage range. Input signals can range from 10v to +10v. This allows sampling of synthesizer control voltages as well as audio signals.

The Sampling Clock

Op amp C is used to form the sampling clock. The 2-position switch, in the position shown in the circuit diagram, completes a positive feedback path from the op amps output to its positive input. This results in a voltage-controlled clock. The op amp C itself functions as a comparator. Its negative input is set at about 0.6v by resistors R8 and R9 when there is no CV Input. When a Control Voltage Input is present, the negative op amp input is set slightly below the actual CV input voltage. As a starting point for our sequence of events, consider op amp Cs output at 15v. The PNP transistor is in saturation with its collector at +15v. Capacitor C2 is quickly charged to +15v through R3 and the diode D3. Ideally, this charging should be as fast as possible so that C2 is fully charged to 15v before the op amp switches to +15v. However, the current limiting R3 has been inserted to prevent glitches on the supply lines and subsequent coupling of the sampling clock to the Sample and Hold output. The additional time required to allow C2 to fully charge is bought by inserting a 100pf capacitor and a 2M resistor between the output and positive input. This couples the highto-low transition of the comparator output to the positive input, which brings it below the negative input for the necessary time. After the comparators output goes high the transistor goes into cutoff and C2 slowly discharges toward ground through R2, R3, and R4. R2 is made variable to act as a clock rate control. The comparator does not switch to 15v again until the capacitors voltage drops below the voltage as seen by the negative input, making the CV input act as a second clock rate control. High CV Input voltages effectively shorten the discharge time of C2 and thus increase the sampling clocks frequency. The resulting waveform at Cs output is a pulse oscillator and the waveform at the positive input is a sawtooth. The two switches provide a number of additional operating modes for the Sample Clock. When the clock is in its free running mode, the pushbutton can stop the clock. It stops it by holding the positive input of the comparator high for as long as the pushbutton is pressed. When the 2-positive switch is switched to External Clock, the operation of the positive feedback path is broken and the op amp acts as a simple comparator with the External signal as an input. The CV Input now acts as a switching threshold control. One application would be to use a noise source as the External clock Input. In such a setup the sampling becomes random with an overall rate controlled by the CV Input threshold setting.

With no External Clock Input, the pushbutton can be used for single sample triggering.

Control Voltage Noise Generator

A second circuit provides a randomly varying signal for either the Sample and Holds main input or its external clock input. The 3080 chip is a transconductance device. The noise signal from the 2N967 transistor junction is amplified by about 1000 (220K/220). The output of the 3080 is a current that charges and discharges the 1.0uF capacitor with the amplified noise signal. The amount of current available for this process is determined by the Rate control 741 op amp. A smaller rate means that less current is available to charge and discharge the capacitor so that it is unable to keep up with the fast changes of the noise signal. A larger rate input voltage translates into more current at the output of the 3080 allowing the changing voltage on the capacitor to keep up with the amplified noise signal. Finally, the output 741 provides a means to adjust the final voltage offset and gain with trimmers.

John Talbert 10/1980

R1 A Slew Rate 741 R2 Clock Rate R3 D3 R4

2N5951

B

+

1K Out LM351

In

C1

1 M

C2

100K 2M 100pf 100K 2N3638

D2

R5

Ext Clk 100K

C3

+

C4 C

D1

D

+

N.O. Pushbutton

741 741 240K

R6

CV IN 10K

R8

Sample And Hold

R9 0.1F

R7

+15v 220 100K 50F

-

220K

+15v 33K 2N5951 1.0F 24K

-

0.47F

3080

+

100K Gain Adjust 1K Noise Voltage Out 3volt to 12volt

0.1F 2N967

741 -15v +15v

+

+15v 27K Rate 100K

47K

100K

Offset

20K

20K

20K

-15v 20K Noise Rate Control Voltage In

-

741

+

Control Voltage Noise Generator

You might also like

- AN-4104 Fairchild Elenota - PLDocument18 pagesAN-4104 Fairchild Elenota - PLdavidthijsNo ratings yet

- SMPS ForwardConverterTypePCDocument17 pagesSMPS ForwardConverterTypePCNAYEEMNo ratings yet

- 493.simple CSADocument1 page493.simple CSAJustin FozzardNo ratings yet

- AN-1349 LM34910 Evaluation Board: User's GuideDocument5 pagesAN-1349 LM34910 Evaluation Board: User's GuiderolandseNo ratings yet

- Experiment Title: Study of Operational Amplifier As Precision Rectifier ObjectiveDocument2 pagesExperiment Title: Study of Operational Amplifier As Precision Rectifier ObjectiveAaa AaaNo ratings yet

- AN4104 Forward Converter Type PC SMPS With FPS: Sangtae-Im PD DivisionDocument17 pagesAN4104 Forward Converter Type PC SMPS With FPS: Sangtae-Im PD DivisionJose Miguel Rodriguez CarreñoNo ratings yet

- Ic Special Function For Sensor Signal ConditioningDocument101 pagesIc Special Function For Sensor Signal ConditioningLaura TampubolonNo ratings yet

- BigmufpiDocument4 pagesBigmufpinene_guitarNo ratings yet

- AM Transmitter: Mudit AgarwalDocument1 pageAM Transmitter: Mudit Agarwalsubdh neupaneNo ratings yet

- Ring Frobnicator: To Millenium Bypass Batt Clip Led 3 Depth 10K Lin (Back) (Back) Freq 100K Log Trem/Ring (SPDT)Document1 pageRing Frobnicator: To Millenium Bypass Batt Clip Led 3 Depth 10K Lin (Back) (Back) Freq 100K Log Trem/Ring (SPDT)Emmanuel SanzNo ratings yet

- PIR Motion DetectorDocument6 pagesPIR Motion DetectorTomi OzzyNo ratings yet

- Power Supply Trainer Using Lm723 IcDocument8 pagesPower Supply Trainer Using Lm723 IcDinesh Kumar MehraNo ratings yet

- Arduino Inverter230515Document3 pagesArduino Inverter230515Ibrahim Dalafika AbdullahiNo ratings yet

- QRP DSB Pentru 40 Si 20mDocument8 pagesQRP DSB Pentru 40 Si 20mfox7878No ratings yet

- Clap SwitchDocument1 pageClap SwitchSaravana_Kumar_4984No ratings yet

- Acom 1011 Service ManualDocument40 pagesAcom 1011 Service ManualHubert JoriskesNo ratings yet

- pa16uDocument14 pagespa16uRony SouzaNo ratings yet

- Roland Funny Cat SchematicDocument4 pagesRoland Funny Cat SchematicGustavoTfLa100% (1)

- CDV700Pro Construction Tutorial PDFDocument33 pagesCDV700Pro Construction Tutorial PDFjuan9gonzalez_9No ratings yet

- Experiment 10: To Plot The Magnitude and Phase Response of A Third-Order Butterworth Low Pass FilterDocument5 pagesExperiment 10: To Plot The Magnitude and Phase Response of A Third-Order Butterworth Low Pass FilterEngr. Afshan ishaq Electronics ABTNo ratings yet

- PMSMDocument6 pagesPMSMChacho ChocosNo ratings yet

- Design high frequency push-pull DC/DC converterDocument5 pagesDesign high frequency push-pull DC/DC converterEdoardoNo ratings yet

- PCB Wizard - Sun TrackerDocument2 pagesPCB Wizard - Sun TrackerArunkumar Murugappan100% (1)

- MP39 - MP39A: Power Operational AmplifierDocument14 pagesMP39 - MP39A: Power Operational AmplifierPtichkinNo ratings yet

- Microphone Preamplifier Circuit DiagramDocument1 pageMicrophone Preamplifier Circuit DiagramSigg KeyoNo ratings yet

- Audio Smps 700w V2.1Document5 pagesAudio Smps 700w V2.1amir arkaskNo ratings yet

- IRS2092 1-kW Class D Amp THD & Layout TestsDocument8 pagesIRS2092 1-kW Class D Amp THD & Layout Testsllcoolj11413No ratings yet

- Opamp TIDocument5 pagesOpamp TIAmogh Gajaré100% (1)

- Service Information Service Information: WWW - Laney.co - UkDocument3 pagesService Information Service Information: WWW - Laney.co - UkCarlos Cárdenas BarbaNo ratings yet

- ReportDocument6 pagesReportZeshan Ahmad SipraNo ratings yet

- 2 UkDocument2 pages2 UkJosé ManuelNo ratings yet

- Laney Lg12 SMDocument3 pagesLaney Lg12 SMJavier RojasNo ratings yet

- Clip Azul: Resistors Capacitors Diodes Parts ListDocument1 pageClip Azul: Resistors Capacitors Diodes Parts ListBastiaoNo ratings yet

- iwomi electDocument5 pagesiwomi electP1nice48No ratings yet

- DIY Naim MC To MM Mod Sch2Document1 pageDIY Naim MC To MM Mod Sch2tubetymeNo ratings yet

- Dual Driver v2Document5 pagesDual Driver v2Jorge JuniorNo ratings yet

- Elec3404 Term Project 2011Document6 pagesElec3404 Term Project 2011aliNo ratings yet

- That - DN140 (Verschoben) 2Document1 pageThat - DN140 (Verschoben) 2sdtrnkNo ratings yet

- 25W + 25W Stereo Class-D Amplifier 50W Mono in BTL: DescriptionDocument10 pages25W + 25W Stereo Class-D Amplifier 50W Mono in BTL: DescriptionJULIONo ratings yet

- Ssc1s312a Ds EnmDocument26 pagesSsc1s312a Ds Enmdeivison sobrinhoNo ratings yet

- Eecs412 Lab1Document4 pagesEecs412 Lab1Josué TriveñoNo ratings yet

- Linear Power Amplifier Using HEXFETDocument9 pagesLinear Power Amplifier Using HEXFETRicardoCavalheiroNo ratings yet

- UcD 10w NoB v1Document1 pageUcD 10w NoB v1Leegh Lungset MbesesetNo ratings yet

- SWR Auto & Peak-Power Wattmeter Rev6 PDFDocument4 pagesSWR Auto & Peak-Power Wattmeter Rev6 PDFkierosNo ratings yet

- In-Plug Series: IPS201: Revision 4Document10 pagesIn-Plug Series: IPS201: Revision 4chafic WEISSNo ratings yet

- Model Spice - Laborator 1Document97 pagesModel Spice - Laborator 1Fage RaulNo ratings yet

- EE322 LAB3 ReportDocument6 pagesEE322 LAB3 ReportkynguyenNo ratings yet

- NCP1396A, NCP1396B Controller, High Performance Resonant Mode, With High and Low Side DriversDocument26 pagesNCP1396A, NCP1396B Controller, High Performance Resonant Mode, With High and Low Side DriversMaria VaccarielloNo ratings yet

- ECE 306 Lab 4: Class AB Amplifier EfficiencyDocument8 pagesECE 306 Lab 4: Class AB Amplifier EfficiencyShehzadtajNo ratings yet

- Regulated DC power supply with current limiter and adjustable outputDocument5 pagesRegulated DC power supply with current limiter and adjustable outputЂорђе МалешевићNo ratings yet

- Flyback transformer specification and circuit diagramDocument2 pagesFlyback transformer specification and circuit diagramRodrigoNo ratings yet

- DC Motor Speed Controller 1 PDFDocument1 pageDC Motor Speed Controller 1 PDFyukie heningNo ratings yet

- DC Motor Speed Controller 1Document1 pageDC Motor Speed Controller 1Antonio BentoNo ratings yet

- DC-MOTOR-SPEED-CONTROLLER-1 Using 3525 Circuit of Oscillator PDFDocument1 pageDC-MOTOR-SPEED-CONTROLLER-1 Using 3525 Circuit of Oscillator PDFChAmirShokatGujjar100% (2)

- DC Motor Speed Controller 1 PDFDocument1 pageDC Motor Speed Controller 1 PDFRyn YahuFNo ratings yet

- EasyArc Zx7-200 Igbt Inverter WelderDocument1 pageEasyArc Zx7-200 Igbt Inverter WelderSandeep Kumar67% (12)

- R3 3.6kΩ C2 R9 10kΩ R10 3.6kΩ C5: Q1 2N3904* Q2 2N3904Document2 pagesR3 3.6kΩ C2 R9 10kΩ R10 3.6kΩ C5: Q1 2N3904* Q2 2N3904Justine Aldwin SarmientoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet