Professional Documents

Culture Documents

BVM

Uploaded by

Manish PrajapatiOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BVM

Uploaded by

Manish PrajapatiCopyright:

Available Formats

NATIONAL CONFERENCE ON RECENT TRENDS IN ENGINEERING & TECHNOLOGY 14-15 May 2011

SVPWM Scheme for Two-Level and Three Level Inverter Fed Induction Motor Drive

Manish G. Prajapati1,Himanshu N Chaudhari2 Bhavesh R Patel3 and Dr Hina Chandwani4

Student, Dept. of Electrical Engineering, The M.S.U. Baroda, Gujarat, India Lecturer, Dept. of Electrical Engineering, G.E.C, Palanpur, Gujarat, India 4 Professor, Dept. of Electrical Engineering, The M.S.U baroda, Gujarat, India E-Mail Id :- manish.er570@gmail.com, him.chaudhari@gmail.com, and hinachandwani@gmail.com

3 1 and 2

Abstract This paper describe comparison of SVPWM scheme for Two level and Three inverters . This paper introduces the working principle of SVPWM for Two-Level and Three level inverter. Simulation results are obtained using PSIM Software with a 45-kW (60 HP) motor drive and analysis of THD (Total Harmonic Distortion) and FFT (Fast Fourier Transform) in Line Voltage and Line Current for both Inverter. From results it is concluded that SVPWM scheme use more dc link voltage than SPWM scheme. In Three level inverter scheme THD in line voltage & line current is also less than Two level inverter. Index TermsTwo level inverter, Three level inverter, space vector pulse width modulation (SVPWM).

inverter simulated using PSIM software and compare both. From results, three level inverter scheme has more advantage than two level inverter scheme. I. INVERTER SCHEME FOR AN INDUCTION MOTOR DRIVE The circuit model of a typical three-phase voltage source PWM inverter is shown in Fig. 1 There are the six power switches(IGBT) that shape the output, which are controlled by the switching variables a, a, b, b, c and c[4].When an upper IGBT is switched on, i.e., when a, b or c is 1,the corresponding lower IGBT is switched off, i.e .,the corresponding a, b or c is 0.Therefore, the on and off states of the upper IGBT S1, S3 and S5 can be used to determine the output voltage[5].

I.

INTRODUCTION

HE TWO-Level inverter topology has attracted attention in low power low voltage drive applications where as THREE-Level inverter topology has attracted attention in high power High performances voltage drive applications. Single-phase VSI cover low-range power applications and three-phase VSI cover the medium- to high-power applications [1]. The Main purpose of these two level and three level inverter topologies is to provide a three phase voltage source, where the amplitude, phase, and frequency of the voltages should always be controllable. Although most of the applications require sinusoidal voltage waveforms (e.g., ASDs, UPSs, FACTS, VAR compensators), arbitrary voltages are also required in some emerging applications (e.g., active filters, voltage compensators) [2]. with increase of semi conductor technology voltage source inverter have been extending its application area widely. The two level inverter is composed of only one switching cell per phase but the three level inverter has two switching cell per phase. Three level diode clamped (Neutral point ) inverter is most favourable among the various multi level configuration[4].The three level diode clamped inverter employs clamping diode and series DC capacitor to produce AC voltage waveform with three level. Three-level voltage-fed PWM inverters are recently showing popularity for multi-megawatt industrial drive applications [3]. SVPWM modulation techniques are famous for inverter fed induction motor drives. Both the

Fig. 1. Three-phase voltage source PWM Inverter

II. SVPWM METHOD FOR TWO -LEVEL INVERTER Space Vector PWM (SVPWM) refers to a special switching sequence of the upper three power IGBT of a three-phase inverter [6]. It has been shown to generate less harmonic distortion in the output voltages and or currents applied to the phases of an AC motor and to provide more efficient use of supply voltage compared with sinusoidal modulation technique [4]. Fig.2 shows the basic Switching Vector of SVPWM Technique. In this schemes there are eight valid switching state out of six active switching space vector are evenly distributed 60 interval with 2Vdc/3 length and form a hexagon. Also two zero space vector are locate at the center of hexagon in the complex plane as shown in

NATIONAL CONFERENCE ON RECENT TRENDS IN ENGINEERING & TECHNOLOGY 14-15 May 2011

fig 2.For a given Magnitude (length) and position, Vref can be synthesized by three nearby stationary vectors, based on

T2 (Ts Ma) sin (Theta))

(7) (8)

T0 Ts - T1- T2

Where, TS = Sampling Time Ma = Modulation Index Fs = Sampling Frequency

Fig. 2. Basic switching vectors and sectors

Fig. 3. Vector diagram when reference vector in sector-1 (where = 60)

which the switching states of the inverter can be selected and gate signals for the active switches can be generated [8]. When Vref passes through sectors one by one, different sets of switches will be turned on or off. As a result, when Vref rotates one revolution in space, the inverter output voltage varies one cycle over time. The inverter output frequency corresponds to the rotating speed of Vref, while its output voltage can be adjusted by the Magnitude of Vref. The Vref (called the reference vector) vector rotates counter clockwise with the angle varying between 0 and 360 degrees. III. STEPS FOR SIMULATING THE SVPWM FOR TWO LEVEL INVERTER

C. Step 3: Determine the switching time of each IGBT (S1 to S6) Fig.5 shows space vector PWM switching patterns at each sector. Based on this the switching time at each sector is summarized in Table-I, and it will be built in PSIM model to simulate SVPWM.

A. Step 1. Determine Vref, and angle (Theta)

Freq Speed ref Pole 120

Freq Vbase Fbase

SVPWM Switching Pattern at Sector 1 and 2

(1)

Vref

(2)

(3) (4)

SVPWM Switching Pattern at Sector 3 and 4

Ma

Vref Vdc

Theta 2 Frequency time

B. Step 2. Determine time duration T1, T2,T0 From Fig. 4, the switching time duration in any Sector can be calculated as follows:

Ts

1 Fs

(5) (6)

T1 (Ts Ma) sin (pi 3) Theta

SVPWM Switching Pattern at Sector 5 and 6 Fig.4. Space Vector PWM switching patterns at each sector

NATIONAL CONFERENCE ON RECENT TRENDS IN ENGINEERING & TECHNOLOGY 14-15 May 2011

TABLE-I SWITCHING TIME CALCULATION AT EACH SECTOR SECTOR UPPER SWITCHES (S1,S3,S5) S1 = T1+T2+T0/2 S3=T2+T0/2 S5=T0/2 S1 = T1+T0/2 S3=T1+T2+T0/2 S5=T0/2 S1 = T0/2 S3=T1+T2+T0/2 S5=T2+T0/2 S1 = T0/2 S3=T1+T0/2 S5=T1+T2+T0/2 S1 = T2+T0/2 S3=T0/2 S5=T1+T2+T0/2 S1 = T1+T2+T0/2 S3=T0/2 S5=T1+T0/2 UPPER SWITCHES (S4,S6,S2) S4 = T0/2 S6=T1+T0/2 S2=T1+T2+T0/2 S4 = T2+T0/2 S6=T0/2 S2=T1+T2+T0/2 S4 = T1+T2+T0/2 S6=T0/2 S2=T1+T0/2 S4 = T1+T2+T0/2 S6=T2+T0/2 S2=T0/2 S4 = T1+T0/2 S6=T1+T2+T0/2 S2=T0/2 S4 = T0/2 S6=T1+T2+T0/2 S2=T2+T0/2

There are 24 active states, and three zero states that lie at the center of the hexagon. Each sector has four regions (1,2,3,4) [three]. The switching states of the inverter are summarized in Table I. Switching state P denotes that the upper two switches in leg A are on and the inverter terminal voltage vAn, which is the voltage at terminal A with respect to the neutral point n, is +Vdc/2, whereas N indicates that the lower two switches conduct, leading to vAn = Vdc/2. Switching state O signifies that the inner two switches S2 and S3 are on and vAn is clamped to zero through the clamping diodes. Depending on the direction of load current[bin wo]. It can be observed from Table 1 that switches S1 and S3 operate in a complementary manner. With one switched on, the other must be off. Similarly, S2 and S4 are a complementary pair as well.

IV. SVPWM METHOD FOR THREE LEVEL INVERTER FIG.5 shows a schematic drawing of a multilevel inverter using Diode clamped inverters. The diode-clamped multilevel inverter employs clamping diodes and cascaded dc capacitors to produce ac voltage waveforms with multiple levels. The inverter leg A is composed of four active switches S1 to S4 with four anti parallel diodes D1 to D4. On the dc side of the inverter, the dc bus capacitor is split into two, providing a neutral point n. The diodes connected to the neutral point, Dn1 and Dn2, are the clamping diodes. When switches S2 and S3 are turned on, the inverter output terminal A is connected to the neutral point through one of the clamping diodes. The voltage across each of the dc capacitors is Vdc/2, which is normally equal to half of the total dc voltage Vdc.

Fig 6 Space vector of three Level inverter

The principle of SVPWM method is that the command voltage vector is approximately calculated by using three adjacent vectors. The duration of each voltage vectors obtained by vector calculations; T1V1+T2V2+T3 =TSV* T1 + T 2 + T3 = TS (10)

Fig. 5Three-level Diode clamped inverter topology for induction motor drive

A three-level inverter is characterized by 33= 27switching states as indicated in Fig.2 where the space vector diagram for the three-level inverter which is divided into the six sectors (I, II, III, IV, V, and VI) is also shown.

where V1, V2, and V3 are vectors that define the triangle region in which V* is located. T1, T2 and T3 are the corresponding vector durations and Ts is the sampling time. In a three-level inverter similar to a two-level inverter, each space vector diagram is divided into 6 sectors. For simplicity here only the switching patterns for Sector A will be defined so that calculation technique for the other sectors will be similar. Sector A is divided into 4 regions as shown in Fig.3 where all the possible switching states for each region are given as well. SVPWM for three-level inverters can be implemented by using the steps of sector determination, determination of the region in the sector, calculating the switching times, Ta, Tb, Tc and finding the switching states.

NATIONAL CONFERENCE ON RECENT TRENDS IN ENGINEERING & TECHNOLOGY 14-15 May 2011

V. STEPS FOR SIMULATING THE SPACE VECTOR PWM FOR THREE LEVEL INVERTER A. Determining the sector n (Theta) is calculated Using the Equation no 4 and then the sector, in which the command vector Vref is located, is determined as; If n is between 0 <= n < 60, then Vref in Sector 1, If n is between 60 <= n < 120, then Vref in Sector 2, If n is between 120 <= n < 180, then Vref in Sector 3, If n is between 180 <= n < 240, then Vref Sector 4, If n is between 240 <= n < 300, then Vref Sector 5, If n is between 300 <= n < 360, then Vref Sector 6,

Table 2 SUMMARY OF DUTY CYCLES FOR SVPWM SCHEME

B.

Determining the Region & Simplified Calculation of Duty Cycles

The theoretical maximum length of the normalized reference vector is the two-unity value. However, in steadystate conditions, its length is limited to 3 due to the fact that longer lengths of this vector will be outside of the vectordiagram hexagon, and thus cannot be generated by modulation. Over modulation is produced if the normalized reference vector assumes lengths longer than 3 for some positions of this vector, but it can never be outside of the hexagon. In fig , the reference vector is decomposed into the axes located at zero and sixty degrees, obtaining projections m1 and m2 , respectively.

C.

Finding the switching states

By considering the switching transition of only one device at any time, the switching orders given below are obtained for each region located in Sector 1 if all switching states in each region are used. Therefore, switching signals for Sector 1are, Region 1: - ---, 0--, 00-, 000, +00, ++0, +++ Region 2: - 0--, 00-, +0-, +00, ++0 Region 3: - 0--, +--, +0-, +00 Region 4: - 00-, +0-, ++-, ++0

VI. SIMULATION RESULTS AND DISCUSSION A) Simulation Results of Two level Inverter Fig shows The simulation circuit Diagram of two level inverter. This Two level inverter is simulated on a 45 kW (60 Hp) 4-Pole,415 volts three-phase induction motor at no load with open loop V/f control. The scheme is simulated using DLL (Dynamic Link Library) block of PSIM simulation software package. Output frequency can be varied according to the reference speed input in DLL (Dynamic Link Library) block. C-programming has been developed for SVPWM scheme using DLL block. Base frequency and Base voltage input in DLL block is used to maintain V/f ratio constant. The 2-level SVPWM scheme is used for the PWM signal generation, based on the sampled amplitudes of reference phase voltages. The line voltage, line current, FFT & THD of Line Voltage and Line Current waveforms for inverter operation are presented in Fig. 10.

Fig 7 Projections of the normalized vector reference vector in the region-1

In general, these values are the direct duty cycles of the vectors, as in the following, Table-2 summarizes to ascertain the region where the reference vector lies and the duty cycles of the nearest three vectors in the first sector. Same duty cycles can be used for others sectors of stationary vectors.

NATIONAL CONFERENCE ON RECENT TRENDS IN ENGINEERING & TECHNOLOGY 14-15 May 2011

simulation software package. Also In this inverter scheme Output frequency can be varied according to the reference speed input in DLL (Dynamic Link Library) block. The SVPWM scheme is used for the PWM signal generation, based on the sampled amplitudes of reference phase voltages. The line voltage, line current, FFT & THD of Line Voltage and Line Current waveforms for inverter operation are presented for three level inverter in Fig. 10.

Fig.9. Simulation circuit for two level inverter using SVPWM

(a) Line Voltage waveform (X- axis: 1 div = 10 ms, Y- axis: 1 div= 250 V)

Fig.10. Simulation circuit for Three level inverter using SVPWM (b) Enlarged Line Voltage FFT (X- axis: 1 div = 10 kHz, Y- axis: 1 div= 50 V)

(a)

(c) Line current waveform (X- axis: 1 div = 10 ms, Y- axis: 1 div= 20 A)

(a) Line Voltage waveform (X- axis: 1 div = 10 ms, Y- axis: 1 div= 250 V)

(d) Enlarged Line current FFT (X- axis: 1 div = 10 kHz, Y- axis: 1 div= 0.5 A) Fig. 10. Simulation results for SVPWM

Enlarged Line Voltage FFT (X- axis: 1 div = 10 kHz, Y- axis: 1 div= 50 V)

Simulation Results of Three level Inverter The Three level inverter is also simulated on a 45 kW (60 Hp) 4-Pole, 415 volts three-phase induction motor at no load with open loop V/f control. Fig shows the simulation circuit diagram of three level inverter. The scheme is simulated using DLL (Dynamic Link Library) block of PSIM

Line current waveform (X- axis: 1 div = 10 ms, Y- axis: 1 div= 20 A)

NATIONAL CONFERENCE ON RECENT TRENDS IN ENGINEERING & TECHNOLOGY 14-15 May 2011

(d) Enlarged Line current FFT (X- axis: 1 div = 10 kHz, Y- axis: 1 div= 0.5 A)

I. CONCLUSION This paper has presented an overview of SVPWM theory and simulation for Two-Level inverter and Three level inverter. It has been seen that SVPWM generate less Harmonic distortion in the output voltages and currents applied to the phases of an induction motor. switching pattern available from the direct switching between positive and negative half buses is violated all times and minimum switching is assured. The proposed method is based on standard two level inverter and then uses a mapping process to achieve the SVM for multilevel. Simulation results have been provided to prove the viability of the scheme.

Department of Electrical Engineering College Station, Texas, pp. 223-224. [7] Do-Hyun jang and duck yong yoon Space vector technique for two phase inverter fed single phase induction Motor IEEE-1999 [8] B. Wu, High-Power Converters and AC Drives, IEEE Press and Wiley, 2006. [9] Krisztina Leban, Cristian Lascu, and Alin Argeseanu Implementation of Space Vector Modulation Strategies for Voltage Source Inverters for Induction Motor Drives University of Timisoara. [10] M. Lakshmi Swarupa, G. Tulasi Ram Das and P.V. Raj Gopal Simulation and Analysis of SVPWM Based 2-Level and 3-Level Inverters for Direct Torque of Induction Motor International Journal of Electronic Engineering Research ISSN 0975 - 6450 Vol- 1 No.3 (2009) pp. 169184

APPENDIX Ratings of the three-phase 45 kW (60 H.P.), 4-pole, 415 V, 50 Hz squirrel cage induction motor are: Power Output: 45kW (60 H.P.) Stator resistance (Rs): 0.07 Rotor resistance (Rr): 0.025 Stator leakage inductance (Lls) : 0.0008 H Rotor leakage inductance (Llr): 0.0008 H Magnetizing inductance (Lm): 0.0228 H Rotor inertia (J) : 0.42kgm2

REFERENCES [1] P. J. Patel, Rakesh A. Patel, Vinod Patel, P. N. Tekwani Implementation of Self Balancing Space Vector Switching Modulator for Three-Level Inverter, IEEE Region 10 Colloquium and the Third International Conference on Industrial and Information Systems, Kharagpur, INDIA December, 2008. Sunil Panda, Anupam Mishra, B Srinivas Control of Voltage Source Inverters using SVPWM for Adjustable Speed Drive Applications Thesis of Department of Electrical Engineering National Institute Of Technology Rourkela, Rourkela ,May- 2009. Mr.Venkatara, Mana Naik, Mrs. K.Sree Gowri Space Vector Based Hybrid Pulse Width Modulation for reduced Current Ripple National Conference on Intelligent Electrical Systems (NCIES09), April 2009. Kalpesh H Bhalodi and Pramod agraval Space Vector Modulation withDC-Link Voltage Balancing Control for Three-Level Inverters International Journal of Recent Trends in Engineering, Vol 1, No. 3, May 2009 jin-woo jung space vector pwm inverter mechatronic systems laboratory department of electrical and computer engineering he ohio state university, pp 4 - 14. Hamid A. Toliyat and Steven Campbell dsp-based electromechanical motion control Texas A&M University

[2]

[3]

[4]

[5]

[6]

You might also like

- Chapter - 3 Phase Controlled RectifierDocument10 pagesChapter - 3 Phase Controlled RectifierManish PrajapatiNo ratings yet

- Multi Stack Variable Reluctance Stepper MotorDocument1 pageMulti Stack Variable Reluctance Stepper MotorManish PrajapatiNo ratings yet

- Notes 2Document14 pagesNotes 2Manish PrajapatiNo ratings yet

- Multi Stack Variable Reluctance Stepper MotorDocument1 pageMulti Stack Variable Reluctance Stepper MotorManish PrajapatiNo ratings yet

- Variable Reluctance and Stepping Motor TypesDocument7 pagesVariable Reluctance and Stepping Motor TypesManish PrajapatiNo ratings yet

- Three Level InverterDocument5 pagesThree Level InverterManish PrajapatiNo ratings yet

- Variable Reluctance and Stepping Motor TypesDocument7 pagesVariable Reluctance and Stepping Motor TypesManish PrajapatiNo ratings yet

- DesDocument6 pagesDesManish PrajapatiNo ratings yet

- Comparison of SPWM and SVPWM Scheme For Two-Level Inverter Fed Induction Motor DriveDocument6 pagesComparison of SPWM and SVPWM Scheme For Two-Level Inverter Fed Induction Motor Drivemanish_er570No ratings yet

- Manit 2Document8 pagesManit 2Manish PrajapatiNo ratings yet

- 15 03Document6 pages15 03Manish PrajapatiNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5782)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Intoduction To Project ManagementDocument15 pagesIntoduction To Project Managementsahil kumarNo ratings yet

- IC202 Quick GuideDocument134 pagesIC202 Quick GuideFAUSTO ORQUERANo ratings yet

- Sky Esports Skirmish 2022 RulebookDocument6 pagesSky Esports Skirmish 2022 RulebookIts MeNo ratings yet

- Lib 12F629Document18 pagesLib 12F629Sixto AgueroNo ratings yet

- Web Based Meeting SchedulerDocument16 pagesWeb Based Meeting Schedulerraghu84taduriNo ratings yet

- Connection Manual (Hardware) : Fanuc Series 0 - Model C FANUC Series 0 Mate-MODEL CDocument370 pagesConnection Manual (Hardware) : Fanuc Series 0 - Model C FANUC Series 0 Mate-MODEL CTrương Vũ Jr.100% (1)

- dSPACE FlexRay Configuration PackageDocument6 pagesdSPACE FlexRay Configuration PackageEyob T. BiratuNo ratings yet

- Artificial Intelligence123987Document6 pagesArtificial Intelligence123987Sandeep BhargavaNo ratings yet

- Oracle HCM Cloud-Kronos Workforce Central IntegrationDocument10 pagesOracle HCM Cloud-Kronos Workforce Central IntegrationyurijapNo ratings yet

- TCPD User GuideDocument270 pagesTCPD User GuideRichard DeodathNo ratings yet

- (Csc. 351 Software Engineering) : Lecturer: Hiranya BastakotiDocument13 pages(Csc. 351 Software Engineering) : Lecturer: Hiranya Bastakotiauthor acessNo ratings yet

- Microsoft: Exam Questions Az-500Document25 pagesMicrosoft: Exam Questions Az-500Doaa AlhamadiNo ratings yet

- Management Information SystemDocument48 pagesManagement Information SystemRachit Puri100% (89)

- Automated Carton Conveyor System: Automation Project: PLC Based Coal Crushing and ConveyorDocument2 pagesAutomated Carton Conveyor System: Automation Project: PLC Based Coal Crushing and ConveyorFaryal MughalNo ratings yet

- Light SailDocument21 pagesLight SailYegnasivasaiNo ratings yet

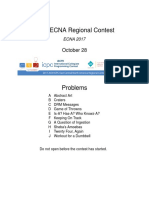

- Game of Throwns ECNA 2017 Regional ContestDocument22 pagesGame of Throwns ECNA 2017 Regional ContestDuarte Garcia JorgeNo ratings yet

- AWS Solution Architect CertificationDocument6 pagesAWS Solution Architect Certificationpappupass200467% (12)

- Course Work 1 ReportDocument41 pagesCourse Work 1 Reportbenji100100% (3)

- ICSI Foundation Program Admission DetailsDocument7 pagesICSI Foundation Program Admission DetailsPratibha LakraNo ratings yet

- Ti Iwr6412Document84 pagesTi Iwr6412alperusluNo ratings yet

- Hopf 6870 - 1101Document58 pagesHopf 6870 - 1101macakafkaNo ratings yet

- The 2011 Focus Experts' Guide To Enterprise Resource PlanningDocument24 pagesThe 2011 Focus Experts' Guide To Enterprise Resource PlanningRahul KapoorNo ratings yet

- Using System Class Name (Public Static Void Main (Console - Writeline ("My Name Is Sujit") ) )Document26 pagesUsing System Class Name (Public Static Void Main (Console - Writeline ("My Name Is Sujit") ) )Sunil KumarNo ratings yet

- SGE Cheat Sheet PDFDocument5 pagesSGE Cheat Sheet PDFKeerati ManeesaiNo ratings yet

- Digital Forensics ReportDocument36 pagesDigital Forensics Reportehtisham sadiqNo ratings yet

- A Guide To The Dragon Ies of Borneo - Their Identification and BiologyDocument37 pagesA Guide To The Dragon Ies of Borneo - Their Identification and Biologyagusrahman ekaputra abasNo ratings yet

- QSD111.00 Corporate Quality ManualDocument21 pagesQSD111.00 Corporate Quality ManualDiego Torres ObregonNo ratings yet

- HydrologyDocument10 pagesHydrologyMarianne Lou PalomarNo ratings yet

- Cisco IOS Debug Command Reference - Commands S Through ZDocument894 pagesCisco IOS Debug Command Reference - Commands S Through ZscorcdNo ratings yet

- Sign in - Top AI Chatbot AppsDocument1 pageSign in - Top AI Chatbot AppsMariah DemolNo ratings yet