Professional Documents

Culture Documents

23570458

Uploaded by

Michelle Celeste BatuOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

23570458

Uploaded by

Michelle Celeste BatuCopyright:

Available Formats

VLSI DESIGN TECHNIQUES FOR ANALOG AND DIGITAL CIRCUITS

Randall L. Geiger

Department of Electrical Engineering Texas A&M University

Phillip E. Allen

Department of Electrical Engineering Georgia Institute of Technology

Noel R. Strader

MCC Austin, Texas

McGraw-Hill Publishing Company

New York St. Louis San Francisco Auckland Bogota Caracas Hamburg Lisbon London Madrid Mexico Milan Montreal New Delhi Oklahoma City Paris San Juan Sao Paulo Singapore Sydney Tokyo Toronto

CONTENTS

Preface 1

1.0 1.1 1.2 1.3 1.4 1.5 1.6

Xlll

Practical Considerations

Introduction Size and Complexity of Integrated Circuits The Microelectronics Field . IC Design Process Economics Yield Trends in VLSI Design References Problems

l

2 4 10 12 16 19 28 29 29

2

2.0 2.1

Technology

Introduction IC Production Process 2.1.1 Processing Steps 2.1.2 Packaging and Testing Semiconductor Processes 2.2.1 MOS Processes 2.2.1a NMOS Process 2.2Ab CMOS Process 2.2.1c Practical Process Considerations 2.2.2 Bipolar Technology 2.2.3 Hybrid Technology Design Rules and Process Parameters Layout Techniques and Practical Considerations References Problems

32

32 32 33 41 42 46 49 55 59 64 68 72 78 85 85

2.2

'

2.3 2.4

Appendixes

2A 2B Process Characterization of a Generic NMOS Process Process Characterization of a Generic CMOS Process

95

95 108

VI

CONTENTS

2C 2D 2E

Process Characterization of a Generic Bipolar Process Process Characterization of a Generic Thick Film Process Process Characterization of a Generic Thin Film Process

118 127 130

3

3.0

Device Modeling

Modeling 3.0.1 dc Models 3.0.2 Small Signal Models 3.0.3 Use of Device Models in Circuit Analysis MOS Models 3.1.1 dc MOSFET Model 3.1.2 Small Signal MOSFET Model 3.1.3 High Frequency MOSFET Model 3.1.4 Measurement of MOSFET Model Parameters 3.1.5 Short Channel Devices 3.1.6 Subthreshold Operation 3.1.7 Operation in the Third Quadrant of the ID ~ VDS Plane 3.1.8 Modeling Noise Sources in MOSFETs 3.1.9 Simple MOSFET Models for Digital Applications Diode Models 3.2.1 dc Diode Model 3.2.2 Small Signal Diode Model 3.2.3 High-Frequency Diode Model Bipolar Models 3.3.1 dc BJT Model 3.3.2 Small Signal BJT Model 3.3.3 High-Frequency BJT Model 3.3.4 Measurement of BJT Model Parameters Passive Component Models 3.4.1 Monolithic Capacitors 3.4.2 Monolithic Resistors Summary References Problems

132

132 134 134 139 143 144 158 161 167 171 174 177 180 185 187 187 190 190 191 192 202 205 208 210 211 213 221 221 222

3.1

3.2

3.3

3.4

3.5

@} Circuit Simulation

Introduction Circuit Simulation Using Spice MOSFET Model 4.2.1 Level 1 Large Signal Model 4.2.2 Level 2 Large Signal Model ^.5.3 High-Frequency Model 4.2.4 Noise Model of the MOSFET 4.2.5 Temperature Dependence of the MOSFET 4.3 Diode Model 4.3.1 Large Signal Diode Current 4.3.2 High-Frequency Diode Model *4.4 BJT Model - 4.4.1 Large Signal BJT Model v-4.4.2 High-Frequency BJT Model 4.0 4.1 4.2

237

237 237 240 241 244 246 251 251 252 253 254 255 256 261

CONTENTS

VI1

M.4.3 BJT Noise Model Y4.4.4 Temperature Dependence of the BJT 4.5 Summary References Problems

262 263 264 264 265

Appendixes

4A 4B 4C Mosfet Parameter Definitions Diode Parameter Definitions BJT Parameter Definitions

271

271 280 282

Basic Integrated Circuit Building Blocks

5.0 K 5.1 K 5.2 X 5.3 v-5.4 J 5.5 C x5.6 Introduction Switches Active Resistors Current Sources and Sinks Current Mirrors/Amplifiers Voltage and Current References Summary , References x Problems , Design Problems

287

287 289 302 318 333 354 372 372 373 376

6

6.0 6.1

Amplifiers

Introduction Inverting Amplifiers 6.1.1 General Concepts of Inverting Amplifiers 6.1.2 MOS Inverting Amplifiers 6.1.3 BJT Inverting Amplifiers Improving the Performance of Inverting Amplifiers 6.2.1 Current-Driven CMOS Cascode Amplifier 6.2.2 Voltage-Driven CMOS Cascode Amplifier 6.2.3 Improving the Gain of the CMOS Cascode Amplifier 6.2.4 The BJT Cascode Amplifier Differential Amplifiers 6.3.1 CMOS Differential Amplifiers 6.3.2 BJT Differential Amplifiers 6.3.3 Frequency Response of Differential Amplifiers 6.3.4 Noise Performance of Differential Amplifiers . Output Amplifiers 6.4.1 Output Amplifiers without Feedback 6.4.2 Output Amplifiers with Feedback Operational Amplifiers 6.5.1 Characterization of Op Amps 6.5.2 The BJT Two-Stage Op Amp 6.5.3 The CMOS Two-Stage Op Amp 6.5.4 Cascode Op Amps 6.5.5 Op Amps with an Output Stage 6.5.6 Simulation and Measurement of Op Amps

378

378 379 379 389 407 414 416 418 419 426 431 432 444 449 452 454 455 466 473 473 481 485 488 491 494

6.2

(^6.3

(J6.4 6.5

Vlll

CONTENTS

6.6

6.7

Comparators 6.6.1 Characterization of Comparators 6.6.2 High-Gain Comparators 6.6.3 Propagation Delay of Two-Stage Comparators 6.6.4 Comparators Using Positive Feedback 6.6.5 Autozeroing Summary References Problems Design Problems

499 499 502 507 511 514 518 518 519 524

7

7.0 7.1 7.2

Digital Circuits

Introduction Design Abstraction Characteristics of Digital Circuits 7.2.1 Logic Level Standards 7.2.2 Inverter Pair Characteristics 7.2.3 Logic Fan-out Characteristics 7.2.4 Digital Logic Analysis Single-Channel MOS Inverters . 7.3.1 Basic Inverter ' . 7.3.2 Inverter Device Sizing 7.3.3 Enhancement-Load versus Depletion-Load Inverters NMOS NOR and NAND Logic Circuits 7.4.1 Basic NMOS NOR Logic Circuits 7.4.2 Basic NMOS NAND Logic Circuits . 7.4.3 Multi-Input NAND and NOR Logic Circuits Complementary MOS Inverters . 7.5.1 A Basic CMOS Inverter 7.5.2 CMOS Inverter Logic Levels . 7.5.3 Inverter Device Sizing .. CMOS Logic Gates 7.6.1 CMOS NOR Logic Gate 7.6.2 CMOS NAND Logic Gate ' 7.6.3 Multi-Input CMOS Logic Gates Transmission Gates 7.7.1 NMOS Pass Transistor 7.7.2 CMOS Transmission Gate Signal Propagation Delays 7.8.1 Ratio-Logic Model " 7.8.2 Process Characteristic Time Constant 7.8.3 Inverter-Pair Delay 7.8.4 Superbuffers ' 7.8.5 NMOS NAND and NOR Delays 7.8.6 Enhancement versus Depletion Loads 7.8.7 CMOS Logic Delays 7.8.8 Interconnection Characteristics Capacitive Loading Considerations 7.9.1 Capacitive Loading 7.9.2 Logic Fan-out Delays .

525

525 526 528 528 530 532 532 534 534 537 539 540 540 542 543 544 546 546 548 551 551 553 556 558 559 562 564 565 570 570 573 575 578 579 582 584 584 585

7.3

7.4

7.5

7.6

'

7.7 7.8

7.9

CONTENTS

IX

7.10 7.11

7.12

7.9.3 Distributed Drivers 7.9.4 Driving Off-Chip Loads 7.9.5 Cascaded Drivers Power Dissipation 7.10.1 NMOS Power Dissipation 7.10.2 CMOS Power Dissipation Noise in Digital Logic Circuits 7.11.1 Resistive Noise Coupling 7.11.2 Capacitive Noise Coupling 7.11.3 Definition of Noise Margins 7.11.4 NMOS Noise Margins 7.11.5 CMOS Noise Margins Summary References Problems

587 588 590 593 595 597 599 599 601 602 603 605 607 608 608

8

8.0 8.1 8.2

Analog Systems

Introduction Analog Signal Processing Digital-to-Analog Converters 8.2.1 Current-Scaling D/A Converters 8.2.2 Voltage-Scaling D/A Converters 8.2.3 Charge-Scaling D/A Converters 8.2.4 D/A Converters Using Combinations of Scaling Approaches 8.2.5 Serial D/A Converters Analog-to-Digital Converters 8.3.1 Serial A/D Converters 8.3.2 Successive Approximation A/D Converters 8.3.3 Parallel A/D Converters 8.3.4 High-Performance A/D Converters 8.3.5 Summary Continuous-Time Filters 8.4.1 Low-Pass Filters 8.4.2 High-Pass Filters 8.4.3 Bandpass Filters Switched Capacitor Filters 8.5.1 Resistor Realization 8.5.2 Passive RLC Prototype Switched Capacitor Filters 8.5.3 Z-Domain Synthesis Techniques Analog Signal Processing Circuits 8.6.1 Precision Breakpoint Circuits 8.6.2 Modulators and Multipliers 8.6.3 Oscillators 8.6.4 Phase-Locked Loops Summary References Problems

612

612 612 615 623 626 629 633 638 642 648 651 659 664 671 673 674 685 688 692 693 703 716 729 729 735 747 762 765 770 773

8.3

8.4

8.5

8.6

8.7

9

9.0 9.1

Structured Digital Circuits and Systems

Introduction Random Logic versus Structured Logic Forms

778

778 779

CONTENTS

9.2

9.3 9.4 9.5 9.6

9.7

9.8 9.9 9.10 9.11 9.12 9.13 9.14 9.15

9.16

9.17

Programmable Logic Arrays 9.2.1 PLA Organization 9.2.2 Automatic PLA Generation 9.2.3 Folded PLAs 9.2.4 Large PLAs Structured Gate Layout 9.3.1 Weinberger Arrays 9.3.2 Gate Matrix Layout Logic Gate Arrays MOS Clocking Schemes Dynamic MOS Storage Circuits 9.6.1 Dynamic Charge Storage 9.6.2 Simple Shift Register 9.6.3 Other Shift Registers Clocked CMOS Logic 9.7.1 C2MOS 9.7.2 Precharge-Evaluate Logic 9.7.3 Domino CMOS Semiconductor Memories 9.8.1 Memory Organization Read-Only Memory 9.9.1 Erasable Programmable Read-Only Memory 9.9.2 Electrically Erasable Programmable Read-Only Memory Static RAM Memories Dynamic RAM Memory Register Storage Circuits 9.12.1 Quasi-Static Register Cells 9.12.2 A Static Register Cell PLA-Based Finite-State Machines Microco'ded Controllers Microprocessor Design 9.15.1 Data Path Description 9.15.2 Barrel Shifter 9.15.3 Arithmetic Logic Unit 9.15.4 Microcoded Controller Systolic Arrays 9.16.1 Systolic Matrix Multiplication 9.16.2 General Linear System Solver 9.16.3 Bit-Serial Processing Elements Summary References Problems

783 784 790 791 792 793 794 796 799 805 808 808 811 814 815 815 817 819 821 822 824 825 826 827 835 839 840 842 845 848 853 856 857 858 860 861 861 862 863 866 866 867

10

10.0 10.1 10.2

Design Automation and Verification

Introduction Integrated Circuit Layout 10.1.1 Geometrical Specification Languages 10.1.2 Layout Styles Symbolic Circuit Representation 10.2.1 Parameterized Layout Representation 10.2.2 Parameterized Module Generation

872

872 873 875 878 880 880 883

CONTENTS

XI

10.3 10.4

10.5

10.6 10.7

10.8 10.9

10.10

10.11

10.12

10.2.3 Graphical Symbolic Layout 10.2.4 Logic Equation Symbology Computer Check Plots Design Rule Checks 10.4.1 Geometrical Design Rules 10.4.2 Computer Design Rule Checks 10.4.3 Design Rule Checker Output Circuit Extraction 10.5.1 A Simple Circuit Extraction Algorithm 10.5.2 Circuit Extractor Output 10.5.3 Interface to Other Programs Digital Circuit Simulation Logic and Switch Simulation 10.7.1 Logic-level Simulation 10.7.2 Switch-level Simulation 10.7.3 Hardware Logic Simulation Timing Analysis 10.8.1 Timing Analysis Methodology 10.8.2 Timing Analysis Tools Register-Transfer-Level Simulation 10.9.1 Simple RTL 10.9.2 ISPS Specification and Simulation 10.9.3 RTL Simulation with LISP Hardware Design Languages 10.10.1 EDIF Design Description 10.10.2 EDIF Net List View of Full Adder 10.10.3 EDIF Mask Layout View of Full Adder 10.10.4 VHDL Design Description Algorithmic Layout Generation 10.11.1 Bristle Blocks Silicon Compiler 10.11.2 MacPitts Silicon Compiler 10.11.3 Commercial Silicon Compilers Summary References Problems

884 885 889 894 894 897 898 901 902 903 908 908 909 909 913 917 918 918 919 923 923 925 926 929 930 931 931 935 938 938 941 943 944 945 946

Index

951

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Basic Computer ConceptsDocument77 pagesBasic Computer ConceptsJerry Mugambi100% (1)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- GRC Fiori End User Guide Final - V2Document75 pagesGRC Fiori End User Guide Final - V2Subhash BharmappaNo ratings yet

- InductorsDocument13 pagesInductorsManish AnandNo ratings yet

- System Engineering Management Plan (SEMPDocument2 pagesSystem Engineering Management Plan (SEMPKatie WestNo ratings yet

- How To Choose Food StarchesDocument20 pagesHow To Choose Food StarchesBoat Tanin100% (3)

- CCTV Camera Hack With Google Dork ListDocument3 pagesCCTV Camera Hack With Google Dork ListsarahdianewhalenNo ratings yet

- Mathcad - Ampacity CalculationDocument76 pagesMathcad - Ampacity CalculationAlex Ribeiro100% (4)

- Raft Foundations - Design & Analysis With A Practical Approach PDFDocument140 pagesRaft Foundations - Design & Analysis With A Practical Approach PDFemmanuel83% (6)

- Turkle Sherry What Does Simulation Want PDFDocument11 pagesTurkle Sherry What Does Simulation Want PDFmonterojuNo ratings yet

- Services Marketing: Consumer Behavior in Services Unit 2Document78 pagesServices Marketing: Consumer Behavior in Services Unit 2mpsrishaNo ratings yet

- SoundDocument1 pageSoundMichelle Celeste BatuNo ratings yet

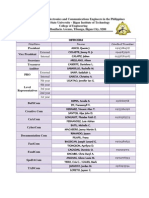

- ECE 117 FinalfinalDocument30 pagesECE 117 FinalfinalMichelle Celeste BatuNo ratings yet

- ECE 117 FinalfinalDocument30 pagesECE 117 FinalfinalMichelle Celeste BatuNo ratings yet

- JIECEP OfficersDocument2 pagesJIECEP OfficersMichelle Celeste BatuNo ratings yet

- Batu BSECE-5 ECE-195 Resistor Layout and DRC/LVS ResultsDocument3 pagesBatu BSECE-5 ECE-195 Resistor Layout and DRC/LVS ResultsMichelle Celeste BatuNo ratings yet

- Level ShifterDocument1 pageLevel ShifterMichelle Celeste BatuNo ratings yet

- Astral Column Pipe PricelistDocument4 pagesAstral Column Pipe PricelistVaishamNo ratings yet

- DC Motor Direction Control ReportDocument6 pagesDC Motor Direction Control ReportEngr Farhanullah SarkiNo ratings yet

- X-Span & Setting ToolsDocument18 pagesX-Span & Setting ToolsDenier RubianoNo ratings yet

- Product Data Sheet: Linear Switch - iSSW - 2 C/O - 20A - 250 V AC - 3 PositionsDocument2 pagesProduct Data Sheet: Linear Switch - iSSW - 2 C/O - 20A - 250 V AC - 3 PositionsMR. TNo ratings yet

- Admin Interview Questions and Answers - Robert HalfDocument2 pagesAdmin Interview Questions and Answers - Robert HalfWaqqas AhmadNo ratings yet

- Enclosed Product Catalogue 2012Document24 pagesEnclosed Product Catalogue 2012Jon BerryNo ratings yet

- 38.11 Cum Total Qty of 4 Nos. Culvests 38.11x4 152.43 CumDocument14 pages38.11 Cum Total Qty of 4 Nos. Culvests 38.11x4 152.43 CumMandeep SinghNo ratings yet

- Questionnaire For Future BLICZerDocument1 pageQuestionnaire For Future BLICZerAlejandra GheorghiuNo ratings yet

- FiatDocument56 pagesFiatOmkar ParkarNo ratings yet

- Pink Fun Doodles and Blobs Math Online Class Creative Presentation SlidesCarnivalDocument28 pagesPink Fun Doodles and Blobs Math Online Class Creative Presentation SlidesCarnivalraine castorNo ratings yet

- CV Ali EzzeddineDocument3 pagesCV Ali EzzeddineOmar RajadNo ratings yet

- Dealer FeedbackDocument3 pagesDealer FeedbackTarun BhatiNo ratings yet

- Zhao PeiDocument153 pagesZhao PeiMuhammad Haris HamayunNo ratings yet

- Template Icme 13 PosterDocument1 pageTemplate Icme 13 PosterZulma Xiomara Rueda GarciaNo ratings yet

- RELAY SEEDER PROTECTION GUIDE (P40 Agile CompactDocument23 pagesRELAY SEEDER PROTECTION GUIDE (P40 Agile CompactvinodlifeNo ratings yet

- Brake Pedals and ValveDocument4 pagesBrake Pedals and Valveala17No ratings yet

- Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 SeriesDocument3 pagesMobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 SeriesMudabbir Shan AhmedNo ratings yet

- Safety Training Evaluation Form: Instructor RatingDocument1 pageSafety Training Evaluation Form: Instructor RatingNate JamesNo ratings yet

- Panasonic WJ FS616Document62 pagesPanasonic WJ FS616triliteNo ratings yet

- Allcargo Corporate BrochureDocument12 pagesAllcargo Corporate BrochureallinonecargologisticsNo ratings yet