Professional Documents

Culture Documents

HD74LS83A

Uploaded by

Jorman Cristopher Amaya AvilezOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HD74LS83A

Uploaded by

Jorman Cristopher Amaya AvilezCopyright:

Available Formats

HD74LS83A

4-bit Binary Full Adder (with Fast Carry)

REJ03D04200200 Rev.2.00 Feb.18.2005 This improved full adder performs the addition of two 4-bit binary numbers. The sum () outputs are provided for each bit and the resultant carry (C4) is obtained from the fourth bit. This adder features full internal look ahead across all four bit generating the carry term in ten nanoseconds typically. This provides the system designer with partial lookahead performance at the economy and reduced package count of a ripple-carry implementation.

Features

Ordering Information

Part Name HD74LS83AP Package Type DILP-16 pin Package Code (Previous Code) PRDP0016AE-B (DP-16FV) Package Abbreviation P Taping Abbreviation (Quantity)

Note: Please consult the sales office for the above package availability.

Pin Arrangement

A4 3 A3 B3 VCC 2 B2 A2

1 2 3 4 5 6 7 8 2 B2 A2 1 B1 A1 3 A3 B3 A4 B4 4 C4 C0

16 15 14 13 12 11 10 9

B4 4 C4 C0 GND B1 A1 1

(Top view)

Rev.2.00, Feb.18.2005, page 1 of 7

HD74LS83A

Function Table

Input A1 A3 L H L H L H L H L H L H L H L L H H L L H H L L H H L L B1 B3 L L L L H H H H L L L L H H A2 A4 L L L L L L L L H H H H H H B2 B4 L H H L L H H L L H H L L H When C0 = L 1 3 L L L H H H H L H H H L L L 2 Output When C0 = H When C2 = L C2 1 2 4 C4 3 L H L L L L L H L H L L L L H H L H L L L L H H H H H L

L H H H H L L L H L L L L H

When C2 = H C2 4 C4 L L L L L H H H L H H H H H

L H H H H L H L H H H H H H L H H H H H H; high level, L; low level, X; irrelevant Note: Input conditions at A1, B1, A2, B2, and C0 are used to determine outputs 1 and 2 and the value of the internal carry C2. The value at C2, A3, B3, A4, and B4 are than used to determine outputs 3, 4 and C4.

Rev.2.00, Feb.18.2005, page 2 of 7

HD74LS83A

Block Diagram

C4

B4 A4 4

B3 A3 3

B2 A2 2

B1 A1 C0 1

Absolute Maximum Ratings

Item Supply voltage Input voltage Power dissipation Storage temperature Symbol VCC VIN PT Tstg Ratings 7 7 400 65 to +150 Unit V V mW C

Note: Voltage value, unless otherwise noted, are with respect to network ground terminal.

Recommended Operating Conditions

Item Supply voltage Output current Operating temperature Symbol VCC IOH IOL Topr Min 4.75 20 Typ 5.00 25 Max 5.25 400 8 75 Unit V A mA C

Rev.2.00, Feb.18.2005, page 3 of 7

HD74LS83A

Electrical Characteristics

(Ta = 20 to +75 C)

Item Input voltage Symbol VIH VIL VOH min. 2.0 2.7 20 Supply current ICC Input clamp voltage VIR Note: * VCC = 5 V, Ta = 25C typ.* 22 19 19 max. 0.8 0.4 0.5 40 20 0.8 0.4 0.2 0.1 100 39 34 34 1.5 V mA Unit V V V Condition

Output voltage VOL except C0 C0 except C0 C0 except C0 C0 Short-circuit output current IIH IIL II IOS

V A mA mA mA

VCC = 4.75 V, VIH = 2 V, VIL = 0.8 V, IOH = 400 A IOL = 4 mA VCC = 4.75 V, VIH = 2 V, VIL = 0.8 V IOL = 8 mA VCC = 5.25 V, VI = 2.7 V VCC = 5.25 V, VI = 0.4 V VCC = 5.25 V, VI = 7 V VCC = 5.25 V All inputs = 0 V B input = 0.8 V, Other inputs 4.5 V All inputs = 4.5 V VCC = 4.75 V, IIN = 18 mA VCC = 5.25 V

Input current

Switching Characteristics

(VCC = 5 V, Ta = 25C)

Item Symbol tPLH tPHL tPLH tPHL tPLH tPHL tPLH tPHL Inputs CO Ai, Bi CO Ai, Bi Outputs 1 1 C4 C4 min. typ. 16 15 15 15 11 15 11 12 max. 24 24 24 24 17 22 17 17 Unit Condition

Propagation delay time

ns

CL = 15 pF, RL = 2 k

Rev.2.00, Feb.18.2005, page 4 of 7

HD74LS83A

Testing Method

Test Circuit

VCC 4.5V RL C4 A4 Input B4 Output 4 Output 3 Output 1 Output 1 Same as Load Circuit 1. Same as Load Circuit 1. Same as Load Circuit 1. Same as Load Circuit 1. A3 B3 A2 B2 A1 B2 C0 CL Output

Load circuit 1

P.G. Zout = 50

Notes:

1. CL includes probe and jig capacitance. 2. All diodes are 1S2074(H).

Waveform

tTLH 90% 1.3 V 10% tPLH tTHL 90% 1.3 V 10% tPHL 3V 0V

Input

See Testing Table

VOH In phase output tPHL 1.3 V tPLH VOH Out of phase output 1.3 V 1.3 V VOL 1.3 V VOL

Note:

Input pulse; tTLH 15 ns, tTHL 6 ns, PRR = 1 MHz, duty cycle = 50%

Rev.2.00, Feb.18.2005, page 5 of 7

HD74LS83A Testing Table

Item From input to output CO i or C4 B4 GND GND GND GND GND tPLH tPHL GND IN GND GND GND 4.5 v IN A4 GND GND GND GND GND IN GND GND GND GND IN 4.5 v B3 GND GND GND GND GND IN GND GND GND 4.5 v IN GND A3 GND 4.5 v GND GND IN GND GND GND GND IN 4.5 v GND Input B2 GND GND GND GND IN GND GND GND 4.5 v IN GND GND A2 GND 4.5 v GND IN GND GND GND GND IN 4.5 v GND GND B1 GND GND GND IN GND GND GND 4.5 v IN GND GND GND A1 GND 4.5 v IN GND GND GND GND IN 4.5 v GND GND GND C0 IN IN GND GND GND GND GND GND GND GND C4 OUT OUT 4 OUT OUT OUT OUT Output 3 2 OUT OUT OUT OUT OUT OUT OUT OUT 1 OUT OUT OUT OUT

Ai or Bi i or C4

Rev.2.00, Feb.18.2005, page 6 of 7

HD74LS83A

Package Dimensions

JEITA Package Code P-DIP16-6.3x19.2-2.54 RENESAS Code PRDP0016AE-B Previous Code DP-16FV MASS[Typ.] 1.05g

16

1 0.89 b3

A1

Reference Symbol

Dimension in Millimeters Min Nom 7.62 19.2 6.3 20.32 7.4 5.06 0.51 0.40 0.48 1.30 0.19 0 2.29 2.54 0.25 0.31 15 2.79 1.12 2.54 0.56 Max

e D E

L

A A1

bp

e1

b c b c

p 3

e Z ( Ni/Pd/Au plating ) L

Rev.2.00, Feb.18.2005, page 7 of 7

Sales Strategic Planning Div.

Keep safety first in your circuit designs!

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap. Notes regarding these materials 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party. 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials. 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors. Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com). 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein. 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use. 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials. 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited. 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

RENESAS SALES OFFICES

Refer to "http://www.renesas.com/en/network" for the latest and detailed information. Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501 Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900 Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071 Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999 Renesas Technology (Shanghai) Co., Ltd. Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, China Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952 Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

http://www.renesas.com

2005. Renesas Technology Corp., All rights reserved. Printed in Japan.

Colophon .2.0

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Stp5N105K5: N-Channel 1050 V, 2.9 Ω Typ., 3 A Mdmesh™ K5 Power Mosfet In A To-220 PackageDocument15 pagesStp5N105K5: N-Channel 1050 V, 2.9 Ω Typ., 3 A Mdmesh™ K5 Power Mosfet In A To-220 PackageJorman Cristopher Amaya AvilezNo ratings yet

- STP2N80 STP2N80FI: N - Channel Enhancement Mode Power Mos TransistorDocument10 pagesSTP2N80 STP2N80FI: N - Channel Enhancement Mode Power Mos TransistorscribdsteNo ratings yet

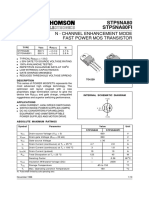

- STP5NA80 Stp5Na80Fi: N - Channel Enhancement Mode Fast Power Mos TransistorDocument11 pagesSTP5NA80 Stp5Na80Fi: N - Channel Enhancement Mode Fast Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

- STB57N65M5, STF57N65M5, Sti57n65m5, STP57N65M5Document23 pagesSTB57N65M5, STF57N65M5, Sti57n65m5, STP57N65M5Jorman Cristopher Amaya AvilezNo ratings yet

- STP2N80 STP2N80FI: N - Channel Enhancement Mode Power Mos TransistorDocument10 pagesSTP2N80 STP2N80FI: N - Channel Enhancement Mode Power Mos TransistorscribdsteNo ratings yet

- Stp52N25M5: N-Channel 250 V, 0.055, 28 A, To-220 Mdmesh V Power MosfetDocument13 pagesStp52N25M5: N-Channel 250 V, 0.055, 28 A, To-220 Mdmesh V Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- STP53N08: N - Channel Enhancement Mode Power Mos TransistorDocument6 pagesSTP53N08: N - Channel Enhancement Mode Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

- STP50N06 STP50N06FI: N - Channel Enhancement Mode Power Mos TransistorDocument11 pagesSTP50N06 STP50N06FI: N - Channel Enhancement Mode Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

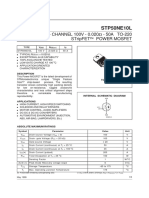

- Stp50Ne10: N - Channel 100V - 0.021 - 50A To-220 Stripfet Power MosfetDocument9 pagesStp50Ne10: N - Channel 100V - 0.021 - 50A To-220 Stripfet Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stb50Nf25 Stp50Nf25: N-Channel 250V - 0.055 - 45A - D Pak - To-220 Low Gate Charge Stripfet™ Power MosfetDocument15 pagesStb50Nf25 Stp50Nf25: N-Channel 250V - 0.055 - 45A - D Pak - To-220 Low Gate Charge Stripfet™ Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- DSDocument8 pagesDSJorman Cristopher Amaya AvilezNo ratings yet

- Stp50Ne10: N - Channel 100V - 0.021 - 50A To-220 Stripfet Power MosfetDocument9 pagesStp50Ne10: N - Channel 100V - 0.021 - 50A To-220 Stripfet Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stp50Ne10L: N - Channel 100V - 0.020 - 50A To-220 Stripfet Power MosfetDocument9 pagesStp50Ne10L: N - Channel 100V - 0.020 - 50A To-220 Stripfet Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stb50Nf25 Stp50Nf25: N-Channel 250V - 0.055 - 45A - D Pak - To-220 Low Gate Charge Stripfet™ Power MosfetDocument15 pagesStb50Nf25 Stp50Nf25: N-Channel 250V - 0.055 - 45A - D Pak - To-220 Low Gate Charge Stripfet™ Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

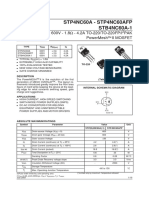

- Stp4Nc60 - Stp4Nc60Fp Stb4Nc60-1: N-Channel 600V - 1.8 - 4.2A To-220/To-220Fp/I Pak Powermesh™Ii MosfetDocument11 pagesStp4Nc60 - Stp4Nc60Fp Stb4Nc60-1: N-Channel 600V - 1.8 - 4.2A To-220/To-220Fp/I Pak Powermesh™Ii MosfetJorman Cristopher Amaya AvilezNo ratings yet

- 4NK60ZFP DatasheetDocument16 pages4NK60ZFP DatasheetrpaqrvNo ratings yet

- Stp4Nc60A - Stp4Nc60Afp Stb4Nc60A-1: N-Channel 600V - 1.8 - 4.2A To-220/To-220Fp/I Pak Powermesh Ii MosfetDocument11 pagesStp4Nc60A - Stp4Nc60Afp Stb4Nc60A-1: N-Channel 600V - 1.8 - 4.2A To-220/To-220Fp/I Pak Powermesh Ii MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stp4Nm60 Std3Nm60 - Std3Nm60-1: N-Channel 600V - 1.3 - 3A To-220/Dpak/Ipak Zener-Protected Mdmesh™Power MosfetDocument13 pagesStp4Nm60 Std3Nm60 - Std3Nm60-1: N-Channel 600V - 1.3 - 3A To-220/Dpak/Ipak Zener-Protected Mdmesh™Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- STD4N52K3, STF4N52K3, STP4N52K3, Stu4n52k3Document22 pagesSTD4N52K3, STF4N52K3, STP4N52K3, Stu4n52k3Jorman Cristopher Amaya AvilezNo ratings yet

- 1Document6 pages1Jorman Cristopher Amaya AvilezNo ratings yet

- Stp4Nc50 Stp4Nc50Fp: N-Channel 500V - 2.2 - 3.5A To-220/To-220Fp Powermesh Ii MosfetDocument10 pagesStp4Nc50 Stp4Nc50Fp: N-Channel 500V - 2.2 - 3.5A To-220/To-220Fp Powermesh Ii MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stp50Ne10L: N - Channel 100V - 0.020 - 50A To-220 Stripfet Power MosfetDocument9 pagesStp50Ne10L: N - Channel 100V - 0.020 - 50A To-220 Stripfet Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stp4Nb50 Stp4Nb50Fp: N - Channel Enhancement Mode Powermesh MosfetDocument8 pagesStp4Nb50 Stp4Nb50Fp: N - Channel Enhancement Mode Powermesh MosfetJorman Cristopher Amaya AvilezNo ratings yet

- STP3N100 STP3N100FI: N - Channel Enhancement Mode Power Mos TransistorDocument11 pagesSTP3N100 STP3N100FI: N - Channel Enhancement Mode Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

- BC548 Hoja de Datos PDFDocument5 pagesBC548 Hoja de Datos PDFJuan FiNo ratings yet

- STP36N06L STP36N06LFI: N - Channel Enhancement Mode Power Mos TransistorDocument11 pagesSTP36N06L STP36N06LFI: N - Channel Enhancement Mode Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

- C 32725Document4 pagesC 32725Hannibal Zeugon ZǝnƃouNo ratings yet

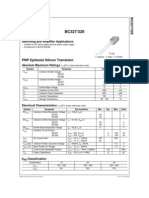

- PNP Silicon Planar Medium Power Transistor: Absolute Maximum RatingsDocument2 pagesPNP Silicon Planar Medium Power Transistor: Absolute Maximum RatingsJorman Cristopher Amaya AvilezNo ratings yet

- Darlington Transistors BC517: NPN SiliconDocument9 pagesDarlington Transistors BC517: NPN SiliconJhonny Mamani LópezNo ratings yet

- Data Sheet: PNP Darlington TransistorDocument9 pagesData Sheet: PNP Darlington TransistorJorman Cristopher Amaya AvilezNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Field Devices - Flow: Log oDocument16 pagesField Devices - Flow: Log osalmo83:18No ratings yet

- Practical Circuits: Exercise 12.2 Using the Internal Resistance EquationsDocument2 pagesPractical Circuits: Exercise 12.2 Using the Internal Resistance EquationsKaren MartinNo ratings yet

- Lecture 2 Is in The EnterpriseDocument44 pagesLecture 2 Is in The EnterpriseAludahNo ratings yet

- Multitrack HistoryDocument5 pagesMultitrack HistoryMatt GoochNo ratings yet

- Packer Conveyor1 PDFDocument77 pagesPacker Conveyor1 PDFĐoàn Ngọc ĐạiNo ratings yet

- Piaggio Mp3 400 I.E Service Station Manual-7Document20 pagesPiaggio Mp3 400 I.E Service Station Manual-7H. KeithNo ratings yet

- UI Design vs UX Design: Key Differences ExplainedDocument9 pagesUI Design vs UX Design: Key Differences ExplainedHuzaifa qureshiNo ratings yet

- 0092 Adobe Photoshop TutorialDocument40 pages0092 Adobe Photoshop TutorialAnandChhetriNo ratings yet

- Essailec® Test BlocksDocument68 pagesEssailec® Test BlocksPhong DuongNo ratings yet

- Python Modes and OperatorsDocument27 pagesPython Modes and OperatorsTejas BhagitNo ratings yet

- Equipment Master in SAP PMDocument6 pagesEquipment Master in SAP PMMarco Antônio Claret TeixeiraNo ratings yet

- Manager Director CTO Telecommunications in Denver CO Resume Bruce RotvoldDocument4 pagesManager Director CTO Telecommunications in Denver CO Resume Bruce RotvoldBruceRotvoldNo ratings yet

- Simulation and Implementation of A BPSK Modulator On FPGADocument14 pagesSimulation and Implementation of A BPSK Modulator On FPGAAnonymous 01LLHnZTSNo ratings yet

- Road Safety Strategy: Dr. Md. Jahir Bin AlamDocument18 pagesRoad Safety Strategy: Dr. Md. Jahir Bin AlamMd Habibur RahmanNo ratings yet

- CPH Micro Project PDFDocument10 pagesCPH Micro Project PDFAbhay PotdarNo ratings yet

- Memory Bites PDFDocument353 pagesMemory Bites PDFAli Aydin100% (1)

- Diagnostics - 2 On Board Diagnostics II SystemDocument338 pagesDiagnostics - 2 On Board Diagnostics II SystemJoão Gabriel B AbrantesNo ratings yet

- HMK12AA Product Specification and Performance DataDocument4 pagesHMK12AA Product Specification and Performance DataMarcos EvansNo ratings yet

- Dancing Robots Now On Duty at San Jose International AirportDocument3 pagesDancing Robots Now On Duty at San Jose International Airportapi-358751761No ratings yet

- Epson L1300 A3 Colour Inkjet Tank System Printer DatasheetDocument2 pagesEpson L1300 A3 Colour Inkjet Tank System Printer DatasheetWebAntics.com Online Shopping StoreNo ratings yet

- 02 FT48992EN04GLA0 Safety and Bef StarDocument24 pages02 FT48992EN04GLA0 Safety and Bef StarLkLukkeNo ratings yet

- Designing For Payload Modularity: Richard Drake Mr. Jeff OwenDocument7 pagesDesigning For Payload Modularity: Richard Drake Mr. Jeff Owensalman GtrNo ratings yet

- JLG 153-12Document2 pagesJLG 153-12Luis Vélez RomàNo ratings yet

- EEI's 80 Years of Construction ExcellenceDocument32 pagesEEI's 80 Years of Construction ExcellenceDiana Mae LomentigarNo ratings yet

- The Evolution of Steering WheelsDocument2 pagesThe Evolution of Steering WheelsAmogus MogusNo ratings yet

- FM Global Property Loss Prevention Data Sheets: List of FiguresDocument25 pagesFM Global Property Loss Prevention Data Sheets: List of Figureskw teoNo ratings yet

- Project Management With Pert & CPMDocument26 pagesProject Management With Pert & CPML'HOMME Business PlanNo ratings yet

- ECE 6130/4130: Advance VLSI Systems: Combinational Logic Styles: Part-II Dynamic Logic Other StylesDocument26 pagesECE 6130/4130: Advance VLSI Systems: Combinational Logic Styles: Part-II Dynamic Logic Other StylesRupesh ParabNo ratings yet

- Ee303 QuarterlysyllabusDocument2 pagesEe303 QuarterlysyllabusDin Mark AngelesNo ratings yet

- Validation Based ProtocolDocument7 pagesValidation Based ProtocolTerimaaNo ratings yet