Professional Documents

Culture Documents

A Phase-Frequency-Locked Controller For Stepping Servo Control Systems

Uploaded by

hamsaxyzOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Phase-Frequency-Locked Controller For Stepping Servo Control Systems

Uploaded by

hamsaxyzCopyright:

Available Formats

I12

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 39, NO. 2 , APRIL 1992

A Phase/Frequency-Locked Controller for Stepping Servo Control Systems

Jung-Chien Li and Guan-Chyun Hsieh, Member, IEEE

Abstract-A phase-controlled oscillator (PCO), composed of an adaptive digital-pumped controller (ADPC) and a voltagecontrolled oscillator (VCO), is proposed as a novel stepping motor driver. Therefore, a phase-locked stepping servomechanism (PLSS) is established and the PCO can provide an accurate and stable pulse train to adaptively drive the stepping motor. System modeling, analysis, stability investigation, design, and implementation are all conducted. Computer simulation and experiment result indicate that the performance of the PLSS is close to the theoretical prediction. Some speed responses for 40-1000 r/min are examined in the real PLSS. A good speed regulation of kO.15 r/min is achieved. An adaptive line density selector can be used to improve the system performance.

I. INTRODUCTION ECENTLY the stepping servomechanism plays an important role due to the demand for speed and position control. It performs especially well in the low-speed range. The driving signal for the stepping motor is a train of pulses, which is easily combined with the digital system. The development of the microprocessor makes this servo system perform better. However, most of the control strategies up to date usually use the digital code as the reference input. In order to achieve a better and more reliable performance, the controller design must be more complicated. This paper proposes a phase-controlled oscillator (PCO) as the controller for the phase-locked stepping servomechanism (PLSS), based on the phase-locked technique with real-time adaptive control capability. The PCO controller consists of an adaptive digital-pumped controller (ADPC) [4] and a voltage-controlled oscillator (VCO). The PCO provides a phase-locked range of [ - 2 n , 2n1, within which the associated train of pulses will be used as the driving signal for the PLSS. Because the PCO controller employs the multirate sampling technique with the linear quantization property, the speed of the servo system can be linearly and stably conManuscript received July 15, 1991; revised November 17, 1991. This work was supported by National Science Council, Taipei, Taiwan, R.O.C. Project no. NSC79-0404-E011-17. J.-C. Li is with the Department of Electronic Engineering, National Taiwan Ocean University, Keelung, Taiwan, R.O.C. G.-C. Hsieh is with the Department of Electronic Engineering, National Taiwan Institute of Technology, Taipei, Taiwan, R.O.C. IEEE Log Number 9106875.

trolled. Because the phase-locked technique can provide a very wide lock-in range, the VCO does not have to provide a constant control profile. It can adaptively provide the optimum control signal. This phase-locked servo system proves to be adaptive, accurate, reliable, and practical. jump The parameters considered are multisampling rate N, voltage P, sampling period T , and VCO gain K,. This paper employs the Laplace and z transformations for PLSS simulation and analysis [ 5 ] . In stability analysis, the system is complicated since the stepping motor is at least of second order. Consequently, the computer-aided graphical method can be used for controller design. We propose a practical example to verify the simulation result. The speed range of the presented PLSS lies in 40-1000 r/min where a speed regulation of f0.15 r/min is achieved. It is obvious that this system contributes to the low-speed range. It is also confirmed that the digital phase-locked technique [l], [4] can be satisfactorily applied to motor speed control.

11. BASIC SCHEME OF

THE

PCO

Fig. 1 shows the PCO in the PLSS. The PCO consists of an ADPC and a VCO so that the driving frequency for the stepping motor is proportional to the phase error. The detailed ADPC scheme can be seen in [4]. If the VCO operates in the linear region, it can be viewed as a constant gain K,. From [4], we have the mathematical model of the ADPC as

T= T I N

8, is the phase error, and V, is the output voltage of the ADPC. 111. MODELING THE STEPPING OF MOTOR From [lo], we have

0278-0046/92$03.00

0 1992 IEEE

LI AND HSIEH: A PHASEIFREQUENCY-LOCKED CONTROLLER

1 I3

r - - - - - - - - - - - - - - - -- 7

wiroi

Phase-Controlled Oscillator, PCO

I I *

Phase Adaptive Digital-Pump--t

I

VCO

1 Stepping ,

Motor

em,

Fig. 1. PCO in the PLSS

where

(5)

k,

-+

0 leads to

With the

z transformation, we obtain

=A

--

GH( Z ) D

L,z2

+ L2z+ L, + cET

(9)

( z - 1 ) ( z 2- 2 D c o s ( E T ) z + D 2 )

Since the real pole s = - r / Lp lies in the negative U axis far from the origin, its effect can be neglected. Thus, (4) can be simplified as

-%(S)

-

L , = 2 b D E c o s ( E T ) - 2bE

+ 2 b2Dsin ( E T ) - cD sin ( E T )

L2 = 2bE - ~ c D E T c o s ( E T ) 2bD2E -

4 ,

s2

4 s )

+ -s

D

J

4 b 2 Dsin ( E T ) + 2 CDsin ( E T ) (IO)

L,

cD2ET + 2 bD2E - 2 bDE COS ( E T )

Equation (5) may be rewritten as

-4 s

+ 2 b2Dsin ( E T ) - cD sin ( E T ) .

The forward gain is (6)

G(s) =

(1 1)

) -

Km

s2 + 2bs + c

&(s)

where

TNPK,K, 2a

1 - epsT

s(s2

+ 2bs + C ) .

(12)

With the

transformation, we obtain

=the parameter related to the rotational inertia and viscous braking coefficient. C =the magnetic and electric parameter. Km/c =the dc gain of the stepping motor, including the 27r factor. f; =the input frequency. U, =the output speed.

IV. MATHEMATICAL Analysis of the PLSS

G ( z )= -

NJ +N 2 z 2 - 2 D c o s ( E T ) z + D2

where

N,= E

DE cos ( E T ) - bD sin ( E T )

(14)

N2 = D2E - DE cos ( E T )

+ bD sin ( E T ) .

(15)

Thus, the closed-loop transfer function will be

Suppose that the system is in the steady state with small phase error, i.e., in the phase-locked range. The linear equivalent model can then be derived as Fig. 2 [4], where n is the line density of the optical encoder, which denotes the number of pulses produced by the optical encoder during one revolution of the stepping motor. From Fig. 2, we have the loop gain

T ( z ) = -- 1 + G H ( z ) d,(z)

-

4 2)

G (4

A C ( Z 1) -

n

where

N,z

Z3

+ N2

QzZ

e 3

+ Qiz2

nTNPK,K,

1-

epsT

Q , = 2 AbDE cos ( E T ) + AcET

+ 2 A b 2 D sin ( E T )

GH(s)=

2n

s2(s2+ 2bs

+ C)

(7)

2 A b E - A c D s i n ( E T ) - 2 D c o s ( E T ) - 1 (17)

114

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 39, NO. 2 , APRIL 1992

Fig. 2.

Linear equivalent model of the PLSS.

Q2 = 2 AbE - 2 AcDETcos ( E T ) - 4 A b 2 D sin ( E T )

where

+ D 2 - 2 AbD2E + 2 AcD sin ( E T ) + 2 D cos ( E T )

(18)

U,

2 - BcE/nw -4BbD2E

- BcD2E/nw

[ BcDEcos ( E / n w ) ] / n w

Q3= 2 AbD2E - D 2 - 2 AbDE cos ( E T )

+ AcD2ET + 2 A b 2 D sin ( E T ) - AcD sin ( E T )

and

(19)

+ 2D2 + 4BbE + 4 0 cos ( E l n u ) -8Bb2Dsin(E/no) + 4BcDsin(E/nw)> 0

( B = NPK,K, / 2 c 2 E n w )

(25)

E = (e - b2) D A=

=

1/ 2

(20)

(21)

'

U, = 4 - BcE/nw

e-bT

+ 2BcDEcos ( E / n w ) / n w + 8BbD2E - 8BbDEcos ( E l n w ) + 3BcD2E/nw - 40'

(26)

n TNPK K , 2c2En

+ 8 B b 2 D s i n ( E / n w )- 4 B c D s i n ( E / n w ) > 0

Now consider the characteristic equation 1 which leads to

+ GH( z ) = 0 ,

U,

BcE/nw

+ [2BcDEcos ( E / n o ) ] / n w

z 3 + [ 2 A b D E c o s ( E T )- 2 A b E

+AcET

- 3BcD2E/nw - 4BbE + 2 - 4BbD2E + 2 D 2 - 4Dcos ( E l n u )

U,

=

+ 2 A b 2 D sin ( E T )

- AcD sin ( E T ) - 2 D cos ( E T ) - 11z 2

+8BbDEcos ( E l n w ) > 0 BcE/nw - [2BcDEcos ( E / n w ) ] / n w

(27) (28)

+ [2A b E - 2 AbD2E + D 2 - 2 AcDET cos ( E T ) -4Ab2Dsin(ET) + 2Dcos(ET)

+ BcD2E/nw > 0

U,U?

+ 2 AcD sin ( E T ) ]z

+ [ - D2 + 2 AbD2E - 2 AbDE cos ( E T ) +AcD2ET + 2 A b 2 D sin ( E T ) - AcD sin ( E T ) ]

= 0.

(23)

In order to consider the stability of the PLSS, we employ the bilinear transformation z = (1 s)/(l - s) with T = 2 n / n w and then apply the Routh-Hurwitz criterion. Therefore.

(29) For a given n , we can compute U,, U,, U,, U,, and U,U2- U,U, as functions of U . Using (25)-(29), we can determine U,,, above which the system is stable. Fig. 3 illustrates this computation for n = 200/32 = 6.25. It is clearly seen that U,," = 165 r/min for n = 6.25. Therefore, we can compute U,,, as a function of n for n = 6.25, 12.5, 25, 50, 100, and 200. Fig. 4 shows this result. It can be observed that the larger the line density n , the lower the minimum speed U,,, that ensures the stable operation. Now consider a phase ramp input O,(t) = Rtu,(t) for (16). From [ 5 ] , this is a type 1 system, and the steady-state error is

R ess = K,

u,q.

u0s3

+ U,? + u 2 s + U, = 0

(24)

LI AND HSIEH: A PHASEJFREQUENCY-LOCKED CONTROLLER

11s

0

-1 -2

-3 -4 -

-5

0 20

40

GO

00

100

120

140

1GO

I80

o (rpni)

Fig. 3 . Computation of

100

U,,,,"

for n

6.25

S t a b l e region

60

40

I!/,/,/

,

n

Fig. 4.

U,,,

versus n

where

K,

= - lim

T z-*1

[( z -

l ) G H ( z)]

A ( & + L + L3) 2 T[l + D 2- 2 D c o s ( E T ) ]

(3 1)

'

Constant steady-state phase error means zero steadystate speed error. V. PLSS DESIGN The objective of this system is to investigate the control of the motor speed. The stepping motor is a nonlinear device with high orders. This system contains computer software

and circuit hardware. The software is written by the Turbo C language. Its main functions include accept and display speed, read the speed, etc. As to the PCO controller, we may select the device and hardware design according to the specifications such as speed resolution, maximum overshoot, steadystate error, rise time, and settling time. Speed resolution is determined by the jump voltage P . The sensitivity of T(z) with respect to P is

where T(z)

N(z)/D(z)

c"X

from (16). T%en

s,T'z) =

z3 + [ - 1

2Dcos(ET)]z2

+ [ D 2 +2 D c o s ( E T ) ] z - D 2

z3 + Q,z2 + Q2z + Q3

(33)

I I6

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 39, NO. 2, APRIL 1992

The speed variation is directly affected by P. P must be selected for the motor input frequency to vary within f 3 Hz range. The product N P determines the maximum output voltage of the ADPC, which is normally between 5 and 30 V. In designing the PCO, the selection of N and P is very important. After the two parameters are determined according to the design procedure, we substitute them into the transfer function to check if the system response satisfies the specifications. If not, we search another set of N and P values until the specifications are met. The PLSS design procedure can be stated as follows. Step 1) Determine the maximum range of the PCO output frequency according to the stepping motor parameters, system speed range, stepping motor and driver gain K,, and VCO gain K , . Choose the possible line density n. Determine wmin according to Fig. 3. Compute Tma, = 2 n /numin . In step 1, the maximum output voltage of the ADPC is the product NP,where P is determined by the permissible motor speed variation during each pumping period TIN. The forward gain of the servo system can be defined as

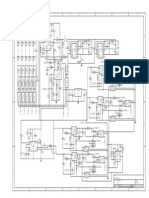

Step 6-2) We use the phase-ramp input to simulate the speed response and compare with the system requirements, such as speed resolution, maximum overshoot, settling time, and steady-state response. Step 6-3) If the specifications can be met, the design is finished. Otherwise, we return to step 1 and repeat again. VI. DESIGN Example, Simulation, and Experiment Suppose that the parameters of the stepping motor are b = 30 rad/s and c = 2000 (rad/s)*. There are 200 steps for each rotation. Now the system employed is half-step excitation and the driver and stepping motor dc gain is Km / c = (2n/400) = 0.0157. That is, when a frequency of 400 Hz is used as the input, the motor will rotate at a speed of 1 r/s. In the hardware used, the optical encoder produces 200 pulses during one rotation. Thus the maximum line density is n = 200. The PCO requires that when we have a phase-ramp input, the steady-state error should be less than 2%, the maximum overshoot be less than l o % , rise time be less than 2 s, settling time be less than 3 s, permissible speed jump be less than 0.0471 rad/s, and speed range be 40-1000 r/min. The VCO has a gain of K, = 454 Hz/V. Consequently, the maximum output voltage of the ADPC is N P = (1000 r/min 2nrad)/(454 Hz/V * 0.0157 60) = 14.68 V. We choose NP to be 15 V. PK,Km/c= 0.0471 rad/s. Then choose P = 6mV and N = 2500. Fig. 5 shows the block diagram of the PLSS. We have Phase comparator: It consists of the MC4044 frequency-phase comparator IC and some digital logic gates. R denotes the reference phase and V denotes the variable phase. If R leads V , U will produce pulse outputs and D keeps high potential. On the other hand, if V leads R ,D will produce pulse outputs and U keeps high potential. Sampler: It consists of a NOT gate and a NAND gate, etc. N3is just the multisampling rate N.It samples the D (or U, depending on which keeps high potential) signal and provides this sampled signal as a clock pulse to the Up terminal of the counter if R leads V (or to the D, terminal if V leads R ) . ADPC: It is composed of a 74193 IC counter and a 12-b D/A converter AD7541. In order to increase system resolution, the D/A converter used in this system is a 12-b IC. Then we use three 4-b 74193 counters in cascade. If the clock pulse appears at the Up (or Dw) terminal, the counter will count up (or down). Then AD7541 must be power supplied by the 7812 regulation IC, which provides a stable saturation voltage of V,,, = 24.6 V. Therefore the D/A converter can provide 2'* = 4096 output voltage levels. Thus, the jump voltage is P = 24.6V/4096 = 6 mV as desired. The VCO and t N I : VCO comprises LM331 VCO IC (with linear response) and pA741 (operational amplifier) so that better resolution can be achieved. The control voltage of the VCO is designed at 0.02V (for

Step 2)

Step 3)

NPK,K,

Gdc

2nc

(34)

Therefore, the speed can be derived as

w = Gdc8e

(35)

where 2x" 8 e = -.

For minimum 8e, we have Thus, the speed jump is

N' = 1 and the jump voltage P.

which shows that A w is proportional to P. N can be determined by P and NP. The controller parameters can be derived from step 1 to step 3. With the derived stepping motor and controller, design the phase comparator, ADPC, VCO, waveshaping circuit, and the hardware circuit of the computer interface. The controller parameters computed from step 1 Step 5) to step 3 are used as the data for computer simulation. We can do the experiment with step 4, and find the optimum line density n. Step 6) The computer simulation of the PLSS can be stated as: Step 6-1)Use P, N, T, K,, K,, b, c , and n to compute the closed-loop transfer function from (16). Step 4)

LI AND HSIEH: A PHASE/FREQUENCY-LOCKED CONTROLLER

117

T

(U.

+ Ni

74,9iI7476

+ NI

7419317476

MICROPRGCESSOR

P C / 4 T X2SS

C1.U. ____c

- ,+

" 1

DRIVER

STEPPIX

MOTOR

<(U

P ~ I M 8n.x I cs

103 8 9 3 2 OIEZ

GSC

k M Hz

FlLP-FOLP

7476

DIGITAL MODIFIER

*

=

Fig. 5 . Block diagram of the PLSS where N , N3 = 20-50.

10, N2 = 30-320, and

5)

6)

7)

8)

171 Hz output frequency) 16.03V (for 72.83 kHz output frequency). In order to operate with the stepping motor, a frequency divider circuit ( +N , , N,= 10) is included that consists of 74193 and 7476. Thus, K , = (72830 - 171)/(16.03 - 0.02)/10 = 454 Hz/V. Driver: It is PMM-CS-803C-1. We need only provide the pulse signal at the input terminal. It provides halfstep and two-phase excitations, clockwise (CW) and counterclockwise (CCW) rotations, etc. The driving signal derived from the VCO and + N , circuit is amplified and feeds the driver input terminal. Stepping motor: It is a 103-8932-01E2 hybrid PM stepping motor, with two-phase windings and a step angle of 1.8"/step (200 steps constitute one rotation). An optical encoder E680200C3J is mounted that includes A and B terminals that generate 200 pulses with 90" phase difference during one rotation, and a C terminal that generates one pulse during one rotation. Waveshaping circuit: Because the stepping motor rotates in a stepping manner, the vibration may occur. The pulse waveform generated by the optical encoder is rather complicated. The waveshaping circuit is used to improve such a waveform. It uses optocoupler IC's MCT2 for noise isolation, relays for CW/CCW isolation, and monostable multivibrators (one shots) with flipflops for waveshaping. Microprocessor and frequency generator: The frequency generator consists of an 8-MHz temperaturecompensated crystal oscillator and a programmable divider, whose divisors N2 and N3 come from the microprocessor. This circuit generates the reference frequency and the multisampling frequency. The microprocessor related circuit includes the PC/AT, multifunction interface cards, and a few buffers. As soon as

the speed command comes from the keyboard, the program computes the correct N2 and N3 values, which go to the programmable divider through ports A and B. The optical encoder output waveforms go to the microprocessor through port C. The program counts the number of pulses during some fixed time interval and obtains the output speed. This system becomes unstable when the PCO is not in the phase-locked range of [ - 2 a , 2 a], i.e., when 1 0, > 2 a in Fig. 2. From (34) and (35), 0, = 2 a leads to w = NPK,Km/c, which is the upper speed limit w H , beyond which the system is unstable. From the data of our example, we have w H = (PK,Km / c ) N = (0.0471 rad/s) * 2500 = 117.75 rad/s = 1124 r/min. From Fig. 4, the lower speed limit is w L = 40 r/min. Thus, the speed range 40-1000 r/min in our experiment is stable, and this is the reason why we choose these comparatively modest operating speeds. The digital modifier provides the frequency-divider function for the output waveform of the optical encoder. Thus we have n = 200, 100, 50, 25, 12.5, and6.25. Weuse n = 100 to find the suitable values of b and c for different speed ranges. Furthermore, we can find the appropriate line density n for different speed ranges to obtain the optimum speed response. The result is shown in Table I. From Fig. 4, as far as the stability is concerned, n is small for high-speed rotation and large for low-speed rotation. In order to explain the effect of n, three families of speed responses for IOW-,middle-, and high-speed rotations with adequate n's are examined and depicted in Figs. 6-8, respectively. It is clearly seen that the simulation and experiment results are very close. Fig. 7 shows the speed responses for 60-120 r/min (with n = 25 and 50) and 60-180 r/min (with n = 25 and 50),

118

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 39, NO. 2, APRIL 1992

00

70

GO

50

1

Simulation : Experiment :

~

40.

30

for 0-60 rpm for 0-90 rpm

o o x

o

for 0-60 rpm for 0-90 rpm

0.2

0.4

0.6

0.8

1.2

1.4

I .G

!

I

Time ( s e c )

Fig. 6 . Speed responses for 0-60 r/min and 0-90 r/min (with n = 200).

130

120

110

100

90

Simulation :

n

..... .....

25

Experiment :

x x

o

x

n = 25 n = 5 0

0.2

0.4

0.6

0.8

1.2

1.4

1.G

Time ( s e c )

(a)

Simulation :

.......~~~~ . . . ~ . . . =

~

n = 25 50 n

Experiment :

o

x

o

x

o

x

n = 25 n = 5 0

0.2

0.4

0.G

0.u Time ( s e c )

(b)

1.2

I .4

1.G

Fig. I

(a) Speed responses for 60-120 r/min (with n

25 and 50). (b) Speed responses for 60-180 r/min (with n = 25 and 50).

LJ AND HSIEH: A PHASE/FREQUENCU-LOCKED CONTROLLER

500,

I19

- I

k

450

400

I

I

r n a

IjnIi^ 1501/0

200

Simulation : ___ for 60-360 rpm for 60-480 rpm Experiment :

o

Y

Q

for 60-360 rpm for 60-480 rpm

100

5of

0

0.2

0.4

0.G

0.u

I .2

I ..I

1 .G

Time (sec)

Fig. 8.

Speed responses for 60-360 r/min and 60-480 r/min (with n = 6.25).

TABLE I SUITABLE c , AND n b, Speed Range (r/min) 40-60 70-90 120-180 210-300 330-390 420-480

b , (rad/s)

50 40 30 20 10 9

C,

((radls)*)

n

200 200 50.25 25, 12.5 12A6.25 6.25

15000-9000 4500-2500 2400- 1200 900-500 425-200 180- 140

the minimum stable speed. Under the steady rotation condition, small line density corresponds to small rise time and large overshoot. We must find the appropriate line density under different speed ranges to obtain the optimum speed response. Therefore, an adaptive n selector can be used. ACKNOWLEDGMENT The authors are very grateful to R. N. Jou for his help in simulation and experiment. REFERENCES

J . Tal, Speed control by phase-locked servo systems-new possibility and limitation, IEEE Trans. Ind. Electron. Contr. Instrum., vol. IECI-24, pp. 118-125, Feb. 1977. DC Motors, Speed Controls, Servo Systems, 4th ed., Engineering Handbook, Electro Craft Corp., 1978. F. M. Gardner, Phaselock Techniques, 2nd ed. New York: Wiley, 1979. G. C . Hsieh, Y. P. Wu, C. H. Lee, and C. H. Liu, An adaptive digital pump controller for phase-locked servo systems, IEEE Trans. Ind. Electron, vol. IE-34, pp. 379-386, Aug. 1987. B. C. Kuo, Digital Control Systems. New York: Holt, Rinehart and Wiston, 1980. I. J. Nagrath and M. Gopal, Confrol Systems Engineering. New York: Wiley, 1982. A. Hughes and P. J . Lawrenson, Electromagnetic damping in stepping motor, IEE Proc., vol. 122, no. 8, pp. 819-824, 1975. A. Hughes, Parameters governing the dynamic performance of permanent-magnet stepping motor, in Proc. Sixth Annual Symposium of IMCSD, 1977, pp. 39-47. P. Lawrenson, A. Hughes, and P. P. Acarnley, Starting/stopping rates of stepping motors, improvement and prediction, in Proc. Int. Conf. on Stepping Motors and Systems, 1976, pp. 54-60. Y. K. Hsu, Principles and Applications of Stepping Motors (in Chinese). Taipei: Chuan-Hua Book Co., 1990. J.-C. Li, G.-C. Hsieh, and R.-N. Jou, A study on stepping servo control system by phase-locked technique, in Proc. IEEE Int. Conf. on Industrial Electronics, Control, and Instrumentation, Kobe, Japan, Oct. 1991, pp. 366-370.

respectively. The steady-state speed error is less than 0.15 r/min. It is clearly indicated that in each case the rise time for n = 25 is shorter than that for n = 50, but the overshoot for n = 25 is larger than that for n = 50. Remarkably, the settling times are nearly the same. According to the three families of speed responses mentioned above, it is concluded that the determination of n is very important. It is found that from Figs. 6-8, with an adequate selection of n, shorter rise time, smaller overshoot, and nearly the same settling time can be obtained over the controlled speed range. The rise times are all within 0.15-0.4 s, the overshoots are below 5%, and the settling times are no more than 0.7 s. As a result, if an adaptive n selector is carefully built according to the speed and stability requirements, a better performance can be obtained in this system. This adaptive n selector can be easily formed by using an optical encoder followed by a programmable divider. VII. CONCLUSIONS We have proposed a PCO, which consists of an ADPC and a VCO. We build the mathematical model of the stepping motor and PCO, from which N, P , T , stability investigation, and design procedure can be determined. The steadystate speed error can be kept within kO.15 r/min over the controlled speed range. The larger the line density, the lower

You might also like

- STI LE KN 14003 Solar Generator 1Document2 pagesSTI LE KN 14003 Solar Generator 1hamsaxyzNo ratings yet

- std883 3000wChg1Document100 pagesstd883 3000wChg1hamsaxyzNo ratings yet

- RTMwin 7Document26 pagesRTMwin 7hamsaxyzNo ratings yet

- Analysis of Satellite Electrical Power Subsystem Architectures To Enhance Survivability and ReliabilityDocument6 pagesAnalysis of Satellite Electrical Power Subsystem Architectures To Enhance Survivability and ReliabilityhamsaxyzNo ratings yet

- Fertility Ovulation Calendar Calculator - BabyMed5Document1 pageFertility Ovulation Calendar Calculator - BabyMed5hamsaxyzNo ratings yet

- Analysis of Satellite Electrical Power Subsystem Architectures To Enhance Survivability and ReliabilityDocument6 pagesAnalysis of Satellite Electrical Power Subsystem Architectures To Enhance Survivability and ReliabilityhamsaxyzNo ratings yet

- SrI VidyA SaparyA vAsanADocument42 pagesSrI VidyA SaparyA vAsanAhamsaxyzNo ratings yet

- 04284040Document6 pages04284040hamsaxyzNo ratings yet

- Test Solutions For Interference Anti-JamDocument5 pagesTest Solutions For Interference Anti-JamhamsaxyzNo ratings yet

- Names of foodstuffs in Indian languagesDocument19 pagesNames of foodstuffs in Indian languagesSubramanyam GundaNo ratings yet

- 08 - Safety Design Features of GS Yuasa LG Li-Ion - TInoueDocument22 pages08 - Safety Design Features of GS Yuasa LG Li-Ion - TInouehamsaxyzNo ratings yet

- Procogue: KillenDocument8 pagesProcogue: KillenhamsaxyzNo ratings yet

- Analog Power SupplyDocument1 pageAnalog Power SupplyhamsaxyzNo ratings yet

- Stereographic Sunpath Diagram Shows Solar vs Mean TimeDocument1 pageStereographic Sunpath Diagram Shows Solar vs Mean TimehamsaxyzNo ratings yet

- TAB Strategic Missile DefenseDocument6 pagesTAB Strategic Missile DefensehamsaxyzNo ratings yet

- TM X 53398 Saturn Block Guidance Summary Report ChapmanDocument46 pagesTM X 53398 Saturn Block Guidance Summary Report ChapmanhamsaxyzNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- PWM MemDocument5 pagesPWM MemNguyễn Trọng DuyNo ratings yet

- OB5269Document11 pagesOB5269aldo_suviNo ratings yet

- PL USD DLRDocument20 pagesPL USD DLRIkram ArifNo ratings yet

- ACS720 DatasheetDocument30 pagesACS720 DatasheetRicardo AntunesNo ratings yet

- Lifi PDFDocument5 pagesLifi PDFHimanshu SaxenaNo ratings yet

- Microelectronics MCQs - Integrated Circuits & Op-Amp QuestionsDocument16 pagesMicroelectronics MCQs - Integrated Circuits & Op-Amp QuestionsKimberly TaboraNo ratings yet

- Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper StabilizationDocument31 pagesOp-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper StabilizationAndres MauricioNo ratings yet

- TL 5001 CDocument23 pagesTL 5001 Cgronci5410No ratings yet

- Design and Simulation of Automatic Satellite Signal Tracking SystemDocument41 pagesDesign and Simulation of Automatic Satellite Signal Tracking SystemFìrœ Lōv MånNo ratings yet

- TPS65198RUYTDocument4 pagesTPS65198RUYTАлександр АндриановNo ratings yet

- Datasheet Lm311Document10 pagesDatasheet Lm311Ed FreemanNo ratings yet

- Half-Bridge Driver IC: Low-Side and High-Side Drive With Simultaneous Conduction LockoutDocument12 pagesHalf-Bridge Driver IC: Low-Side and High-Side Drive With Simultaneous Conduction LockoutIIIkwarkaNo ratings yet

- Operational Amp...Document16 pagesOperational Amp...CHAITANYA KRISHNA CHAUHANNo ratings yet

- General Description Features: Cost Effective LED ControllerDocument10 pagesGeneral Description Features: Cost Effective LED ControlleranilNo ratings yet

- PICELgen Signal Generator Code UpdateDocument40 pagesPICELgen Signal Generator Code UpdateRaGirNo ratings yet

- TL594 DDocument12 pagesTL594 DaaronNo ratings yet

- Manual Soft KV 2Document239 pagesManual Soft KV 2Husna HadzirNo ratings yet

- EEE 2104 - Experiment 03Document2 pagesEEE 2104 - Experiment 03Sadikul Hasan Mridha Atul (181016024)No ratings yet

- 1862 - Iris Manual PDFDocument47 pages1862 - Iris Manual PDFJuned JunaediNo ratings yet

- Sensors: Single Neural Adaptive PID Control For Small UAV Micro-Turbojet EngineDocument21 pagesSensors: Single Neural Adaptive PID Control For Small UAV Micro-Turbojet Enginemarinecustoms.pengemNo ratings yet

- ABB Procontic, PC331 Programming-Software - 7Document524 pagesABB Procontic, PC331 Programming-Software - 7fathazamNo ratings yet

- BigShot ControllerDocument45 pagesBigShot Controllergricenko100% (2)

- Electronics Components Tester (AT89C52)Document2 pagesElectronics Components Tester (AT89C52)Akhil JNo ratings yet

- RDS / RBDS Decoder: BU1924 / BU1924F / BU1924FSDocument5 pagesRDS / RBDS Decoder: BU1924 / BU1924F / BU1924FSshareatorNo ratings yet

- ToslinkDocument20 pagesToslinkEnrique MontealegreNo ratings yet

- SG 3524Document10 pagesSG 3524Akhlaque ShamsiNo ratings yet

- Your Traction Inverter DesignDocument15 pagesYour Traction Inverter DesigndinhquangcdtbkNo ratings yet

- AmplifiersDocument4 pagesAmplifiersRed David BallesterosNo ratings yet

- A 6 Bit 2 GS/s Flash-Assisted Time-Interleaved (FATI) SAR ADC With Background Offset CalibrationDocument4 pagesA 6 Bit 2 GS/s Flash-Assisted Time-Interleaved (FATI) SAR ADC With Background Offset CalibrationKavya MurthyNo ratings yet

- Technical Guide of How To Repair HDL Devices V1.0Document69 pagesTechnical Guide of How To Repair HDL Devices V1.0JP CifuentesNo ratings yet