Professional Documents

Culture Documents

Lab Manual Tutorial Part2

Uploaded by

rajat7169451734Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab Manual Tutorial Part2

Uploaded by

rajat7169451734Copyright:

Available Formats

Tutorial 3 Multiple Instances of the Different Components with VHDL, ISE 9.

2 and ModelsimXE on the Digilent Spartan-3E Starter Kit board

-Introduction

This tutorial will be the third in a series of tutorials as shown below. After someone finishes this tutorial, they should be able to go directly to any of the other tutorials (4-15).

Figure 1. Entire list of tutorials

One of the advantages of VHDL is the ability to develop and use packages of code repeatedly. Many experienced VHDL designers develop a component to perform a specific task. They debug and rework this component until it is perfect. Once this is done, the component can be used again and again for new projects. This lab will be an introduction to reusing different components in a single file using a hardware descriptive language (VHDL) design. Xilinx ISE 9.2 is the design tool provided by Xilinx for this purpose. The board will be a Digilent Spartan3E board with a XC3S500E chip. Whereas Tutorial 2 developed multiple instances of the same component, Tutorial 3 will develop instances of different components.

There are two sections of design for this lab. The first is the VHDL program design of what the project has to do, where the circuit in question will be implemented.

Figure 2. Dog Component

Figure 3. Cat Component The components to be used are the Dog component and Cat component shown above. If you pat the dog or feed the dog, it will bark. This is a logic OR gate. If you water and rub the cat, it will meow. This is a logic AND gate. Although these components are very simple, the same concepts and instantiation techniques can apply to much more complicated designs. The software packages used are the Xilinx ISE and Mentor Graphics ModelsimXE (XE stands for Xilinx Edition). Although ISE has its own simulation engine, ModelsimXE is more powerful and provides greater functionality. ModelsimXE is used to verify the behavioral functionality of the design prior to programming the FPGA. For additional details on the various tools and their uses, view the video on the FMAC website (www.fpgamac.com).

-Objective

The objective is to understand how to create and simulate single components. Once this is done, then the single component will be replicated. The resulting simulation will help in understanding the process.

-Process

1. Analyze the VHDL of a single component. 2. Replicate the component. 3. Program FPGA and verify proper operation.

-Implementation

1. Open the Xilinx ISE Project Navigator by selecting it from the start menu or from the desktop icon. 2. Within the project navigator, select from the File Menu, New Project. Name the project tutorial3. To put the project in a different location, either directly type the file path into Project Location or search by clicking the Three-dotted Browse button. The location of the project can always be seen on the top of the Project Navigator 2

screen. Avoid spaces in the project name or path. Click next and it will show the device properties window.

3. Set the device properties exactly as shown in the following picture and continue to select Next until the project is created.

Figure 4. Device Properties

Figure 5. Adding Sources 4. The project will be a blank project. For this project, there are seven source files (three source files, three simulation files and a ucf file). Copy them into the directory for Tutorial 3. The files are: Dog.vhd, Dog_tb.vhd, Cat.vhd, Cat_tb.vhd, ManyPets.vhd, ManyPets_tb.vhd and ManyPets.ucf. When naming testbenches, it is common practice to add the _tb to the file name. Tutorial 2 covers all the specifics about the Dog component. It will not be repeated here. To start, a project will be created with a single instance of Cat. This will allow for a more complete understanding of the basic building block that will be used in further instantiations. Right click into the Sources pane and select Add Source 3

Figure 7. Selected Sources 5. Select the two files shown above.

Figure 8. Accepted Source Files 6. The green check marks identify that the program knows what type of files they are and what to do with them.

Figure 9. Switch to Simulation 7. Using the drop down selector in Sources for: choose the Behavioral Simulation option. Ensure that the Cat_tb.vhd file is highlighted.

Figure 10. Simulation of Cat 8. Following the procedure from Tutorial 1, run the simulation using the applicable testbench. The resulting waveform confirms that anytime water and rub are high, meow is also high.

Figure 11. Remove Old Testbench 9. The next step will be to transition to an instantiation of the dog and the cat. First, remove the Cat_tb.vhd file. Do this by highlighting the file, right clicking on it and choosing remove. Next, add the new files. Right click in the sources pane and add the four files shown below.

Figure 12. Adding New Files 5

10. The files added can be explored. They are the dog component and the ManyPets file that calls for an instance of dog and cat. This is the critical part. Just as dog and cat are created, verified and used individually, any creation of a quality (and verified) component can be reused.

Figure 13. File Hierarchy 11. The expansion of the file hierarchy in the Behavioral Simulation pane shows how the ISE software believes the components are developed. It shows that ManyPets has two identical components called Dog.vhd and Cat.vhd. The two instantiations are: Poodle and Mixed.

Figure 14. Simulation Waveform 12. Run the simulation. When compared to the Cat simulation, it is now possible to visualize both instantiations. The ManyPets.vhd code shows how this was accomplished. This is component reuse.

Figure 15. User Constraint File (UCF) 13. The UCF shows the pin assignments used to display the developed code on the S3E board.

Figure 16. Synthesis 14. Ensure the Sources for: selection is set for Synthesis/Implementation. Highlight the ManyPets.vhd code, expand the Generate Programming File selection and double click on the iMPACT choice.

Figure 17. iMPACT 15. Choose the JTAG option.

Figure 18. Choosing Programming File 16. When the xc3s500e FPGA device is highlighted, choose petpack.bit and Open. Bypass the other two devices. 8

Figure 19. Programming Device 17. When done, right click on the FPGA icon and program the device. According to the UCF settings, switches 0 and 1 are pat and feed for dog and switch 2 and 3 are water and rub for cat. Flipping switchs high will result in LEDs being activated.

About the author: Craig Kief is the Deputy Director of the FPGA Mission Assurance Center and can be reached at DeptDirector@fpgamac.com.

First Source File --VHDL files contain three parts: library declarations, entity and --behavior. The library describes what each function will do. Entity --describes the inputs and outputs. Behavior is the working --portion of the project. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; --Declaration of the module's inputs and outputs for part 1 of tutorial 2 entity Dog is port ( pat: in std_logic; feed: in std_logic; bark: out std_logic ); end Dog; --Defining the modules behavior Architecture behavioral of Dog is begin process (pat, feed) begin bark <= pat OR feed; end process; end behavioral;

10

Second Source File --VHDL files contain three parts: library declarations, entity and --behavior. The library describes what each function will do. Entity --describes the inputs and outputs. Behavior is the working --portion of the project. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; --Declaration of the module's inputs and outputs for part 1 of tutorial 2 entity Cat is port ( water: in std_logic; rub: in std_logic; meow: out std_logic ); end Cat; --Defining the modules behavior Architecture behavioral of Cat is begin process (water, rub) begin meow <= water AND rub; end process; end behavioral;

11

Third Source File

--VHDL files contain three parts: library declarations, entity and --behavior. The library describes what each function will do. Entity --describes the inputs and outputs. Behavior is the working --portion of the project. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; --Declaration of the module's inputs and outputs for part 1 of tutorial 2 entity PetPack is port ( dog1_Pat: in std_logic; dog1_Feed: in std_logic; dog1_Bark: out std_logic; cat1_Water: in std_logic; cat1_Rub: in std_logic; cat1_Meow: out std_logic ); end PetPack; --Defining the modules behavior Architecture behavioral of PetPack is component Dog is port ( pat: in std_logic; feed: in std_logic; bark: out std_logic ); end component Dog; component Cat is port ( water: in std_logic; rub: in std_logic; meow: out std_logic ); end component Cat; begin Poodle : Dog port map ( pat => dog1_Pat, feed => dog1_Feed, bark => dog1_Bark );

12

Mixed : Cat port map ( water => cat1_Water, rub => cat1_rub, meow => cat1_meow ); end Behavioral;

13

First Test Bench --This is a VHDL testbench. It is used to stimulate the inputs to --file we are testing. A good design practice is to create a testbench --for each component you are developing. Test each component separately --before combining them. LIBRARY IEEE; USE IEEE.std_logic_1164.all; USE IEEE.std_logic_arith.all; USE IEEE.std_logic_unsigned.all; USE IEEE.STD_LOGIC_TEXTIO.ALL; USE STD.TEXTIO.ALL; ENTITY testbench IS END testbench; ARCHITECTURE testbench_arch OF testbench IS COMPONENT Dog PORT ( pat feed bark ); END COMPONENT; --develop signals to stimulate SIGNAL pat : std_logic := '0'; SIGNAL feed : std_logic := '0'; SIGNAL bark : std_logic := '0'; --UUT means unit under test BEGIN UUT : Dog --map signals on right to entitys on the left PORT MAP ( pat => pat, feed => feed, bark => bark ); signal_Pat: process begin pat <= NOT pat; wait for 1 ns; end process; signal_Feed: process 14

: in std_logic; : in std_logic; : out std_logic

begin feed <= NOT feed; wait for 2 ns; end process; END testbench_arch;

15

Second Test Bench --This is a VHDL testbench. It is used to stimulate the inputs to --file we are testing. A good design practice is to create a testbench --for each component you are developing. Test each component separately --before combining them. LIBRARY IEEE; USE IEEE.std_logic_1164.all; USE IEEE.std_logic_arith.all; USE IEEE.std_logic_unsigned.all; USE IEEE.STD_LOGIC_TEXTIO.ALL; USE STD.TEXTIO.ALL; ENTITY testbench IS END testbench; ARCHITECTURE testbench_arch OF testbench IS COMPONENT Cat PORT ( water : in std_logic; rub : in std_logic; meow : out std_logic ); END COMPONENT; --develop signals to stimulate SIGNAL water : std_logic := '0'; SIGNAL rub : std_logic := '0'; SIGNAL meow : std_logic := '0'; --UUT means unit under test BEGIN UUT : Cat --map signals on right to entitys on the left PORT MAP ( water => water, rub => rub, meow => meow ); signal_Water: process begin water <= NOT water; wait for 1 ns; end process;

16

signal_Rub: process begin rub <= NOT rub; wait for 2 ns; end process; END testbench_arch;

17

Third Test Bench --This is a VHDL testbench. It is used to stimulate the inputs to --file we are testing. A good design practice is to create a testbench --for each component you are developing. Test each component separately --before combining them. LIBRARY IEEE; USE IEEE.std_logic_1164.all; USE IEEE.std_logic_arith.all; USE IEEE.std_logic_unsigned.all; USE IEEE.STD_LOGIC_TEXTIO.ALL; USE STD.TEXTIO.ALL; ENTITY testbench IS END testbench; ARCHITECTURE testbench_arch OF testbench IS COMPONENT PetPack PORT ( dog1_Pat: in std_logic; dog1_Feed: in std_logic; dog1_Bark: out std_logic; cat1_Water: in std_logic; cat1_Rub: in std_logic; cat1_Meow: out std_logic ); END COMPONENT; --develop signals to stimulate SIGNAL dog1_Pat : std_logic := '0'; SIGNAL dog1_Feed : std_logic := '0'; SIGNAL dog1_Bark : std_logic := '0'; SIGNAL cat1_Water : std_logic := '0'; SIGNAL cat1_Rub : std_logic := '0'; SIGNAL cat1_Meow : std_logic := '0'; --UUT means unit under test BEGIN UUT : PetPack --map signals on right to entitys on the left PORT MAP ( dog1_Pat => dog1_Pat, dog1_Feed => dog1_Feed, dog1_Bark => dog1_Bark, cat1_Water => cat1_Water, cat1_Rub => cat1_Rub, cat1_Meow => cat1_Meow ); 18

signal_Pat_Water: process begin dog1_Pat <= NOT dog1_Pat; cat1_Water <= NOT cat1_Water; wait for 1 ns; end process; signal_Feed_Rub: process begin dog1_Feed <= NOT dog1_Feed; cat1_Rub <= NOT cat1_Rub; wait for 2 ns; end process; END testbench_arch;

19

UCF File NET "dog1_Pat" LOC = "L13"; #SW0 NET "dog1_Feed" LOC = "L14"; #SW1 NET "dog1_Bark" LOC = "F12"; #LED0 NET "cat1_Water" LOC = "H18"; #SW2 NET "cat1_Rub" LOC = "N17"; #SW3 NET "cat1_Meow" LOC = "E12"; #LED1

20

You might also like

- MPT 3Document8 pagesMPT 3rajat7169451734No ratings yet

- MATH PROGRESSION TEST MCQDocument8 pagesMATH PROGRESSION TEST MCQrajat7169451734No ratings yet

- MATHS Progression TestDocument4 pagesMATHS Progression Testrajat7169451734No ratings yet

- Imo Sample Paper Class-3Document2 pagesImo Sample Paper Class-3Rahul KumarNo ratings yet

- About VLANDocument1 pageAbout VLANrajat7169451734No ratings yet

- How To Install Linux: Installing Any Linux DistributionDocument3 pagesHow To Install Linux: Installing Any Linux Distributionrajat7169451734No ratings yet

- G.K III Term QuestionsDocument3 pagesG.K III Term Questionsrajat7169451734No ratings yet

- Excel Lab ManualDocument79 pagesExcel Lab Manualrajat716945173450% (2)

- G.K III Term QuestionsDocument3 pagesG.K III Term Questionsrajat7169451734No ratings yet

- 1st AssignmentDocument1 page1st Assignmentrajat7169451734No ratings yet

- Karnaugh MapsDocument9 pagesKarnaugh MapsshijinbgopalNo ratings yet

- Computer Organisation & ArchitectureDocument62 pagesComputer Organisation & Architecturerajat7169451734No ratings yet

- 4bit AdderDocument13 pages4bit Adderrajat7169451734No ratings yet

- BIST2Document54 pagesBIST2Rishi Raj RathoreNo ratings yet

- EMoustakasThesis09 1991Document121 pagesEMoustakasThesis09 1991rajat7169451734No ratings yet

- Dbms Complete Lab ManualDocument184 pagesDbms Complete Lab Manualrajat7169451734No ratings yet

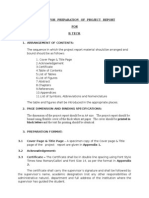

- Format For Preparation of Project Report FOR B. TechDocument9 pagesFormat For Preparation of Project Report FOR B. Techrajat7169451734No ratings yet

- Final Year Project Report CSEDocument5 pagesFinal Year Project Report CSErajat71694517340% (1)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- RAN REFRESH LISTDocument21 pagesRAN REFRESH LISTTomás Villalba LopezNo ratings yet

- TM-3000 Um 96M11193 GB WW 1116-6Document298 pagesTM-3000 Um 96M11193 GB WW 1116-6Juan MtzNo ratings yet

- Manual Panasonic CT-27SL14Document52 pagesManual Panasonic CT-27SL14Marvin100% (2)

- Data Representation and Memory StorageDocument28 pagesData Representation and Memory StoragesubaNo ratings yet

- Error CodeDocument411 pagesError CodeTRIQUERE100% (2)

- divIDE Plus ManualDocument140 pagesdivIDE Plus ManualOscar Arthur KoepkeNo ratings yet

- (Ace - Technology) - XDWL 17 65V VT PDFDocument1 page(Ace - Technology) - XDWL 17 65V VT PDFGiang Nguyễn TrườngNo ratings yet

- Emc SNMP Docu86751Document163 pagesEmc SNMP Docu86751mlazar20009720No ratings yet

- Assignment: SUBJECT: Advanced Computer ArchitectureDocument7 pagesAssignment: SUBJECT: Advanced Computer ArchitectureAbhishemNo ratings yet

- Understanding Schmitt TriggersDocument4 pagesUnderstanding Schmitt TriggersfernandofortunaNo ratings yet

- DS1220AB/AD 16k Nonvolatile SRAM Spec SheetDocument9 pagesDS1220AB/AD 16k Nonvolatile SRAM Spec SheetJoel PalzaNo ratings yet

- Wiring DiagramDocument12 pagesWiring DiagramÁlvaro TorrellasNo ratings yet

- Conclusion Elec Exp2Document1 pageConclusion Elec Exp2Gena Lapuz100% (2)

- Examples of Aliasing in Real Life: by Dr. Wajih A. Abu-Al-Saud Modified by Dr. MuqaibelDocument3 pagesExamples of Aliasing in Real Life: by Dr. Wajih A. Abu-Al-Saud Modified by Dr. Muqaibelsayed Tamir janNo ratings yet

- AN-PFC-TDA 4863-3 Calculation-Tool For PFC-Preconverter Using TDA 4863Document9 pagesAN-PFC-TDA 4863-3 Calculation-Tool For PFC-Preconverter Using TDA 4863NaciConSolNo ratings yet

- Passive ComponentDocument13 pagesPassive Componentفيزار عبد الرحمنNo ratings yet

- SH7020 HitachiDocument507 pagesSH7020 HitachiNoks stNo ratings yet

- MM/MC Phono Preamplifier Owner's ManualDocument4 pagesMM/MC Phono Preamplifier Owner's ManualJD MedinaNo ratings yet

- Ultrasonic Distance SensorDocument1 pageUltrasonic Distance SensorBangon KaliNo ratings yet

- 29PT6657-85 PhilipsDocument4 pages29PT6657-85 PhilipsHugo Flores CastilloNo ratings yet

- Electromagnetic waves in guided mediaDocument20 pagesElectromagnetic waves in guided mediaJose Daniel Ochoa MoyaNo ratings yet

- Multiband 6-Port Antenna for 698-960 and 1695-2690 MHz BandsDocument1 pageMultiband 6-Port Antenna for 698-960 and 1695-2690 MHz BandsАбдуллах аль КаффаNo ratings yet

- GSM+DCS 20dBm Mini Repeater User's ManualDocument25 pagesGSM+DCS 20dBm Mini Repeater User's ManualrobinxonNo ratings yet

- Traffic Light Controller Using VHDLDocument6 pagesTraffic Light Controller Using VHDLAbdoulrazakNo ratings yet

- WWW Electronicslovers Com 2015 09 Arduino Based MPPT Solar CDocument35 pagesWWW Electronicslovers Com 2015 09 Arduino Based MPPT Solar CM Rameez Ur RehmanNo ratings yet

- Dart Monitor Repair GuideDocument6 pagesDart Monitor Repair GuidenicolaecomiciNo ratings yet

- Thermal Simulation Techniques For Nano Transistors: Ken GoodsonDocument41 pagesThermal Simulation Techniques For Nano Transistors: Ken GoodsonSwapnil BhuratNo ratings yet

- Optimized, Certified Optical Transceivers For The Highest-Performance Data Center FabricsDocument2 pagesOptimized, Certified Optical Transceivers For The Highest-Performance Data Center Fabricsamir_bahramNo ratings yet

- EMC Model of Low Voltage DC Motor: I. Oganezova, R. Kado, B. Khvitia, Z. Kuchadze, A. Gheonjian, R. JobavaDocument5 pagesEMC Model of Low Voltage DC Motor: I. Oganezova, R. Kado, B. Khvitia, Z. Kuchadze, A. Gheonjian, R. JobavaDipen DasNo ratings yet

- DP Cheat Sheet 1.50Document4 pagesDP Cheat Sheet 1.50Damián NogueraNo ratings yet