Professional Documents

Culture Documents

Design Examples Using The Toolbox

Uploaded by

rajeevjain09Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design Examples Using The Toolbox

Uploaded by

rajeevjain09Copyright:

Available Formats

Design Examples

MEAD March 2008

Richard Schreier

Richard.Schreier@analog.com

ANALOG DEVICES

R. SCHREIER

ANALOG DEVICES, INC.

Catalog

1 2nd-Order Lowpass

Architecture: Single-bit, switched-capacitor Application: General-purpose, low-frequency ADC Architecture: Multi-bit switched-capacitor Application: Audio Architecture: (Multibit MOD2, pipeline) Cascade Application: Wideband communications Architecture: Single-loop with LC, Active-RC and switchedcapacitor resonators Application: High-dynamic-range radio receiver

5th-Order Lowpass

2-0 Cascade

6th-Order Bandpass

R. SCHREIER

ANALOG DEVICES, INC.

1. MOD2

Specications

Parameter Bandwidth Sampling Frequency Signal-to-Noise Ratio Supply Voltage Symbol fB fs SNR VDD Value ~1 1 100 3 Units kHz MHz dB V

Assumptions

Single-bit switched-capacitor realization Input voltage range is 0-VDD (single-ended) Reference voltage is VDD Op-amp swing is 2 Vpp (differential)

3

R. SCHREIER

ANALOG DEVICES, INC.

Toolbox Design

OSR = 500; H = synthesizeNTF(2,OSR,0,2); [snr amp] = simulateSNR(H,OSR); plot(amp,snr,'bd',amp,snr,'b-'); 120 100 Very high SQNR Quantization noise will be negligible. Maximum input signal 1 dBFS Lets not worry about instability.

SQNR (dB)

80 60 40 20 0 120 100 80 60 40 20 0

Input Amplitude (dB)

4

R. SCHREIER

ANALOG DEVICES, INC.

Block Diagram & DR Scaling

U

b1

1 X1 z1

a1

c1

1 X2 z1

a2

form = 'CIFB'; [a,g,b,c] = realizeNTF(H,form); b(2:end) = 0; ABCD = stuffABCD(a,g,b,c,form); [ABCDs umax] = scaleABCD(ABCD); [a,g,b,c] = mapABCD(ABCDs,form);

Code yields a = [0.27, 0.24], b = [0.27], c = [0.34 5.1], umax = 0.9

Quantize to a1 = b1 = a2 = 1/4, c1 = 1/3 for convenience. 5

R. SCHREIER

ANALOG DEVICES, INC.

Simulated Spectrum

0

STF PSD (dBFS/NBW)

20 40 60 80 100 120 NBW = 1.8x104 fs 0 0.25 0.5

NTF

(scaled)

Normalized Frequency (1 fs ) Coefcient change has negligible performance impact

Peak SQNR = 115 dB, H

= 2.2 .

R. SCHREIER

ANALOG DEVICES, INC.

Simplied Schematic

2 1 1 2 1 x1 2 2 1 x2 L 2 1 D Q C v

Difference Equations x 1(n + 1) = x 1(n) + b 1 u(n) a 1 v(n) x 2(n + 1) = x 2(n) + c 1 x 1(n) a 2 v(n) v(n) = Q( x 2(n))

Timing

1 2

x1(n) x2(n)

x1(n+1)

x2(n+1) v(n)

Verify that the circuit follows the difference equations. Check the quantizer and feedback timing carefully!

7

R. SCHREIER

ANALOG DEVICES, INC.

First Integrator

VDD VSS

1Vd 1Vd

C2

Vin

C1

1 2 2

Vx1

0, 1

1 2Vd

1 2Vd

VDD VSS

Vx1 = 2C1/C2(VinVDDvd) Homework: Verify timing & polarity

Want input (full-scale) range = [0,3] V and want op-amp swing = [1,+1] Vdifferential

x1 = Vx1/1 V, u = (Vin1.5 V)/1.5 V

C 1 C 2 = b 1 3 = 1 12

8

R. SCHREIER

ANALOG DEVICES, INC.

Absolute Capacitor Values

Absolute capacitor values are determined by thermal noise considerations

Capacitor ratios are set by the desired dynamics.

For example, assume noise is purely kT/C noise

i.e. device noise is negligible.

Since thermal noise is white, we get a factor of OSR reduction in the in-band noise vn = 10 Vrms C1 = 83 fF C2 = 1 pF

These capacitor values are quite reasonable! C2 gets smaller if the output swing of the op-amp is increased. kT 1 2 i.e. v n = ----------- -----OSR C 1

R. SCHREIER

ANALOG DEVICES, INC.

Second Integrator

VSS VDD

1 2Vd 2Vd

C 4C

2 1

12C

Vx1

1

1 2

Vx2

VDD 2Vd VSS 2Vd

Homework: Verify capacitor ratios 1 Hint: Vx2 = (4C/12C)Vx1 (C/12C) VDDv)

In-band noise of second integrator is greatly attenuated Capacitor sizes dictated by charge injection errors and desired ratio accuracy

10 ( OSR ) 3 By a factor of ------------------- 10 6 (approximately). 12 2

R. SCHREIER

ANALOG DEVICES, INC.

Building Block Op Amp

VDD bias4

bias3 VON vocm bias1 1 1 2 2 2x VIP bias2 VIN VOP 2 2 1 1 vocm bias1

Folded-cascode op-amp with switched-capacitor common-mode feedback

11

R. SCHREIER

ANALOG DEVICES, INC.

Op-Amp Specications

50% of T/2 = 0.25 s; Q max = C 1 VDD = 0.25 pC Islew = 1 A is sufcient T/2 = 10; = C 1 g m ; C1 = 0.1 pF gm = 2 A/V

Power consumption can be very low!

As a rule of thumb, Amin OSR for negligible SQNR reduction

Assumes that the op amps are linear and that the integrator gain factors are close to 1. SQNR margin can be traded for reduced op-amp gain requirements.

In this implementation, the integrator gain factors are 1/3 and 1/12, and the gain requirements are relaxed

For example, A = 40 dB is sufcient for 110 dB SQNR and the width of the deadband around 0 V is only 4 V if A = 40 dB.

12

R. SCHREIER

ANALOG DEVICES, INC.

Building Block Latched Comparator

VDD V+ V S

2 R S

To DFF

R 2 VSS 2

Falling phase 2 initiates regenerative action

S and R connected to a Set/Reset latch

13

R. SCHREIER

ANALOG DEVICES, INC.

Building Block Clock Generator

1 CLK * * * 2D 2 CLK 1 1D 2 2D * 1D

* = Delay Control

14

R. SCHREIER

ANALOG DEVICES, INC.

2. MOD5

Specications

Parameter Signal Bandwidth Sampling Frequency Signal-to-Noise Ratio Supply Voltage Symbol fB fs SNR VDD Value 50 8 110 3 Units kHz MHz dB V

Assumptions

Single-bit switched-capacitor realization Input voltage range is 2 V (differential) Reference voltage is 2 V (differential) and Op amp swing is 4 Vpp (differential)

15

R. SCHREIER

ANALOG DEVICES, INC.

Toolbox Design

OSR = 8e6/(2*50e3); % OSR = 80 H = synthesizeNTF(5,OSR,1,1.5); amp = [-140:5:-15 -12 -10:0]; snr = simulateSNR(H,OSR,amp); plot(amp,snr,'bd',amp,snr,'b-'); 140 120 Very high peak SQNR Quantization noise will be negligible. Maximum input signal 4 dBFS Scale such that input range is 50% of full-scale.

SQNR (dB)

100 80 60 40 20 0 140 120 100 80 60 40 16 20 0

Input Amplitude (dB)

R. SCHREIER

ANALOG DEVICES, INC.

First Integrator

C1

VREFP VREFN

C2 C1 Vx1

Vin

VREFN VREFP

kT Input-referred differential noise power is P n = 8 -----C1 2 2 = 2 V2 Peak signal power is P s = ( 2 V ) 8kT SNR 110 dB SNR requires C 1 = ---------------------------- = 21 pF OSR P s

This is a big capacitor! 17

R. SCHREIER

ANALOG DEVICES, INC.

Dynamic Range Scaling & Topology Selection

form = 'CRFB'; % or CRFF [a,g,b,c] = realizeNTF(H,form); b(2:end) = 0; % for CRFB only ABCD = stuffABCD(a,g,b,c,form); [ABCDs umax] = scaleABCD(ABCD); [a,g,b,c] = mapABCD(ABCDs,form);

form = CRFB yields b1 = 0.1, i.e. C2 = 10C1!

The integrating capacitor is VERY large!

form = CRFF yields b1 = 0.39, i.e. C2 = 2.5C1

The integrating capacitor is still large, but is more reasonable.

18

R. SCHREIER

ANALOG DEVICES, INC.

Simulated Spectrum

10 dBFS input

0

STF

PSD (dBFS/NBW)

20 40 60 80 100 120 140 160 4 10 105

SQNR = 122 dB

2 H(e 2if ) 2 -------------------------N

NBW = 370 Hz

106

Frequency (Hz) Used k derived from simulation to calculate true NTF

Need to set b6 = 1/k to maintain unity STF. 19

R. SCHREIER

ANALOG DEVICES, INC.

Block Diagram

b6 c1, c2, g1 c3, c4, g2

u(n)

Integrator

b1 a1

Resonator

a2 a3

Resonator

a4 a5

v(n)

-g1 b1 1 z -1 x1(n) a1 c1 z x2(n+1) c 2 z -1 a2 1 z -1 x3(n) a3

Summation is usually performed by a single passive switched-capacitor network

20

R. SCHREIER

ANALOG DEVICES, INC.

Timing Check

2 1 1 2 1 x1 2 2 1 x2 2 1 1 2 1 x5 S 1

Desired Difference Equations

Timing

x 1(n + 1) = x 1(n) + b 1 u(n) c 1 v(n) 2 1 2 1 2 x 2(n + 1) = c 2 x 1(n) + x 2(n) g 1 x 3(n) x1(n) x1(n+1) x 3(n + 1) = c 3 x 2(n + 1) + x 3(n) x2(n) x2(n+1) x 4(n + 1) = c 4 x 3(n) + x 4(n) g 2 x 5(n) x3(n) x3(n+1) x 5(n + 1) = c 5 x 4(n + 1) + x 5(n) y(n) = a 1 x 1(n) + a 2 x 2(n + 1) + a 3 x 3(n) x4(n) x4(n+1) + a 4 x 4(n + 1) + a 5 x 5(n) + b 6 u(n) x5(n) x5(n+1) y a(n) = ( a 1 + a 2 c 2 )x 1(n) + a 2 x 2(n) + ( a 3 a 2 g 1 + a 4 c 4 )x 3(n) y(n) + a 4 x 4(n) + ( a 5 a 4 g 2 )x 5(n) + b 6 u(n 1) v(n) v(n) = Q [ y(n) ] [ y a = y + b 6 ( u(n 1) u(n) ) STF a(z) = STF (z) ( 1 z 1 )NTF (z) ] 21

R. SCHREIER

ANALOG DEVICES, INC.

Behavioral Schematic

22

R. SCHREIER

ANALOG DEVICES, INC.

Impulse Response Verication

0 -.2 -.4 -.6 -.8 -1 -1.2 -1.4 -1.6 -1.8 0 .1 .2 .3 .4 .5 .6 .7 .8 Time, s 23 .9 1 1.1 1.2 1.3 1.4 Expected Impulse Response Simulated Impulse Response

R. SCHREIER

ANALOG DEVICES, INC.

Potential Improvements

Clock faster

Reduces modulator order. Reduces the size of all capacitors whose values are dictated by noise.

Use multi-bit quantization

Reduces modulator order. Increases b1 (after performing voltage scaling), thereby reducing total capacitor area.

24

R. SCHREIER

ANALOG DEVICES, INC.

3. 2-0 Cascade

Specications

Parameter Bandwidth Sampling Frequency Signal-to-Noise Ratio Supply Voltage Symbol fB fs SNR VDD Value 1.25 20 90 5 Units MHz MHz dB V

Simplied Block Diagram

V1 U

5-bit MOD2

5 E1

Pipeline ADC

25

V2 7

(1z -1) 2

R. SCHREIER

ANALOG DEVICES, INC.

Toolbox Evaluation

BW = 1.25e6; Fs = 20e6; OSR = Fs/(2*BW); M = 32; nlev = M+1; nb = 7; kpipe = 2^nb; Ha = zpk([1 1],[0 0],1,1); amp = [-120:5:-15 -12:2:-6 -5:0]; sqnr = zeros(2,length(amp)); N = 8192; ftest = round(0.16/OSR*N); u1 = M*sin(2*pi*ftest/N*[0:N-1]); for i = 1:length(amp) [v1 junk1 junk2 y1] = simulateDSM(undbv(amp(i))*u1,Ha,nlev); v2 = ds_quantize(kpipe*(v1-y1),kpipe+1); v = v1 - filter([1 -2 1],1, v2/kpipe); spec1 = fft(v1.*hann(N))/(M*N/4); sqnr(1,i) = calculateSNR(spec1(1:ceil(N/2/OSR)),ftest); spec = fft(v.*ds_hann(N))/(M*N/4); sqnr(2,i) = calculateSNR(spec(1:ceil(N/2/OSR)),ftest); end plot(amp,sqnr(1,:),'m^','MarkerSize',10,'LineWidth',2); hold on; plot(amp,sqnr(1,:),'m--','LineWidth',3); plot(amp,sqnr(2,:),'bs','MarkerSize',10,'LineWidth',2); plot(amp,sqnr(2,:),'b-','LineWidth',3); figureMagic([-120 0],10,2, [0 120],10,2);

26

R. SCHREIER

ANALOG DEVICES, INC.

Ideal SQNR Curve

120 100 Overall SQNR

SQNR (dB)

80 60 40 20 0 120 100 80 60 40 20 0

40 dB

SQNR of MOD2

Input Amplitude (dB) Simulated peak SQNR = 105 dB

Again, there is a lot of margin, so quantization noise should be small. 27

R. SCHREIER

ANALOG DEVICES, INC.

Gain Mismatch

(Capacitor Ratio Error)

v2 = ds_quantize(kpipe*(v1-y1)*(1+gain_mismatch),kpipe+1);

110

Peak SQNR (dB)

100

90 103

102

101

Gain Mismatch Need gain error < ~0.5%

Not a problem if moderately large capacitors are used. 28

R. SCHREIER

ANALOG DEVICES, INC.

NTF Zero Error

(Due to Finite Op-Amp Gain)

Ha = zpk([1 1]*(1-1/gain),[0 0],1,1);

Peak SQNR (dB)

110

100

90 50

60

70

80

90

Op-Amp Gain (dB) Need op-amp gain > 65 dB

Again, not an unreasonable requirement. 29

R. SCHREIER

ANALOG DEVICES, INC.

Block Diagram [Brooks 1997]

Vin

z z -1

DAC1 DAC2

1 z -1

5-b 5

16 3-b 3

4 3-b 3

4 4-b 4

Correction/Cancellation Logic Dout

Has 1 bit of overlap at each stage

30

R. SCHREIER

ANALOG DEVICES, INC.

An Integrator Stage

Vip Vrefp

1 2b0 2b0 1 2b31 2b31 2b31 2b31 1 2b0 2b0 1

C1P,0 C2 C1P,31

2 1 1

Vx1

C1N,31

C1N,0

31

Vin

Vrefn

R. SCHREIER

ANALOG DEVICES, INC.

4. Bandpass Modulator

Vin 3 MHz IF 300 kHz BW LO BP ADC 24 MHz CLK

Want high dynamic range (~90 dB) with low power consumption (~50 mW) Desire a continuous-time architecture for its inherent anti-aliasing properties Toolbox indicates we should use a 6th-order, 8-level modulator

Use a FB topology to get a clean STF. 32

R. SCHREIER

ANALOG DEVICES, INC.

Simplied Architecture

LC Tank Feedback DAC More Resonators and Feedback DACs

Flash ADC

LO

IF

V-I Converter

ADC Front End

ADC Back End

LNA+Mixer

Bandpass ADC

33

R. SCHREIER

ANALOG DEVICES, INC.

Features of the Architecture

The mixer output current is processed by passive components which yield gain without adding noise or distortion, and without consuming power

More front-end gain makes back-end noise less important.

The rst feedback DAC cancels the bulk of the in-band portion of the mixer output, effectively passing only a residue to the ADC backend

Large signal-handling capability is not compromised. Only the LNA, Mixer and ADC front end have to deal with the full dynamic range of the signal.

34

R. SCHREIER

ANALOG DEVICES, INC.

Choices for the Second Resonator ?

FLASH

A second LC tank would require the least power, but would also need more pins Active-RC:2 mA for 50 nV/ Hz i.r. noise Switched-C:Estimate >10 mA for same i.r.n. gm-C:Tough to get linearity and stability Use Active-RC Tuning implemented with 8-bit capacitor arrays

2:1 tuning range, regardless of process. 35

R. SCHREIER

ANALOG DEVICES, INC.

Choices for the Third Resonator ?

3-bit

Active-RC:Q and drift are uncertain; might need a fourth resonator Switched-C:Q is high (>100) and drift is low Use Switched-C Consumes 1 mA and has an i.r.n of 300 nV/ Hz .

36

R. SCHREIER

ANALOG DEVICES, INC.

SC Resonator

9C 1 7C 2 2 1 2 3C 1 1 2 4C

1 2

f0 1 73 ----- = acos 1 -- --------- = 0.1247 2 9 4 fs

7C

Center frequency is set by capacitor ratios

LDI structure guarantees pole on unit circle ( A = ).

37

R. SCHREIER

ANALOG DEVICES, INC.

AGC

For a 18 dBm input, the mixer output is 2 mApp, so DAC1 needs to sink 2 mA Power consumption can be reduced at low signal levels (the usual case) by reducing DAC1s full-scale

Reduces the FS of the ADC and thus gives the ADC more gain.

Lowering DAC1s full-scale also reduces the output current noise of the DAC

Includes mismatch-induced and dynamic errors as well as thermal noise.

Placing a variable-gain element after the LC tank compensates for the reduced signal level and also saves current by minimizing the i.r.n. of the ADCs backend

38

R. SCHREIER

ANALOG DEVICES, INC.

Full ADC

External LC Tank Tunable Elements fCLK = 13-26 MHz RC Reson. SC Reson. 9-level Flash

LO

DAC1

ESL To Decimation Filter

IFIN 10-300 MHz LNA

V-I Converter

Full-Scale Adjust

Achieves NF = 8 dB and IIP3 = 0 dBm with P = 50 mW

39

R. SCHREIER

ANALOG DEVICES, INC.

Noise vs. AGC

150 kHz BW

(dB relative to a 370-ohm resistor) 15

Noise Density

10

Total

LNA/Mixer

1M DAC

30

RC atch ism

erm DAC1 Th

al

Q tiz uan

atio

28

26

24

22

C Sckend a B 20 18

Full-Scale (dBm)

40

R. SCHREIER

ANALOG DEVICES, INC.

Spectrum of Undecimated Output

fCLK = 18 MHz

0 20 2dBFS Output fCLK = 18 MHz IF = 73.35 MHz

dBFS/NBW

40 60 80 100 0

Measured PSD Theoretical PSD NBW = 3.3kHz 1 2 3 4 5 6 7 8 9

Frequency (MHz)

41

R. SCHREIER

ANALOG DEVICES, INC.

Spectrum of Decimated Output

BW = 270.833 kHz

0 20 fCLK = 26 MHz Dec-by-48

dBFS/NBW

40 60 80 No signal INF = 87 dBFS 18 dBm input @ 103.25 MHz + 25 kHz 1 dBFS output INF = -83 dBFS

100 120 140 270 180 90 0 90 NBW=200 Hz 180 270

Frequency Offset (kHz)

42

R. SCHREIER

ANALOG DEVICES, INC.

Spectrum of Decimated Output

BW = 15 kHz, 24-bit data

0 20 40 60 80 100 120 140 15 10 5 43 0 5 NBW=11 Hz 10 15 No signal INF = 104 dBFS fCLK = 26 MHz dec-by-900 17 dBm input @ 103.25 MHz + 1 kHz 0.5 dBFS output INF = -95 dBFS

dBFS/NBW

Frequency Offset (kHz)

R. SCHREIER

ANALOG DEVICES, INC.

Measured SNR

fIF = 273 MHz, fLO = 269 MHz, fCLK = 32 MHz

100 90 80 OSR =900

SNR (dB)

70 60 50 40 30 20 10 0 -110 -90 -70 -50 AGC range -30 -10 OSR =48

P in (dBm)

44

R. SCHREIER

ANALOG DEVICES, INC.

Summary

Design MOD2 MOD5 2-0 Cascade OSR DR (dB) 500 80 8 100 110 90 Lessons

High OSR is helpful. can yield a very robust design. FF topology has lower cap. area than FB. Multi-bit quantization is needed to get high SNR at low OSR. Must be watchful of gain mismatch and NTF zero error in a cascaded system. An LC tank enables a power-efcient bandpass Mixer+ADC. The loop lter can use both continuoustime and discrete-time resonators.

CT BP (LC)

48

85

Many design choices: /, single-loop/multi-loop, single-bit/multi-bit, lowpass/bandpass, discrete-time/ continuous-time, real/quadrature

45

You might also like

- EC1371 Advanced Analog Circuits L1Document12 pagesEC1371 Advanced Analog Circuits L1RabbitSaviorNo ratings yet

- ADC DAC TheoryDocument24 pagesADC DAC Theoryuser123phcNo ratings yet

- InverterDocument231 pagesInverterMaitrik Shah100% (1)

- 2022 ECM226A Formative Assessment 2Document6 pages2022 ECM226A Formative Assessment 2Maditlhare MolefiNo ratings yet

- Cmos BasicDocument21 pagesCmos BasicAnkesh JaiswalNo ratings yet

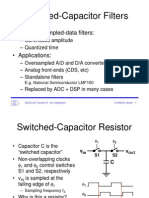

- Switched-Capacitor Filters: - "Analog" Sampled-Data FiltersDocument24 pagesSwitched-Capacitor Filters: - "Analog" Sampled-Data FiltersPushpendra DwivediNo ratings yet

- DelayDocument31 pagesDelayvarun186No ratings yet

- 3 Current SRCDocument10 pages3 Current SRCmelwyn_thomasNo ratings yet

- Pspice TutorialDocument25 pagesPspice Tutorialamar7716dumNo ratings yet

- RDS/RBDS Decoder Audio ICs BU1924/BU1924FDocument5 pagesRDS/RBDS Decoder Audio ICs BU1924/BU1924FLaurentiu IacobNo ratings yet

- ELEN 689 -603 Pipeline ADC’s PerformanceDocument29 pagesELEN 689 -603 Pipeline ADC’s PerformanceInJune YeoNo ratings yet

- Lec2 Frequency ResponseDocument79 pagesLec2 Frequency ResponseAli AhmadNo ratings yet

- 3EJ4 Set 07 Mixed Signal MJDDocument45 pages3EJ4 Set 07 Mixed Signal MJDSoroush AkNo ratings yet

- MCP3202 PDFDocument28 pagesMCP3202 PDFblue11111No ratings yet

- Opamp ModelDocument40 pagesOpamp ModelAMSA84No ratings yet

- 2.7V Dual Channel 12-Bit A/D Converter With SPI Serial InterfaceDocument34 pages2.7V Dual Channel 12-Bit A/D Converter With SPI Serial InterfaceManjunatha Ac100% (1)

- Mart Data2001bDocument30 pagesMart Data2001bdffdfNo ratings yet

- CMOS Analog Design Using All-Region MOSFET Modeling Fundamentals of Sampled-Data CircuitsDocument23 pagesCMOS Analog Design Using All-Region MOSFET Modeling Fundamentals of Sampled-Data Circuitsraju.kprr8862No ratings yet

- Oversampling and Noise Shaping in Sigma-Delta ModulatorsDocument69 pagesOversampling and Noise Shaping in Sigma-Delta ModulatorsKyogbsyNo ratings yet

- CN0350Document7 pagesCN0350Narayan ApteNo ratings yet

- Netzer DS 247 128 SpecsheetDocument8 pagesNetzer DS 247 128 SpecsheetElectromateNo ratings yet

- Ad 7821Document16 pagesAd 7821compilixNo ratings yet

- EE204 Analog Electronics Frequency ResponseDocument61 pagesEE204 Analog Electronics Frequency ResponseAli AhmadNo ratings yet

- NMOS Common-Source Amplifier DesignDocument4 pagesNMOS Common-Source Amplifier DesignRedDotNo ratings yet

- FDocument24 pagesFrotenolabsNo ratings yet

- Analog Electronic Circuits Lab-Module1: Gowra P SDocument5 pagesAnalog Electronic Circuits Lab-Module1: Gowra P SReddyvari VenugopalNo ratings yet

- Micro: Description FeaturesDocument20 pagesMicro: Description FeaturespopcriNo ratings yet

- MRF 5 S 9100 NDocument16 pagesMRF 5 S 9100 NpankajNo ratings yet

- SAR Cyclic and Integrating ADCsDocument50 pagesSAR Cyclic and Integrating ADCsAlberto DanNo ratings yet

- Pspice Tutorial AcDocument89 pagesPspice Tutorial AcZadziorNo ratings yet

- DatasheetDocument24 pagesDatasheetRafael PavanNo ratings yet

- VLSI Architecture Design: IEP On Technology CAD (12-17 May 2008)Document52 pagesVLSI Architecture Design: IEP On Technology CAD (12-17 May 2008)Mohammed ElNeanaeiNo ratings yet

- Multisimm Report 301 Final ProjectDocument3 pagesMultisimm Report 301 Final Projectapi-296881750No ratings yet

- Active LoadDocument69 pagesActive LoadVijay P. LabdeNo ratings yet

- Finite Wordlength Effects in Digital FiltersDocument32 pagesFinite Wordlength Effects in Digital FiltersArunmozhliNo ratings yet

- Lecture 23Document6 pagesLecture 23Rakesh AshokNo ratings yet

- Clock and Data Recovery For Serial Digital CommunicationDocument79 pagesClock and Data Recovery For Serial Digital Communicationquail36No ratings yet

- Ansys Workbench TutorialsDocument13 pagesAnsys Workbench Tutorialsmech118No ratings yet

- 665 Ring OscillatorsDocument13 pages665 Ring OscillatorszuckignoNo ratings yet

- Switched Capacitor 2898320923Document36 pagesSwitched Capacitor 2898320923pardeep184No ratings yet

- MSM6544Document13 pagesMSM6544Shuvamay GuhaNo ratings yet

- ADC DAC DiscreteDocument4 pagesADC DAC DiscretegersonymayerNo ratings yet

- EE236 NGSPICE Simulation of RC and RLC CircuitsDocument15 pagesEE236 NGSPICE Simulation of RC and RLC CircuitsAakanksha JainNo ratings yet

- Datasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic SemiconductorDocument17 pagesDatasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic Semiconductorfernandog251186No ratings yet

- MC145151-2 and MC145152-2: PLL Frequency Synthesizers (CMOS)Document24 pagesMC145151-2 and MC145152-2: PLL Frequency Synthesizers (CMOS)Willington Augusto ArizaNo ratings yet

- Features Description: LTC2368-16 16-Bit, 1Msps, Pseudo-Differential Unipolar SAR ADC With 94.7dB SNRDocument24 pagesFeatures Description: LTC2368-16 16-Bit, 1Msps, Pseudo-Differential Unipolar SAR ADC With 94.7dB SNRrotenolabsNo ratings yet

- PK Aec Lab ManualDocument26 pagesPK Aec Lab ManualkrishnagdeshpandeNo ratings yet

- TIES328 Matlab Exercise 1: Zhdizhan@student - Jyu.fiDocument42 pagesTIES328 Matlab Exercise 1: Zhdizhan@student - Jyu.fiNacho ReyesNo ratings yet

- Moin-10 1109@EIConRus 2019 8657039Document3 pagesMoin-10 1109@EIConRus 2019 8657039Moin SadiNo ratings yet

- Opamp ReportDocument38 pagesOpamp ReportMuhammad SaperNo ratings yet

- UWB FMCW Radar RF Front-End Design for Concealed Weapon DetectionDocument33 pagesUWB FMCW Radar RF Front-End Design for Concealed Weapon DetectionEugenio PasquaNo ratings yet

- AFT05MP075NDocument21 pagesAFT05MP075NjeremyAW2SNo ratings yet

- 16-Bit, Serial Input Multiplying Digital-to-Analog ConverterDocument16 pages16-Bit, Serial Input Multiplying Digital-to-Analog ConverternhbrNo ratings yet

- Introduction to Frequency Selective CircuitsDocument36 pagesIntroduction to Frequency Selective CircuitsPhan Phuong NgocNo ratings yet

- Finalo CDSL ManualDocument86 pagesFinalo CDSL ManualSteny SimsonNo ratings yet

- HSMS-282x Surface Mount RF Schottky Barrier DiodesDocument15 pagesHSMS-282x Surface Mount RF Schottky Barrier Diodeswhynot05No ratings yet

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- حلول لوكDocument2 pagesحلول لوكاحمدعطيهNo ratings yet

- Melvin Bouracho Gen-Ed 2023Document27 pagesMelvin Bouracho Gen-Ed 2023Jam Piana100% (1)

- Transcription M3S2Document21 pagesTranscription M3S2GrowUP. AINo ratings yet

- Questionnaire 1: Money From The Table While The Croupier Isn't Looking". Explain Einstein Quote inDocument3 pagesQuestionnaire 1: Money From The Table While The Croupier Isn't Looking". Explain Einstein Quote inTomislav PetrušijevićNo ratings yet

- Versant Test For HCL 9Document5 pagesVersant Test For HCL 9Huy Phan96% (23)

- TROUBLE CODE - Ma-1Document55 pagesTROUBLE CODE - Ma-1José Rojo EspinozaNo ratings yet

- Teaching Listening Micro-Skills For Listening ComprehensionDocument117 pagesTeaching Listening Micro-Skills For Listening Comprehensionnielsen1990No ratings yet

- A Review On Smart Buildings: June 2021Document4 pagesA Review On Smart Buildings: June 2021Keteng KurniawanNo ratings yet

- MGP Paranoia - Forms PackDocument61 pagesMGP Paranoia - Forms PackAurik FreyNo ratings yet

- General Academic Vacancy PositionDocument282 pagesGeneral Academic Vacancy PositionkaranNo ratings yet

- CICLing2011 Manning TaggingDocument19 pagesCICLing2011 Manning TaggingMuhammad AbrarNo ratings yet

- StatisticsDocument1 pageStatisticsNathan Stuart The Retarded idiotNo ratings yet

- Physics Report Simple PendulumDocument3 pagesPhysics Report Simple PendulumGracey- Ann Johnson100% (2)

- Structural Frame Worksheet - UpdatedDocument3 pagesStructural Frame Worksheet - Updatedapi-522554997No ratings yet

- Population Growth: SC.912.L.17.5 Analyze How Population Size Is Determined by Births, Deaths, ImmigrationDocument14 pagesPopulation Growth: SC.912.L.17.5 Analyze How Population Size Is Determined by Births, Deaths, ImmigrationBrianna DominguezNo ratings yet

- 1.my Feelings ADocument2 pages1.my Feelings ACath TempestNo ratings yet

- KSH13007 KSH13007: SEMIHOW REV.A1, Oct 2007Document6 pagesKSH13007 KSH13007: SEMIHOW REV.A1, Oct 2007Manolo DoperNo ratings yet

- Journal - Development PlanDocument11 pagesJournal - Development Planadeyemi kehindeNo ratings yet

- Indigo (The Search For True Understanding and Balance)Document197 pagesIndigo (The Search For True Understanding and Balance)Trunk Boolean100% (1)

- MOVIE4UDocument10 pagesMOVIE4USGNo ratings yet

- Mt271 Lecture Notes 1Document13 pagesMt271 Lecture Notes 1Ahmed MasoudNo ratings yet

- Example of Discussion in Research PaperDocument6 pagesExample of Discussion in Research Paperipkpzjbkf100% (1)

- Line Out Building SettingDocument1 pageLine Out Building SettingvkNo ratings yet

- Psych Stats CIA-2030206 Method FileDocument39 pagesPsych Stats CIA-2030206 Method FileAranya BanerjeeNo ratings yet

- UP ACME - Chem 28 - 2nd LE SamplexDocument4 pagesUP ACME - Chem 28 - 2nd LE SamplexDoom RefugeNo ratings yet

- Pointers in Grade 6.Document4 pagesPointers in Grade 6.Jobert SimoyNo ratings yet

- Dinosaur Lesson by SlidesgoDocument41 pagesDinosaur Lesson by SlidesgoDonalyn PaderesNo ratings yet

- Reading Text On The Rule of The Road by A.G. GardinerDocument2 pagesReading Text On The Rule of The Road by A.G. GardinerSilidNo ratings yet

- Medica2023 ExhibitorsDocument288 pagesMedica2023 ExhibitorsHamza BadraneNo ratings yet

- Eng201 ch7 Accuracy Clarity Conciseness CoherenceDocument2 pagesEng201 ch7 Accuracy Clarity Conciseness CoherenceAyesha MughalNo ratings yet