Professional Documents

Culture Documents

Laboratory Experiment 6 - Analog To Digital

Uploaded by

yellowsubmirOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Laboratory Experiment 6 - Analog To Digital

Uploaded by

yellowsubmirCopyright:

Available Formats

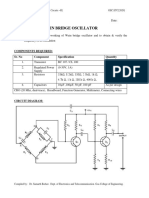

LABORATORY EXPERIMENT 6 Analog to Digital Conversion Purpose: The objective of this experiment is to design example analog to digital converters

(ADC or A/D Converter) using: 1) a two-bit flash (parallel) converter; 2) a four-bit counter (servo) type converter, and 3) a monolithic ADC chip (ADC0804). After designing the circuit configurations determine which gives better performance, speed, cost effectiveness, etc. Pre-laboratory Design: The pre-laboratory design consists of a preliminary design with values calculated using equations found in the ADC Design Notes and the literature. Simulations (MultiSim) for each of the three configurations are required prior to prototyping the circuits. Part 1: Flash A/D Converter The first part of this experiment deals with using a flash (parallel) analog to digital converter to illuminate two LEDs in a manner that corresponds to the value of the analog input. Figure 1 shows the elements of the flash A/D converter.

Figure 1: Two-Bit Flash A/D Converter Configuration.

Implement the comparators with the LM339 Comparators, not a LM741, because the LM741 does not have a rail-to-rail output. The LM339 also has an open-collector output with means it cannot source current directly and therefore requires a pull-up resistor ( like 1 to 10k resistors connected from the LM339 output to the supply rail). The code converter will consist of logic gates that convert the inputs A, B, and C to true binary outputs X and Y. Create a logic table for the code converter and then implement with NAND logic gates. Note that NOT gates can be created by tying the

BIEN-4390 Spring Semester

input pins of the NAND gate together and having a single input applied to them. Try to use as little real estate (chips, resistors, space, etc.) as possible.

Laboratory Measurements/Calculations: 1. 2. 3. 4. 5. 6. Calibration Curve: Digital Outputs vs. Analog Inputs. Find the Conversion Gain Linearity: Find linear regression line for calibration curve. Resolution: Bit resolution (mV). Zero Offset: The digital output when analog input is set to zero. Step Size: Analog input voltage required to change the digital output one bit.

Part 2: Counter (servo) Type Converter The next part of this experiment incorporates a four-bit UP/DOWN counter in a analog to digital converter. Figure 2 shows the configuration for this converter.

Figure 2: Counter (servo) Type Converter Configuration.

When implementing this circuit, R should be at least 10k to limit the current sourced from the CD4050 Buffer device. Also LEDs can be connected to the four bit digital outputs from the five volt power supplies (+Vs) through current limiting resistors (limit current to around 4mA). Note also that the LM339 supply voltage should be higher than the supply voltages of the other chips (greater than 5V) because it does not work with rail-to-rail inputs. The input voltage, Vin, can be supplied from a function generator that

BIEN-4390 Spring Semester

can provide precisely settable DC voltages. Use another function generator to supply the clock input for the 74L191. Make sure to offset the signal appropriately. Eliminate ground loops.

Laboratory Measurements/Calculations: 1. 2. 3. 4. 5. 6. Calibration Curve: Digital Outputs vs. Analog Inputs. Find the Conversion Gain Linearity: Find linear regression line for calibration curve. Resolution: Bit resolution (mV). Zero Offset: The digital output when analog input is set to zero. Step Size: Analog input voltage required to change the digital output one bit.

Part 3: Monolithic A/D Converter Chip The final part of this experiment is to use a commercially available monolithic A/D converter chip to produce 8-bit analog to digital conversion. Refer to the ADC0804 specification sheet for performance parameters and design details. Connect the A/D chip to LED indicators that will represent the most significant outputs bits.

R9

10k

VCC

5V

C1

150pF

1 CS/

U1

Vcc 20

RD/

CLKR

19

DGND

DGND

3 WR/ DB0 18

R1

1.2k

LED1 R2

1.2k

CLK

DB1

17

LED2 LED3 LED4 LED5 LED6 LED7 LED8

StartConversion

INTR/

DB2

16

R3

1.2k

Analog Input

Vin C2

0.1F

Vin+

DB3

15

R4

1.2k

Vin-

DB4

14

R5

1.2k

AGND

DB5

13

R6

1.2k

Vref / 2

2.5V

Vref/2

DB6

12

R7

1.2k

10

C3

0.1F

DGND

DB7

11

R8

1.2k

ADC0804

C4

10F

DGND

BIEN4390 - Biomedical Instrumentation Design Laboratory Monolithic Successive Approximation A/D Converter

DGND

Figure 3: Monolithic Successful Approximation A/D Configuration

BIEN-4390 Spring Semester

Laboratory Measurements/Calculations: 1. 2. 3. 4. 5. 6. Calibration Curve: Digital Outputs vs. Analog Inputs (for 3 MSB). Find the Conversion Gain Linearity: Find linear regression line for calibration curve. Resolution: Bit resolution (mV). Zero Offset: The digital output when analog input is set to zero. Step Size: Analog input voltage required to change the digital output one bit.

BIEN-4390 Spring Semester

You might also like

- Digital Lab IDL-800 Specs Breadboard Power Supply Function Generator Voltmeter DisplaysDocument2 pagesDigital Lab IDL-800 Specs Breadboard Power Supply Function Generator Voltmeter DisplaysyangfakirNo ratings yet

- MNNDocument19 pagesMNNapsNo ratings yet

- Unit III 8086 Microprocessor InterfacingDocument26 pagesUnit III 8086 Microprocessor InterfacingRammanohar Lokiya100% (1)

- Microcontroller Based Weighing MachineDocument7 pagesMicrocontroller Based Weighing MachineNaveen NaniNo ratings yet

- Fuji 116 TimersDocument4 pagesFuji 116 TimersJoe ZanterNo ratings yet

- Lecture Nine 8086 Microprocessor Memory and I/O Interfacing: March 2020Document23 pagesLecture Nine 8086 Microprocessor Memory and I/O Interfacing: March 2020ally0% (1)

- Project Report on Security System SwitcherDocument19 pagesProject Report on Security System SwitcherscribdsunshineNo ratings yet

- CEI44: Network and Hardware Support Lab 1: Network Creation Planning StageDocument11 pagesCEI44: Network and Hardware Support Lab 1: Network Creation Planning StageSvetlanaNo ratings yet

- VISA LabviewDocument22 pagesVISA LabviewVinitaVartakNo ratings yet

- Lab 6 ADCDocument6 pagesLab 6 ADCYaz PuteraNo ratings yet

- RP Jain Adc DacDocument27 pagesRP Jain Adc DacAnand SinghNo ratings yet

- Automatic Night Lamp With Morning AlarmDocument16 pagesAutomatic Night Lamp With Morning Alarms.reeganNo ratings yet

- Experiment No.7 MicroProcessor PDFDocument7 pagesExperiment No.7 MicroProcessor PDFM. Ahmad RazaNo ratings yet

- Automatic Speed Control Based On IotDocument5 pagesAutomatic Speed Control Based On IotDhruva CasNo ratings yet

- A2 Electrical Circuits and Power Jan 2021Document34 pagesA2 Electrical Circuits and Power Jan 2021narenmaniam0% (1)

- L293D Motor Driver PDFDocument6 pagesL293D Motor Driver PDFPedro Cu Aguirre100% (1)

- Electric GoKart Microcontroller Arduino ATMEGA 2560Document10 pagesElectric GoKart Microcontroller Arduino ATMEGA 2560Trista BintoroNo ratings yet

- MCB 51-2 Quick Start Guide 1Document5 pagesMCB 51-2 Quick Start Guide 1GAUTI2212No ratings yet

- Microprocessor 8085 Lab Manual PDFDocument29 pagesMicroprocessor 8085 Lab Manual PDFvp_choudhary33% (3)

- PLC Manual FinalDocument32 pagesPLC Manual FinalMuhammad Usama Muhammad SaleemNo ratings yet

- Fpga ManualDocument7 pagesFpga ManualRahul SharmaNo ratings yet

- 8086 Project TitlesDocument15 pages8086 Project TitlesBahiru Betela BekeleNo ratings yet

- Fastest Finger First IndicatorDocument2 pagesFastest Finger First Indicatorchakralabs0% (1)

- Lecture Notes 1Document59 pagesLecture Notes 1Prabal RawatNo ratings yet

- 8051 Student ProjectsDocument25 pages8051 Student ProjectsAbhijay Sisodia100% (1)

- Lecture 12 (ADC) Rv01Document47 pagesLecture 12 (ADC) Rv01Amirul HaqimieNo ratings yet

- Timers in 8051: How and Why to Use ThemDocument5 pagesTimers in 8051: How and Why to Use ThemKaran AroraNo ratings yet

- CISE414 - Unit 04 AVR Atmega PortsDocument30 pagesCISE414 - Unit 04 AVR Atmega Portsمحمد حمدNo ratings yet

- 8051 Vs Motorola 68HC11Document19 pages8051 Vs Motorola 68HC11zuanne83No ratings yet

- Vacation Training ELEC 1200 Working with NI Instruments MultisimDocument5 pagesVacation Training ELEC 1200 Working with NI Instruments Multisimjaya1816No ratings yet

- Battery Level IndicatorDocument17 pagesBattery Level IndicatorMratunjay ChouhanNo ratings yet

- Serial Communication of Matlab With Arduino: A Project Report OnDocument18 pagesSerial Communication of Matlab With Arduino: A Project Report OnAnonymous TbJ5Lo8nfPNo ratings yet

- Automated Smoking Zone Monitoring & Alerting Project: Block DiagramDocument2 pagesAutomated Smoking Zone Monitoring & Alerting Project: Block DiagramIsraelPerezSanchez100% (1)

- Closed Loop DC Motor Speed ControlDocument3 pagesClosed Loop DC Motor Speed ControlKhayaz KunhabduNo ratings yet

- Water Automation Project ReportDocument23 pagesWater Automation Project ReportMahdee NafisNo ratings yet

- MP 8086 Lab Manual TRAINER KITDocument70 pagesMP 8086 Lab Manual TRAINER KITKavitha Subramaniam100% (1)

- EEEE2201: Electrical and Electronic Measurement Lecture Notes Chap 3: Measurement of Resistance - Potentiometers IDocument8 pagesEEEE2201: Electrical and Electronic Measurement Lecture Notes Chap 3: Measurement of Resistance - Potentiometers IFataahu Nyuydze KehkimokiNo ratings yet

- ADC (Analog-To-Digital Converter)Document11 pagesADC (Analog-To-Digital Converter)Abdullah Muzammil0% (1)

- Home Appliances Controlling Using Bluetooth On Android Mobile AbstractDocument2 pagesHome Appliances Controlling Using Bluetooth On Android Mobile AbstractramyaNo ratings yet

- ARM Architecture - L5Document7 pagesARM Architecture - L5Maniswari MothukuruNo ratings yet

- Interfacing Programs For 8085Document37 pagesInterfacing Programs For 8085archankumarturagaNo ratings yet

- Power Supply For 8051 MicrocontrollerDocument5 pagesPower Supply For 8051 MicrocontrollerAshok Ekanath KalangeNo ratings yet

- Expt 5 - Wein Bridge Oscillator (2020)Document3 pagesExpt 5 - Wein Bridge Oscillator (2020)samarthNo ratings yet

- Washing Machine Control Using 8051 MicrocontrollerDocument4 pagesWashing Machine Control Using 8051 MicrocontrollerPrasath MurugesanNo ratings yet

- Electronics Ii: Engr. Ryann AlimuinDocument162 pagesElectronics Ii: Engr. Ryann AlimuinJulius RicardeNo ratings yet

- C-Bus Product Overview Catalogue C0000239 PDFDocument144 pagesC-Bus Product Overview Catalogue C0000239 PDFAhmadBintangNegoroNo ratings yet

- EMBEDDED BASED Automatic AUDITORIUM CONTROLLER 0TH REVDocument36 pagesEMBEDDED BASED Automatic AUDITORIUM CONTROLLER 0TH REVspringsource100% (1)

- Bicmos TechnologyDocument37 pagesBicmos TechnologyPriya SinghNo ratings yet

- Temprature Sensing SystemDocument17 pagesTemprature Sensing Systemnp2930No ratings yet

- Cell Phone DetectorDocument16 pagesCell Phone DetectorअमितनिमसेNo ratings yet

- Government College University FaisalabadDocument4 pagesGovernment College University FaisalabadRauf SanwalNo ratings yet

- Familiarization With MDA8086 and MTS86C Microprocessor TrainersDocument18 pagesFamiliarization With MDA8086 and MTS86C Microprocessor TrainersAnik Mazumder100% (1)

- Esp32 Wroom 32d - Esp32 Wroom 32u - Datasheet - enDocument28 pagesEsp32 Wroom 32d - Esp32 Wroom 32u - Datasheet - enFranco Rivadeneyra100% (1)

- Notes04 ADCDocument9 pagesNotes04 ADCHosam BendaryNo ratings yet

- 8085 and 8086 Microprocessor FeaturesDocument82 pages8085 and 8086 Microprocessor FeaturesManoj KollamNo ratings yet

- Shortform Guide: Version: 5.2/1 Edition: 26 January 2015Document70 pagesShortform Guide: Version: 5.2/1 Edition: 26 January 2015Sandro ValenteNo ratings yet

- Interfacing To The Analog WorldDocument47 pagesInterfacing To The Analog WorldRM ZhaloNo ratings yet

- Experiment No. 4 ADC PDFDocument16 pagesExperiment No. 4 ADC PDFRia Cordova0% (1)

- Adc Lab Pic18Document23 pagesAdc Lab Pic18Bolarinwa Joseph100% (1)

- A 9-Bit Flash Analog To Digital Convertor: Gururaj Balikatti, Monisha D, Manuja A, Priyanka S R, Rohini M RDocument3 pagesA 9-Bit Flash Analog To Digital Convertor: Gururaj Balikatti, Monisha D, Manuja A, Priyanka S R, Rohini M REditor IJRITCCNo ratings yet

- PBS CCMD CVMD Administrator GuideDocument40 pagesPBS CCMD CVMD Administrator GuidesharadcsinghNo ratings yet

- Corporate Presentation Codex International Fev 2022Document9 pagesCorporate Presentation Codex International Fev 2022Stephane SeguierNo ratings yet

- ACL-PDC-01 - Rev01 (Procurement Document Control)Document3 pagesACL-PDC-01 - Rev01 (Procurement Document Control)Mo ZeroNo ratings yet

- Risk in Clean RoomDocument9 pagesRisk in Clean RoomABEERNo ratings yet

- Real Time Braille To Speech Using PythonDocument10 pagesReal Time Braille To Speech Using PythonKali LinuxNo ratings yet

- Nordson EFD Ultimus I II Operating ManualDocument32 pagesNordson EFD Ultimus I II Operating ManualFernando KrauchukNo ratings yet

- Ch05 - Deformation - HamrockDocument14 pagesCh05 - Deformation - HamrockMuhammad Mansor BurhanNo ratings yet

- Slippery? Contradictory? Sociologically Untenable? The Copenhagen School RepliesDocument10 pagesSlippery? Contradictory? Sociologically Untenable? The Copenhagen School RepliesDaniel CorrenteNo ratings yet

- Sunward Rotary Drilling Rig Maintenance ManualDocument35 pagesSunward Rotary Drilling Rig Maintenance ManualPaul Kenneth AbayataNo ratings yet

- Biocompatibility and HabitabilityDocument143 pagesBiocompatibility and HabitabilitySvetozarKatuscakNo ratings yet

- 942 FullDocument9 pages942 FullZulfah MidahNo ratings yet

- EPABX User's Guide for Making Calls and Using FeaturesDocument4 pagesEPABX User's Guide for Making Calls and Using FeaturesPraveen KumarNo ratings yet

- Paper 2 Answer SPMDocument12 pagesPaper 2 Answer SPMSylarkNo ratings yet

- Activities For Responding To Reading in Year 2Document59 pagesActivities For Responding To Reading in Year 2lancashireliteracy100% (1)

- SATA Product Manual: Standard ModelsDocument32 pagesSATA Product Manual: Standard ModelsEdy AprilyantoNo ratings yet

- NFA To DFA Conversion: Rabin and Scott (1959)Document14 pagesNFA To DFA Conversion: Rabin and Scott (1959)Rahul SinghNo ratings yet

- Chapter 3Document12 pagesChapter 3Raymond LeoNo ratings yet

- TB MBA 101 Management Behavioural ProcessDocument51 pagesTB MBA 101 Management Behavioural Processchetan_don0% (1)

- Ese 570 Mos Inverters Static Characteristics: Kenneth R. Laker, University of Pennsylvania, Updated 13feb12 1Document44 pagesEse 570 Mos Inverters Static Characteristics: Kenneth R. Laker, University of Pennsylvania, Updated 13feb12 1het shahNo ratings yet

- SPMPDocument39 pagesSPMPAnkitv PatelNo ratings yet

- 08 - Chapter 1 - Waveguide-Transmission Line - Microstrip LinesDocument76 pages08 - Chapter 1 - Waveguide-Transmission Line - Microstrip Linesgilberto araujoNo ratings yet

- 26th IEEEP All Pakistan Students' SeminarDocument3 pages26th IEEEP All Pakistan Students' Seminarpakipower89No ratings yet

- Laboratory Activity No. 01 - Properties of LiquidDocument2 pagesLaboratory Activity No. 01 - Properties of LiquidCzarina Relleve0% (1)

- Elements of TQM: Dr. Sanjay MahalingamDocument7 pagesElements of TQM: Dr. Sanjay Mahalingamuday saiNo ratings yet

- Checklist of Bats From Iraq-Mammalian Biology 2020Document14 pagesChecklist of Bats From Iraq-Mammalian Biology 2020Adil DalafNo ratings yet

- DX DiagesDocument36 pagesDX DiagesBpbd Kota BengkuluNo ratings yet

- Educ 61 Module 5 ActivityDocument4 pagesEduc 61 Module 5 ActivityMitchille GetizoNo ratings yet

- Industrial Applications of Olefin MetathesisDocument7 pagesIndustrial Applications of Olefin Metathesisdogmanstar100% (1)

- Public Dealing With UrduDocument5 pagesPublic Dealing With UrduTariq Ghayyur86% (7)

- Presostatos KPI 1Document10 pagesPresostatos KPI 1Gamaliel QuiñonesNo ratings yet