Professional Documents

Culture Documents

Electronics 2007

Uploaded by

Haraprasad DolaiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electronics 2007

Uploaded by

Haraprasad DolaiCopyright:

Available Formats

Ex/ME/ET/T/123/116/2007 FIRST MECHANICAL ENGINEERING EXAMINATION, 2007 ( 2nd Semester ) ELECTRONICS Time : Three hours ( 50 marks from each

part ) Use a separate Answer-Script for each part PART - I Answer Q. No. 1 and any two from the rest : 1. a) Draw the following Ckt diagrams (any 2) i) Capacitor filter Ckt for full-wave rectifier 2+2=4 Full Marks : 100

ii) Fixed bias Ckt of a BJT iii) A diode based OR gate iv) A series clipper Ckt using diodes. b) Fill in the blanks : i) The band gap of Ge temperature. ii) Under the saturation condition of a BJT, the conector base jn is biased. iii) Zener breakdown occurs at a field of approximately V/m. iv) The electron mobility is usually mobility in the same crystal. [ Turn over than the hole biased and the emitter base is jn is 16=6 with the increase of

[2] v) In a full wave rectifier Ckt, the Peak Inverse Voltage is the maximum transformer voltage measured 12. Ckts. from midpoint to either end. vi) Zener diodes are used in 2.

[7] b) State disadvantages of SR Flip-Flop. How can it be overcomed ? 2+2

a) Can you design a T-type and D-Type Flip-Flop using SR Flip-Flop. If yes, design. If not state reason. 2+2+2

a) Draw the Ckt diagram of a bridge rectifier and show the current flow paths over two half cycles of the input. What are the merits of a bridge rectifier over the full wave rectifier ? 3+3=6

b) State disadvantage of JK Flip-Flop. How can it be overcomed ? 2+2

b) Show that for a full wave rectifier Ckt, if RL and Rf respectively denote the load resistance and the forward resistance of the diode, then the efficiency of rectification

r is given by :

r =

81 2 % 1 + (R f / R L )

c) Each diode in the addjacent fig. is describe by a linearized volt-ampere characteristics, with incremental resistance r and offset voltage V . Diode D1 is Ge with V = 0 3V,

r = 25 whereas D2 is silicon with V = 0 6V, and r = 15 . Find the diode currents if R = 50K .

[4] d) Briefly explain what do you mean by Early Effect with reference to a BJT ? 4. 2 5.

[5] a) Consider a graded semiconductor placed along the +ve x direction. Let the hole concentrations at two points x = a and x = b be Pa and Pb per c.c. If Vba designate the potential difference between these two points, then show that Pa = Pr. eVba / VT where VT stands for the volt equivalent of temperatue. 6 b) What do you mean by the dynamic resistance of a p n junction diode ? Show that under forward bias condition, the dynamic resistance of a Ge diode is approximately given by

a) In the Clipper Ckt shown below, the diodes are ideal. Plot Vo Vs Vi indicating all intercepts, slopes and voltage levels. Sketch Vo if Vi = 42 Sin50t volts. Assume that each diode has an offset voltage of V = 1 V . 7

b) What must be the open Ckt source voltage to provide 0.8V peak-to-peak at an amplifiers input terminals, if the amplifier has an input resistance of 5k for the following source resistances : i) 800 ii) 5k . 5

rf 26 where I is the forward current in mA. I

show that the output impedence Zo is given by : Z0 =

=

c) From the hybrid equivalent of a general transistor Ckt,

hi h0 h r h f

1 if h0

hi

if Rs = O

c) Draw the hybrid parameter equivalent Ckt of a common emitter BJT Ckt. Briefly explain how can you determine the parameter hfc graphically. 2+2=4

Rs = 8

where Rs is the source resistance. PART - II Answer any five questions 6. a) Prove the following using Boolean Algebric theorems. 1.

d) A transistor amplifier in CE mode couples a source of internal resistance of 1k to a load of 20k . Find the input resistance of the amplifier given h ie = 1 2 k, h re = 3 10 , h fe = 200 and h oe

4

= 40 k.

A + AB + AB = A + B

[ Turn over

[6] 2. A B + AB + AB = A + B 3. ABC + ABC + ABC + ABC = A 2+2+2 3.

[3] a) Prove that the minimum conductivity of a semiconductor sample occurs when the thermal equilibrium conc. of electrons is given by 0 = i p / n where i is the intrinsic carrier conc. What is the expression for the minim conductivity ? b) Determine the resistances RB and Re for the BJT inverter shown in the fig., provided, I c sat = 8mA 5 5+2=7

b) Why NOR and NAND gets are called as Universal gates ? 2 c) State the application of EX-OR gate. 7. 2

a) Design NOT, AND and OR operation Using NAND and NOR gates only. 8

b) State De Morgans theorem statement. State Boolean Expression. 8. 1+1

a) Draw the symbol of 3-input AND gate. State Boolean Equation. State truthtable. 1+1+2

b) State truthtable of Half adder circuit. Design the same. 2+4 9. Perform the following subtraction using twos complement method. i) 10101 10011 ii) 100111 110111 10 4

c) Given that IC Q = 2mA and ICEQ = 12V, determine R1 and RC for the voltage divider bias configuration shown in the following figure : 6

iii) 101110 111 10.

iv) 101 11010

a) Minimize the following logic function using K-Map Y=

m (0, 1, 2, 3, 5, 7, 8, 9, 11, 14)

b) State truthtable of Half subtractor. Design the same. 2+4 11. a) Design a clocked JK flip-flop using S-R Flip-Flop. State the truthtable. 4+2

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

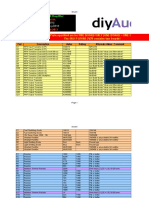

- P DIYAB 2V20 DiyAB Amp BomDocument8 pagesP DIYAB 2V20 DiyAB Amp BomOgyne DacoycoyNo ratings yet

- Bu406 DDocument3 pagesBu406 Danon_136451958No ratings yet

- Ifm SA5030 - LIQU 20160912 IODD11 enDocument14 pagesIfm SA5030 - LIQU 20160912 IODD11 enAnu R RemananNo ratings yet

- Project Report On Speed Control of DC Motor by Using PWM TechniqueDocument77 pagesProject Report On Speed Control of DC Motor by Using PWM TechniqueSBONGISENI MASONDO100% (2)

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument4 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDjalma MotaNo ratings yet

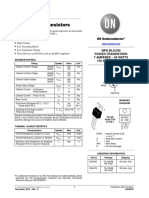

- TIP47 / TIP48 / TIP49 / TIP50 NPN Silicon Transistor: FeaturesDocument5 pagesTIP47 / TIP48 / TIP49 / TIP50 NPN Silicon Transistor: FeaturesЮра ПетренкоNo ratings yet

- LM1203NDocument16 pagesLM1203NAasif ChaudhryNo ratings yet

- Ls Ig5a User ManualDocument177 pagesLs Ig5a User ManualHoàng BửuNo ratings yet

- Mackie 1402-VLZ Pro Service ManualDocument12 pagesMackie 1402-VLZ Pro Service ManuallesoundNo ratings yet

- Frequency Response of BJT AmplifiersDocument14 pagesFrequency Response of BJT AmplifiersRitesh KumarNo ratings yet

- RM With Input Blend CapDocument1 pageRM With Input Blend CapRobWileyNo ratings yet

- Malvino MCQDocument33 pagesMalvino MCQハンター ジェイソンNo ratings yet

- BJT Transfer Characteristics: 1 Objective/AIMDocument12 pagesBJT Transfer Characteristics: 1 Objective/AIMVinay Noel AtluriNo ratings yet

- Topic 1.part1Document71 pagesTopic 1.part1Apek OweNo ratings yet

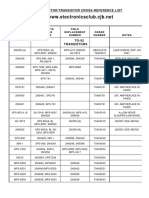

- Boca Semiconductor Corp. BSC: Continental Device India LimitedDocument2 pagesBoca Semiconductor Corp. BSC: Continental Device India LimitedDj-Wilmer GalvanNo ratings yet

- Electronics Module 7Document3 pagesElectronics Module 7mk07 natNo ratings yet

- chp4 - BJT AMPLIFIER - NOTESDocument21 pageschp4 - BJT AMPLIFIER - NOTESNaim NizamNo ratings yet

- BD135, BD137, BD139 Plastic Medium Power Silicon NPN TransistorDocument4 pagesBD135, BD137, BD139 Plastic Medium Power Silicon NPN TransistorCalin LuchianNo ratings yet

- Fig. 4.1: Different TransistorsDocument10 pagesFig. 4.1: Different Transistorsmsicoie1851No ratings yet

- Microelectronics: Circuit Analysis and DesignDocument19 pagesMicroelectronics: Circuit Analysis and DesignMei QiiNo ratings yet

- Discover Discrete Automation SensorsDocument9 pagesDiscover Discrete Automation SensorsAyase ManamiNo ratings yet

- DEE20023 Chapter 3 (B) BIPOLAR JUNCTION TRANSISTOR SESI II 20222023Document23 pagesDEE20023 Chapter 3 (B) BIPOLAR JUNCTION TRANSISTOR SESI II 20222023Muhd ZarifNo ratings yet

- Vignan BTech Syllabus PDFDocument257 pagesVignan BTech Syllabus PDFdevyani_patilNo ratings yet

- MikrotikDocument5 pagesMikrotikPrem KumarNo ratings yet

- Mje15028-15031 DatasheetDocument3 pagesMje15028-15031 DatasheetlektiralektiraNo ratings yet

- 7-Circuit 500mA Darlington Transistor Array with Clamp DiodesDocument5 pages7-Circuit 500mA Darlington Transistor Array with Clamp DiodesRamasokolor778No ratings yet

- Power TransistorDocument37 pagesPower Transistorsaikarthick023No ratings yet

- Panel Mounting Type, 5 Digit Display Unit D5Y/D5W SeriesDocument8 pagesPanel Mounting Type, 5 Digit Display Unit D5Y/D5W Serieszakky firmaNo ratings yet

- lm393 NDocument24 pageslm393 NL oNo ratings yet

- Reemplazos Transistores PEAVEY Ej 70484140Document24 pagesReemplazos Transistores PEAVEY Ej 70484140Josue Hernandez Gutierrez100% (2)