Professional Documents

Culture Documents

A Low Power Grid Connected Photo Voltaic Inverter

Uploaded by

totovasiOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Low Power Grid Connected Photo Voltaic Inverter

Uploaded by

totovasiCopyright:

Available Formats

Undergraduate ThesIs Feport

l0N F0N0f l0N F0N0f l0N F0N0f l0N F0N0f 6fl0 6fl0 6fl0 6fl0 0000l00 0000l00 0000l00 0000l00

F00l090ll8l0 F00l090ll8l0 F00l090ll8l0 F00l090ll8l0 l90fl0f l90fl0f l90fl0f l90fl0f

by

Anthony Kahl

SubmItted for the degree,

8achelor of EngIneerIng (Honours)

n the dIvIsIon of ElectrIcal EngIneerIng.

0epartment of InformatIon TechnoIogy and

EIectrIcaI EngIneerIng

UnIversIty of ueensIand

Dctober 2002

declare that the work submItted In thIs thesIs Is my own, except as

acknowledged In the text and footnotes, and has not been prevIously

submItted for a degree at the UnIversIty of Queensland or any other

InstItutIon.

Anthony KahI

I wouId IIke to thank 0r Ceoff WaIker for hIs tIme and guIdance

throughout thIs year. HIs enthusIasm for the topIc matter was aIways

refreshIng. He couId be counted on to gIve vaIuabIe Input at crucIaI tImes

or when progress had staIIed, aIthough somethIng about '...goose chase'

keeps comIng to mInd.

Abstract

0evelopment of clean, renewable, economIc energy sources has been

central to research conducted by many engIneers and scIentIsts worldwIde,

partIcularly In the last few decades. As current technologIes Improve and

manufacturIng costs fall more doors are beIng opened to researchers In the

fIeld of renewable energy productIon. Dne of these technologIes Is solar

energy, In partIcular photovoltaIc (P7) power generatIon.

The UnIversIty of Queensland currently has a 12 panel, 720W P7 array

Installed on the roof of Its central engIneerIng buIldIng. ThIs project

concerns the InterconnectIon of such an array to an exIstIng utIlIty grId. ThIs

Involves conversIon of 0C P7 power to AC power of suItable qualIty to be

Injected Into the grId. ssues of grId protectIon, power factor and power

poInt trackIng also demand regard.

Project CoaI - To research, desyn and construct a Low Power Crd

Connected Power lnverter jor Photovoltac alcatons.

8asIc DperatIon of the Inverter Is accomplIshed In two stages. They Involve

the conversIon of the 12 - 240C7 P7 output to J500C7 followed by InversIon

to 2407AC. The unIt also electrIcally Isolates the panel from the grId vIa a

hIgh frequency power transformer and optIcally Isolated feedback

technIques.

v

TabIe of Contents

1.0 INTRODUCTION................................................................................................. 1

1.1 THE SUN'S POWER ................................................................................................ 1

1.2 SOLAR ENERGY LOGISTICS AND FEASIBILITY....................................................... 2

1.2 Cost................................................................................................................... 2

1.2 PJ Lifetime ....................................................................................................... 2

1.2 Grid Connection ............................................................................................... 2

2.0 PV POWER HANDLING.................................................................................... 3

2.1 FOCUS................................................................................................................... 3

2.2 PRIMARY OBJECTIVES........................................................................................... 4

2.3 SPECIFICATIONS AND FEASIBILITY........................................................................ 5

Technical specifications ......................................................................................... 5

Efficiencv ................................................................................................................ 5

Si:e.......................................................................................................................... 6

Reliabilitv ............................................................................................................... 6

Cost......................................................................................................................... 7

Grid Connection ..................................................................................................... 7

Australian Standards .............................................................................................. 8

3.0 PV TECHNOLOGY BACKGROUND............................................................... 9

3.1 PHOTOVOLTAICS................................................................................................... 9

Cell/Panel Characteristics ..................................................................................... 9

J-I Relationship...................................................................................................... 9

3.2 POWER CONVERSION .......................................................................................... 11

Switch-mode Technologv...................................................................................... 11

Tvpical Solution.................................................................................................... 11

Isolation................................................................................................................ 11

DC-DC Conversion .............................................................................................. 12

DC-AC Inversion.................................................................................................. 14

Converter Control ................................................................................................ 16

4.0 CONVERTER DESIGN..................................................................................... 18

4.1 TOPOLOGY SELECTION ....................................................................................... 18

4.2 POWER STORAGE ................................................................................................ 19

4.3 HALF BRIDGE DUAL ........................................................................................... 20

Isolation................................................................................................................ 21

Isolated Control Options ...................................................................................... 22

Switch Selection.................................................................................................... 30

Gate Drive ............................................................................................................ 32

Over-voltage Snubber........................................................................................... 32

vi

Inductor Selection................................................................................................. 33

Power Transformer .............................................................................................. 34

4.4 FULL BRIDGE INVERTER ..................................................................................... 36

Switch Selection.................................................................................................... 36

Gate Drive ............................................................................................................ 37

Output Filter......................................................................................................... 38

4.5 CURRENT AND VOLTAGE SENSING...................................................................... 38

DC Bus Joltage .................................................................................................... 38

AC Bus Joltage..................................................................................................... 39

AC Current ........................................................................................................... 40

Offset Reference Joltage ...................................................................................... 41

4.6 CONVERTER MASTER CONTROL ......................................................................... 42

Processor Selection .............................................................................................. 43

RS485 Interface .................................................................................................... 44

Software................................................................................................................ 44

4.7 POWER SUPPLIES ................................................................................................ 45

PJ Side ................................................................................................................. 45

Grid Side............................................................................................................... 45

4.8 PHYSICAL LAYOUT ............................................................................................. 46

Strav Inductance................................................................................................... 46

Surface Mount Devices......................................................................................... 47

5.0 CONVERTER PERFORMANCE..................................................................... 48

5.1 DC-DC CONVERTER OPERATION....................................................................... 48

Boost Operation.................................................................................................... 48

Gate Drive ............................................................................................................ 48

SG2524 and PWM Filter Operation..................................................................... 49

Efficiencv .............................................................................................................. 49

5.2 CONTROLLER OPERATION................................................................................... 51

5.3 DC-AC INVERTER OPERATION........................................................................... 51

5.4 COST................................................................................................................... 52

5.5 SIZE .................................................................................................................... 52

6.0 CONCLUSION.................................................................................................... 53

6.1 SUMMARY AND EVALUATION............................................................................. 53

6.2 FUTURE WORK ................................................................................................... 53

Efficiencv .............................................................................................................. 53

Code Development................................................................................................ 54

7.0 REFERENCES.................................................................................................... 56

8.0 APPENDICES ..................................................................................................... 58

TabIe of FIgures

Figure 1. PJ Window Shades 1

Figure 2. Converter Prototvpe 3

Figure 3. PJ J-I Characteristics 10

Figure 4. Tvpical Conversion Svstem 11

Figure 5. Push-Pull Converter 13

Figure 6. Resonant Half Bridge Dual Converter 13

Figure 7. Full Bridge Inverter 14

Figure 8. Converter Block Diagram 18

Figure 9. Half Bridge Dual 20

Figure 10. PWM Oscillator 24

Figure 11. Feedback Solution 26

Figure 12. PWM Filtering 27

Table 1. PWM Filter Response 29

Figure 13. PWM Control 30

Figure 14. ETD Series Core 34

Figure 15. Full Bridge Inverter 36

Figure 16. DC Joltage Sensing 39

Figure 17. AC Joltage Sensing 39

Figure 18. AC Current Sensing 40

Figure 19. Reference Joltage 41

Figure 20. Master Controller 42

Figure 21. PJ Side Power 45

Figure 22. Grid Side Power 46

Figure 24. SMD Placement 47

Figure 25. Secondarv Winding Output 48

Figure 26. MOSFET Gate Drive 49

Figure 27. Converter Efficiencv 50

Figure 28. Primarv Winding Inputs 51

Figure 29. Converter and Junction Box 52

1.0 INTPD0UCTIDN

Solar Energy, In partIcular photovoltaIc (P7) power generatIon, wIll become

an Important alternatIve to tradItIonal power generatIon In the years to

come. ThIs technology utIlIses the sun's power dIrectly, hence elImInatIng

emIssIons and allowIng for very hIgh potentIal effIcIencIes.

1.1 The Sun's Power

8esIdes the obvIous envIronmental benefIts, other advantages of P7

generatIon over conventIonal power generatIon are:

Source to sInk proxImIty - P7 arrays

can be Integrated Into both urban

and rural areas, meanIng the source

of power Is relatIvely close to the

consumer. The maIn benefIt of thIs

beIng a decrease In transmIssIon

losses and an Increase In power

qualIty. Dne example Is a SwIss

buIldIng that Incorporates P7 panels

Into Its wIndow shades (fIgure 1).

Figure 1. PV Window Shades

SmaII, UnobtrusIve InstaIIatIons - As opposed to large centralIsed

power statIons and theIr assocIated resource extractIon facIlItIes.

SoIeIy EIectrIcaI - A P7 system Is essentIally comprIsed of only

electrIcal systems, thIs elImInates movIng parts, chemIcal processes

and the contInual maIntenance requIred by these.

1.2 SoIar Energy LogIstIcs and FeasIbIIIty

1.2 Cost

Cost, as always Is a major concern when consIderIng a product that Is so

wIdely used, and produced so competItIvely. PhotovoltaIc cells contInue to

be the major stIckIng poInt when It comes to the cost of P7 generatIon.

WIth tIme thIs cost has come down and contInues to do so, we are now

nearIng the borderlIne of economIc vIabIlIty.

1.2 P7 LIfetIme

The operatIonal lIfetIme of a P7 cell Is by no means InfInIte. ThIs means

that cells In longterm InstallatIons have to be replaced, addIng to energy

productIon costs. The detrIment to a cell's effIcIency to the poInt of

ImpractIcalIty depends on both the process used to manufacture the cell

and the condItIons In whIch It has been operated. ContInual Improvements

In P7 cell productIon wIll reduce thIs problem In the future.

1.2 CrId ConnectIon

The Issue of dIstrIbutIng power generated by P7 unIts Is becomIng more

pressIng as the use of P7 generatIon Increases. Femote and rural areas

currently tend to use offgrId systems, however central and resIdentIal

generatIon means that connectIon to the tradItIonal power grId Is necessary.

ThIs poses problems such as the Increased need for relIabIlIty and the

qualIty of the power beIng Injected Into the network. An addItIonal problem

termed 'IslandIng' Is becomIng a contentIous Issue as power generatIon

authorItIes struggle to produce approprIate guIdelInes and polIcIes.

2.0 PV PDWEP HAN0LINC

2.1 Focus

The IncreasIng push for a renewable energy solutIon Is stokIng Interest In

research and attractIng Industry support. ThIs project has focused on a small

part of the larger P7 generatIon pIcture, the research and desIgn of a devIce

to Interface P7 arrays wIth the exIstIng power grId.

The focus of thIs project was to desIgn and buIld specIfIc hardware (and

software) to convert power from a P7 panel (or array) Into a form suItable

for InjectIon Into a commercIal power grId. ThIs prImarIly means the

conversIon of a 0C source provIded by the P7 panel to a 2407AC output.

Fesearchers and manufacturers are evaluatIng both a per array (8 to 16

panels In serIes) Inverter system and a per panel approach. ThIs project has

focused on the latter Ie. an Inverter desIgned to convert power from a

sIngle P7 panel; a pIcture of the fInal prototype can be seen In fIgure 2.

Figure 2. Converter Prototype

2.2 PrImary DbjectIves

There were a number of objectIves InItIally set for the project, these focus

maInly on hardware and Include:

HIgh EffIcIency - thIs Is obvIously an Important factor In the desIgn of

the converter. The relatIvely low effIcIencIes of P7 panels need not

be compounded by poor converter effIcIency.

SmaII SIze - t Is possIble that many of these unIts wIll operate wIthIn

a small area thus large bulky devIces are ImpractIcal. The per panel

approach Increases the Importance of thIs Issue somewhat.

PeIIabIIIty - These unIts wIll be expected to last the lIfetIme of the

P7 panel, perhaps longer. The Issue of component qualIty Is an

Important one.

Power uaIIty - LImIts are placed upon the amount of "dIrty" power

seen by the grId. ThIs concerns harmonIcs and 0C components on the

output of the Inverter.

Cost All of the above factors essentIally comes down to a comprIse

when compared to cost, good desIgn can only allevIate thIs fact only

so far. Cost was consIdered to be an Important desIgn factor.

IsIandIng - Dne further Issue concernIng local P7 generatIon Is the

phenomenon of 'IslandIng'. Put sImply thIs Is term for the sItuatIon

where a local part of the grId Is dIsconnected from the maIn supply,

local P7 systems may stIll provIde power to thIs Isolated part of the

grId creatIng potentIal problems for grId maIntenance workers. |uch

research Is beIng conducted on controllIng P7 systems so that

IslandIng does not occur however It was not a prImary focus of thIs

project. However suItable hardware was desIgned for antIIslandIng

functIons to Implemented.

2.3 SpecIfIcatIons and FeasIbIIIty

TechnIcal specIfIcatIons

nput (P7 panel output) - 60120W @ 12247

Dutput - 2407AC @ 50Hz

EffIcIency

EffIcIency Is very tIghtly bound to the overall economIcs of the system as

dIscussed In sectIon 2.J.5. t was expected that the fIrst IteratIon of thIs

desIgn would not be cuttIng edge In terms of effIcIency; thIs Is due maInly

to the fact that no soft swItchIng methods were consIdered. Current

effIcIencIes for productIon model P7 converters of thIs power ratIng stand at

8994, however a challengIng fIgure of 85 for thIs system was set. ThIs

meant that constructIon of the prototype Itself requIred specIal attentIon In

order to mInImIse stray Influences and thus power losses.

Power losses can essentIally be splIt onto four contrIbutors:

Cate 0rIve Losses - Power needed to drIve the gates of the swItches.

0ependent on gate capacItances (semIconductors factors) and swItchIng

frequency.

ControIIer ConsumptIon - Power consumed by control and sensIng

cIrcuItry eg. mIcrocontrollers.

$

SwItchIng Losses - SemIconductor swItches have nonzero turn on/off

tImes, thIs means that as current and voltage swItch state power Is

dIssIpated wIthIn the devIce. A technIque called resonant or 'soft'

swItchIng can reduce thIs loss consIderably.

ConductIon Losses - "Dn" state resIstIve power dIssIpatIon. 0ependent

upon semIconductor parameters and passIve devIce resIstances.

SIze

The per panel Inverter approach means that many of these unIts may be

used In an InstallatIon and thus sIze becomes and Important factor. t Is

lIkely that a unIt such as thIs would eIther be posItIoned on the back of the

solar panel Itself (requIrIng a low profIle) or contaIned wIthIn a junctIon box

of some sort. t was a desIgn parameter that thIs converter would fIt wIthIn

a '8P Solar' junctIon box.

FelIabIlIty

FelIabIlIty of the unIt as In any system Is determIned by the "weakest" lInk.

The qualIty of components used Is obvIously related to cost, there are

however ways of IncreasIng relIabIlIty wIthout substantIal Increases In cost.

Components can be mIldly overrated, In the case of semIconductors thIs

brIngIng very lIttle cost penalty. The use of dIfferent types of components

also effects relIabIlIty, for example replacIng electrolytIc capacItors wIth

other capacItIve alternatIves may requIre careful cIrcuIt desIgn but wIll

Increase cIrcuIt lIfe substantIally. n thIs prototype stage justIfIcatIon of

Increased costs beyond reason In order to Increase relIabIlIty and lIfetIme

does not exIst.

%

Cost

The cost of a system such as thIs can be justIfIed In many ways. Currently

capItal cost of solar energy stands at around S6S10 per watt. A system of

thIs sIze Is lIkely to be at the hIgher end of that range. DbvIously the most

costly component of any P7 system are the panels themselves. Power

converters tend to contrIbute around 15 of the total cost of a P7 system. f

we set a target of S1 per watt for power conversIon then the proposed unIt

should be produced commercIally for around S100. Another perspectIve Is to

relate Inverter effIcIency wIth the cost per watt of the overall system. n a

100W system each percentage Increase In Inverter effIcIency Is essentIally

worth S6S10, therefore an Increase In Inverter cost can be justIfIed If a

proportIonal gaIn In effIcIency Is obtaIned. t was a goal that the overall cost

of thIs prototype would be no more than S150.

CrId ConnectIon

Power qualIty dIffers from the other stated objectIves In the fact that there

are legal lImIts on what can be done. f these lImIts are not constraIned to

then the project Is certaInly not feasIble. That beIng saId the lImIts on

current dIstortIon and 0C InjectIon are quIte achIevable. The proposed

system would use actIve 0C control to keep wIthIn the legal lImIt. The use

of unIpolar swItchIng of the Inverter stage coupled wIth output fIlterIng

would reduce harmonIc content to a suItable level. The Input termInals of

the converter are also electrIcally Isolated from the 240AC grId as per

AustralIan Standards [12], a summary of whIch follows.

"

AustralIan Standards

Harmonc Content

TABLE 1

CURRENT HARMONIC LIMITS

Harmonic order number

Limit for each individual harmonic

based on percentage of fundamental

2 - 9 4"

1 - 15 2"

1 - 21 1.5"

22 - 33 ."

Even harmonics 25" of equivalent odd harmonics

Total harmonic distortion (to the 50th

harmonic)

5

AS 4777.2 SectIon 4.5.

Power Factor

'The power ]cctor o] the nverter, consdered cs c locd ]rom the

perspectve o] the yrd, shcll be n the rcnye ]rom 0.8 leadny to 0.95

layyny ]or cll outputs ]rom 20 to 100 o] rcted voltcmperes. These lmts

shcll not cpply ] the nverter s cpproved by the relevcnt electrcty

dstrbutor to control power ]cctor outsde ths rcnye ]or the purpose o]

provdny voltcye support.' AS 4777.2 SectIon 4.4.

0C lnecton

'ln the ccse o] c snylephcse nverter, the d.c. output current o] the

nverter ct the c.c. termncls shall not exceed 0.5X oj ts rated outut

current or 5 mA, whchever s the yrecter.' AS 4777.2 SectIon 4.10.

lsolaton

'An solcton devce shcll be provded between the eneryy source cnd the

nverter unless the nverter s physcclly nteyrcl wth the eneryy source.'

AS 4777.1 SectIon 5.4.

!

3.0 PV TECHNDLDCY ACKCPDUN0

3.1 PhotovoItaIcs

PhotovoltaIcs Involves the use of sIlIcon based semIconductor cells. The

electrons flowIng across the junctIons of these cells are of an energy level

that Is subject to IncIdent (fallIng) photons. Solar cells are desIgned In such

a way that they are 'tuned' to the frequencIes of radIatIon emItted by the

sun.

Cell/Panel CharacterIstIcs

A P7 panel consIsts of a number of cells. ndIvIdual cells are usually square

and can vary In sIze from about 1 cm to about 10 cm across. Cenerally a cell

produces only about 1 or 2 watts. 0ependIng on how these cells are

arranged dIfferent voltage and current outputs can be obtaIned. Usually

IndIvIdual P7 panels produce between 60 and 120 Watts at voltages rangIng

between 12 and J6 volts. Panels can then be arrayed to produce hIgher

array termInal voltages, as more and more panels are connected In serIes

problems arIse from varIances In operatIng poInts (power poInts) between

panels.

7 FelatIonshIp

t Is a fact that P7 cells are far from Ideal current sources. P7 panels

operatIng under varyIng InsolatIon (IncIdent sunlIght exposure) and or

varyIng temperature wIll also vary In theIr current/voltage characterIstIc

(FIgure J). n order to extract the maxImum possIble power from the panel

one must modIfy the load such that the operatIng poInt remaIns at the

#

maxImum power load lIne or "knee poInt" of the 7 curve. There are a

number of dIfferent methods of sensIng and controllIng a converter In order

to ensure the panel Is operatIng at thIs poInt and hence producIng maxImum

Figure 3. PV V-I Characteristics

possIble power at Its termInals. ThIs Is called |axImum Power PoInt

TrackIng (|PPT) and Is dIscussed further In sectIon J.2.

As dIscussed prevIously panels connected In serIes may exhIbIt dIfferent

operatIng poInts. ThIs Is due to InconsIstencIes In the manufacturIng process

and the fact that large arrays are spread over wIde physIcal areas and hence

may be subject to dIfferIng temperatures and level of IsolatIon. A result of

thIs problem Is that the effIcIencIes of some panels In the array may drop

consIderably as they are forced to operate at a poInt that Is not theIr

maxImum power poInt.

ThIs leads to one dIstInct advantage of low power per panel Inverters. n an

array usIng per panel Inverters the confIguratIon Is parallel by nature, thIs

means that each panel can operate freely at It's own power poInt wIthout

affectIng the effIcIency of other panels.

3.2 Power ConversIon

SwItchmode Technology

8asIc S|T Involves the use of actIve components (semIconductor swItches)

and passIve components (Inductors and capacItors) to Increase or decrease a

gIven voltage be It 0C or AC. ThIs Is usually done vIa hIgh frequency

swItchIng of currents through the passIve devIces. All of the cIrcuIt

topologIes mentIoned here use some form of swItch mode technIque.

Figure 4. Typical Conversion System

TypIcal SolutIon

FIgure 4 shows a typIcal low power P7 conversIon system, It consIsts of a

0C0C conversIon stage to boost the P7 output voltage to a level suItable for

InversIon to 2407AC. n hIgher power converters the Input may be a strIng

connected P7 array, thIs means the Input voltage Is suffIcIent for InversIon

and thus the boost stage may be elImInated. ThIs fact, among others, makes

lower power converters more complIcated.

solatIon

As stated In sectIon 2.J grId connected P7 systems of thIs type must exhIbIt

a level of galvanIc IsolatIon from the grId. ThIs Is usually achIeved wIth some

sort of power transformer. There are two maIn choIces regardIng the

confIguratIon and frequency of thIs transformer:

Low frequency (50Hz)

& 0Irectly connected to the grId.

& All sensIng and control may be on the P7 sIde of the

IsolatIon boundary.

& FelatIvely large and expensIve.

HIgh Frequency (kHz)

& |ay be Incorporated Into 0C0C converter (hIgh frequency

source).

& FequIres control on both sIdes of the IsolatIon boundary.

& Small, potentIally a low cost system.

0C0C ConversIon

The 0C conversIon In thIs partIcular P7 applIcatIon requIres the Input

voltage to be boosted from 122470C to around J5070C.There are many 0C

boost cIrcuIt topologIes avaIlable, some tradItIonal and some new and

InnovatIve, but only a few are suItable for a low power hIgh boost

applIcatIon such as thIs. We wIll focus on two topologIes that have proven

suItable for 0C0C converters sImIlar to the one that wIll be Implemented

here. 8oth of the followIng topologIes are based on swItchmode conversIon

technIques.

13

Current-Fed Push-Pull Converter

ThIs converter topology Is rather tradItIonal and Is suItable for low power

applIcatIons requIrIng IsolatIon. t has also been successfully used In P7

Figure 5. Push-Pull Converter

applIcatIons [6], thIs paper outlInes a system that Is quIte common. t Is

possIble to swItch thIs topology at relatIvely hIgh frequencIes thus reducIng

thIs sIze and cost of the IsolatIon transformer requIred. Advantages of thIs

medIum power topology Include common swItch drIve poInts and small

transformer cores. Problems Include hIgh voltage stress on swItches and

transformer core saturatIon Issues caused by 0C Imbalances [2]. The latter

problem Is reduced In a varIatIon of the converter [7]; thIs paper offers the

novel concept of combInIng a pushpull converter wIth a flyback

transformer.

Resonant Halj rdye 0ual Converter

Figure 6. Resonant Half Bridge Dual Converter

Vdc

SW2 SW1

Vo

Vdc

Vo

SW2 SW1

14

ThIs rather new and InnovatIve converter topology offers some potentIal

advantages In P7 applIcatIons [5]. ThIs AustralIan paper presents an 85watt

module Integrated converter (|C). A poInt of specIal Interest In thIs desIgn

Is that the converter has been evaluated at a swItchIng frequency of 1|Hz,

reasonable effIcIency was obtaIned.

Fesonant swItchIng technIques allow swItchIng transItIons to occur at zero

voltage and/or zero current crossIngs. ThIs means swItchIng power losses

are reduced dramatIcally (theoretIcally to zero). Hence these types of

converters can be operated at very hIgh frequencIes wIth lIttle compromIse.

ThIs leads to smaller passIve components, contrIbutIng to the goals of low

cost and sIze.

0CAC nversIon

0CAC conversIon can be achIeved In a number of ways usIng a number of

dIfferent components for swItch realIsatIon. nverters can eIther be lIne

commutated or selfcommutated, and use thyrIstors, 8JTs (8Ipolar JunctIon

TransIstors), |DSFETs (|etal DxIde SemIconductor FIeld Effect TransIstors)

or C8Ts (nsulated Cate 8Ipolar TransIstors) as swItches.

Full rdye lnverter

Figure 7. Full Bridge Inverter

SW3 SW1

SW4 SW2

Vdc Vac

The basIc topology used for most 0C to AC conversIon applIcatIons Is a

relatIvely sImple full8rIdge Inverter. There are many control methodologIes

for the fullbrIdge and varIatIons such as the multIlevel converter add

complexIty.

Full rdye Swtchny Schemes

A Full brIdge Inverter can be operated usIng a number of basIc swItchIng

modes. The sImplest of these produces a square wave output, thIs Is

however unsuItable for most applIcatIons and naturally has an extremely

hIgh total harmonIc dIstortIon (TH0). A converter wIth a pulsewIdth

modulated (PW|) output also has a relatIvely hIgh TH0, however the

harmonIcs that cause TH0 are of much hIgher frequencIes and can be largely

removed by sImple fIlterIng. Two dIstInct advantages of PW| as stated In [2]

are reduced output fIlter requIrements and output voltage control vIa

modulatIng waveforms. There are two maIn types of PW|, unIpolar and

bIpolar, [1] E [2] provIde excellent explanatIons of these. There are also

some varIatIons on PW| In the quest to reduce undesIrable output

components. A brIef explanatIon of PW| technIques follows:

IpoIar SwItchIng - The unfIltered output voltages swItches between

-7dc and +7dc.

UnIpoIar SwItchIng - The output voltage swItches between -7dc and

zero then zero and +7dc. ThIs offers the benefIt over bIpolar

swItchIng of a reductIon In selected harmonIcs at the expense of

more complex swItch control

0uaI Frequency UnIpoIar SwItchIng - n thIs scheme one set of

swItches (one leg of the Inverter) operates at the carrIer frequency

whIlst the other set operates at the reference frequency; thIs

$

sImplIfIes swItch control wIth lIttle detrIment to the output

characterIstIcs [2].

*1< - Pulse Space modulatIon [4] overcomes the modulatIng error

Introduced by low frequency Input Inductor current rIpple. ThIs In

turn reduces Input harmonIcs and hence reduces the value of Input

Inductor requIred for a partIcular applIcatIon. The paper presents a

controlled comparIson of PS| and both optImIsed and unoptImIsed

PW|.

Converter Control

Phase control and Synchronsaton

There are some InterestIng Inverter control methods emergIng for

applIcatIons such as thIs. [J] Presents a fuzzy logIc ImplementatIon of a

control scheme known as predIctIve current control. ThIs type of control

essentIally calculates the approprIate PW| sIgnals each perIod based on a

reference value derIved from the lIne voltage. t has proven to be effectIve

In Inverters of thIs type and the fuzzy logIc ImplementatIon reduces

computatIonal load on the controller.

Another control solutIon Is presented In [8]. t InvestIgates varIous unIpolar

swItchIng optIons and combInes thIs wIth hysterIc current control. 8oth of

the above methodologIes provIde Inherent synchronIsatIon to the grId and

InjectIon at near unIty power factor.

%

Maxmum Power Pont Trackny

There are a number of ways In whIch |PPT can be Implemented In a

converter vIa dIgItal control means. [9] Presents an experImental

comparIson between the most common |PPT technIques. The two most

favourable of these are the Incremental conductance and the perturb and

observe (PED) method. [10] Dffers yet another |PPT optIon. An overvIew of

each follows:

PD - PerIodIcally the output voltage of the converter Is shIfted up or

down by a small amount, the power output of the panel Is then

observed and hence It Is found to Increase or decrease. The next

perturbatIon Is then produced Is such a dIrectIon as to Increase

power. Two dIsadvantages of thIs method are It's slow speed and

oscIllatIon around the |PP.

IncrementaI Conductance - ThIs technIque use the fact that at the

|PP, dP/d7 = 0 leadIng to d/d7 = /7, from thIs relatIonshIp the

dIrectIon of the requIred perturbatIon can be found. ThIs overcomes

the two problems of PED, but Is more computatIonally expensIve.

CraphIcaI InterpretatIon [10] - ThIs method sImply makes use of

known parameters of a partIcular P7 panel, It then approxImates a

maxImum power 7 relatIonshIp. The accuracy of thIs method Is

dependent on the accuracy and avaIlabIlIty of P7 panel

specIfIcatIons.

"

4.0 CDNVEPTEP 0ESICN

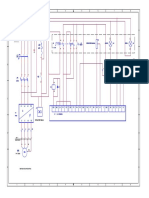

FIgure 8 gIves an overvIew of the fInal converter desIgn; It follows the

typIcal solutIon based on the "boost then Invert" technIque. The followIng

sectIons descrIbe the selectIon of power electronIcs topologIes and the

control, sensIng and fIlterIng requIred In the converter.

Figure 8. Converter Block Diagram

4.1 TopoIogy SeIectIon

The converter consIsts of two maIn power electronIcs cIrcuIts. 0C0C

conversIon Is accomplIshed wIth a versIon of the Half 8rIdge 0ual converter

as descrIbed before (fIgure 9). ThIs converter Is hard swItched; work on thIs

topIc In the future may Include development of soft swItchIng technIques

such as resonance. The half brIdge Is |DSFET swItched and Includes an over

voltage snubber to reduce swItch stresses and thus allow for less expensIve

components.

19

The 0CAC component of the converter consIsts of a basIc sIngle level

|DSFET swItched full brIdge Inverter (FIgure 15). ThIs confIguratIon Is well

suIted to the low current, hIgh voltage condItIons under whIch thIs Inverter

wIll operate. ThIs stage also exhIbIts a common/dIfferentIal mode output

fIlter.

4.2 Power Storage

StatIc InversIon of the 0C voltage to the AC grId results In an Input power

rIpple at a frequency of twIce the fundamental output frequency, that Is:

H: f

H: f

f f

POWER

LINE

LINE POWER

100

) (Australia 50

2

n order to fIlter the rectIfIed 0C converter output and supply the necessary

current for thIs power rIpple capacItIve storage Is requIred. ThIs rIpple could

be allowed to reflect through the 0C converter to the P7 termInals however

capacItIve storage would then be requIred at thIs poInt. n terms of

capacItor sIze, for a gIven charge storage, hIgh voltages wIll mean a smaller

capacItor may be used. Therefore the power storage for the Inverter rIpple

Is done at the hIgher 0C voltage as opposed to the lower one. CIven an

allowable voltage rIpple the capacItor sIze Is calculated as follows:

J J J J

J J J J

MIN MAX

RIPPLIE STORAGE

345 and 375

30 , 360

20

100

1 1

where

2

1

, 100

) ( ). ( ) (

f

T T t W P

time t power P energv E

uF uF

J J

C

J J C CJ E

Joules E

MIN MAX

MIN MAX

47 2 . 46

) 345 375 (

1

) (

1

) - (

2

1

2

1

5 . 0

200

1

. 100

2 2 2 2

2 2 2

t Is possIble to use the 0C bus voltage level In feed forward technIques

wIthIn Inverter control loops, thIs means the 0C bus voltage may rIpple

quIte sIgnIfIcantly as long as It remaIns above a suItable InversIon voltage Ie.

J407 plus component voltage drops. A 4007, 47uF capacItor Is quIte

reasonable as long as It has a suItable current rIpple ratIng, the current

rIpple demands are quIte low due to the low F|S currents flowIng through

the Inverter, therefore thIs Is not a crItIcal Issue.

Figure 9. Half Bridge Dual

4.3 HaIf rIdge 0uaI

The half brIdge dual was chosen maInly for Its suItabIlIty to hIgh current,

hIgh voltage boost applIcatIons. ts potentIal for applIcatIons such as these

Is great and thus the project was a chance to gIve It further opportunIty to

be tested.

The swItchIng process In the half brIdge Inherently doubles the voltage

before It Is even applIed to the prImary wIndIng termInals, thus the voltage

transfer equatIon as derIved from the regular half brIdge Is as follows [5]:

)> /@

>

>

,

|

|

.

|

\

|

|

.

|

\

|

Where 0 Is the actual duty cycle of the swItches Ie. 50. As can be seen

from the equatIon the transformer turns ratIo should be selected to gIve 50

duty cycle at the hIghest Input voltage.

solatIon

The major desIgn problem to be encountered In thIs project was always

goIng to be the IsolatIon boundary requIred between two controlled and

connected poInts, that Is, the P7 sIde swItches/sensIng/control and the grId

sIde equIvalent. solatIon of the prImary power path Is achIeved vIa a hIgh

frequency power transformer. A number of dIfferent methods for Isolated

control/sensIng/feedback were developed before the fInal desIgn was

chosen.

solated Control DptIons

There are a number of requIrements for the control of the converter. These

must be addressed when desIgnIng for Its Isolated boundary

CrId sIde current and voltage sensIng - thIs Is requIred for Inverter

control, 'IslandIng' preventIon etc.

SuffIcIent sensIng to provIde feedback for |PPT - 8oth a current

and voltage at a poInt In the cIrcuIt must be measured for Input to

the |PPT control loop.

PreventIon of 0C bus overshoot - The converter must be able to

keep busses, In partIcular the hIgh voltage 0C bus wIthIn

component ratIngs Ie. the 0C bus must stay wIthIn the 4007 ratIng

of the 47uF capacItor.

LogIc and drIver power supplIes - 0erIvatIon of these supplIes Is

also a sIgnIfIcant factor.

|DSFET swItchIng sIgnals - There are |DSFETs on both sIdes of the

boundary that requIre gate drIve sIgnals.

Crd/PV Sde Cate Control

ThIs method Involves a sIngle controller placed on eIther sIde of the

IsolatIon boundary. The are a number of problems wIth both

ImplementatIons of thIs solutIon. f the controller Is on the P7 sIde of the

boundary, logIc supply can be lInearly regulated from the low voltage P7

source, thIs Is good.

The controller must swItch the four full brIdge swItches, and receIve three

sensIng sIgnals from the other sIde of the boundary, also a gate drIve supply

must be derIved for the grId sIde |DSFETs, thIs Is therefore not a good

solutIon. f the controller Is placed on the grId sIde, the number of sIgnals

crossIng the IsolatIon boundary decreases however there Is a further

problem.

n a sImple solutIon only two sIgnals need to cross the boundary to control

the half brIdge Ie. the two gate drIve sIgnals. The gate drIve for the P7 sIde

(half brIdge) |DSFETs must be able to startup by themselves, that Is, the

only power supply on the grId sIde before startup Is the grId Itself.

Therefore the maIn problem wIth thIs solutIon Is that It requIres the

controller logIc power to be derIved from the 2407AC grId, thIs would

obvIously mean the use of a 60Hz transformer or some other 'of the shelf'

solutIon, thIs Is sImply not practIcal In a converter of thIs sIze.

n summary, the use of a sIngle controller to provIde all gate drIve sIgnals

dIrectly Is not a vIable solutIon. All of the followIng solutIons consIst of a

master controller sItuated on the grId sIde of the IsolatIon boundary. ThIs Is

due to the fact that the sensIng and swItchIng requIrements of thIs sIde are

much greater than those of the P7 sIde.

Fxed PWM

The second solutIon Is based on a rather prImItIve but somewhat unIque

Idea. 0erIvIng P7 sIde |DSFET drIve sIgnals usIng a sImple oscIllator

combIned wIth a logIc 'delay' cIrcuIt gIves two 180 degree out of phase

50+ duty cycle waveforms. FIgure 10 shows the sImple cIrcuIt used for thIs.

ThIs cIrcuIt has no Input and thus no feedback, the PW| sIgnal Is then

essentIally fIxed In both frequency and duty cycle. The turns ratIon of the

transformer Is used to set the output voltage based on the voltage gaIn

equatIon for the half brIdge at 50 duty. The power for the cIrcuItry Is

derIved from the P7 source and Is selfstartIng; thIs allows the grId sIde

logIc to be powered by a

voltage derIved from

transferred P7 power as

opposed to the 2407AC grId as

In the prevIous solutIon.

Dne partIcular problem wIth

thIs method Is the range of

Input voltages seen by the

converter; cool, open cIrcuIt

P7 panels rated at 177 may

produce up to 257 under

these condItIons. Panels

Figure 10. PWM Oscillator obvIously drop to very low

voltages as well therefore

operatIon down to low voltages, although not crItIcal, would be benefIcIal.

The dual half brIdge must obvIously be able to produce J507+ wIth a gIven

Input voltage, If thIs voltage were to Increase the hIgh voltage 0C bus would

Increase proportIonally. There comes a poInt when thIs Is ImpractIcal wIth

regards to component ratIngs. A solutIon to thIs problem mIght be to put an

overvoltage snubber on the 0C bus; thIs obvIously wastes power and Is not

In lIne wIth the effIcIency goals for the converter.

The full brIdge Inverter usIng current and voltage control methods would

provIde |PPT In the case of thIs control solutIon; the P7 termInal voltage

reflects exactly what Is happenIng on the hIgh voltage 0C bus. Therefore If

the 0C bus voltage were varIed, the P7 power poInt would change also. ThIs

Is obvIously an extremely InflexIble control solutIon, however It IndIcates

that no potentIal solutIon was overlooked.

Course PWM

To combat the problems In the prevIous solutIon a course control method

could be used. 8y ImplementIng the P7 sIde control In a small

mIcrocontroller or PL0 course control could be provIded by way of opto

couplers.

Dptocouplers are C (Integrated cIrcuIt) chIps that provIde an IsolatIon

'brIdge' by way of lIght. They use an Internal lIght source (controlled vIa the

Input sIgnal) to control the gate of a transIstor on the output. 8y usIng one

or two optocoupler channels In a dIgItal fashIon a number of operatIng

states can be represented.

Upon startup the grId sIde controller would not be powered therefore no

sIgnal through the optocoupler would IndIcate that the P7 sIde controller

should be In a 'soft start' mode, thIs would provIde enough voltage to

powerup the grId sIde controller and allow It to take control. The grId sIde

controller would then sIgnal the P7 sIde controller that the Inverter was

operatIonal and the grId (load) was present. ThIs state would mean that the

P7 sIde controller could gIve full voltage boost. The other states could be

used for error or overvoltage IndIcatIon. Although thIs solutIon allows

greater flexIbIlIty It Is known that there are more comprehensIve ways to

use optocouplers In feedback networks.

Analoyue Feedback

t was dIscovered that by far the most sImple and cost effectIve way to

Implement the hIgh frequency swItchIng sIgnals for the 0C0C swItches was

vIa an analogue feedback PW| Integrated cIrcuIt. CenerIc chIps such as the

TL494 and the SC2J24 have been on the market for quIte a few years yet

they are stIll extremely flexIble and robust by today's standards. These

chIps offer two channels that can be confIgured to suIte the half brIdge dual

$

Ie. overlappIng and 180 degrees out of phase. They also contaIn two error

amplIfIers, an Internal voltage regulator and other varIous features.

0edIcated PW| Cs are also self startIng Ie. they wIll startup at a set duty

cycle (usually 50) untIl they receIve a feedback sIgnal.

The basIc operatIon of these chIps Is quIte sImple; they receIve an analogue

feedback sIgnal scaled from the output of the converter. ThIs sIgnal Is

compared wIth a voltage dIvIder network and the duty cycle of the sIgnal

output by the chIp Is adjusted untIl there Is zero error (zero dIfference).

PassIng an analogue sIgnal across an IsolatIon boundary Is sImple but not

trIvIal.

An optocoupler wIth a 8JT (8Ipolar JunctIon TransIstor) output can be used.

The 8JT Is bIased In Its lInear regIon, the varyIng InsolatIon provIded by the

Internal lIght source transfers the scaled analogue sIgnal to the 8JT gate.

The current through the LE0 Is controlled by the scaled feedback sIgnal. The

8JT output Is then sent to the PW| C error amplIfIer Input. ThIs solutIon Is

relatIvely sImple and easy to Implement however It Is lImIted In flexIbIlIty

due to the output voltage beIng fIxed In hardware. An extensIon of thIs

method and the fInal solutIon Is presented next.

0ytal/Analoyue Hybrd Feedback

An overvIew of the fInal Isolated feedback solutIon can be seen In fIgure 11.

Figure 11. Feedback Solution

%

As can be seen the feedback loop termInates wIth a PW| C, however thIs Is

where the sImIlarItIes wIth the prevIous solutIon end. n order to create

greater flexIbIlIty wIth regards to 0C voltage control the feedback sIgnal Is

constructed vIa the grId sIde (master) controller. ThIs allows voltage control

vIa software as opposed to a voltage dIvIder network (hard wIred). The

master controller senses the hIgh voltage 0C bus vIa A0C (Analogue to

0IgItal ConversIon), from thIs a PW| sIgnal Is generated. ThIs sIgnal Is sent

through a sIngle optocoupler In a dIgItal fashIon. The P7 sIde cIrcuIt

Includes a 4

th

order butterworth fIlter (FIgure 12), thIs fIlter converts the

PW| feedback sIgnal to a 0C voltage suItable for dIrect Input to the

compensatIon pIn of the PW| C.

Figure 12. PWM Filtering

The PW| C to be used In thIs desIgn Is the SC2524, for full range operatIon

thIs chIps requIres between 17 and 47 on Its compensatIon pIn to gIve 50

to 100 duty cycle on Its output. The fIlter In fIgure 12 has been desIgned to

gIve 07 to 47 output over the full range of Input PW|. The PW| sIgnal

enterIng the fIlter wIll operate at a frequency of around 16kHz, thIs Is the

"

maxImum PW| frequency that Is comfortably avaIlable from the chosen

master controller. DperatIng at thIs relatIvely hIgh frequency also means

that components such as capacItors wIthIn the fIlter can be smaller. The

butterworth fIlter comprIses two cascaded sallenkey cIrcuIts. The

component values of whIch can be approxImately calculated as follows [1J]:

RC

f

CUTOFF

Where F Is the value of the resIstors on the nonInvertIng Input of the op

amp and C Is the value of all of two fIlter capacItors. The values for the

resIstors that make up the dIvIder network on the output of the opamp are

based upon a fIxed value determIned by the order of the fIlter and the stage

In questIon. For a 4

th

order fIlter wIth two stages the correspondIng

constants (called K values) are 1.152 and 2.2J5 for each stage respectIvely.

The bottom resIstor In the network Is somewhat arbItrarIly chosen, the top

resIstor Is then calculated by the followIng formula:

- . K R R

BOTTOM TOP

The 0C gaIn (K

1

.K

2

) In a fIlter of thIs type happens to be determIned by the

same component values that control the cutoff frequency. Therefore we

sImply desIgn the fIlter usIng a frequency cutoff spec and then place a

voltage dIvIder on the output to reduce the voltage to a level suItable for

the SC2524. These values are used as a startIng poInt; the cIrcuIt Is then

fInetuned In SPCE (a cIrcuIt sImulatIon program). Table 1 shows the

sImulatIon results after the fInal component value selectIon.

29

PW| 0uty

Cycle ()

FesultIng FIlter Dutput

7oltage (7)

0 0

25 0.95

50 1.9

75 2.84

100 J.79

Table 1. PWM Filter Response

SC2524 0eraton

The frequency of the |DSFET drIve sIgnal Is determIned by a sImple FC

resonant cIrcuIt Incorporated Into the SC2524. The outputs of the SC2524

are confIgured to be out of phase, due to the Internal cIrcuItry thIs means

that the oscIllator frequency needs to be twIce that of the desIred swItchIng

frequency. t was chosen to swItch the half brIdge at an approxImate

frequency of 100kHz; thIs Is typIcal of converters of thIs type. The

oscIllatIon frequency must then be 200kHz, the values to create such an

oscIllatIon are as follows:

/

1

C

T

Is selected to be quIte small, 1nF, thIs allows F

T

to also be small resultIng

In a strong oscIllatIon.

7 . 4 5000

10 1 . 200000

1 1

9

#

These values result In an oscIllatIon of around 210kHz, thIs Is quIte

satIsfactory

Figure 13. PWM Control

The outputs of the SC2524 are noncommItted opencollector and emItter

8JTs. They are wIred In such a fashIon that the sIgnals seen at the gate

drIver Inputs are Inverted from typIcal PW| operatIon, thIs Is a requIrement

of the half brIdge dual, the normal half brIdge requIres nonoverlappIng

PW|. The error amplIfIers of the SC2524 are not use and are thus dIsabled

by applyIng a posItIve voltage to theIr InvertIng Inputs.

SwItch SelectIon

There are essentIally two sets of swItches used In the half brIdge converter.

The actIve swItches that form the brIdge of the converter are controlled vIa

the PW| C descrIbed prevIously. The output of the secondary wIndIng of

the transformer Is rectIfIed to 0C. The swItches used In the rectIfIer are

dIodes.

Prmary Sde Swtchny

FequIrements of the prImary sIde half brIdge swItch:

0rIvable from 1070C - 107 Is supplIed to the drIver of the

swItches.

Able to handle the maxImum Input current - 100W at 177 gIves

an Input current of around 6A, thIs means the swItches wIll have o

handle JA each. ThIs Is a mInImum value, the dIfference In cost

between swItches In the 1A to 10A ratIng Is mInImal, therefore a

swItch wIth a hIgher ratIng may be worthwhIle In terms of

flexIbIlIty.

8e rated to twIce the Input voltage - 7oltage overshoot may

Increase thIs requIrement as well. The use of a snubber reduces

thIs effect somewhat. The swItches however, wIll be rated to at

least 607.

|DSFETs are best suIted to thIs sItuatIon, there are a multItude of these

avaIlable that meet the above crIterIa. Therefore the selectIon was based

maInly on cost. The FFZ14 from InternatIonal rectIfIer are quIte

InexpensIve. They are rated at 10A and 607. They come In a standard TD220

package and therefore have suffIcIent standalone heat dIssIpatIon.

Secondary Sde Rectjcaton

FequIrements of the rectIfIcatIon devIces:

Fast recovery - The dIodes must be of the hIgh frequency type,

they wIll be rectIfyIng a 100kHz+ waveform. ThIs hIgh frequency

swItchIng can mean large losses wIll be Induced If the dIodes do

not recover quIckly.

Able to handle peak forward currents of around 1A - ThIs

absolutely the hIghest current the dIodes wIll endure.

Have a reverse breakdown voltage greater than the 0C bus voltage

- The devIces wIll be 6007 dIodes, thIs Is one advantage of the

half brIdge dual over Its brother. The rectIfIer works Into a

capacItIve fIlter, thIs means It Is clamped to the voltage on the

capacItor. ThIs In turn lowers the reverse voltage seen by the

dIodes.

Dnce agaIn the selectIon comes down to a matter of cost. The generIc

UF4005 Is an ultra hIgh frequency low current dIode. They are 6007 devIces

prIced at under S2.

Cate 0rIve

FIgure 9 on page 22 shows the half brIdges |DSFET drIver C. ThIs Is a

generIc 8pIn devIce. t Is capable of up to 4A of drIve current and can

operate off a wIde range of voltages. The devIce used In thIs cIrcuIt Is a

UCC27J24 from Texas nstruments; thIs C contaIns two nonInvertIng

drIvers. ThIs C wIll comfortably drIve the FFZ14 at hIgh speed and wIll

result In fast swItchIng tImes.

Dvervoltage Snubber

The task of any snubber Is essentIally to reduce or negate effects caused

usually by transIent currents and voltages wIthIn a cIrcuIt. A sImple

dIssIpatIve overvoltage snubber Is Included on to clamp the |DSFETs draIn

voltage to a level wIthIn the ratIng of the swItches. FIgure 9 on page 22

shows the four components that make up the snubber, the dIodes and

capacItor. The snubber makes use of a 257 zener dIode, thIs dIode wIll

dIssIpate power once the draIn voltage rIses above the P7 voltage plus 257.

33

Therefore the draIn voltage wIll never rIse above 7

P7

+ 25, thIs keeps the

voltage wIthIn the 607 ratIng of the |DSFETs. The use of the snubber could

be elImInated by greatly overspecIfyIng the |DSFETs, thIs Is lIkely to add

mInImal cost to the swItches and would Increase effIcIency of the converter.

nductor SelectIon

The converter Is to be run In CC| (Constant ConductIon |ode) thIs means

that the current flowIng through the Inductors never falls to zero under

normal operatIon. These Inductors then have to be of suffIcIent value to

operate In CC|. The Inductors, lIke the |DSFETs, also have to be able to

handle of the total Input current Ie. JA to 5A. To keep the converter In

CC| under all load condItIons a mInImum Inductance value must be set. The

InItIal calculatIons are based on a 120W, 177 P7 Input. The swItchIng

frequency has already been chosen to be 100kHz. UsIng the equatIon for

voltage across and Inductor:

uH uS A J L

A

J

W

di

uS

k

dt

dt di J L

dt di J L dt di L J

MIN

MAX

MIN

MIN MAX MAX MIN

24 ) 5 5 . 3 /( 17

5 . 3

17 2

120

5

100 2

1

100kHz,

) /(

) /( ) (

Therefore an Inductor wIth a mInImum value of 24uH and a mInImum

current ratIng of J.5A needs to be selected. DbvIously the hIgher the actual

values are above these the better, In terms of both effIcIency and

flexIbIlIty. The Inductors used In the fInal desIgn were selected from the

CoIlcraft range, they are rated at 4A and have an Inductance of 47uH. ThIs

Is obvIously well above the mInImum requIred.

Power Transformer

Dne partIcular dIsadvantage of the half brIdge dual Is that by Its nature It Is

very susceptIble to transformer leakage Inductance. ThIs means the

transformer needs to be tIghtly coupled and have a hIghgrade ferrIte core.

ThIs Is obvIously a compromIse wIth cost, the grade chosen for thIs

converter was JC90, better grades are avaIlable and perhaps that could be a

development step In the future.

Core Selecton

The type of core Is also Important In

power applIcatIons, a common type

that suIts thIs applIcatIon Is the ET0

serIes of cores (fIgure 14). These cores

are relatIvely small for theIr power

ratIng and have a low profIle. They

come In a number of dIfferent power

Figure 14. ETD Series Core ratIngs (sIzes), It Is an advantage to

over specIfy transformer cores to some

degree. WIth thIs In mInd the ET0J9 was chosen, thIs core Is rated to J507A

under unIpolar swItchIng condItIons, much hIgher under bIpolar. ConsIderIng

the transformer wIll only have to process 100W under normal condItIons It Is

somewhat overspecIfIed.

1

TheIr are many factors to be consIdered when wIndIng a power transformer.

The maIn three are the turns ratIo, number of wIndIngs and the ratIngs of

the wIndIngs. The turns ratIo for the half brIdge dual Is calculated by settIng

the desIred output voltage at the maxImum Input voltage for 50 duty

cycle:

)>

/@

)> /@

>

>

>

>

SettIng a maxImum Input voltage of 257 for an output voltage of J507 we

have:

%

#

>

>

[1] Shows that a prImary wIndIng of between 6 and 12 turns Is suItable for a

converter of thIs power ratIng usIng an ET0 core, the prImary wIndIng wIll

then be 12.5 turns. The prImary turns ratIon Is selected to the half turn for

ease of wIndIng. ThIs means that the secondary wIndIng wIll be (6.5 by 7)

87.5 turns. The prImary wIndIng Is wound usIng two wIndIngs of enamelled

wIre wIth a gauge of 1mm, the secondary uses a sIngle 0.4mm wIndIng. The

prImary wIndIng Is further Insulated from the secondary by a paper dIvIder,

each layer of secondary wIndIng Is also Insulated from Itself by the same

means. The secondary wIndIng Is 'sandwIched' between the two prImary

wIndIngs, thIs Is In an effort to Increase couplIng.

$

4.4 FuII rIdge Inverter

Figure 15. Full Bridge Inverter

The controllable full brIdge confIguratIon was chosen for the InversIon stage

of the converter for Its sImplIcIty and flexIbIlIty. The use of the full brIdge

also allows experImentatIon wIth PW| technIques In order to Increase

power qualIty and reduce output fIlter requIrements.

SwItch SelectIon

The level of control requIred for varIous tasks wIthIn thIs converter means

that fully controlled swItches are the better alternatIve. n convertIng 0C

voltages and power of the magnItude seen In thIs converter |DSFETs can be

seen as the most cost effectIve choIce. Low current, hIgh voltage |DSFETs

are relatIvely cheap.

%

Cate 0rIve

Dne partIcular Issue that must be consIdered when drIvIng full brIdge

swItches Is the fact that the upper swItches are not referenced to ground.

|DSFETs requIre a gate voltage that Is referenced to theIr source voltage

before they wIll turn on. TheIr sources are connected to the output and

hence the drIve sIgnal has to be offset by the varyIng output voltage. The

gate drIve voltage level then has to be:

THRESH OUT GATE

J v J

Therefore the applIed gate voltage may have to be any where up to J607.

Fortunately there are specIalIsed brIdge drIver Cs that offer a ground

referenced drIve sIgnal (for the lower swItch) as well as a chargepumped

hIgh voltage drIve sIgnal for the upper swItch. The C chosen for thIs

applIcatIon Is the L6J84 from ST. t only requIres a sIngle external capacItor

for Its charge pump cIrcuItry. Four factors have to be consIdered when

selectIng the value of the boot capacItor:

7oltage drop due to transfer of charge to the |DSFET gate.

7oltage drop due to the chargIng of the boot capacItor vIa the

Internal 0|DS transIstor.

7oltage drop caused by steady onstate |DSFET gate leakage - the

Inverter In thIs case Is beIng swItched at a relatIvely hIgh

frequency thus gate leakage problems can be Ignored.

Feference voltage frequency when compared to boot capacItance

- Ie. the capacItor can not be too large.

f a C

8DDT

value of 1uF Is selected we can generally avoId the effects

mentIoned above. ThIs Is a usual value and Is suItable for thIs applIcatIon.

"

Two of these Cs are requIred, one for each leg of the full brIdge. They

feature an Inverted lower swItch output, thIs means only a sIngle PW|

sIgnal per leg Is requIred from the master controller.

Dutput FIlter

FIlterIng of the Inverters output Is essentIal to meet the total harmonIc

dIstortIon standards. A typIcal confIguratIon of a common mode suppressIon

coIl followIng by a dIfferentIal mode maIns rated capacItor Is used (fIgure

15). ThIs fIlter, coupled wIth unIpolar PW| technIques wIll result In an

output power qualIty that meets the AustralIan standard (SectIon 2.J).

4.5 Current and VoItage SensIng

There are three sensIng requIrements for the converter, the voltage on the

J5070C bus, the output voltage (grId voltage) and the output current. All of

these quantItIes must be condItIoned before than can be Input to analogue

to dIgItal converters.

0C 8us 7oltage

The 0C bus voltage Is requIred for control of the 0C boost converter, the

control of the boost wIll be achIeved vIa Isolated PW| as dIscussed

prevIously. The 0C bus voltage may also be used In feed forward Inverter

control technIques. The natural power rIpple on the 0C bus can also be left

'as Is' to enable automatIc perturbatIon for power trackIng. n thIs case the

0C voltage would also be used as an Input to the |PPT algorIthm. FIgure 16

shows that the sensIng cIrcuIt Is sImply a voltage dIvIder followed by an op

amp cIrcuIt confIgured as a voltage follower. Extra protectIon Is provIded

for the opamp termInals by two separate resIstors connected In serIes wIth

!

the hIgh voltage bus. The voltage follower offers a degree of IsolatIon for

the A0C Inputs.

Figure 16. DC Voltage Sensing

AC 8us 7oltage

7oltage sensIng on the AC bus Is a lIttle more complIcated, the cIrcuIt Is a

dIfferentIal amplIfIer confIguratIon (fIgure 17). The opamp wIll output a

sIgnal based upon the dIfference between the two Inputs as opposed to a

Figure 17. AC Voltage Sensing

neutral referenced sIgnal. ThIs reduces noIse and hence Increases accuracy

In the readIng. An offset voltage must be applIed In order to convert the bI

#

polar AC sIgnal Into a 07 to +57 sIgnal suItable for A0 conversIon. ThIs offset

voltage Is 2.57 and Is applIed to the 'ground' of the nonInvertIng voltage

dIvIder network.

ProtectIon dIodes are Included at the termInals of the opamp, these are

sImply backtoback dIodes. 0urIng power off the opamps termInals would

be subject to AC grId voltages, enough to destroy the C, the dIodes reduce

thIs voltage to 0.67 (the voltage drop across a forward bIas dIode).

AC Current

The current flowIng out of the converter Is perhaps the most dIffIcult

quantIty to measure. The low currents Involved allow sense resIstors to be

used wIth mInImal power loss. However measurIng such small voltages

across these resIstors wIthIn such a large common mode sIgnal (240AC)

presents some dIffIcultIes. t Is for thIs reason that dIrectly sensIng current

flowIng out of the converter Is a not a vIable solutIon.

Figure 18. AC Current Sensing

Another approach Is to measure the current flowIng through each leg of the

full brIdge Inverter durIng theIr 'on' state. ThIs Is done by placIng a small

sense resIstor between the source of the lower |DSFET and ground on both

legs (fIgure 15). ThIs means that the voltage measured across thIs resIstor Is

essentIally referenced to ground and thus wIll not be swamped by hIgh

common mode voltages.

The sensIng cIrcuItry Is now made quIte sImple (fIgure 18), two of these

cIrcuIts are requIred, one for each leg. The opamp Is wIred as a non

InvertIng hIgh gaIn amplIfIer. ThIs cIrcuIt elImInates the need for an offset

voltage, posItIve and negatIve goIng currents are represented by a

respectIve leg of the full brIdge.

Dffset Feference 7oltage

The offset voltage requIred by the AC voltage measurIng cIrcuIt Is provIded

by a reference voltage C, the L|2J6 (fIgure 19). The output If thIs C Is also

Input to a spare A0C channel, the readIng can be dIrectly subtracted from

the voltage sensIng Input. ThIs sImplIfIes the voltage calculatIon In the

mIcrocontroller as well as IncreasIng accuracy In the readIng.

Figure 19. Reference Voltage

4.6 Converter haster ControI

As can be seen In fIgure 8 on page 19 a central controller Is used to provIde

the majorIty of the functIonalIty In the converter. Two maIn optIons were

consIdered for thIs controller, a standard mIcrocontroller or a 0SP (0IgItal

SIgnal Processor). A 0SP Is essentIally a hardware extended mIcroprocessor,

It contaIns addItIonal hardware to speed up common functIons used In

control and sIgnal processIng applIcatIons. t was decIded that the addItIonal

Figure 20. Master Controller

cost of a 0SP was sImply not warranted. 0SPs also consume a consIderable

amounts of power, around 20 tImes that of a mIcrocontroller, they are also

physIcally larger than most mIcrocontrollers.

Processor SelectIon

Two mIcrocontrollers were found to be suItable for the task, a low power

chIp from Texas nstruments and a proven controller from Atmel's range. t

was eventually decIde to use the 90S85J5 from Atmel, ease of access to

development tools and programmers was a factor In thIs choIce. The 85J5

contaIns 8K of flash memory, enough to comfortably develop control and

functIonalIty of the converter. ts perIpherals Include A0Cs, PW| functIons

and a UAFT channel. The cIrcuItry for the controller can be seen In fIgure

20.

A0C Channels

The 85J5 contaIns an 8 channel, 10bIt A0C. ThIs level of resolutIon Is

suffIcIent for all of the sensIng applIcatIons, 5 out of the 8 channels are

used.

PWM Caabltes

The 85J5 has one 8bIt and one 16bIt counter that can be used In PW|

control. The chIp also has an addItIonal 8bIt counter that can be used for

tImIng functIons. The 16bIt counter offers suffIcIent resolutIon for unIpolar

swItchIng of the full brIdge, It also features two outputs referenced from

the same counter. FunnIng the 85J5 at Its rated speed of 8|Hz allows a

PW| swItchIng speed of around 16kHz, quIte suItable for the full brIdge.

The PW| sent to the half brIdge controller Is also at 16kHz and Is produced

usIng the 8bIt PW| enabled counter.

ln System Proyrammny

The Atmel chIp features SP (n System Programmable) capabIlItIes, thIs

allows code to be downloaded dIrectly to the C vIa an 0C connector. ThIs

In turn aIds development of code and allows a surface mount versIon of the

chIp to be used thus reducIng the physIcal space used.

Reset Control

Although the 85J5 features a poweron reset tImer an addItIonal reset

controller was added to the cIrcuIt. ThIs Is to ensure error free startup and

mInImIse data corruptIon, thIs Is partIcularly Important due to the noIsy

envIronment In whIch the processor wIll work. The reset C sImply holds the

85J5 In reset untIl the supply voltage has reached a satIsfactory level.

FS485 nterface

An Industry standard FS485 Interface was Included In the desIgn for

Increased flexIbIlIty. 0ebug InformatIon can be receIved from thIs port

durIng code development. The port can also be networked wIth other

converters to monItor power flow and error condItIons In a large system.

Software

Code for the Atmel, can be compIled from C source. ThIs allows fast

development tImes and ease of software maIntenance. ntegratIng the CNU

CCC compIler wIth Atmels own A7F StudIo creates a powerful development

system and allows ease of programmIng.

4.7 Power SuppIIes

The derIvatIon of logIc and gate drIve power supplIes Is not always a trIvIal

task. 0ue to the low amount of power used In the controllIng devIces of the

converter lInear regulators are used exclusIvely.

P7 SIde

Dnly a sIngle regulator was requIred on the P7 sIde of the IsolatIon

boundary. The P7 voltage Is regulated to 107, thIs voltage Is supplIed to the

gate drIve C, fIlter opamps as well as the Internal regulator of the PW| C

(fIgure 21). ThIs Internal regulator outputs 57 to supply the logIc wIthIn the

C, It can also be used externally and Is used as the supply for the logIc level

optocoupler.

Figure 21. PV Side Power

CrId SIde

The grId sIde supply Is slIghtly more complIcated. The logIc and gate drIve

supply Is derIved from a second, secondary wIndIng on the hIgh frequency

power transformer. ThIs wIndIng consIsts of three turns, the voltage Is

rectIfIed usIng small 1n4148 dIodes and Input to a fIlter capacItor (fIgure

22). The resultIng voltage In then Input to two separate lInear regulators,

one 107 and the other 57. These regulators supply the gate drIve Cs,

sensIng cIrcuItry, the optocoupler and the mIcrocontroller. A number of 1uF

capacItors are placed near 7cc pIns of the varIous components In order to

reduce transIent effects.

$

Figure 22. Grid Side Power

4.8 PhysIcaI Layout

n order to meet set sIze lImIt of the converter much car was taken In the

placement and routIng of components on the PC8 (PrInted CIrcuIt 8oard).

|any of the devIces used were S|0s (Surface |ount 0evIces) thIs allow hIgh

component densIty and placement on both sIdes of the board. Dne

partIcular layout Issue relevant to power electronIcs Is the effect of stray

Inductances and capacItances, thIs Is due to the PC8 tracks themselves

exhIbItIng capacItance and Inductance. The entIre PC8 can be seen In

appendIx A at the end of thIs document.

Stray nductance

As mentIoned prevIously the half brIdge dual Is

partIcularly susceptIble to stray Inductance

effects. n order to mInImIse thIs problem one can

easIly reduce loop Inductance, thIs essentIally

means reduces the physIcal sIze of loops In the

hIgh frequency swItchIng path. FIgure 2J shows

how the half brIdge swItches are routed between

the prImary termInals of the transformer and the

Figure 23. Loop Routing feedIng Inductors. 8y keep tracks close together

and placIng the ground track on the bottom the

swItchIng loop can be mInImIsed. Stray Inductance can also be produced by

the track Itself, therefore mInImIsIng track length Is also Important.

%

Surface |ount 0evIces

Surface mount devIces offer many

advantages In terms of routIng and

component densIty. FIgure 24 shows an

example of S|0 placement, these are

Figure 24. SMD Placement the full brIdge |DSFET gate drIvers, they

are placed on the bottom of the board.

ThIs allows room for larger passIve components on the top of the board

such as the 0C bus storage capacItor.

"

5.0 CDNVEPTEP PEPFDPhANCE

5.1 0C-0C Converter DperatIon

8oost DperatIon

FIgure 25 shows the output voltage of the converter prIor to rectIfIcatIon, It

can be seen that thIs voltage Is approxImately 4007 peak to peak. The

rIngIng seen on the transItIons Is one of the undesIred effects of extremely

hard swItchIng.

Figure 25. Secondary Winding Output

Cate 0rIve

FIgure 26 shows the actual |DSFET gate drIve waveforms of the half brIdge

dual, as can be seen these are quIte suffIcIent and relatIvely clean. The

mInImum overlap can also be seen, thIs Is therefore the lowest duty cycle

that the |DSFETs wIll see. The frequency of thIs swItchIng Is around

122kHz.

!

Figure 26. MOSFET Gate Drive

SC2524 and PW| FIlter DperatIon

As shown prevIously the PSpIce analysIs of the PW| fIlter revealed that It

gave a smooth response from 0 to 100 duty cycle Input. The actual cIrcuIt

dIffered only In the fact that full range output actually occurs wIthIn a

smaller range of PW| duty cycle. ThIs essentIally means that control of the

boost of the converter Is not as fIne as was desIgned. ThIs presents no real

problem. The SC2524 PW| controller performs as expected, through full

range error Input the output duty cycle ranges between 52 and 97. ThIs

means that full range control of the boost converter Is avaIlable to the

master controller.

EffIcIency

FIgure 27 shows a plot of converter effIcIency versus load as a percentage of

rated load Ie. 100W. As can be seen the converter reaches a maxImum

effIcIency of 80.5. Although lower than hoped thIs fIgure Is stIll quIte

#

respectable for an Isolated converter. The converter performs poorly at low

loads, although thIs Is to be expected thIs area obvIously needs ImprovIng

for P7 specIfIc applIcatIons. The effIcIency test was carrIed out at a duty

cycle of 50 wIth an ohmIc load varyIng between 1k and 10k ohms. 0etaIled

results of the effIcIency test can be seen In table 1 In the appendIces.

Figure 27. Converter Efficiency

Transjormer leakaye

Few problems were observed relatIng to transformer leakage and other

stray Inductances. 7oltage overshoot was mInImal thus the overvoltage

snubber dIssIpates very lIttle power. FIgure 28 shows the Input waveforms to

the prImary wIndIng of the transformer, these measurements were taken

wIth an Input voltage of 207. The snubber In thIs case was dIsabled to see

actual swItchIng voltages. As can be seen the maxImum voltage at the

termInals of the transformer (also the voltage across the |DSFETs) reaches

a maxImum of 527. ThIs Is well wIthIn the |DSFETs ratIng of 607.

65

67

69

71

73

75

77

79

81

83

21 36 67.2 100.7 63 126 120 138

Percentage of FuII Load (100W)

E

f

f

i

c

i

e

n

c

y

(

%

)

Figure 28. Primary Winding Inputs

5.2 ControIIer DperatIon

The small amount of code wrItten for the master controller was prImarIly

for testIng the SP of the Atmel and the general operatIon of the

mIcrocontroller Itself. The SP hardware Is operatIonal; a small LE0 was

perIodIcally flashed to IndIcate controller operatIon. ThIs LE0 also IndIcates

that the prImary sIde power supply (derIved from the transformer) Is also

operatIonal. The test code lIstIng can be found on page 1 of the appendIces.

5.3 0C-AC Inverter DperatIon

Unfortunately at the tIme If wrItIng no code had been developed for the

control of the Inverter swItches. ThIs means that both the effIcIency of the

Inverter and the performance of the output fIlter had not been evaluated.

5.4 Cost

An aIm of thIs project was to construct prototype hardware for less than

150AU0. The total component cost of the prototype was approxImately