Professional Documents

Culture Documents

CPU registers and status flags explained

Uploaded by

Reparación De Laptops En CelayaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CPU registers and status flags explained

Uploaded by

Reparación De Laptops En CelayaCopyright:

Available Formats

Scanned and converted to PDF by HansO, 2001

Chapter 3 page 1-42

In this PDF: Chapter 3 page 1-42

CPU REGISTERS AND STATUS FLAGS

The CPU registers and status flags for the laO may be illustrated as follows:

Alternate Flags

Flags

Sign

Zero

Auxiliary Carry

Parity10verfiow

Subtract

Carry

Stack Pointer

Program Counter

ndex Register

Index Register

nterrupt Vector Register

Refresh Register

Accumulator

} Secondary Data Counters

Primary Data Counter

Alternate Accumulator

}

Alternate Secondary

Data Counters

Alternate Primary Data Counter

~

ro-

, ,r

I

r r

S I Z I IAct IPloi N Ic

A

B C

0 E

H L

S'I z'l lAd IP!c)'1 N'I C'

A'

B' C'

0' E'

H' L'

SP

PC

IX I

IV

I I

R

Secondary {

Accumulators

Alternate {

Secondary

Accumulators

The Accumulator is the primary source and destination for one-operand and two-

operand instructions. For example, the shortest and fastest data transfers between the

CPU and 1/0 devices are performed through the Accumulator, In addition, more Memo-

ry Reference instructions move data between the Accumu later and memory than bet-

ween any other register and memory All 8-bit arithmetic and Boolean instructions take

one of the operands from the Accumulator and return the result to the Accumulator. An

instruction must therefore load the Accumulator before the laO can perform any a-

bit arithmetic or Boolean operations.

The B. C. D. E. H. and L registers are all secondary registers. Data stored in any of

these six registers may be accessed with equal ease: such data can be moved to any

other register or can be used as the second operand In two-operand instructions.

There are, however, some important differences in the functions of Registers B, C. D. E.

H. and L

Registers Hand L are the primary Data Pointer for the laO. That is to say. you will

normally use these two registers to hold the 16-bit memory address of data being ac-

cessed. Data may be transferred between any registers and the memory location ad-

dressed by Hand L Since HL is the primary Data Pointer, It ohen takes fewer bytes of

object code and less instruction cycles to perform operations with it. The Z80 program-

mer should try to address data memory via Registers Hand L whenever possible.

Within your program logic. always reserve Registers Hand L to hold a data memo-

ryaddress.

3-2

Registers B. C. D. and E provide secondary data storage; frequently. the second

operand for two-operand instructions is stored in one of these fou r registers. (The first

operand is stored in the Accumulator. which is also the destination for the result.)

There are a limited number of instructions that treat Registers Band C. or D and E.

as 16-bit Data Pointers. But these instructions move data between memory and the

Accumulator only.

In your program logic you should normally use Registers B. C. D. and E as tempor-

ary storage for data or addresses.

Registers IX and IV are index registers. They provide a limited indexing capability of

the type described in An Introduction to Microcomputers: Volume 1 for short instruc-

tions.

The alternate registers F'. A'. B'. C'. 0'. E

/

H'. and L' provide a duplicate set of

general purpose registers. Just two single-byte Exchange instructions select and

deselect all alternate registers; one instruction exchanges AF and the alternate AF'

as a register pair. and one instruction exchanges BC. DE. and HL with the alternate BC'.

DE'. and HL' Once selected. all subsequent register operations are performed on the ac-

tive set until the next exchange selects the inactive set. The alternate registers can be

reserved for use when a fast interrupt response is required. Or. they may be used in

any desired way by the programmer.

There are a number of instructions that handle 16 bits of data at a time. These in-

structions refer to pairs of CPU registers as follows:

F

B

D

H

F'

B'

D'

H'

~

High-

order

byte

and

and

and

and

and

and

and

and

A

C

E

L

A'

C'

E'

L'

~

Low-

order

byte

The combination of the Accumulator and flags. treated as a 16-bit unit. is used only for

Stack operations and alternate register switches Arithmetic operations access Band C.

D and E. or Hand L as 16-bit data units.

The Carry status flag holds carries out of the most significant bit in any arithmetic

operation. The Carry flag is also included in Shift instructions: it is reset by Boolean in-

structions.

The Subtract flag is designed for internal use during decimal adjust operations, This

flag is set to 1 for all Subtract instructions and reset to 0 for all Add instructions.

The Parity/Overflow flag is a multiple use flag. depending on the operation being

performed. For arithmetic operations, it is an overflow flag. For input. rotate. and

Boolean operations, it is a parity flag. with 1 = even parity and 0 = odd parity. Dur-

ing block transfer and search operations. it remains set until the byte counter decre-

ments to zero: then it is reset to zero It is also set to the current state of the interrupt

enable flip-flop (IFF2) when a LD A.I or LD A.R instruction is executed.

The Zero flag is set to 1 when any arithmetic or Boolean operation generates a

zero result. The Zero status is set to 0 when such an operation generates a non-

zero result.

3-3

The Sign status flag acquires the value of the most significant bit of the result

following the execution of any arithmetic or Boolean instruction.

The Auxiliary Carry status flag holds any carry from bit 3 to 4 resulting from the

execution of an arithmetic instruction. The purpos'e of this status flag is to simplify

Binary-Coded-Decimal (BCD) operations; this is the standard use of an Auxiliary Carry

status flag as described in An Introduction to Microcomputers: Volume 1, Chapter 3.

All of the above status flags keep their current value until an instruction that modifies

them is executed. Merely changing the value of the Accumulator will not necessarily

change the value of the status flags. For example. if the Zero flag is set. and a load im-

mediate to the Accumulator is executed. that causes the Accumulator to acquire a non-

zero value: the value of the Zero flag remains unchanged.

The 16-bit Stack Pointer allows you to Implement a Stack anywhere in addressa-

ble memory. The size of the Stack is limited only by the amount of addressable memory

present In reality you will rarely use more than 256 bytes of memory for your Stack.

You should use the Stack for accessing subroutines and processing interrupts. Do not

use the Stack to pass parameters to subroutines. This is not very efficient within the

limitations of the zao instruction set. The zao Stack is started at its highest address. A

Push decrements the Stack Pointer contents; a Pop increments the Stack Pointer con-

tents

The Interrupt Vector register and the Refresh register are special-purpose

registers not normally used by the programmer.

The Interrupt Vector register is used to store the page address of an interrupt response

routine: the location on the page is provided by the interrupting device. This scheme

allows the address of the interrupt response routine to be changed while still providing

a very fast response time for the interrupting device.

The Refresh register contains a memory refresh counter in the low-order seven bits.

This counter is incremented automatically after each instruction fetch and provides the

next refresh address for dynamic memories. The high-order bit of the Refresh register

will remain set or reset. depending on how it was loaded at the last LD RA instruction.

lao MEMORY ADDRESSING MODES

The zeo provides extensive addressing modes. These Include:

Implied

Implied Block Transfer with Auto-Increment/Decrement

Implied Stack

Indexed

Direct

Program Relative

Base Page

Register Indirect

Immediate

3-4

Implied

In implied memory addressing. the Hand L registers hold the address of the

memory location being acces.ed. Data may be moved between the identified memo-

ry location and anyone of the seven CPU registers A. B. C. D. E, H, or L. For example, the

instruction

LD C.(HU

loads the C register with the contents of the memory location currently pointed to by

HL. This is illustrated as follows:

Data

q

mmmm

mmm+ 1

1----.. mmrnm + 2

1- .. mmmm + 3

Memory

r

yy

1

-

pp qq

mmmm

~ m m m + ~

Program

Memory

I 4E

I m

s Z AcP/O N C

Fc:::I:IJ:I:]

A

S.C

D.E

H.l

SP

PC

IX

IV

I

R

LD C. (HU

~

76543210

EE:EE:EEEEl

1:1 [------Load Implied via HL

C Register

3-5

A limited number of instructions use Registers Band C or 0 and E as the Data

Pointer. These instructions move data between the Accumu lator and the memory loca-

tion addressed by Registers Band C or Registers D and E. The instruction

LD (BCLA

stores the contents of A into the memory location currently addressed by Register Pair

Be. This is illustrated as follows:

SZACPONC Data

Q

mmm

mmm+1

mmmm+2

1-----4mmmm + 3

CIIIIIl

Memorv

vv -

ppq

pp qql

1

j

- ~ V

Program

mmmm ~ m m m + 1

MemOry

I

02 m

I

m

F

A

B.C

O.E

H.L

SP

PC

IX

IY

I

R

LD (BCl.A

---

"",._...",.A....~ __...

r, 6 S:-4 3 2 1 0'

~

-..... J

T Store Implioed from A via BC

3-6

ED mmmm

...-----==80;-..... mmmm + 1

mmmm+2

1----1 mmmrri +3

Implied Block Transfer With Auto-Increment/Decrement

Block Transfer and Search instructions operate on a block of data whose size is

set by the programmer as the contents of the BC register pair. In this form of ad-

dressing. a byte of data is moved from the memory location addressed by HL to

the memory location addressed by DE; then HL and DE are incremented and Be is

decremented. Data transfer continues until BC reaches zero. at which point the In-

struction is terminated. Variations include allowing other instructions to follow

each data transfer. with the programmer supplying the loopback; auto-decrement-

ing HL and DE instead of auto-incrementing; and a complementary set of Block

Search instructions that compare the memory byte addressed by HL with the con-

tents of the A register. setting a flag if a match is found.

The Load. I ncrement. and Repeat instruction

LDIR

is illustrated as follows:

Set if BC- 1- o.eS8t otherwise

S Z AcP'ON C

Fo:::EI:E:I2IJ

Ar-__...-__..... .......

B.CI-__ .......__.."

D,E 1-__

.L

Spt- .....

PC mmmm

IX ...------...;..------....

IV ....... 4111........--_

I

R

LOIR

...+o....-+.....-.-..O-+-:... } load. Increment, and Repeat instruction

A similar group of Input/Output instructions is provided. allowing a block of data

to be input or output between memory and an I/O device. The I/O port nu mber is

taken as the contents of the C register. with the sing Ie B reg ister used as the byte

counter. Memory is addressed by HL.

3-7

Implied Stack

Since the Stack is part of ReadIWrite memory, we must consider Stack instructions as

Memory Reference instructions. Pu.h and Pop in.truction. move two byt of data

b.twn a r.gl.t.r pair and the .ddrd Stack Polnt.r location. i,e., current top-

of-stack, The Z80 Stack address is decremented with each Push and incremented with

each Pop. The instruction

PUSH DE

is illustrated as follows:

5 ZAcP/ON C

Data

ssss - 2

ssss - 1

ssss

mmmm

mmmm+ 1

...- oImmmm + 2

I- -tmmmm + 3

r::IJ:IJ:IJ

Memorv

-

C

qq

I

JA ssss-2 ~ -

pp I

pp qq

/'/'

ssss

~ - ~ ~

mmmm

:mmm+l

Program

Memory

I 05

I

F

A

B.C

D.E

H,l

SP

PC

IX

IV

,

R

PUSH DE

~ X ,

76543210

~ ~ , o , o , ~ _

-- PUSH instruction

---Register Pair DE

3-8

The laO allo hal instructions that exchange the two top-of-stack bytes with a

16-blt register - HL or one of the two index registers. The instruction

EX (SPl,HL

is illustrated as follows:

S Z Ac Pia N C

Data

ssss

ssss + 1

ssss + 2

mmmm

mmmm+ 1

mmmm+2

.....-----t

mmmm

+ 3

DIIIIJ

Memory

-

---

:

qq

pp

M"

xx yy

ssss

-" :v

mmmm mmmm +'

Program

Memory

I E3

I

F

A

B.C

D.E

H.L

SP

PC

IX

IV

I

R

3-9

Indexed

Th. zao ha. two 16-bit Ind.x r.gl.t.rs, call.d IX and IV. They may be used in-

terchangeably, All memory reference operations for which (HU can be specified can

alternatively be specified as an indexed operation, The difference between implied ad-

dressing using HL and indexed addressing using IX and IY is that the ind.x op.rand

includ a di.plac.m.nt valu. that i. add.d to the ind.x addr. ln the instruction

ADD A. (IX+40H)

the memory address is the sum of the contents of the IX register and 40

16

, This may be

illustrated as follows:

40

m

m+ 1

m+2

m+3

Data

IMemory J

ppqq

xx XX+YY

--

,

yy

; ppqQj

I

-

Program

mmmm

ppqq

-

Memory

I DO mmm

I 86

mmm

40 mmm

JI' -

.:L

mmm

ADD A,OX + 40)

S Z Ac P/O N C

A

B,C

D.E

H,l

SP

PC

IX

IV

,

R

3-10

Direct

Direct addressing can be used to load the Accumulator with any 8bit value from

memory, load BC, DE, HL, SP, IX, or IV with any 16-bit memory value, and jump or

call subroutines direct at any memory location. The 16-bit direct address is stored in

the last two bytes of the instruction. in low-byte high-byte order (this is the reverse of

the standard high-low schemel.

The i nstructi on

LD A.(NETX)

loads the A register with the contents of the memory location addressed by the label

NETX. The instruction

LD HL.l1 FFH)

loads the L register with the contents of memory location 01 FF16 and the H register

with the contents of memory location 0200

16

. This may be illustrated as follows:

Data

OIFF

0200

mmmm

) mmmm+ t

1 01 mmmm+2

1-----1 mmmm + 3

Memory

YV

xx

6

,

xx YV

- '"

Program

mmmm mmmm + 3

- "-

Memory

I 2A

I FF

'-,

S Z Ac P/O N C

FCIIIID

A

S,C

D.E

H.L

SP

PC

IX

IV

I

R

LD HL.!IFFH)

76543210

0 0

,

0 1 0

,

0

1 1 1 1 1 1 1 1

0 0 0 0 0 0 0 1

Load HL Direct instruction

Direct address - low byte

Direct address - High byte

The direct Jump instructions provide jumps and jumps-to-subroutines, both un-

conditional and conditional. These are all 3-byte instructions. with the direct address

stored in the second and third bytes of the instruction. as shown above for Load Direct.

There are three additional addressing modes used by zao Branch instruc-

tions: program relative. base page. and register indirect. In general. they are shorter

and/or faster than direct jumps but may have more limited addressing capabilities.

3-11

Program Relative

Jump Re.etlve instructions pro'ltde pregrem re.etive eddre.slng In the renge -128,

+129 byte. from the first byte of Relative instruction. These instructions

are all 2-byte instructions, with 1'fte signed displacement value stored in the second

byte of the instruction. There .... uaaonditlonel end conditioneI re.etive jump., e.

well Decrement end Jump " Not Zero in.truction (DJNZ) thet fecllltete. loop

control.

Given the instruction

JR SRCH

assume that SRCH is a label alltdressing a location 5A

16

bytes up in memory from the

JR op-code byte. The operati.on may be illustrated as follows:

5 Z AcP/O N C

FCIIIIIJ

Data

Memory

A

B.C

D,E

H,L

SP

PC

IX

IV

I

R

- 'mmmm:f)

Program

mmmm

"""- SA

Memory

I 18

I SA

--.

JR SRCH

mmmm

mmmm+l

mmmm+2

mmmm+3

Jump Relative iAStruction

o Displacement

...."'--"'--"'--"""-"'--.....

3-12

Base Page

The Z80 has a modified base page addressing mode for the Restart instruction. This is

a special Call instruction that allows a single-byte instruction to jump to one of

eight subroutines located at specific points in lower core. The effective address is

calculated from a 3-bit code stored in the instruction. as follows:

Lower Core Address 3-Bit Code

OOH

08H

10H

18H

20H

28H

30H

38H

000

001

010

all

100

101

110

111

The decoded address value is loaded into the low-order byte of the Program Counter;

the high-order byte of the Program Counter is set to zero. For example. the instruction

RST OOH

is illustrated as follows:

s Z AcP/O N C Data

F

A

B.C

D.E

H.L

SP

PC

IX

IV

I

R

CIII:ID

Memory

,

mm+l

fl

mm

t:. ssss - 2

----..........

ssss

mmmm

Program

Memory

I

......-....

C7

000

I

ssss - 2

ssss - 1

ssss

mmmm

mmmm+ 1

mmmm+2

mmmm+3

RST OOH

76543210

-ccT--_Rest8rt instruction

code

3-13

Data

Memory

Register Indirect

In standard indirect addressing. a memory location contains the effective address. and

the instruction specifies the address of the memory location containing the effective

address. In register indirect addressing. a register contains the effective address. and

the instruction specifies which of the registers contains the effective address Note that

for a Load, for instance. this is just another way of describing implied addressing.

However. the l80 has Jump instructions that allow a jump to the memory location

whose address is contained in the specified register. This is a form of indirect ad-

dressing. and is described separately because. while most microcomputers have im-

plied addressing. very few have register indirect jumps.

The instruction

JP (HL)

directs that a jump is to be taken to the memory location whose address is contained in

HL This may be illustrated as follows:

S Z AC P/O N C

FCCIIIIJ

A

B,C

D.E

H.L

SP

PC

IX

IV

I

R

pp qq

D

mmmm

I

I

JP (HLl

--:x..-

.... ----...... :0-.

76543210

3-14

Program

Memory

E9 mmmm

1-__...... mmmm + ,

mmmm+2

1---...... mmmm + 3

Immediate

Some texts identify Immediate instructions as Memory Reference instructions. An Im-

mediate instruction is a 2-. 3-. or 4-byte instruction in which the last one or two bytes

hold fixed data that is loaded into a register or memory location. The Z80 provides Im-

mediate instructions to:

load 8-bit data into any of the 8-bit registers.

load 16-bit data into any of the register pairs or 16bit registers.

store 8-bit data into any memory location using implied or indexed addressing.

perform arithmetic and logical operations using the Accumulator and 8-bit im-

mediate data.

The instruction

LD BC.OBCH

loads the immediate data value BC16 into Register Pair BC. This may be illustrated as

follows:

S Z AcP/O N C

FCD:IIIJ

Data

Memory

A

B.C

D.E

H.l

SP

PC

IX

IV

I

R

...

mmmm

Program

Memory

I

01

I BC

'- 00

mmmm

mmmm + 1

mmmm+2

mmmm+3

LD BC. 08CH

76543210

'4T """ Om"""'... M ROO' "',

Pair BC

76543210

1 0 1 1 1 1 0

o I

0 0 0 0 0 0 0

o I

Immediate data - low-order byte

Immediate data - high-order byte

3-15

Table 3-1. Frequently Used Instructions of the zeo

Instruction Code Meaning

ADC A Add with Carry to Accumulator

ADD Add

AND Logical AND

CALL addr Call Subroutine

CALL cond,addr Call Conditional

CP Compare

DEC Decrement

DJNZ Decrement and Jump If Not Zero

IN Input

INC Increment

JR Jump Relative

JR cond.addr Jump Relative Conditional

LD reg.(HL) Load Register

LD A,(addr) Load Accumulator Direct

LD data Load Immediate

LD (HL).reg Store Register

LD (addrl.A Store Accumulator Direct

LD dst.src Move Register-ta-Register

OUT Output

POP Pop from Stack

PUSH Push to Stack

RET Return from Subroutine

RET cond Return Conditional

RLA Rotate Accumulator Left Through Carry

RRA Rotate Accumulator Right Through Carry

SLA Shift Left Arithmetic

SRL Shift Right Logical

SUB Subtract

3-16

Table 3-2. Occasionally Used of the laO

Instruction Code Meaning

BIT Test Bit

CPD,CPDR Compare. Decrement. (Repeat)

CPI, CPIR Compare, Increment. (Repeat)

CPL Complement A<:cumulator

DAA Decill11itl Adj ust Accumu lator

01 IMerrupts

EI Enable Interrupts

EX Exchange

HALT Halt

IND.INDR Input. [)ecrement. (Repeat)

IN!. INIR Input. IncremtiHlt. (Repeat)

JP addr Jump

JP cond,addr Jump Conditional

LD A, (BC) or (DE) Load Accumulator Secondary

LD HL.(addd Load Hl Direct

LD reg, (xy+disp) Load Register Indexed

LD rp.(addr) Load Pair Direct

LD xy,(addr) Load Index Register Direct

LD (BC) or (DE),A Store Accu mu lator Secondary

LD (addr),HL Store Hl Direct

LD (xy+disp).reg Store Regfster Indexed

LD (addr),rp Store R-egis1'er Pair Direct

LD (addd,xy Store Index Register Direct

LD (HL),data Store Immediate to Memory

LD {xy+displ.data Store Immediate to Memory Indexed

LDD. LDDR Load, Decrement. (Repeat)

LD!. LDIR Load. Increment. (Retlleat)

NEG Negate (Twos Complement) Accumulator

NOP No Operation

OR Logical OR

OUTD.OTDR Output. Decrement. lRepeat)

OUTI. OTIR Output. Increment. (l\epeat)

RES Reset !i'it

RETI Retu rn from Interrupt

RL Rotate Left ThrouQh Carry

RLC Rotate Left Circular

RLCA Rotate Accumulator Left Circular

RR Rotate Right Throullh Carry

RRC Rotate RiQt1t Circll'tar

RRCA Rotate Accumu"tor Right Circular

SET Set Bit

SRA Shift Right Arithmetic

XOR Exclursi-ve OR

3-17

Table 3-3 Seldom Used Instructions of the Z80

Instruction Code Meaning

ADC HLrp Add Register Pair with Carry to HL

CCF Complement Carry Flag

EXX Exchange Register Pairs and Alternatives

1M n Set Interrupt Mode

RETN Return from Non-Maskable Interrupt

RLD Rotate Accumulator and Memory Left Decimal

RRD Rotate Accumulator and Memory Right Decimal

RST Restart

SSC Subtract with Carry (Borrow)

SCF Set Carry Flag

LD AI Load Accumulator from Interrupt Vector Register

LD AR Load Accumulator from Refresh Register

LD I.A Store Accu mu lator to Interru pt Vector Register

LD R.A Store Ac{'u mu lator to Refresh Register

LD SP.HL Move HL to Stack Pointer

LD SP.xy Move Index Register to Stack Pointer

ABBREVIATIONS

Program Counter

An 8-bit I/O port address

data

data16

These are the abbreviations used in this chapter:

A.F.B.C.D,E.H.L The 8-bit registers. A is the Accumulator and F is the Flag Word.

AF'.BC'.DE'.HL' The alternate register pairs

addr A 16-bit memory address

x(b) Bit b of 8-bit register or memory location x

cond Condition for program branching. Conditions are:

NZ - Non-Zero (Z = 0)

Z -Zero(Z=l)

NC - Non-carry (C = 0)

C - Carry (C = 1)

PO - Parity Odd (P = 0)

PE - Parity Even (P = 1)

P - Positive Sign (S = 0)

M - Negative Sign (S = 1)

An 8-bit binary data unit

A 16-bit binary data unit

An 8-bit signed binary address displacement

The high-order 8 bits of a 16-bit quantity xx

Interrupt Vector register (8 bits)

The Index registers (16 bits each)

A 16-bit instruction memory address

The low-order 8 bits of a 16-bit quantity xx

Least Sig nificant Bit (B it 0)

Most Significant Bit (Bit 7)

port

IX IY

label

disp

xx(HI)

I

xx(LO)

LSB

MSB

PC

3-18

pr

R

reg

rp

SP

xy

Object Code

Any of the following register pairs:

BC

DE

HL

AF

The Refresh register (8 bits)

Any of the following registers:

A

B

C

D

E

H

L

Any of the following register pairs:

BC

DE

HL

SP

Stack Pointer (16 bits)

Either one of the Index registers (IX or lY)

bbb Bit number 000 (LSB) to 111 (MSB)

eec Condition code 000 = non-zero

001 = zero

010 = no carry

011 = carry

100 = parity odd

101 = parity even

110 = positive sign

111 =negative sign

ddd Destination register - same coding as rrr

ppqq A 16-bit memory address

rrr Register 111 = A

000 = B

001 = C

010 =D

011 = E

100 = H

101 = L

sss Source register - same coding as rrr

x Index reg ister 0 = IX

1 =IY

xx Register pair 00 = BC

01 = DE

10 = HL

11 =SP (rp) or AF (pr)

xxx Restart code (000 to 111)

yy An 8-bit binary data unit

yyyy A 16-bit binary data unit

3-19

Statuses

[[ ]]

[]

A

V

41-

---+

The l80 has the following status flags:

C - Carry status

l - lero status

S - Sign status

P/O - Parity/Overflow status

AC - Auxiliary Carry status

N - Subtract status

The following symbols are used in the status columns:

X - flag is affected by operation

(blank) - flag is not affected by operation

1 - flag is set by operation

o - flag is reset by operation

U - flag is unknown after operation

P - flag shows paritY status

o - flag shows overflow status

I - flag shows interrupt enabled/disabled status

Memory addressing: 1) the contents of the memory location

whose address is contained in the designated register. 2) an

I/O port whose address is contained in the designated register.

The contents of a register or memory location.

For example:

([HLll +- [[HLll + 1

indicates that the contents of the memory location addressed by

the contents of HL are incremented. whereas:

[HL] +- [HL] + 1

indicates that the contents of the HL register itself are incre-

mented.

Logical AND

Logical OR

Logical Exclusive-OR

Data is transferred in the direction' of the arrow

Data is exchanged between the two locations designated on either

side of the arrows.

3-20

INSTRUCTION MNEMONICS

Table 3-4 summarizes the leO instruction set. The MNEMONIC column shows the

instruction mnemonic UN, OUT, LD). The OPERAND column shows the operands,

if any. used with the instruction mnemonic.

The fixed part of an assembly language instruction is shown In UPPER CASE. The

variable part (Immediate data. I/O device number, register name. label or address)

is .hown in lower case.

are:

For closely related operands, each type is listed separately

mnemonic. For instance, examples of the format entry

LD rp,(addr)

xy,(addr)

LD BC.(DAT2)

LD IX,(MEM)

INSTRUCTION OBJECT CODES

without repeating the

The object code a"d instruction length in byte. are shown in Table 3-4 for each

instruction variation. Table 3-5 lists the object codes in numerical order.

For instruction bytes without variations. object code. are represented as two

hexadecimal digits (e.g 3F).

For instruction bytes with variations in one of the two digits, the object code is

shown as one 4-bit binary digit and one hexadecimal digit le.g. 11 x 1 D) in Table

3-5. For other instruction bytes with variation., the object code is .hown as eight

binary digits (e.g., 0118.001).

INSTRUCTION EXECUTION TIMES

Table 3-4 lists the instruction execution times in clock periods. Real time can be

obtained by dividing the given number of clock periods by the clock frequency. For

example. for an instruction that requires 7 clock periods. a 4 MHz clock will result in a

1.75 microsecond execution time.

When two possible execution times are shown (j.e., 5/11), it indicates that the

number of clock periods depends on condition flags. The first time is for "condi-

tion not met," whereas the second is for "condition met."

STATUS

The six status flags are stored in the Flag register (F) as follows:

--+-...--t--+--......--These bits are not used

......--Carry status (carry out of bi,t 7)

......---- Subtract stetus

(, aftar subtract operation. 0 otharwise)

""------ Parity/Overflow

(for logical operations. 1 for ellen. 0 for odd parity.

For arithmetic, 1 for overflow)

10.- Auxiliary Carry status (carry out of bit 3)

.....------------Zero status (1 for zero, 0 for nonzero)

.....-------------Sign status (vatue of bit 7)

3-21

In the individual instruction descriptions. the effect of instruction execution on

status is illustrated as follows:

s Z AC Pia N C

171 !ll

x

l

o

l

x

l

~ l j ~ ~ ~ I

Modified to reflect results of execution

Unconditionally reset to 0

Unconditionally set to 1

Unchanged

Unknown

An X identifies a status that is set or reset. A 0 identifies a status

that is always cleared. A 1 identifies a status that is always set. A

blank means the status does not change. A question mark (?)

means the status is not known.

3-22

STATUS

CHANGES

WITH

INSTRUCTION

EXECUTION

Address Bus: AO-A7: [e)

AS-A1S: [B)

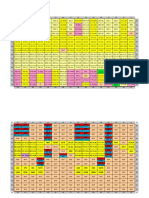

Taole 3-4. A Summary of the zao Instruction Set

(,J

I

""

(,J

Clock

Status

Type Mnemonic Operend Object Code Bytes Operation Performed;

Cycles

C Z S PIO AC N

IN A,(portl DB yy 2 10 [AJ- [pertJ

Input to Accumulator from directly addressed 1/0 port.

Address Bus: AO-A7: port

AS-A15 [AI

IN reg,ICl ED 01dddOOO 2 11 X X P X 0 [regl- [[ Cll

Input to register from 1/0 port addressed by the contents of C."

ED B2 2 20/15" 1

] ] 1

If second byte is 70

16

only the flags will be affected.

INIR ? Repeat until [ BJ = 0:

[[ HLI)- [(Cll

[BJ-[Bl- 1

[ HLI - [HLI + 1

Transfer a block of data from 1/0 port addressed by contents of C

to memory location addressed by contents of HL, going from low

addresses to high. Contents of B serve as a count of bytes remain-

ing to be transferred."

0 INDR ED BA 2 20/15" 1 7 ]

? 1 Repeat until [ BJ =0:

::.

[[HL1J-[[Cll

[B)-[B]- 1

[ HLJ - [HLJ - 1

Transfer a block of data from 1/0 port addressed by contents of C

to memory location addressed by contents of HL, going from high

addresses to low. Contents of B serve.as a count of bytes remaining

to be transferred."

INI ED A2 2 15 X ?

]

? 1 [[ HLI- [[ C]]

[B)-[BJ - 1

[ HLI - [ HLI + 1

Transfer a byte of data from 1/0 port addressed bv contents of C to

memory location addressed by contents of HL Decrement byte

count and increment destination address."

Address Bus: AO-A7: IC]

A8-A1S: IB)

Table 3-4. A Summary of the zao Instruction Set (Continued)

Co)

I

~

Clock

Statu.

Typa, Mnemonic Operand Object Code Byte.

Cycle.

Operation Performed

C Z S PIO A

C

N

INO EDAA 2 15 X ?

]

? I [[ HU] - [[ CII

(BJ - [BI- I

t HL] - [HLI - I

Transfer a byte of data from I/O port addressed by contents of C to

memory location addressed by contents of HL. Decrement both

byte count and destination address."

OUT (portl.A 03 yy 2 II [port] - [A]

Output from Accumulator to directly addressed I/O port.

Address Bus: AO-A7: port

A8-A1S: [Al

OUT (Cl.reg EO 01555001 2 12 11 C])- [reg]

Output from register to I/O port addressed by the contents of C."

OTIR ED B3 2 20/15 1

]

?

]

1 Repeat until ( BI =0:

'ij

([C])-([HL])

[8]- [BI - 1

::>

.5 (HU-[HU+ 1

e

Transfer a block of date from memory location addressed by con- 0

~

tents of HL to I/O port addressed by contents of C. going from low

g

memory to high. Contents of B serve as a count of bytes remaining

to be transferred.

OTOR ED BB 2 20/15 I 7 7 ? 1 Repeat until [BI = 0:

[[C])-[[HL])

[BI-IBJ -,

[ HLI - I HU - ,

Transfer a block of data from memory location addressed by con-

tents of Hl to I/O port addressed by contents of C. going from high

memory to low. Contents of B serve as a count of bytes remaining

to be transferred.

.. Address Bus: AO-A7; (C)

AS-A15: [B)

Table 3-4. A Summary of the zao Instruction Set (Continued)

w

N

C1l

Clock

Status

Type Mnemonic Operand Object Code Bytes

Cycles

Operation Performed

C Z S PIO

AC N

OUli ED A3 2 15 X ? 7 7 1 [[ClI - [[HLlJ

[Bl- [BI- 1

[HLJ - [HLl + 1

'ii

Transfer a byte of data from memory location addressed by con-

tents of Hl to 1/0 port addressed by contents of C. Decrement byte :::I

c

....

count and increment source address.

c

0

OUTD ED AB 2 15 X 7 7 7 1 [[C)]-[(HL)]

H

[B]- [Bl - 1

g

[HLl-[HLl-1

Transfer a byte of data from memory location addressed by con-

tents of HL to 110 port addressed by contents of C. Decrement both

byte count and source address.

LD A,(addd 3A ppqq 3 13 [Al- [addrl

load Accumulator from directly addressed memory location.

LD HL,(addd 2A ppqq 3 16 [ HI - [ addr + 1l. [ Ll - [ addrl

load Hl from directly addressed memory.

LD rp,laddd ED 01xx1011 ppqq 4 20 [ rplHIlJ - I addr + 1l. [ rpllOI) - [ addrl or

xy,(addrl 1hl11012Appqq 20 [ xy(HIl] - [ addr + 1L [xy(LOII - [ addrl

u

4

c

Load register pair or Index register from directly addressed memo-

...

ry. a

II:

LD laddd,A 32 ppqq 3 13 [addrl- [AI

>-

Ii

Store Accumulator contents in directly addressed memory location.

E

II LD !addd,HL 22 ppqq 3 16 [ addr + 1] - [Hl. [addrl - ( L]

~

Store contents of Hl to directly addressed memory location.

>-

..

LD laddrl,rp ED 01xxOOll ppqq 4 20 [ addr + 1] - [rp(HIlI. [addrl - [ rplLO)] or II

,

(addd,xy 1hl1101 22 ppqq 4 20 [ addr + 11 - [ xy(HIIl. [addr] - [ xy(lOll

.t

Store contents of register pair or Index register to directly ad-

dressed memory.

LD A,IBC) OA 1 7 [ Al - [[ BC]l or [ Al - [[ DEli

A,IDEI 1A 1 7 load Accumulator from memory location addressed by the con-

tents of the specified register pair.

Co)

I

!'oJ

(J)

Table 3-4. A Summary of the zao Instruction Set (Continued)

Clock

Status

Type Mnemonic Operand Object Code Byte.

Cycle.

Operation Performed

C Z S PIO A

C

N

LD reg.(HU 01ddd110 1 7 I reg] - I[ HLII

to

Load register from memory location addressed by contents of HL.

...

LD (Bel,A 02 1 II BClI - I Alar [[ DEll - [ A) ~ 7

!

(DEl,A 12 1 7 Store Accumulator to memory location addressed by the contents to

'0_

of the specified register pair.

11:-0

>

LD (HLl,reg 01110sss 1 7 [I HLII - I reg)

6 . ~

E .. Store register contents to memory location addressed by the con-

.~

tents of HL.

~ ~

~

LD reg.(xy+disp 11x1110101ddd110 3 19 [ reg] - [[ xy] + disp]

'"

disp Load register from memory location using base relative addressing.

E

~

LD xy +displ,reg 11x1110101110sss 3 19 [[ xy] + displ - I reg]

disp Store register to memory location addressed relative to contents of

Index regi ster.

LDIR ED BO 2 20116 0 0 0 Repeat until [ BCl ~ 0:

[[ DEll - [[ HLl]

I DEI - I DEI + 1

I HLI - I HLl + 1

~

[ BC] - [ BC] - 1

!!

'"

Transfer a block of data from the memory location addressed by

III

the contents of HL to the memory location addressed by the con-

-0

~

tents of DE. going from low addresses to high. Contents of BC

'"

0-

serve as a count of bytes to be transferred.

-!

LDDR ED B8 2 20/16 0 0 0 Repeat until [ BC] = 0:

~

~

I[ DEll - [[ HLl]

~ I DEl - [ DE) - 1

u

IHLl-IHLl-1

0

iii

[ BC] - [BCl - 1

Transfer a block of data from the memory location addressed by

the contents of HL to the memory location addressed by the con-

tents of DE. going from high addresses to low. Contents of BC

serve as a count of bytes to be transferred.

Co)

I

N

.....

Table 3-4. A Summary of the Z80 Instruction Set (Continued)

Clock

Status

Type Mnemonic Operand Object Code Bytes Operation Performed

Cycles

C Z S PIO

AC N

LDI EO AO 2 16 X 0 0 [[ DEll [[ HLlI

[ DEl [DEI + 1

[ HLI [HLI + 1

[ BCI [ BCI - 1

Transfer one byte of data from the memory location addressed by

the contents of HL to the memory location addressed by the con-

tents of DE. Increment source and destination eddresses and decre-

ment byte count.

LDD ED AS 2 16 X 0 0 [[ DEll

'ii [ DE] - [ DEI - 1

:l

[ BCI [ BCI - 1

c

0

Transfer one byte of data from the memory location addressed by

.t:. Ihe conlents of HL to Ihe memory location addressed by the con-

l,)

Iii tents of DE. Decrement source and destination addresses and byte

II)

count.

'C

CPIR ED B1 2 20/16" X X X X Repeat until [AI =[[ HLll or [ BCI =0: c: 1

II

I A] - [[ HLll (only flags are affected)

.!

.. [ HLI [HLI + 1

c:

l! [ BCI [BCI - 1

I-

Compare contents of Accumulator with those of memory block ad-

'"

u

dressed by contents of HL. going from low addresses to high. Stop

.S!

III

when a match is found or when the byte count becomes zero.

CPDR ED B9 2 20/16" X X X X 1 Repeat until [AI =[[ HLll or [ BCI =0:

[A] - [[ HLlI (only flags are affected)

[ HLl [ HLI - 1

IBCI 1

Compare contents of Accumulator with those of memory block ad-

dressed by contents of HL. going from high addresses to low. Stop

when a match is found or when the byte count becomes zero.

CtJ

I

N

CD

Table 3-4. A Summary of the lSO Instruction Set (Continued)

Clock

Stetus

Type Mnemonic Operand Object Code Byte.

Cycles

Operation Performed

C Z S PIO

AC

N

CPI ED Al 2 16 X X X X 1 rAl - II HLIl (onlV flags are affected)

[ HLl - [HLl + 1

..,- I BC) - ! Bel - 1

t: '0

~

Compare contents of Accumulator with those of memory location

~ t:

.-

addresslid bv contllnts of HL. Increment addrllss and dllcrement ....

t: C 0 byte count.

! ! ~

".r.

CPO ED A9 2 16 X X X X 1 I Al - [[ HLII (onlV flags are affectedI

~ u

[ HL] - [HLl - 1 u ~

o - .

[ BCI - [ BCI - 1

CIIU1

Compare contents of Accumulator with those of memory location

addressed bV contents of HL. Decrement address and byte count

ADD A.(HLI 86 1 7 X X X 0 X D [ Al - [AI + II HLlI or [ Al - ( Al + [( xvI + disp]

A.(xV +disp) l1xll101 86 disp 3 19

.

Add to Accumulator using implied addressing or base relative ad-

dressing.

ADC A.IHLI 8E 1 7 X X X 0 X 0 [ Al - [AJ + II HLlJ + C or [ AI - ( Al + [[ xvi + disp! + C

A,(xV +disp) l1xl11018Edisp 3 19 Add with Carry using implied addressing or base relative address-

u ing.

t:

i

SUB IHLI 96 1 7 X X X 0 X I I Al - rAI - II HLlI Or I Al - [ AI - [( xvI + displ

(XV + disp) l1xl1101 96 disp 3 19 Subtract from Accumulator using implied addressing or base rela-

IZ:

tive addressing.

~

SBC A.IHLI 9E 1 7 X X X 0 X 1 I Al - [ Al - [I i'lL]) - C or [ Al ~ [A] II xvi + disp] - C

0

e

A,(xV+disp) llxl11D19Edisp 3 19 SUbtract with Carry using implied addressing or base relative ad-

:! dressing.

>-

AND IHLI A6 1 7 0 X X P 1 0 [ Al - I Al A [[ HLlI or ( Al ~ [AI A [[ xvi + displ

lii

'0

(XV + d i s p ~ l1xl1101 A6 disp 3 19 AND with Accumulator using implied addressing or base relative e:

0

addressing. u

UI

OR (HL) 86 1 7 0 X X

...

I 0 rAl - [ Al V II HLlJ or [AI ~ [ Al V rr xyJ + disp!

(XV + displ l1x11101 B6 disp 3 19 OR with Accumulator using implied addressing or base relative ad-

dressing.

ff

~

Table 3-4. A Summary of the Z80 Instruction Set (Continued)

Clock

Statu.

Type Mnemonic Operend Object Code Byte.

Cycle.

Operation Performed

C Z S P/O

AC N

XOR IHU AE 1 7 0 :,( X P 1 0 I A] - I AI :!J-II HlJl or ( Al - I Al :!J- [[ xy] + displ

>-'ii (XV + disp) 1h1 1101 AE disp 3 19 Exclusive-OR with Accumulator usin9 implied addressing or base

.. .

relative addressing.

o :I

E .=

..

CP (HU BE 1 7 X X X 0 X 1 [ Al - [[ HlJl or [ Al - [[ XV) + disp]

::i S

>-y

(XV + disp) 11x11101 BE disp 3 19 Compare with Accumulator using implied addressing or base rela-

..

tive addressing. Onlv the flags are affected.

" ... c c

INC (HU 34 1 11 X X 0 X 0 II Hlll -II HlJl + 1 or II XV] + disp) - II xy) + disp) + 1

o

u ..

(xy + disp) 11x1110134disp 3 23 Increment using implied addressing or base relative addressing.

Ul';

DEC (HU 35 1 11 X X 0 X 1 [[ Hlll - II HLII - 1 or II xvI + disp] - [( XV) + disp] - 1 II:

(XV + disp) 11x1110135disp 3 23 Decrement using implied addressing or base relative addressing.

&y

7 oj:] RlC (HU CB 06 2 15 X X X P 0 0

~

(XV + disp) 11x11101 CB disp 4 23

II Hlll or [[ XV] + displ

06 Rotate contents of memory location (implied or base relative address-

ing) left with branch Carry

..

LEJ..

oJ:]

..

I7

0

II:

Rl (Hll CB 16 2 15 X X X P 0 0 ..

"

c

(xy + disp) 11x11101 CBdisp 4 23

II Hl)J or [I xvI + disp]

::

16

:c Rotate contents of memory location left through Carry.

Ul

>-

lj

.. o ~

Ii

E

RRC (Hll CB OE 2 15 X X X P 0 0 7

::i

{XV + disp} 11xl1101 CB disp 4 23

[( Hl)J or [( XV] + dispJ

OE

Rotate contents of memory location right with branch Carry.

W

I

W

o

Table 3-4. A Summary of the laO Instruction Set (Continued)

Clock

Statu.

Type Mnemonic Operlnd Object Code Bytes

Cyc'e.

Operation Performed

C 2 S P/O AC N

l:f7

EJJ

o f

RR IHLI CB1E 2 15 X X X P 0 0 ~

Ixy + displ lhlll0l CBdisp 4 23

[[ HLlI or [[ xv1 + disp]

IE

Rolale conlenls of memory location right through Carry

SLA (HLI CB 26 2 15 X X X P 0 0

EJ.. I7

-4 O ~ O

'i;

(XV + disp) lhlll0l CB disp 4 23 II

::I [[ HLll or [[ xvI + disp]

.5

26

IShift contenlS of memory location lefl and clear LSB !Arithmelic ;:

0

g

Shift)

:l

.:l

o I 0

SRA (HLI CB 2E 2 15 X X X P 0 0 7 .- C

II:

I

...

(XV + disp) 1hll101 CB disp 4 23

c

[( HLlI or [( XV] + disp)

co

:: 2E

:E

I/)

>- Shift contents of memory location right and preserlle MSB

;;

E

(Arithmetic Shift).

II

~

SAL (HLl CB 3E 2 15 X X X

p

0 0

o -.J 7 ... 0 I

-8

(xV + disp) llxll101 CBdisp 4 23

[( HLlJ or I[ xvI + disp)

3E

Shift contents of memory location right and clear MSB (logical Shift)

W

I

W

Table 3-4. A Summary of the zao Instruction Set (Continued)

Clock

Status

Type Mnemonic Operand Object Code Bytes

Cycles

Operation Performed

C Z S PIO A

C

N

LD reg.data OOdddllO VV 2 1 [reg] -data

load immediate into register.

..

LD rp.data16 OOxxOOOl yyyy 3 10 (rp) - datal 6 or [xy] - datal 6 01

'ij

xv.data16 1hlll0l 21 Vyyy 4 14 load 16 bits of immediate data into register pair or Index register.

E

lD (HLI.data 36 yy 2 10 II HLl] - data or [[ xy] + disp] - data

E

-

(xy+ displ. 1h11l01 36 disp VY 4 19 load immediate into memory location using implied or base relative

data addressing

JP label C3 ppqq 3 10 .

I PC) -label

a.

Jump to instruction at address represented by label.

E JR disp 18Idisp-2) 2 12 I PC] - I PCI + 2 + (disp-2)

:::I

Jump relative to p ~ e s e n t contents of Program Counter.

..,

JP (HLI E9 1 4 I PC] - I HLI or [PC) - I XV]

(xy) 1hlll01 E9 2 8 Jump to address contained in Hl or Index register.

CAll label CD ppqq 3 17 [[SP] -l)-[PCIHU]

II SP) - 2) - [ PC(lOI]

[ SP] - [SP] - 2

c:

[PCl -label

..

Jump to subroutine starting at address represented by label. :::I

..

CAll cond.label 11 cccl 00 ppqq 3 10/17 Jump to subroutine if condition is satisfied; otherwise. continue in

a:

"

sequence.

c:

III

RET C9 1 10 [ PCILO)) - I[ SPJI

..

[PCIH1lJ - [[ SP] + 1]

0

[ SP] - I SPJ + 2

. ~

Return from subroutine.

S

~

RET cond 11 cccOOO 1 5/11 Return from subroutine if condition is satisfied; otherwise. continue

:::I

in sequence.

ell

c.>

I

to)

N

Table 3-4. A Summary of the laO Instruction Set (Continued)

Clock

Status

Type Mnemonic Operand Object Code Bytes

Cycles

Operation Performed

C Z S PIO A

C

N

ADD A,data C6 yy 2 7 X X X 0 X 0 ( Al ~ I A] + data

Add immediate to Accumulator.

ADC A,data CE yy 2 7 X X X 0 X 0 { Al ~ I A] + data + C

Add immediate with Carry,

SUB data 06 yy 2 7 X X X 0 X 1 [ A] - I A] - data

I>

...

Subtract immediate from Accumulator .

~

SBC 0 X [ A] ~ I A] - data - C I> A,data DE yy 2 7 X X X 1

a.

0

Subtract immediate with Carry.

I>

[ A] ~ I A] A data

...

AND data E6 yy 2 7 0 X X P 1 0

:s

AND immediate with Accumulator

I>

E

OR data F6 yy 2 7 0 X X P 1 0 [ A] ~ { A] V data

.5

OR immediate with Accumulator.

XOR data EE yy 2 7 0 X X P 1 0 [A] ~ I A] -Odata

Exclusive-OR immediate with Accumulator.

CP data FE yy 2 7 X X X 0 X 1 [AI - data

Compare immediate data with Accumulator contents; only the

flags are affected.

JP cond,label 11 cccO10 ppqq 3 10 If cond, then I PCI ~ label

Jump to instruction at address represented by label if the condition

is true.

JR C,disp 38 (disp-21 2 7/12 If C = 1, then (PCI ~ (PC) + 2 + (disp - 2)

c

Jump relative to contents of Program Counter if Carry flag is set.

:8

:s

JR NC,disp 30 (disp-21 2 7/12 If C =0, then (PC) - (PC) + 2 + Idisp -2)

c

Jump relative to contents of Program Counter if Carry flag is reset.

0

0

JR Z,disp 28 (disp-2) 2 7/12 If Z = 1, then I PCI ~ [PCl + 2 + (disp -2)

c

0

Jump relative to contents of Program Counter if Zero flag is set.

a.

E JR NZ,disp 20 (disp-2) 2 7/12 If Z = O. then I PCI ~ [PC] + 2 + (disp -2)

:::l

... Jump relative to contents of Program Counter if Zero flag is reset.

DJNZ disp 10 {disp-2l 2 8/13 IB] ~ ( B I - 1

If [B] ." 0, then (PC] + 2 + (disp -21

Decrement contents of B and Jump relative to contents of Program

Counter if result is not O.

W

I

W

W

Table 3-4. A Summary of the zao Instruction Set (Continued)

Clock

Status

Type Mnemonic Operand Object Code Bytes Operation Performed

Cycles

C Z S P/O A

c

N

lD dstsrc 01 dddsss 1 4 [ dstl - [ srcl

Move contents of source register to destination register. Register

designations src and dst may each be A, B, C, 0, E, H or L.

LD A,I ED 57 2 9 X X I 0 0 [AJ-II]

Move contents of Interrupt Vector register to Accumulator.

LD A,R ED SF 2 9 X X I 0 0 [AI-[R)

Move contents of Refresh register to Accumulator.

LD I,A ED 47 2 9 [Il-[A)

Load Interrupt Vector register from Accumulator.

LD R,A ED 4F 2 9 [R)-[A]

Load Refresh register from Accumulator.

LD SP,HL F9 1 6 [SP)- [HLl

..

Move contents of HL to Stack Pointer. >

0

:E LD SP.xy 11x11101 F9 2 10 [SP]- [xy]

;; Move contents of Index register to Stack Pointer.

..

EX OE,HL EB 1 4 [DEI- ~ [HLl

'iii

..

Exchange contents of DE and HL,

~

EX AF,AF' 08 1 4 [ AF] - ~ [ AF'I

..

..

Exchange program status and alternate program status.

..

'iii

.. EXX 09 1 4

CBC) CBC')

Cl:

[DEl - ~ [ DE'l

[ HLl [HL')

Exchange register pairs and alternate register pairs.

Co)

I

Co)

~

Table 3-4. A Summary of the laO Instruction Set (Continued)

Clock

Status

Type Mnemonic Operand Object Code Bytes

Cycles

Operation Performed

C Z 5 PIO AC

N

ADD A.reg 10000rrr 1 4 X X X 0 X 0 l AI - [AI + [reg]

Add contents of register to Accumulator.

AOC A.reg 10001 rrr 1 4 X X X 0 X 0 [ AI - [AI + [ reg] + C

Add contents of register and Carry to Accumulator.

SUB reg 10010", 1 4 X X X 0 X 1 [ AI - [ AI - [ reg]

Subtract contents of register from Accumulator.

SBC A.reg 10011", 1 4 X X X 0 X 1 [ AI - [ Al - [ reg] - C

Subtract contents of register and Carry from Accumulator.

AND reg 10000rrr 1 4 0 X X P 1 0 [ Al - [AI A [ regl

AND contents of register with contents of Accumulator.

OR reg 10110rrr 1 4 0 X X P 1 0 [ Al - [ AI V [ reg]

..

OR contents of register with contents of Accumulator.

..

XOR reg 10101", 1 4 0 X X P 1 0 [A] - [AI--[ reg]

hclusive-OR contents of register with contents of Accumulator.

Q.

0

CP reg 10111rrr 1 4 X X X 0 X 1 [A] - [reg]

..

! Compare contents of register with contents of Accumulator. Only

..

'0. the flags are affected.

..

~

ADD HL.rp 00nl00l 1 11 X

}

0 [ HLl - [ HLl + [rpl

16-bit add register pair contents to contents of Hl.

..

..

ADC HL.rp [ HLl - [ HLl + [rp] + C

'0. ED Olxxl0l0 2 15 X X X 0

}

0

..

16-bit add with Carry register pair contents to contents of HL. a:

SBC HL.rp ED Olxx0010 2 15 X X X 0

}

1 [ HLl - [ HLl - [rp] - C

16-bit subtract with Carry register pair contents from contents of

HL.

ADD IX.pp DO 00xxl00l 2 15 X ? 0 [ IX] - [ IX) + [ pp]

16-bit add register pair contents to contents of Index register IX

(pp ~ BC. DE. IX, SPI

ADD IV." FD 00nl00l 2 15 X ? 0 [ IV] - [ IV] + [ rrl

1B-bit add register pair contents to contents of Index register IV

(n ~ BC. DE. IV. SPI

Co)

,

Co)

U1

Table 3-4. A Summary of the zao Instruction Set (Continued)

Clock

5t.tu.

Type Mnemonic Operand Object Code Byte. Oper.tion Performed

Cycle.

C Z 5 PIO AC

N

DAA 27 1 4 X X X P X Decimal adjust Accumulator, assuming that Accumulator contents are

the sum or difference of BCD operands.

CPL 2F 1 4 1 1 [A)-[AJ

II

Complement Accumulator (ones complement).

..

NEG ED 44 2 8 X X X 0 X

,

[A)-[AJ +' II

..

II

Negate Accumulator (twos complement).

a.

0

INC OOm'OO 1 4 X X 0 X 0 [ regl - [ reg] + 1

reg

.. Increment register contents.

II

'iiI

INC rp OOxxOO'1 1 6 ( rpJ - [ rp) + , or [ XV] - ( XV) + ,

II

II:

xy '1xlll0l 23 2 10 Increment contents of register or Index register.

DEC reg OUrrr101

,

4 X X 0 X 1 ! reg] - [ reg) - 1

Decrement register contents.

DEC rp 00xx10'1 1 6 [rp] - [rpl - , or! xVJ - [xy] - ,

xv llxl11012B 2 10 Decrement contents of register pair or Index register.

&y7 op

RLCA 07 1 4 X 0 0 4

II

[A]

..

Rotate Accumulator left with branch Carry.

..

..

0

II:

LE]4

oj:] ""

I7

c

RLA 17 1 4 X 0 0

..

:::

:c [AJ

qj

i

Rotate Accumulator left through Carry

..

II

q7 o ~

'co

II

II:

RRCA OF 1 4 X 0 0 ...

[AJ

Rotate Accumulator right with branch Carry.

W

I

Co)

0)

Table 3-4. A Summary of the zao Instruction Set (Continued)

Clock

Statu.

Type Mnemonic Operand Object Code Byte.

-

Operation Performed

Cycle.

C Z S Ip/O

"c

N

l:f7

:J

oI

RRA IF 1 4 X 0 0 ..

(AJ

'Rotate Accumulator right through Carry.

&y

17

of:J

RlC reg CB OOOOOrrr 2 8 X X X P 0 0 ..

~ I [ reg]

IRotate contents of register left with branch Carry. ~

c

;::

L].

oiJ

g

t7

9

CB 00010rrr 2 B X X X P 0 0

Rl reg

..

~

0 [ reg]

II:

'I::J Rotate contents of register left through Carry,

c

l:j7

O ~

i:

.l:

RRC reg C8 o o 1 rrr 2 8 X X X P 0 0

C/)

..

..

[ reg)

'a.

Rotate contents of register right with branch Carry.

II:

l:j7

oI

.E}J RR reg CB 0001 1m 2 8 X X X p 0 0 ...

[ reg!

Rotate contents of register right through Carry.

SlA reg CB 00100rrr 2 8 X X X P 0 0

El-

I7

...

o J.- 0

[reg]

Shift contents of register left and clear lSB (Arithmetic ShiftJ.

W

I

W

.....

Table 3-4. A Summary of the laO Instruction Set (Continued)

Clock

Statu.

Type Mnemonic Operand Object Code Byte.

Cycle.

Operation Performed

C Z S PIO

Ac

N

Cj

o I

"0

SRA reg CB 00101rrr 2 8 X X X P 0 0 ...

[ reg]

Shift contents of register right and preserve MSB (Arithmetic Shift).

SRL reg CB 00111rrr 2 8 X X X P 0 0 0

-.1

7

...

o I

--EJ

;;

[ reg]

Shift contents of register right and clear MSB (Logical Shiftl.

:::I

c:

;::

I

c:

0

tJ

-

I 7 4 I 3 o I I 7 4 I 3 o I

RLD ED 6F 2 18 X X P 0 0

..

..

I

~

0 [Al

a::

'tl

c:

:::

Rotate one BCD digit left between the Accumulator and memory loca-

:c

tion (implied addressingl.Contents of the upper half of the Accumula-

III

a

tor are not affected.

J I

I

RRD ED 67 2 18 X X P 0 0

I 7 4 I 3 o I I 7 4 I 3 o I

[AI

[[ HLlJ I

Rotate one BCD digit right between the Accumulator and memory

location (implied addressingl.Contents of the upper half of the Ac-

cumulator are not affected.

to)

I

(0)

co

Table 3-4. A Summary of the zao Instruction Set (Continuedl

Clock

Statu.

Type Mnemonic Operand Object Code Byte.

Cycle.

Operation Performed

C Z S PIO

Ac

N

BIT b,reg CB 01bbbrrr 2 8 X ? ? 1 0 Z - reglbl

Zero flag contains complement of the selected register bit.

BIT b.IHlI CB 01bbbllO 2 12 X ? ? 1 0 Z - [[ HLlJlbl or Z - [[ xvI + displlb)

b.(xV" disp) 1lx11101 CB disp 4 20 Zero flag contains complement of selected bit of the memory loca-

e:

01bbb110 tion (implied addressing or base relative addressing).

.g

SET b.reg CB 11 bbbrrr 2 8 reglbl - 1

.!

Set indicated register bit.

:::l

a.

SET b.(HU CB 11bbb1 10 2 15 [( HLlJlb) - 1 or [[ XV] + dispJlb) - 1

'i:

II

b.lxV +disp) 1h11101 CB disp 4 23 Set indicated bit of memory location (implied addressing or

~

..

11bbb110

base relative addressing/.

iii

RES b.reg CB 10bbbrrr 2 8 reg(b) - 0

Reset indicated register bit.

RES b.(HU CB 10bbbll0 2 15 [[ HLlJlbl - 0 or [[ XV] + dispJlbl - 0

b.(xV + displ 1lx11 101 CB disp 4 23 Reset indicated bit in memory location limplied addressing or base

10bbb110 relative addressing).

PUSH pr 1'u0101 1 11 ([ SP]-ll - [ pdHIIl

xv 1h11101 E5 2 15 (( SPl-21- [ pr(LOl]

[ SP)- [ SPl-2

Put contents of register pair or Index register on top of Stack and

decrement Stack Pointer.

POP pr lhxOO01 1 10 [ pr(LOll - [[ SPII

.;0: xv 1h11101 E1 2 14 [ pr(HIlI - [[ SPI + 1I

u

[ SP] - [SP] + 2 II

..

(/)

Put contents of top of Stack in register pair or Index register and

increment Stack Pointer.

EX ISPl.HL E3 1 19 [ HI - - [[ SP] + 1]

(SPl,xv llxlllOl E3 2 23 [Ll -- [[ SPII

Exchange contents of HL or Index register and top of Stack.

CAl

,

CAl

CD

Table 3-4. A Summary of the zao Instruction Set (Continued)

Status

Type Mnemonic Operand Object Code Bytes

Clock

Operetion Performed

Cycles

C Z S P/O

Ac

N

01 F3 1 4 DiSable interrupts,

EI FB 1 4 Enable interrupts.

RST n 1lxxx1 11 1 11 [[ SP)-1] - [PCIHIIl

[[ SP)-2J - [ PCILOI)

..

[ SP] - [ SPI-2

a.

[PCl -18.nl,6

i

Restart at designated location.

S

RETI ED 40 2 14 Return from interrupt.

RETN ED 45 2 14 Return from nonmaskable interrupt.

1M 0 ED 46 2 B Set interrupt mode O. 1. or 2.

1 ED 56 2 B

2 ED 5E 2 B

SCF 37 1 4 1 0 0 C-1

Set Carry flag.

a

II CCF 3F 1 4 X ? 0 C-C

et)

Complement Carry flag.

NOP 00 1 4 No operation - volatile memories are refreshed,

HALT 76 1 4 CPU halts. executes NOPs to refresh volatile memories.

"Execution time shown is for one iteration.

Table 3-5. Instruction Object Codes in Numerical Order

OBJECT CODE INSTRUCTION

00 NOP

01 yyyy LD BC.data16

02 LD (BCl.A

03 INC BC

04

INC B

05

DEC B

06 VV

LD B,data

07 RLCA

08 EX Af.AF

09 ADD HL,BC

OA LD A,lBC)

OB DEC BC

DC INC C

DO DEC C

OEvv

LO C,data

OF RRCA

10 disp-2 OJNZ disp

II yyyy Lo oE,data16

12 LO (DEI,A

13 INC DE

14 INC 0

15

DEC 0

16 vv

to o,data

17 RLA

18 disp-2 JR disp

19 ADD HL,OE

lA LD A,(OE)

18 DEC DE

lC INC E

10 DEC E

IE vv

LO E,data

1f RRA

20 disp-2 JR NZ,disp

21 yyyy LO HL,datal

22 ppqq LO (addr),HL

23 INC HL

24 INC H

25 DEC H

26 vv LO H,data

27 OM

28 disp-2 JR Z,disp

29 ADO HUiL

2A ppqq LO HL,laddr)

28 DEC HL

2C INC L

20 DEC L

2E LO L,data

2f CPL

30 disp-2 JR NC,disp

31 yyyy LO SP,data16

32 ppqq LO (addrl,A

33 INC SP

34 INC (HU

35 DEC iHU

36 vv LO (HU,data

37 SCF

38 JR C.disp

OBJECT CODE INSTRUCTION

39 ADO HL,SP

3A ppqq LO A,laddr)

38 DEC SP

3C INC A

3D DEC A

3E vv LD A,data

3F CCf

4 Osss LO B,reg

46 LO B,(HLJ

4 lsss LO C,reg

4E LO C,(HU

5 Osss LD O,reg

56 LO O,(HLJ

5 lsss LO E,reg

5E LO E.lHU

6 Osss LO H.reg

66 LO H.lHU

6 lsss LO L,reg

6E LO L,(HU

7 Osss LO IHU,reg

76 HALT

7 lsss LO A,reg

7E LO A,(HU

80m ADD A,reg

86 ADD A,(HLI

8 1m ADC A,reg

8E AOC A,{HLl

90m SUB reg

96 SU8 (HU

9 lrrr sac A,reg

9E SBC A,{HU

AOm AND reg

A6 AND (HU

A 1m XOR reg

AE XOR (HU

BOrn OR reg

B6 OR (HLI

B 1m CP reg

BE CP (HU

CO RET NZ

Cl

pop

BC

C2 ppqq JP NZ,addt

C3 ppqQ JP addr

C4 ppqQ CALL NZ,addr

C5 PUSH BC

C6 vv ADD A,data

C7 RST OOH

C8 RET Z

C9 RET

CA ppqq JP Z,addr

CB 0 Orr, RLC reg

CB06 RLC (HU

ca 0 1,rr RRC reg

CB Of RRC (HU

CB 1 Orrr RL reg

CB 16 RL {HLI

CB 1 1m RR reg

3-40

Table 3-5. Instruction Object Codes in Numerical Order (Continued)

OBJECT CODE INSTRUCTION

CB IE RR (HU

CB 2 Om SLA reg

CB 26 SLA (HU

CB21m SRA reg

CB 2E SRA (HLI

CB 31m SRL reg

CB 3E SRL (HLI

CB 01bbbm BIT b.reg

CB 01bbbl10 BIT b.IHU

CB IObbbm RES b.reg

CB IObbbl10 RES b.IHU

CB l1bbbm SET b.reg

CB llbbbllO SET b.IHL)

CC PPQq CALL Z,addr

CO PPQq CALL addr

CE yy ADC A,data

CF RST 08H

00 RET NC

01

pop

DE

02 PPQq JP NC,addr

03 yy OUT (portl.A

D4 PPQq CALL NC,addr

05 PUSH DE

Deyy SUB data

07 RST 10H

D8 RET C

09 EXX

DA PPQq JP C,addr

DB yy IN A,(port)

DC ppqq CALL C,addr

DO OOxx 9 ADD IX,pp

DO 21 yyyy LD IX,dllta16

DO 22 PPQq LO (addrl.lX

DO 23 INC IX

DO 2A PPQq Lo IX,(addrl

DO 2B DEC IX

DO 34 disp INC (IX + displ

00 35 disp DEC (IX + diep)

DO 36 disp yy Lo (IX + displ.dlltl

DO 01ddd110 disD LD reg,(lX + diapl

00 I Oass disD Lo (IX + displ.reg

DO S6 disp ADD A,(lX+disp)

DO SE disp ADC A,(IX + diap)

DO 96 disp SUB (IX +disp)

DO 9E disp SBC A'(lX+disp)

DO A8 disp AND (IX + disp)

DO AE disp XOR (IX + displ

DO B6 disp OR (IX + disp)

DO BE disp CP (lX+disp)

00 CB disp 06 RLC (lX+disp)

00 CB disp DE RRC (IX +displ

DO CB disp 16 RL IIX +disp)

DO CB disp 1E RR (IX +diap)

DO CB disp 26 SLA (IX +disp)

DO CB disp 2E SRA (IX +disp)

DO CB disp 3E SRL (lX+displ

DO CB disp 01bbbl 10 BIT b,(lX + displ

OBJECT CODE INSTRUCTION

DO CB disp lObbbl10 RES b.(lX+displ

DO CB disp l1bbb110 SET b,(lX+displ

DO El pop

IX

DO E3 EX (SPI.IX

DO E5 PUSH IX

DO E9 JP (IX)

DO F9 LD SP.IX

DE yy SBC A,data

OF RST ISH

EO RET PO

E1

pop

HL

E2 PPQq JP PO.addr

E3 EX (SP).HL

E4 PPQq CALL PO.addr

E5 PUSH HL

E6 yy AND data

E7 RST 20H

E8 RET PE

E9 JP IHLI

EA PPQq JP PE,addr

EB EX OE,HL

EC ppqq CALL PE,addr

EO 01dddOOO IN reg,(CI

ED 01sss001 OUT (CI.reg

EO 01xx 2 sse HL,rp

EO 01xx 3 ppqq LD (addrl.rp

EO 44 NEG

ED 45 RETN

ED 01Onnl10 1M m

EO 47 LD I.A

ED 01xx A ADC HL,rp

ED 01xx B ppqq LD rp,(addrl

ED 40 RETI

ED 4F Lo R,A

EO 57 Lo A.I

ED 5F Lo A,R

ED 67 RRO

EO 6F RLO

EO AO LDI

ED Al CPl

ED A2 INI

ED A3 OUTI

EO AS LOO

ED A9 CPO

EO AA iND

ED AS OUTO

ED SO LDIR

ED B1 CPlR

ED 82 INIR

ED B3 OTIR

ED 88 LDDR

ED B9 CPOR

EO SA INDR

EO Be OTOR

EE yy XOR dIIta

EF RST 2SH

3-41

ADC A,data - ADD IMMEDIATE WITH CARRY TO

ACCUMULATOR

F

A

B.C

D.E

H.L

SP

PC

IX

IV

I

R

s Z AC Pia N

Data

I

Memory

..

xx

.. '" Program

mmmm mmmm+2

""""-

Memory

CE

I

-

yy

mmmm

mmmm+ 1

mmmm+2

mmmm+ 3

ADC A.

--

CE

data

--

yy

1 010

1 1 00

o

001 1

o1 1 1

Add the contents of the next program memory byte and the Carry status to the Ac-

cumulator.

Suppose xx=3A16. yy=7C16. and Carry=O. After the instruction

ADC A.7CH

has executed. the Accumulator will contain 8616:

3A

7C

Carry

1 sets S to 1

No carry. set C to 0

a.If 1= 1. set P/0 to 1

1011 0110

f.J ,esult set Z to 0

"'-------Carry. set AC to 1

Addition instruction. set N to 0

The ADC instruction is frequently used in multibyte addition for the second and subse-

quent bytes.

3-43

ADC A,reg - ADD REGISTER WITH CARRY TO

ACCUMULATOR

F

A

S.C

D.E

H.L

SP

PC

IX

IV

I

R

SZACP/ON!

i

- ~ ~

~

r,

~ x + v y + c

}-l

xx

contents of

A,B.C,D,E,H

orLisvy

- ~

mmmm mmmm + 1

........

I

I

Data

Memory

Program

Memory

10001xxx mmmm

....__--1mmmm + 1

....__--1mmmm + 2

1-__...... mmmm +3

reg

--

ADC A

-..-

10001 xxx

-.-

000 for reg=B

001 for reg=C

010 for reg=D

011 for reg=E

100 for reg=H

101 for reg=L

111 for reg=A

Add the contents of Register A. B. C. D, E, H or L and the Carry status to the Accumula-

tor.

Suppose xx=E316, Register E contains A016. and Carry=l. After the instruction

ADC AE

has executed, the Accumulator will contain 8416:

E3

AO

Carry

1 1 1 0 001 1

1010 0000

1

1 sets S to 1

Carry. set C to 1

1000 01 00

t

u

LNon.mo ,.sult. Sol Z to 0

,,",-----No carry. set AC to 0

1 1=0, set P/0 to 0 Addition instruction. set N to 0

The ADC instruction is most frequently used in multibyte addition for the second and

subsequent bytes.

3-44

ADC A,(HL) - ADD MEMORY AND CARRY TO

ADC A,(IX+disp) ACCUMULATOR

ADC A,(IY+disp)

S ZAcP/ON C Data

Q

m

mm+l

mmmm+2

~ - - - t mmmm + 3

IxlXIXlxlOIX

Memory

l

- ~ ~

~ X

_ I.,,:,x,+ YV + C

YV PPQ

,

QQ

PP

- ~ V

Program

mmmm ~ m m m + 1

Memory

I BE mmm

I

mm

F

A

B.C

D.E

H.L

SP

PC

IX

IV

I

R

The illustration shows execution of ADC A.(HU:

ADC A(HU

----

8E

Add the contents of memory location (specified by the contents of the HL register pair)

and the Carry status to the Accumu lator

Suppose xx=E316, yy=A016, and Carry=l. After the instruction

ADC A(HU

has executed, the Accumulator will contain 8416:

E3

AO

Carry

1110 0011

1010 0000

1

1 sets S to 1

Carry. set C to 1

1 1=0. set P/O to 0

1000 0100

.fJ LNon,,.,o cesult. set Z to a

~ - - - - No carry, set AC to 0

Addition instruction, set N to 0

ADC A(lX+disp}

~ - . . -

DO BE d

Add the contents of memory location (specified by the sum of the contents of the IX

register and the displacement digit d) and the Carry to the Accumulator

ADC A(lY+disp)

~ - . -

FD BE d

This instruction is identical to ADC A(lX+displ. except that it uses the IY register in-

stead of the IX register

The ADC instruction is most frequently used in multibyte addition for the second and

subsequent bytes.

3-45

ADC HL.rp - ADD REGISTER PAIR WITH CARRY TO HAND L

S Z AC P/O N C

F ~

Data

Memory

A

B.C

D,E

H.L

SP

PC

IX

IY

I

R

Be, DE, HL or SP

:" contain yyyy

xx xx

- ~ x x + y y y y

..""""

+C

mmmm

~

~ m m m + v

I

I

Program

Memory

ED mmmm

01xxl010 mmmm + 1

mmmm+2

t-----t mmmm + 3

K

EDOlxxl010

-..-

00 for rp is register pair BC

01 for rp is register pair DE

10 for rp is register pair HL

11 for rp is Stack Pointer

Add the 16-bit value from either the BC, DE. HL register pair or the Stack Pointer. and

the Carry status, to the HL register pair.

Suppose HL contains A53616, BC contains 104416, and Carry=l. After execution of

ADC HLBC

Addition instruction, set N to 0 011-0=0, set P!O to 0

the HL register pair will cqrtain:

A536 1010{)101 0011 0110

1044 0001 000001000100

Carry 1

1011010101111011

1 sets S tc 1 V t.Ncncmc result. set Z to 0

No carry, set C to 0 1 No carry, set AC to 0

The ADC instruction is most frequently used in multibyte addition for the second and

subsequent bytes.

3-46

:xx+vvr

xx

"

Program

mmmm mmmm + 2

""""'- Memory

I C6

I

.....

YV

ADD A,data - ADD IMMEDIATE TO ACCUMULATOR

5 Z AcP/O N C Data

F(E[E[[IE]]JEJ Memory

to

S,C

D,E

H,L

SP

PC

IX

IY

I

R

mmmm

mmmm+ 1

mmmm+2

mmmm+3

ADD A, data

---..-- -.-

C6 yy

Add the contents of the next program memory byte to the Accumulator,

Suppose xx=3A16. yy=7C16. and Carry=O, After the instruction

ADD A,7CH

has executed. the Accumulator will contain 8616:

3A 001 1 1 01 0

7C = 0 1 1 1 1 1 0 0

101U

110

1 sets S 10 1 t LNon-ze""esu,tset Z to 0

No carry. set C to 0 - Carry. set AC to 1

o 1= 1: set P/0 to 1

This is a routine data manipulation instruction,

3-47

Addition instruction. set N to 0

Data

Memory

Program

Memory

l0000xxx mmmm

mmmm+ 1

t-----1mmmm + 2

mmmm+3

t-----1

..

r.

} 0001..,

xx

H or L is yy

. r 3>

mmmm _ + 1

I

I

F

ADD A.reg - ADD CONTENTS OF REGISTER TO

ACCUMULATOR

S Z Ac P/O N C

A

B,C

D.E

H,L

SP

PC

IX

IY

I

R

ADD reg

-v-" -.-

10000 xxx

000 for reg=B

001 for reg=C

010 for reg""-D

011 for reg=E

100 for reg =H

101 for reg=L

111 for reg=A

Add the contents of Register A. B. C. D. E. H or L to the Accumulator.

Suppose xx=E316. Register E contains A016. After execution of

ADD A.E

Addition instruction. set N to 0

1 sets S to 1

Carry. set C to 1

1 1=0. set PIO to 0

the Accumulator will contain 8316:

E3 1 1 1 0 00 1 1

AO = 1 0 1 0 0 0 0 0

1000 0011

r LNon-wo msull. set Z to a

.....-----No carry. set AC to 0

This is a routine data manipulation instruction

3-48

ADD A.(HL) - ADD MEMORY TO ACCUMULATOR

ADD A. (IX+disp)

ADD A.(lY+disp}

d

m

m+ 1

m +2

m + 3

Data

X X X X 0 X

Memory

-

"""" xx

"" xx+yy

yy ppqq+

-

Program

mmmm mmmm+3

ppqq

I--

........

Memory

I 00 mmm

I 86

mmm

d mmm

mmm

S ZACP/ON C

A

B,C

D,E

H,L

SP

PC

IX

IV

I

R

The illustration shows execution of ADD A,(IX+disp).

ADD A,(IX+disp}

--...-- --

DO 86 d

Add the contents of memory location (specified by the sum of the contents of the IX

register and the displacement digit d) to the contents of the Accumulator

Suppose ppqq=4000 16. xx= 1A16. and memory location 400F16 contains 5016, After

the instruction

Addition instruction. set N to 0 oO=O; set P/O to 0

ADD A(lX+OFH)

has executed. the Accumulator will contain 6A16,

lA = 0001 1010

50 = 0 1 0 1 0 0 0 0

o1 1 0 101 0

o sets S to 0 fJ LNon-,em ,""It. set Z to 0

No carry. set C to 0 . No carry. set AC to 0

ADD A(lY+disp)

FD 86 d

This instruction is identical to ADD A(lX+disp). except that it uses the IY register in-

stead of the IX reg ister.

ADD A(HL)

86

This version of the instruction adds the contents of memory location, specified by the

contents of the HL register pair. to the Accumulator.

The ADD instruction is a routine data manipulation instruction

3-49

ADD HL,rp - ADD REGISTER PAIR TO HAND L

Data

Memory

A

B.C

D.E

H.l

SP

PC

IX

IY

I

R

Be, DE, HL or SP

=t." YVVYv.J

-

-,

xx xx II. xxxx + VYYY

mmmm

-

I

I

Program

Memory

OOxxl001 mmmm

mmmm+ 1

1------1mmmm + 2

mmmm+3

1------1

1K

00 xx 1001

--- 00 for rp is register pair BC

01 for rp is register pair DE

10 for rp is register pair HL

11 for rp is Stack Pointer

Add the 16-bit value from either the BC, DE. HL register pair or the Stack Pointer to the

HL register pair.

Suppose HL contains 034A16 and BC contains 214C16. After the instruction

ADD HLBC

has executed. the HL register pair will contain 249616.

034A 0000 0011 0100 1010

214C = 0010 0001 0100 1100

001aa100 1001 a11 a

No carry. set C to 0....J carry. set AC to a

Addition instruction. set N to a

The ADD HLHL instruction is equivalent to a 16-bit left shift.

3-50

ADD xy,rp - ADD REGISTER PAIR TO INDEX REGISTER

Data

Memory

A

B.C

D.E

H,L

SP

PC

IX

IV

I

R

rr 55

- ~ ~ mmmm mmmm + 2

ppqq t'--.. ..........