Professional Documents

Culture Documents

Cours Motorola

Uploaded by

Mahmoud ReinCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cours Motorola

Uploaded by

Mahmoud ReinCopyright:

Available Formats

1

Structure dun systme microprocesseur

Logique cble :

C`est une technique qui permet de realiser un systeme logique en choisissant les

composants appropries et en adaptant le cblage . La realisation d`un systeme cble

oblige a trouver d`abord une solution theorique au probleme pose. DiIIerentes methodes

permettent d`y parvenir :

- algebre de Boole ;

- tableau de Karnaugh ;

- matrice des etats ;

- diagramme des phases ;

- reseau de Petri ;

A partir de celles-ci, on elabore un schema de principe deIinissant le Ionctionnement du

systeme, puis un schema de cblage.

A partir d`un certain degre de complexite, les realisations des systemes cbles

necessitent l`emploi d`un personnel qualiIie ainsi qu`un temps de realisation important.

De plus, ce genre de systeme est Iige pour une application particuliere et toute

modiIication du systeme impose une modiIication du cblage., voir un changement des

composants.

Les systemes electroniques cbles presentent deux avantages : ils sont tres rapides ;

compacts et peu onereux en materiel.

Logique programme :

Contrairement aux systemes cbles dans lesquels le Ionctionnement est determine par le

cblage, les systemes programmes Ionctionnent independamment du cblage qui reste

toujours le mme. Ils sont determines par une suite d`instructions appelee programme ;

celui-ci peut tre modiIiable en Ionction de l`application.

Il existe divers types de logiques programmees :

- Les calculateurs industriels ;

- Les microsystemes ;

- Les microprocesseurs;

- L`automate programmable.

2

Dans ce cours, nous nous limiterons aux microprocesseurs.

Architecture gnrale dun systme microprocesseur

Un microprocesseur presente peu d`utilite Ionctionnelle par lui-mme. En eIIet, il ne

represente qu`un element du systeme a microprocesseur dont il gere le Ionctionnement.

Il importe donc de savoir comment le systeme est organise et quelles sont les Ionctions

speciIiques assignees a chacun des elements qui le composent.

La Iigure n1 nous montre l`architecture simpliIiee d`un systeme standard a base d`un

microprocesseur.

Nous y distinguons le p, la ROM, la RAM et les PIO.

ROM RAM PIO

p

Port A

Port B

Bus de donnes

Bus dadresse

Bus de contrle

3

Le microprocesseur

Le p est un circuit integre avec lequel on peut realiser des operations tres complexes. Il

remplit les Ionctions d`une unite centrale (CPU, Central Processing Unit) ; il comprend

une unite arithmetique et logique (ALU, Arithmetic and Logic Unit), des registres

internes et une unite de commande (CU, Control Unit).

La ROM

La ROM (Read Only Memory) est la memoire a lecture seule ; elle presente l`avantage

d`tre permanente (son contenu ne disparat pas quand le systeme n`est plus alimente).

Elle contient le programme moniteur pour permettre le Ionctionnement du systeme.

La RAM

La RAM (Random Access Memory) est la memoire a lecture et a ecriture du systeme ;

elle est volatile (son contenu est perdu lorsque l`on coupe l`alimentation). Elle contient :

- Les programmes lors de leur mise au point.

- Les donnees necessaires a l`execution des programmes.

Les dispositifs dentre-sortie

Le systeme comporte un ou plusieurs botiers d`interIace aIin de pouvoir communiquer

avec le monde exterieur. Le botier le plus utilise est l`interIace d`entree-sortie parallele.

Nous y voyons egalement trois bus qui assurent les communications entre le p et

autres elements du systeme :

- Le bus de donnees qui achemine les donnees echangees par les diIIerents elements

du systeme. Le bus de donnees est un bus bidirectionnel (il peut tre utilise dans les

deux sens).

- Le bus d`adresse emane du microprocesseur et transporte des adresses vers tous les

dispositiIs branches sur le bus des donnees. Une adresse envoyee par le p sert a

selectionner un dispositiI ou un registre du dispositiI.

- Le bus de commande transporte les signaux de synchronisation entre le p et tous les

dispositiIs branches sur le bus de donnees. Ces signaux sont generalement les signaux

de lecture, d`ecriture, de remise a zero, d`interruption, .

4

Microprocesseur 89

Prsentation gnrale

Le 6809 est le plus evolue des microprocesseurs a 8 bits de la Iamille Motorola

(6800,6802,6805). Il est dote d`une architecture amelioree qui dispose de plusieurs

registres supplementaires, des nouvelles instructions et des modes d`adressage

supplementaires. Il est compatible avec tous les circuits peripheriques de la Iamille 6800

(PIA 6821, ACIA 6850, .) et il est optimise pour l`execution de programmes en

langages evolues (Pascal, C, Forthran, .).

Le microprocesseur 6809 est Iabrique en technologie MOS a canal N et se presente sous

la Iorme d`un botier DIL 40 broches. On peut l`utiliser avec trois horloges internes :

1 MHz pour le 6809 ; 1,5 MHz pour le 68A09 et 2 MHz pour le 68B09.

Architecture interne du 6809

Le microprocesseur possede 3 bus independants (non multiplexes) :

- Un bus de donnees bidirectionnel de 8 bits,

- Un bus dadresse de 16 bits

- Un bus de controle de 10 bits.

Le bus de donnes achemine les donnees echangees par les diIIerents dispositiIs du

systeme a base du microprocesseur. Pour le 6809, le bus de donnees est un bus

bidirectionnel de 8 bits (il peut tre utilise dans les deux sens). C`est un bus a 3 etats

(logique a trois etats), ce qui lui permet d`tre utilise pour realiser un acces DMA (voir

plus loin).

Le bus d`adresse emane du microprocesseur et transporte des adresses vers tous les

dispositiIs branches sur le bus des donnees. C`est un bus de 16 bits, ce qui permet au

6809 d`adresser un espace memoire de 64 K (2

16

). Une adresse envoyee par le 6809 sert

a selectionner un dispositiI ou un registre du dispositiI.

5

Le bus de commande transporte les signaux de synchronisation entre le 6809 et tous

les dispositiIs branches sur le bus de donnees. Ces signaux sont generalement les

signaux de lecture, d`ecriture, de remise a zero, d`interruption, .

L`unite arithmetique et logique (UAL) contient tous les circuits electroniques qui

realisent eIIectivement les operations desirees. Ces operations sont principalement les

operations arithmetiques (,-,x,.) et les operations logiques (ET, OU , XOR, .).

L`unite de commande s`occupe de gerer l`execution des instructions d`un programme.

Les principaux dispositiIs de l`unite de commande sont :

- Le registre instruction (RI) qui reoit l`instruction qui doit tre executee.

- Le decodeur du code operation, qui determine quelle operation doit tre eIIectuee,

parmi toutes les operations possibles ;

- Le sequenceur qui genere les signaux necessaires a l`execution de chaque instruction

d`un programme. Cette unite a besoin d`une horloge pour enchaner les commandes.

6

Registres internes du 6809

Le microprocesseur 6809 dispose de neuI registres internes accessibles a l`utilisateur

(Iigure n2).

Figure n2

Les registres sont les suivants :

Accumulateurs A,B,D

Le 6809 possede deux accumulateurs independants A et B de longueur 8 bits qui

peuvent tre associes pour constituer un seul accumulateur 16 bits nomme D. Le registre

A constitue l`octet de poids Iort de D, le registre B celui de poids Iaible.

Les accumulateurs A, B, D sont utilises pour les calculs arithmetiques et les

manipulations de donnees.

Registres dindex X et Y

Les registres d`index X et Y sont utilises pour les modes d`adressage indexe lors de

rangement de donnees en memoire sous Iorme de table.

Pointeur de Pile utilisateur U

Accumulateur B

Pointeur de Pile Systme S

Compteur-Programme PC

Registre dindex X

Registre dindex Y

Registre de page DP

Registre dtat CC

Accumulateur A

7

Pointeurs de pile S et U

Le 6809 dispose de deux pointeurs de pile S et U sur 16 bits.

Le pointeur de pile S (hardware Stack Pointer) est utilise par le processeur pour gerer

la sauvegarde de ses registres internes lors des appels des sous-programmes et des

demandes d`interruptions. Il contient une adresse a 16 bits qui pointe le sommet de la

pile. Cette derniere peut tre implantee n`importe ou dans l`espace memoire RAM

adresse par le processeur (voir plus loin).

Le pointeur de pile U (User Stack Pointer) est laisse entierement a la disposition de

l`utilisateur pour transIerer ses propres arguments lors de l`appel des sous programmes.

Les pointeurs de pile S et U peuvent tre utilises comme registres d`index au mme titre

que X et Y.

Compteur programme PC

Le compteur programme PC est un registre a 16 bits qui contient l`adresse de la

prochaine instruction a executer (qu`il Iaut aller chercher en memoire). Il s`incremente

automatiquement a chaque lecture d`un octet en memoire a moins qu`un branchement

ou un saut ne l`oblige a prendre une autre valeur particuliere.

Registre de page DP

Le registre de page DP est un registre a 8 bits. Le 6809 s`en sert pour le mode

d`adressage direct.

Au cous de l`execution d`une instruction en mode d`adressage direct, le registre DP

Iournit l`octet de poids Iort de l`adresse. Celui de poids Iaible suit le code operation de

l`instruction. Ainsi, le programmeur peut explorer une zone memoire de 256 octets sans

changer le contenu du registre DP. Pour atteindre une autre zone, le programmeur doit

redeIinir le registre DP.

Pour rester compatible avec la Iamille 6800, le DP est mis a 0 a l`initialisation du p

(Reset).

8

Registre dtat CCR (Condition Code Register)

Le registre d`etat CCR est un registre a 8 bits qui contient les 8 indicateurs du p. Il

deIinit apres chaque operation arithmetique ou logique l`etat du p et l`aide a prendre

des decisions lors de l`execution des instructions de branchement.

Bit C (Retenue)

L`indicateur de retenue C est positionne a 1 chaque Iois qu`une retenue est generee.

Voici des illustrations :

Exemple : Addition

ADDA #$20 Addition avec retenue du contenu de l`accumulateur A et

de la valeur hexadecimale $20

On suppose que le contenu de A est : $F0

1111 0000

+ 0010 0000

C=1 1 0001 0000

Dans le cas d`une addition, l`indicateur C est la retenue de poids 2

8

.

Retenue

Depassement

Zero

Negatif

Masque dinterruption IRQ

Demi-retenue

Masque dinterruption FIRQ

Etat de Sauvegarde

CCR

9

L`indicateur C est utilise pour realiser des operations arithmetiques sur des nombres

superieurs a 8 bits.

Exemple : soit a eIIectuer N

1

N

2

, N

1

et N

2

etant des nombres de 16 bits.

Le p commence par additionner les deux octets de poids le plus Iaible de N

1

et N

2

(N

1L

et N

2L

), ce qui donne une somme S

L

(octet) et une retenue eventuelle C. On additionne

ensuite les deux octets de poids le plus Iaible N

1H

et N

2H

en tenant compte de la retenue

C. Ceci est automatiquement eIIectue par l`instruction ADC (addition avec retenue).

Bit V (Overflow dbordement en complment 2)

Ce bit est positionne a 1 si le resultat d`une operation arithmetique entre deux nombres

representes en complement a 2 deborde ; c`est a dire si le resultat excede l`intervalle -

128 a 127.

Les instructions de chargement, de stockage et les operations logiques positionnent V a

0.

Bit Z (Zro)

Ce bit est positionne a 1 quand une operation quelconque produit un resultat nul. Il est

mis a 0 dans le cas contraire.

Bit N (Ngative)

Ce bit est signiIicatiI seulement quand le p manipule des nombres signes. Il recopie

l`etat du bit de signe du resultat de l`operation eIIectuee. Quand le resultat est negatiI, le

bit N est positionne a 1 ; si le resultat est positiI, N est positionne a 0.

N1L

N2L

N1H

N2H

10

Bit H (Demi-retenue)

Ce bit n`a de signiIication que quand le p manipule des nombres representes en DCB.

Rappelons qu`en code DCB, on Iait correspondre a chaque chiIIre decimal son

equivalent binaire code sur 4 bits. Il est possible, avec quatre bits, de representer tous

les nombres allant de 0 a 15. Or dans le code DCB, il ne nous est pas permis de depasser

9. Le code DCB n`utilise donc que 10 quartets parmi 16 qui servent a coder les chiIIres

decimaux allant de 0 a 9. Les quartets interdits sont : 1010,1011,1100,1101,1110,1111.

Si l`un des quartets interdits se maniIeste lors d`une addition, il Iaut eIIectuer une

correction en y ajoutant 6(0110)

2

. Cette operation supplementaire s`appelle ajustement

decimal. Ceci est automatiquement eIIectue par l`instruction DAA qui utilise cet

indicateur pour corriger le resultat apres une addition ADDA ou ADCA.

Exemples : 6 + 5

6 0110

5 0101

1010

Le resultat de l`addition 1011 est un quartet interdit. Donc, une correction est

necessaire. On ajoute 6 au resultat, ce qui donnera :

1011

0110

0001 0001

1 1

Le resultat est bien 11.

Bit I (Interrupt Mask Masque dinterruption)

Ce bit, lorsqu`il est a 1, masque l`interruption materielle IRQ. On traitera en detail les

interruptions (Voir Chap. : Les interruptions).

Bit F (Fast Interrupt Mask Masque dinterruption rapide)

Ce bit, lorsqu`il est a 1, masque l`interruption materielle FIRQ. Les deux bits I et F

peuvent tre mis en place par le programmeur a l`aide des instructions de type ANDCC

11

ou ORCC (Voir Chap. : Le Jeu d`Instructions). Ainsi, le p ne tient pas compte des

demandes d`interruption provenant de la ligne correspondante (ou les deux).

Bit E (sauvegarde des registres internes dans la pile)

Quand une demande d`interruption IRQ a lieu, le bit E se positionne a 1. Dans ce cas,

tous les registres internes sont sauvegardes dans la pile.

Quand il s`agit de la demande d`interruption FIRQ, le bit E se positionne a 0. Dans ce

cas, seuls les registres PC et CCR sont sauvegardes dans la pile.

Ainsi, l`indicateur E diIIerencie entre les deux mode d`interruption et indique au p le

nombre de registres a depiler lorsque ce dernier a Iini d`executer le programme

d`interruption.

12

Les modes dadressage

Le 6809 est tres complet au niveau des modes d`adressage. On appelle mode

d`adressage la Iaon dont les instructions accedent aux operandes (donnees situees en

memoire). La plupart des instructions du 6809 supportent plusieurs types d`adressage.

1. Adressage inhrent (ou implicite)

Adressage inhrent simple

Dans le mode d`adressage inherent simple, le code operation contient toute

l`inIormation necessaire a l`execution de l`instruction.

Exemple : CLRA,CLRB,INCA,INCB,LSRA,LSRB

Adressage inhrent paramtr

L`instruction comporte un octet supplementaire qui precise les registres internes

intervenant dans l`instruction.

Exemples :

TFR A,DP transIert de A dans DP

PSHS A,B,X sauvegarde dans la pile de A,B,X

2. Adressage immdiat

Dans ce mode d`adressage, le code operation est suivi directement de l`operande. Ce

type d`adressage permet de charger les registres internes du microprocesseur avec la

valeur de l`operande.

Exemple : registre 8 bits

LDA #$12 charger la valeur $10 dans l`accumulateur A

Le symbole #` signiIie immediat dans la syntaxe assembleur.

Exemple : registre 16 bits

LDX #$E000 charger la valeur $E000 dans le registre d`index X

13

Remarque : le chargement immediat est valable pour tous les registres internes a

l`exception du registre de page DP.

Pour charger la donnee $E0, a titre d`exemple, dans DP :

LDA #$E0

TFR A,DP Transfrer le contenu de A vers DP

3. Adressage direct

Dans ce mode d`adressage, le code operation est suivi des 8 LSB de l`adresse dont les 8

MSB se trouvent dans le registre de page DP. Ce mode d`adressage est utilise pour

adresser des pages en memoire. Le registre DP speciIie le numero de page.

Il suIIit donc d`initialiser le registre de page DP pour pouvoir travailler en adressage

direct sur les 256 octets de la page choisie. A la mise sous tension, DP est mis a zero.

Exemple :

LDA $00 ; charger l`accumulateur A avec le contenu de l`adresse memoire $1000

(On suppose que le contenu de DP est $10).

4. Adressage tendu

Dans ce mode d`adressage, le code operation est suivi les deux octets constituant

l`adresse de l`operande proprement dit.

Exemple :

LDA $E000 charger l`accumulateur A avec le contenu de $E000

5. Adressage tendu indirect

L`operande speciIie non pas la donnee mais l`adresse de cette donnee. On parle

d`indirection. L`assembleur reconnat la presence d`un adressage etendu indirect par

mise entre [ ] de l`adresse operande.

Exemple :

LDA [ $E000] charger l`accumulateur A avec le contenu dont l`adresse se trouve

en $E000 et $E001

14

6. Adressage relatif court

Ce mode d`adressage est utilise par les instructions de branchement qui requierent deux

octets : le premier est le code operation et le second speciIie le deplacement qui peut

tre positiI ou negatiI. On pourra donc se deplacer de 128 ($80) octets en arriere et de

127 ($ 7F) en avant, par rapport a la valeur du compteur ordinal (PC) a la Iin du

traitement de l`instruction de branchement.

Exemple :

Langage machine Langage assembleur

Adresse Contenu Etiquette Code op. Oprande Commentaires

$8000 B6 E0 00 LDA $E000

$8003 47 ASRA

$8004 24 03 BCC PAIR Si la retenue est 0, un branchement est

effectu Ltiquette PAIR. On se dplace

de +3.

$8006 B7 E0 0A STA $E00A

$8009 B7 E0 0B PAIR : STA $E00B

$800C 3F SWI

7. Adressage relatif long

Ce mode d`adressage est reserve lui aussi aux instructions de branchement. Cette Iois,

les instructions sont codees sur 4 octets : Les deux premiers representent le code

operatoire et les deux autres speciIient le deplacement qui peut tre positiI ou negatiI.

On pourra donc se deplacer de 32768 ($8000) octets en arriere et de 32767 ($7FFF)

en avant, par rapport a la valeur du compteur ordinal (PC) a la Iin du traitement de

l`instruction de branchement.

Exemple :

LBCC PAIR ; Si le bit de retenue est a 0, un branchement relatiI long a l`etiquette est alors execute.

15

8. Adressage index

Le principe de l`adressage indexe est que l`instruction speciIie une base (index) plus un

deplacement par rapport a cette base. On peut donc ecrire :

Adresse effective base + dplacement

La base peut tre soit :

- un des deux registres d`index X ou Y;

- un des deux pointeurs de pile U ou S;

- le compteur programme PC (cas particulier de l`adressage relatiI).

Quant au deplacement, il peut tre soit :

- nul;

- code sur 5 bits (-16 a 15);

- code sur 8 bits (-32768 a 32767);

- variable dans le cas de l`utilisation d`un accumulateur A, B ou D.

Adressage index avec dplacement nul :

Ce mode est le mode indexe le plus rapide. Un registre (X,Y,U ou S) contient l`adresse

eIIective de la donnee utilisee par l`instruction. Il existe deux types d`instruction :

Instructions sur deux octets : le premier octet deIinit le code operatoire, le second

designe le post octet (1RR00100).

RR

Registre de base : X 00

Registre de base : Y 01

Registre de base : U 10

Registre de base : S 11

Exemple :

16

Langage machine Langage

assembleur

Adresse Contenu Code op. Operande Commentaires

A6 84 LDA ,X Charger l`accumulateur A avec le contenu dont l`adresse

se trouve dans X

Instructions sur trois octets : le code operatoire est deIini par deux octets. Le troisieme

constitue le post octet

Exemple :

Langage machine Langage

assembleur

Adr

esse

Contenu Code op. Operande Commentaires

10 AE

84

LDY ,X Charger l`accumulateur Y avec le contenu dont

l`adresse Se trouve dans X.

Adressage index avec dplacement constant

Dans le mode d`adressage indexe, le deplacement (en complement a 2) est ajoute au

contenu du registre de base pour Iormer l`adresse eIIective de la donnee. Le contenu

initial du registre de base n`est pas modiIie par l`addition.

1) Dplacement sur 5 bits

Le deplacement sur 5 bits (en complement a 2) est compris dans le post octet

(RRnnnnn), ce qui est avantageux de point de vue place memoire et vitesse

d`execution.

Exemple :

17

Langage machine Langage assembleur

Adresse Contenu Code op. Operande Commentaires

A6 FD LDA $03,X Charger laccu. A par le contenu de ladresse .

(X) 3

2) Dplacement sur 8 bits

Le deplacement sur 8 bits (en complement a 2) est compris dans l`octet suivant le post

octet (1RR1).

Exemple :

Langage machine Langage assembleur

Adresse Contenu Code op. Operande Commentaires

A6 88 14 LDA $20,X Charger laccu. A par le contenu de ladresse .

(X) $20

3) Dplacement sur 16 bits

Le deplacement sur 16 bits, en deux octets, suit immediatement le post octet

(1RR11).

Exemple :

Langage machine Langage assembleur

Adresse Contenu Code op. Oprande Commentaires

A891LDA$1,XChargerl'accu.Aparlecontenudel'adresse:

(X)+$1

AdressageindexAuto-incrmentation/dcrmentation

Cemodeestutilispourgrerunetablededonnes. L'auto-

incrmentation/dcrmentationpermetd'accderrapidementauxdonnessuccessives.

leregistredebasecontientl'adresseeffectivedeladonnedel'instruction.

Danslemodeauto-incrmentation,leregistredebaseestincrmentdeun:+'oude

deux:++'aprslerecherchedel'instructionsuivante.

Danslemodeauto-dcrmentation,leregistredebaseestdcrmentdeun:-'oude

deux:--'avantlerecherchedel'instructionsuivante.

Exemple:

18

Langage machine Langage assembleur

Adresse Contenu Code op. Operande Commentaires

A6 80 LDA ,X charger l`accumulateur A avec le contenu dont l`adresse

se trouve dans X. Incrementation par Un de X.

A6 81 LDA ,X charger l`accumulateur A avec le contenu dont l`adresse

se trouve dans X. Incrementation par deux de X.

A6 82 LDA ,-X charger l`accumulateur A avec le contenu dont l`adresse

se trouve dans X. Decrementation par Un de X.

A6 83 LDA ,--X charger l`accumulateur A avec le contenu dont l`adresse

se trouve dans X. Decrementation par deux de X.

Adressage index avec Dplacement accumulateur ((A,R), (B,R), (D,R))

Ce mode d`adressage est semblable au precedant sauI que cette Iois-ci le deplacement

est contenu dans l`un des accumulateurs A,B ou D du 6809. L`adresse eIIective de la

donnee est la somme du contenu du registre de base et celui de l`accumulateur speciIiee

dans l`instruction. Le contenu initial du registre de base n`est pas modiIie par l`addition.

les instructions sont codees sur 2 octets : le premier represente le code operatoire et le

second speciIie le post octet.

19

Post octet

Accumulateur A 1RR00110

Accumulateur B 1RR00101

Accumulateur D 1RR01011

Exemple :

Langage machine Langage assembleur

Adresse Contenu Code op. Operande Commentaires

A6 85 LDA B,X Charger l`accu. A par le contenu de l`adresse :

(X) (B)

Adressage index avec comme registre de base : Compteur Programme (PC)

Dans ce mode d`adressage, un deplacement en complement a deux de 8 ou 16 bits est

ajoute au contenu du PC pour obtenir l`adresse eIIective de la donnee.

Exemple :

LDA $F0,PC Charger laccu. A par le contenu de ladresse : (PC) +

$F0

20

21

Jeu dinstructions du 6809

On peut classer les instructions du 60809 en six categories principales :

- Instructions de transIert de donnees

- Instructions de traitement de donnees

- Instructions de pointeurs de donnees

- Instructions de tests et branchements

- Instructions d`entrees-sorties

- Instructions de commandes

1. - Instructions de transfert de donnes

Les instructions de transIert de donnees transmettent des donnees entre :

- les registres internes du 6809;

- les registres internes et la memoire;

- les pointeurs.

1.1. Instructions de transfert sur les registres internes

Les instructions EXG et TFR permettent le transIert de donnees entre les registres

internes.

Le transIert ne peut se Iaire que sur des registres de mme taille.

EXG R1,R2 Les contenus des registres R1 et R2 sont echanges.

Exemple : EXG A,DP

TFR R1,R2 Le contenu du registre R1 est transIere dans le registre R2.

Exemple : TFR D,X

1.2. Instructions de transfert sur les registres internes et la mmoire

Les instructions LD (LOAD : charger) et ST (Store : stocker) permettent le transIert

de donnees entre les registres internes et la memoire.

22

Instruction Fonction

LD la donne en mmoire est charge dans le registre spcifie

ST Le contenu du registre interne spcifi dans linstruction est

transfr dans lemplacement mmoire indiqu.

Exemple :

LDA $1000 charger l`accumulateur A avec le contenu de l`adr. $1000

STA $2000 Stocker le contenu de l`Acc. A a l`adresse memoire $2000

1.3. Instructions de transfert sur les pointeurs

Les instructions PUSH (empiler) et PULL (dpiler) permettent le transIert des

registres internes dans la pile en memoire. Les registres a empiler/dpiler sont indiques

dans l`octet (post octet) qui suit immediatement le code operation de l`instruction

PUSH/ PULL. Chaque bit du post octet indique un registre interne

b7 b6 b5 b4 b3 b2 b1 b0

PC U ou S Y X DP B A CC

Ordre d`empilement

Ordre de depilement

Quand un de ces bits vaut 1, le registre correspondant est empile/depile.

Le pointeur de pile speciIie dans l`instruction ne peut tre empile/depile.

Chaque Iois qu`un octet est mis dans une pile, le pointeur de pile est decremente de 1.

Pour un registre de 16 bits, on empile d`abord l`octet de poids Iaible dans la pile. Le

depilement est identique excepte qu`il incremente le pointeur de pile.

23

Instruction Fonction

PSH Empilement de(s) registre(s) dans la pile.

PUL Dpilement de(s) registre(s) de la pile.

Exemple :

PSHS #$FF

24

ssss - C CC

ssss - B A

ssss -A B

ssss - 9 DP

ssss - 8 X-haut

ssss - 7 X-bas

ssss - 6 Y-haut

ssss - 5 Y-bas

ssss - 4 U-haut

ssss - 3 U-bas

ssss - 2 PC-haut

ssss - 1 PC-bas

ssss

2. - Instructions de traitement de donnes

Les instructions de traitement de donnees peuvent tre classees en quatre categories :

25

- les instructions arithmetiques;

- les instructions logiques;

- les instructions de deplacements (rotation et de decalage);

- Les instructions d`incrementation/decrementation, mise a zero,

complementation

2.1. Instructions arithmtiques

Les instructions arithmetiques sont listees dans le tableau suivant :

Instruction Fonction

ADD Addition du contenu mmoire un accumulateur

ADC Addition du contenu mmoire un accumulateur avec retenue

ABX Addition de laccumulateur B X

DAA Ajustement dcimal de lacc. A

MUL Multiplication de A par B (non signe)

SUB Soustraction du contenu mmoire un accumulateur

SBC Soustraction du contenu mmoire un accumulateur avec retenue

SEX Extension de signe de laccu. B lacc. A

2.2. Instructions logiques

Les instructions logiques sont listees dans le tableau suivant :

Instruc

tion

Fonction

AND ET logique entre mmoire et registre interne

EOR XOR entre mmoire et registre interne

OR OU logique entre mmoire et registre interne

26

L`instruction AND est utile pour mettre a 0 ou masquer un ou plusieurs bits dans

un mot. L`instruction XOR est utile pour des comparaisons. On peut l`utiliser aussi pour

complementer un mot (EORA #$FF).

2.3. Instructions de dplacement (rotation et dcalage)

Il Iaut tout d`abord distinguer entre une operation de decalage et une operation de

rotation.

Dans une operation de decalage, tous les bits sont decales d`une position vers la droite

ou vers la gauche. Le bit qui sort du registre va dans le bit de retenue C ; le bit qui entre

est un zero.

Dans une operation de rotation, le bit entrant dans le registre est celui qui provient de la

retenue C.

Instruction Fonction

ASR Dcalage arithmtique droite.

Les bits sont dcals vers la droite. b

0

est transfr vers C et b

7

reste inchang

LSL ou ASL Dcalage logique ou arithmtique gauche.

Les bits sont dcals vers la gauche. b

7

est transfr vers C et b

0

est mis 0.

LSR Dcalage logique droite.

Les bits sont dcals vers la droite. b

0

est transfr vers C et b

7

est mis 0.

ROL Rotation gauche

Les bits subissent une rotation vers la gauche. b

7

est transfr vers C et la valeur

dorigine de celui-ci est transfre vers b

0

.

ROR Rotation droite

Les bits subissent une rotation vers la droite. b

0

est transfr vers C et la valeur

dorigine de celui-ci est transfre vers b

7

.

Exemple :

RORA ; ROLB ; LSRA ; LSRB

2.4. Instructions d`incrmentation/dcrmentation, mise zro, complmentation

27

Ces instructions sont listees dans le tableau suivant :

Instruction Fonction

CLR Remise a 0 du contenu memoire ou de l`accumulateur

DEC Decrementation du contenu memoire ou de l`accumulateur

INC Incrementation du contenu memoire ou de l`accumulateur

COM Complement a 1 du contenu memoire ou de l`accumulateur

NEG Complement a 2 du contenu memoire ou de l`accumulateur

NOP Pas d`operation. Incrementation du compteur programme

3. Instructions de tests et branchement

Les instructions de tests et branchements peuvent tre classees en trois categories :

- les instructions de tests et de comparaison;

- les instructions de test et de branchement;

- les instructions de test et branchement

3.1. Instructions de test et de comparaison

Ces instructions sont utilisees pour realiser des tests de bits d`etat et des

comparaisons aIin de pouvoir prendre des decisions au cours du deroulement d`un

programme dependant de la valeur de ces indicateurs. Seul le registre d`etat est

modiIie ; ni le registre speciIie ni l`operande en memoire ne sont changes. Aucun

branchement n`est eIIectue.

Ces instructions sont listees dans le tableau suivant :

28

Instruction Fonction

BIT Test de bits BITA M , BITB M

L`acc. (A ou B) spcifi et l`oprande en mmoire font l`objet d`un ET logique.

CMP Comparaison d`un contenu mmoire avec un accumulateur CMPA , CMPB

ACCX M

TST Test du contenu mmoire ou d`un accumulateur TSTA , TSTB , TST M

ACCX 0 , M 0

3.2. Instructions de test et branchement

Ces instructions eIIectuent des tests sur 4 indicateurs du registre d`etat (C, N, Z, V)

aIin de realiser des branchements au cours du deroulement d`un programme dependant

de la valeur de ces indicateurs. Deux types de branchement existent :

- Un branchement cours : deplacement entre 128 et 127

- Un branchement long : deplacement entre 32768 et 32767.

Les instructions utilisant un branchement long ont une lettre L` qui precede leurs

mnemoniques.

Ces instructions sont listees dans le tableau suivant :

29

Instruction Fonction

BCC ou BHS Branchement si pas de retenue BCC N ; LBCC NN

Si C=0, alors : PC PC + N (ou) PC PC + NN

BCS ou BLO Branchement si retenue BCS N ; LBCS NN

BEQ Branchement si gal zro

BNE Branchement si diffrent de zro

BGE Branchement si suprieur ou gal zro (sign)

Si (N V)=0 alors : PC PC + N (ou) PC PC + NN

BLT Branchement si infrieur (sign)

BGT Branchement si suprieur (sign)

BLE Branchement si infrieur ou gal (sign)

BHI Branchement si suprieur (non sign)

BLS Branchement si infrieur ou gal (non sign)

BMI Branchement si ngatif

BPL Branchement si positif

BVC Branchement si pas de dbordement

BVS Branchement si dbordement

5. Instructions de traitement des interruptions

Le tableau suivant illustre ces instructions :

30

Instruction Fonction

CWAI Mise zro dindicateurs dtat et attente dinterruption CWAI #N

CC = CC and N. Ceci peut mettre 0 certains bits donc dmasquer les

interruptions.

SYNC Synchronisation avec une ligne dinterruption SYNC

RTI Retour de sous-programme dinterruption RTI

SWI/SWI2/SWI3 Interruptions logicielles

Ltat complet est sauvegard dans la pile systme.

31

Les interruptions

Quand un organe d`entree-sortie a besoin d`un service, il envoie une impulsion sur

la ligne d`interruption du microprocesseur. Ce dernier termine l`instruction en cours,

ensuite il se branche a un sous-programme d`interruption. Ceci entrane la sauvegarde

de l`etat partiel ou total du p.

Pour Iaciliter la comprehension d`une interruption d`un p, imaginez a titre

d`exemple qu`au cours du travail, vous tes appele au telephone ; vous repondez au

telephone en consultant eventuellement d`autres dossiers, puis vous revenez reprendre

votre tche exactement au point ou vous l`aviez laissee.

Une interruption peut survenir a n`importe quel instant par rapport au deroulement

du programme. On dit qu`elle asynchrone au programme.

Interruptions matrielles

Le 6809 possede trois interruptions materielles executables (NMI,IRQ,FIRQ)

pendant le deroulement d`un programme plus une entree d`initialisation (RESET) qui

est traitee comme l`interruption la plus prioritaire du systeme.

Interruption NMI (Interruption Non Masquable)

L`interruption NMI ne peut pas tre masquee par le programmeur. Elle est

employee en cas d`urgence comme par exemple, une deIaillance d`alimentation

(sauvegarde dans une memoire CMOS alimentee par pile). Cette interruption est la plus

prioritaire des interruptions materielles du 6809. Un Iront descendant sur l`entree NMI

provoque une sequence d`interruption non masquable. La Iigure n1 montre les

diIIerentes phases de cette sequence.

L`adresse de depart du sous-programme de traitement de NMI doit tre loge aux

adresses memoires $FFFC : $FFFD (octet haut dans $FFFC, octet bas dans $FFFD)

Lors d`une reconnaissance de NMI, l`etat complet du p est sauvegarde dans la pile

systeme a l`exception du pointeur S. L`instruction de retour d`interruption (RTI) doit

tre executee a la Iin du sous-programme de traitement. Cette instruction extrait le

registre d`etat de la pile systeme. Si le bit E est egal a 1, l`etat complet du p est alors

depile; dans le cas contraire, seuls le PC et le registre d`etat sont depiles.

32

Espace

Mmoire

Contenu de S

CC ssss - C

A ssss - B

B ssss -A

DP ssss - 9

X-haut ssss - 8

X-bas ssss - 7

Y-haut ssss - 6

Y-bas ssss - 5

U-haut ssss - 4

U-bas ssss - 3

PC-haut ssss - 2

PC-bas ssss - 1

ssss

1 : Un front descendant de AMI est pris en compte la fin de l'instruction en cours.

2 : Le processeur positionne le bit E 1 pour indiquer qu'il va faire une sauvegarde totale de l'tat du

89 dans la pile systme.

NMI

1 E

1 I

1 F

Sauvegarde des registres dans la pile Systme

Recherche du vecteur NMI

contenu dans FFFD : FFFC

0 BS

Excution du sous-programme de NMI

0 BA

1 BS

33

3 : 1ous les registres du 89 sont sauvegards partir de l'adresse contenue dans S moins un (ssss -

1) dans l'ordre indiqu la figure.

4 : Les interruptions matrielles sont masques. Les signaux IRQ et FIRQ n'ont plus d'influence.

5 : Le processeur indique l'environnement externe qu'il recherche un vecteur d'interruption

: Le contenu des adresses FFFC et FFFD est pris en compte par le 89

7 : Le fonctionnement redevient normal. Le PC contient l'adresse du sous-programme de AMI.

8 : Le 89 excute le sous programme de AMI

Interruption IRQ (Interruption normale)

L`interruption IRQ est une interruption masquable. Quand une IRQ survient et que le bit

I est a zero (interruption IRQ non masquee), tous les registres internes (excepte S) sont

empiles dans la pile systeme. L`adresse de depart du sous-programme de traitement de

IRQ est cherchee aux emplacements memoires $FFF8 :$FFF9 (octet haut dans $FFF8,

octet bas dans $FFF9).

Le sous-programme de traitement se termine par l`instruction RTI qui depile le registre

d`etat de la pile systeme. Si le bit E est egal a 1, l`etat complet du p est alors depile;

dans le cas contraire, seuls le PC et le registre d`etat sont depiles.

La Iigure suivante montre le sequencement des operations internes du 6809 lors d`une

detection d`un niveau bas sur l`entree IRQ.

34

oui

Espace Mmoire Contenu de S

CC ssss - C

A ssss - B

B ssss -A

DP ssss - 9

X-haut ssss - 8

X-bas ssss - 7

Y-haut ssss - 6

Y-bas ssss - 5

U-haut ssss - 4

U-bas ssss - 3

PC-haut ssss - 2

PC-bas ssss - 1

ssss

IRQ

I = 0

1 I

Sauvegarde des registres dans la pile Systme

1 E

Recherche du vecteur IRQ

contenu dans FFF8 : FFF9

0 BS

Excution du sous-programme de

IRQ

0 BA

1 BS

Continue lexcution

du programme en

cours

35

1 . Un niveau bas sur IRQ est pris en compte a la fin de linstruction en cours.

2 . Le processeur teste le bit I du registre detat. Si I1, linterruption IRQ est masquee, le processeur continue

lexecution du programme. Si I0, le programme est arrtee, le processeur traite linterruption IRQ.

3 . Le bit E a 1 pour indiquer quil va faire une sauvegarde totale de letat du 6809 dans la pile svsteme.

4 . Tous les registres du 6809 (sauf S) sont sauvegardes partir de ladresse contenue dans S.

5 . Les autres interruptions materielles IRQ sont masquees. FIRQ est toufours valide puisque prioritaire sur IRQ.

6 . Le processeur indique a lenvironnement externe (BA0 et BS1) quil recherche un vecteur dinterruption

7 . Le contenu des adresses FFF8 et FFF9 est pris en compte par le 6809

8 . Le fonctionnement redevient normal (BS0) Le PC contient ladresse du sous-programme de IRQ.

9 . Le 6809 execute le sous programme de IRQ

Interruption FIRQ (Interruption rapide)

Le Ionctionnement de l`interruption FIRQ est identique a celui de IRQ sauI qu`elle plus

rapide car elle ne sauvegarde que 3 octets : PC (deux octets) et CCR (1 octet) au lieu de

12. D`ou un gain de temps de neuI cycles d`horloge (1 cycle d`horloge par cycle

sauvegarde). L`interruption FIRQ est plus prioritaire que IRQ. Quand une FIRQ

survient et que le bit F est a zero (interruption FIRQ non masquee), seuls PC et CCR

sont empiles dans la pile systeme. L`adresse de depart du sous-programme de traitement

de FIRQ est cherchee aux emplacements memoires $FFF6 :$FFF7 (octet haut dans

$FFF6, octet bas dans $FFF7).

L`instruction RTI restaure le registre d`etat et le PC du programme interrompu.

La Iigure n montre le sequencement des operations internes du 6809 lors d`une

detection d`un niveau bas sur l`entree FIRQ.

36

oui

Espace

Mmoire

Contenu de S

CC ssss - 3

PC-haut ssss - 2

PC-bas ssss - 1

ssss

1 : Un niveau bas sur FIRQ est pris en compte la fin de l'instruction en cours.

FIRQ

F = 0

1 I 1 F

Sauvegarde des PC et CCR dans la pile Systme

0 E

Recherche du vecteur FIRQ

contenu dans FFF6 : FFF7

0 BS

Excution du sous-programme de

FIRQ

0 BA

1 BS

Continue lexcution

du programme en

cours

37

2 : Le processeur teste le bit F du registre d'tat. Si F1, l'interruption FIRQ est masque, le

processeur continue l'excution du programme. Si F, le programme est arrte, le processeur traite

l'interruption IRQ.

3 : Le bit E pour indiquer qu'il va faire une sauvegarde partielle de l'tat du 89 (PC,CCR) dans

la pile systme.

4 : Le compteur programme PC et le registre CCR sont sauvegards partir de l'adresse contenue

dans S.

5 : Les autres interruptions matrielles sont masques.

: Le processeur indique l'environnement externe (BA et BS1) qu'il recherche un vecteur

d'interruption

7 : Le contenu des adresses FFF et FFF7 est pris en compte par le 89

8 : Le fonctionnement redevient normal (BS) Le PC contient l'adresse du sous-programme de

FIRQ.

9 : Le 89 excute le sous programme de FIRQ

Interruptions logicielles

Mise a part les interruptions materielles, le 6809 possede des interruptions

logicielles qui viennent du programme lui mme. Ces interruptions servent a arrter le

programme, executer le programme instruction par instruction, lecture ou ecriture sur un

organe peripherique ...

Le 6809 possede 3 interruptions logicielles : SWI, SWI2, SWI3

Interruption SWI (Software Interrupt)

L`interruption SWI provoque l`arrt due l`execution d`un programme. La Iigure

suivante montre le sequencement des operations internes du 6809 lors de l`execution de

l`instruction SWI.

38

Espace

Mmoire

Contenu de

S

CC ssss - C

A ssss - B

B ssss -A

DP ssss - 9

X-haut ssss - 8

X-bas ssss - 7

Y-haut ssss - 6

Y-bas ssss - 5

U-haut ssss - 4

U-bas ssss - 3

PC-haut ssss - 2

PC-bas ssss - 1

ssss

1 . SWI entraine larrt du programme en cours.

2 . Le processeur positionne le bit E a 1 pour indiquer quil va faire une sauvegarde totale de letat du

6809 dans la pile svsteme.

3 . Tous les registres du 6809 dans la pile

4 . Les interruptions materielles IRQ et FIRQ sont masquees.

5 . Le processeur indique a lenvironnement externe quil recherche un vecteur dinterruption

6 . Le contenu des adresses FFFA et FFFB est pris en compte par le 6809

7 . Le fonctionnement redevient normal. Le PC contient ladresse du sous-programme de SWI

8 . Le 6809 execute le sous programme de SWI

Interruption SWI2/SWI3 (Software Interrupt)

SWI

1 E

1 I

1 F

Sauvegarde des registres internes dans la pile Systme

Recherche du vecteur NMI

contenu dans FFFA : FFFB

0 BS

Excution du sous programme de SWI

0 BA

1 BS

39

Les interruptions SWI2/SWI3 sont les moins prioritaires. Elles ont un Ionctionnement

identique a SWI. La Iigure n montre le sequencement des operations internes du 6809

lors de l`execution de l`instruction SWI.

40

Espace

Mmoire

Contenu de S

CC ssss - C

A ssss - B

B ssss -A

DP ssss - 9

X-haut ssss - 8

X-bas ssss - 7

Y-haut ssss - 6

Y-bas ssss - 5

U-haut ssss - 4

U-bas ssss - 3

PC-haut ssss - 2

PC-bas ssss - 1

ssss

SWI2

1 E

1 I 1 F

Sauvegarde des registres internes dans la pile Systme

Recherche du vecteur SWI2

contenu dans FFF5 : FFF4

0 BA

1 BS

0 BS

SWI3

Recherche du vecteur SWI3

contenu dans FFF3 : FFF2

Excution du sous

programme de SWI2

Excution du sous

programme de SWI3

41

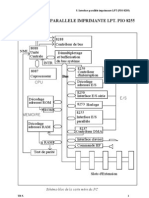

Interface d'entres-sorties parallles : PIA 821

PIA vient de Peripheral-Interface Adapter (Adaptateur d'Interface de priphrique).

Le PIA 821 est un dispositif programmable qui permet de raliser la liaison parallle

entre le 89 et ses priphriques. Il communique au p par l'intermdiaire du bus de

donnes, du bus d'adresse et du bus de contrle. Il communique avec les

priphriques par deux ports 8 bidirectionnels et quatre lignes de contrle qui

assurent la synchronisation des transferts (figure n1).

Figure n1

Mmoire

PIA

680X

Port A (8 bits)

Port B (8 bits)

Bus de

donnes

Bus

dadresse

Bus de

contrle

Contrle

A

Contrle

B

Priphriques :

- imprimante

- CAN/CNA

- Relais

- Claviers

- ..

42

Structure interne du PIA 6821

La structure interne du PIA est donnee en Iigure n2. Le PIA est divisee en deux parties

A et B independantes ayant strictement les mmes caracteristiques. Chacune des parties

dispose d`un port 8 bits bidirectionnels et deux lignes de contrle ainsi que trois

registres internes de 8 bits :

Registre de sortie (ORA,ORB : Output Register)

Ces registres, accessibles en lecture et ecriture, permettent de memoriser les donnees

destinees a la sortie. Les donnees destinees a l`entree sur les ports ont prises en compte

par une lecture du registre ORA ou ORB mais ne sont pas memorisees dans ces

derniers.

Registre de direction des donnes (DDRA,DDRB : Data Direction Register)

Chaque ligne du port A ou B peut tre programmee individuellement en entree ou en

sortie. Pour cela, chaque port dispose d`un registre de direction des donnees. Un 0 dans

un bit du registre de direction indique une entree. Un 1 speciIie une sortie. Ainsi, apres

initialisation (RESET) ou tous les registres sont mis normalement a 0, toutes les lignes

d`entree-sortie du PIA sont programmees en entrees.

Registre de contrle (CRA,CRB : Control Register)

Ces deux registres oIIrent un certain nombre de modes de Ionctionnement. On donnera

par la suite une description complete de ces possibilites.

43

Structure externe du PIA 6821

Liaisons avec le microprocesseur

Bus de donnes D0-D7 : Les lignes D0-D7 sont directement liees au bus de donnees du

p . Elles permettent le transIert de donnees entre le p et le PIA. Ces lignes sont dans

l`etat haute impedance` si elles ne sont pas utilisees.

Bus d`adresse :

CS0,CS1,CS2 : ces trois entrees permettent de selectionner le botier PIA. Celui-ci est

selectionne si :

CS0,CS1,CS2 sont generalement des fonctions booleennes des entrees A

2

-A

15

.

RS0,RS1 : ces deux lignes en liaison avec un bit du registre de contrle interne

(CRA2,CRB2) permettent de selectionner l`un des six registres internes du PIA.

Generalement RS0 est liee au Iil d`adresse A

0

et RS1 au Iil d`adresse A

1

.

Port A Port B CA1 CA2 CB2 CB1

Bus de

donnes

Slection

de

registres

IRQA IRQB

ORA

DDRA

CRA

ORB

DDRB

CRB

0 1 1

2

1 0

. . . . = CS CS CS

44

Signal de validation E : ce signal permet la synchronisation des echanges. Cette entree

correspond a la sortie E du 6809.

Lecture-Ecriture R/W : ce signal est produit par le p pour contrler le sens de

transfert de donnes sur le bus de donnes.

RESET (Initialisation du PIA) : un tat bas sur cette entre met tous les registres

internes du PIA .

IRQA et IRQB : ces sorties, si elles sont reliees a IRQ, FIRQ ou NMI du p,

permettent d`interrompre l`execution d`un programme pour traiter un sous-programme

speciIique au peripherique ayant active IRQA ou IRQB.

Liaisons avec la priphrie

Le PIA s`interIace avec les circuits peripheriques par deux ports bidirectionnels de 8

bits et quatre lignes de contrle.

PA0-PA7 : ces huit broches permettent de transmettre ou de recevoir une donnee de 8

bits. Chacune de ces lignes programmables peut tre utilisee soit comme une entree ou

une sortie. Ceci est Iait par l`intermediaire du registre DDRA.

PB0-PB7 : mmes possibilites de programmation PA0-PA7 selon le registre DDRB.

Entres de demande d`interruption CA1-CB1 : ces entrees permettent de positionner

les indicateurs d`interruption des registres de contrle (CRA7-CRB7). Elles peuvent

tre activees par des Ironts montants ou descendants selon le contenu des registre de

contrle correspondant.

CA2-CB2 : ces lignes bidirectionnelles peuvent tre programmees en entree ou en sortie

dans un mode deIini par les bits 3,4 et 5 du registre de contrle correspondant.

En sortie, ces lignes servent au dialogue avec la peripherie. En entree, elles permettent

de positionner les indicateurs d`interruption des registres de contrle (CRA6-CRB6).

45

CS0

CS1

/CS2

RS0

RS1

RS2

R/W

E

RESET

IRQB

D0-D7

PA0-PA7

PB0-PB7

CA1

CA2

CB1

CB2

IRQA

Ampli.

Bus de

Donnes

Registre

dentre

du bus

Slect.

de

Botier

Slect.

De

registres

Registre

de

Contrle A

(CRA)

Registre

de

Sortie A

(ORA)

Registre

de

Sortie B

(ORB)

Registre

de

Contrle B

(CRB)

Contrle

Dinterrup.

Port A

Registre de

Sens de

transfert

(DDRA)

Interface

Avec la

Priphrie

Port A

Interface

Avec la

Priphrie

Port B

Registre

de

Sens de

transfert

(DDRB)

Contrle

Dinterrup

.Port B

46

Fonctionnement du PIA

Slection des registres internes

Le PIA occupe 4 octets en memoire pour les registres internes. Les registres CRA et

CRB sont accessibles directement par le 6809, l`acces aux quatre autres registres tient

compte de l`etat du CRA2 ou CRB2. Le tableau suivant resume l`adressage des registres

internes du PIA.

B

u

s

A

1

5

L

o

g

i

q

u

e

.

.

.

D

e

A

2

D

e

c

o

d

a

g

e

A

1

A

0

D

a

d

r

e

s

s

e

P

I

A

C

S

0

C

S

1

C

S

2

R

S

1

R

S

0

C

R

A

2

C

R

B

2

A

d

r

e

s

s

e

s

R C

R

A

1 1 0 0 1 X X A

d

r

.

47

1

E A D

D

R

A

1 1 0 0 0 0 X A

d

r

.

G O

R

A

1 1 0 0 0 1 X A

d

r

.

I C

R

B

1 1 0 1 1 X X A

d

r

.

3

S B D

D

R

B

1 1 0 1 0 X 0 A

d

r

.

2

T

.

O

R

B

1 1 0 1 0 X 1 A

d

r

.

2

48

1ableau n1 : Slection des registres internes

Les lignes A2-A15 sont reliees a une logique de decodage qui determine l`adresse de

base du PIA (Adr.).

ORA,DDRA : Adr.

CRA : Adr.+1

ORB,DDRB : Adr.+2

CRB : Adr.+3

Registres de contrle CRA et CRB

b

7

b

6

b

5

b

4

b

3

b

2

b

1

b

0

I

R

Q

A

1

I

R

Q

A

2

C

o

n

t

r

l

e

C

A

2

A

c

c

s

D

D

R

A

C

o

n

t

r

l

e

C

A

1

b

7

b

6

b

5

b

4

b

3

b

2

b

1

b

0

I

R

Q

B

1

I

R

Q

B

2

C

o

n

t

r

l

e

C

B

2

A

c

c

s

D

D

R

B

C

o

n

t

r

l

e

C

B

1

49

a) Contrle des lignes CA1 et CB1

Les bits CRA0 et CRB0 sont utilises pour valider les lignes de demande d`interruption

CA1 et CB1. Les bits CRA1 et CRB1 determinent la transition active des entrees CA1

et CB1 (tableau n2).

C

R

A

1

(

C

R

B

1

)

C

R

A

0

(

C

R

B

0

)

C

A

1

(

C

B

1

)

Drap

eau

dint

erru

ption

CRA

7

CRB

7)

Demande

dinterruption

IRQA (IRQB)

0 0

A

c

t

i

f

Mise

a 1

au

de

CA1

(CB1

)

Non validee. IRQA

(IRQB) toufours a1

0 1

A

c

t

i

f

Mise

a 1

au

de

CA1

(CB1

)

Mise a 0 si le

drapeau

dinterruption

CRA7(CRB7) est

mis a 1

1 0

A

c

t

i

f

Mise

a 1

au

de

CA1

(CB1

)

Non validee. IRQA

(IRQB) toufours a1

1 1

Mise Mise a 0 si le

50

A

c

t

i

f

a 1

au

de

CA1

(CB1

)

drapeau

dinterruption

CRA7(CRB7) est

mis a 1

1ableau n2 : contrle des lignes CA1 et CB1

Remarques :

- le drapeau d`interruption CRA7 (CRB7) est mis a 0 au cours d`un cycle de lecture CPU du registre

de sortie ORA (ORB).

- Si un Iront actiI est appliquee sur CA1 (CB1) alors que la demande d`interruption est non validee

(CRA00 ou CRB00), la ligne CPU IRQA (IRQB) sera activee au moment ou, par logiciel, on

mettra le bit CRA0 (CRB0) a l`etat 1.

b) CRX2

Le bit CRX2 (XA ou B) est associe aux lignes d`adresse RS0 et RS1 pour acceder aux

registres DDRX (CRX20) et ORX (CRX21) (voir tableau n1).

c) Contrle des lignes CA2 et CB2

Le bit CRX5 (XA ou B) deIinit le sens de Ionctionnement de la ligne CX2.

- CRX50 mode entree (interruption)

- CRX51 mode sortie (contrle)

c.1.) Mode entre (CRX50)

CA2 et CB2 sont alors des lignes de demande d`interruption. Les bits CRA3 et CRB3

sont utilises pour valider les demandes d`interruption IRQA et IRQB.

Les bits CRA4 et CRB1 determinent la transition active des entrees de demande

d`interruption CA2 et CB2 (tableau n3).

C

R

A

4

(

C

R

A

3

(

C

A

2

(

Drap

eau

dint

erru

ption

Demande

dinterruption

IRQA (IRQB)

51

C

R

B

4

)

C

R

B

3

)

C

B

2

)

CRA

6

(CR

B6)

0 0

A

c

t

i

f

Mise

a 1

au

de

CA2

(CB2

)

Non validee. IRQA

(IRQB) toufours a1

0 1

A

c

t

i

f

Mise

a 1

au

de

CA2

(CB2

)

Mise a 0 si le

drapeau

dinterruption

CRA6 (CRB6) est

mis a 1

1 0

A

c

t

i

f

Mise

a 1

au

de

CA2

(CB2

)

Non validee. IRQA

(IRQB) toufours a1

1 1

A

c

t

i

f

Mise

a 1

au

de

CA2

(CB2

)

Mise a 0 si le

drapeau

dinterruption

CRA6 (CRB6) est

mis a 1

1ableau n3 : contrle des lignes CA2 et CB2

Remarques :

- le drapeau d`interruption CRA6 (CRB6) est mis a 0 au cours d`un cycle de lecture CPU du registre

de sortie ORA (ORB).

52

- Si un Iront actiI est appliquee sur CA2 (CB2) alors que la demande d`interruption est non validee

(CRA30 ou CRB30), la ligne CPU IRQA (IRQB) sera activee au moment ou, par logiciel, on

mettra le bit CRA3 (CRB3) a l`etat 1.

c.1.) Mode sortie (CRX51)

Deux sous-modes de Ionctionnement sont possibles :

- CRX41 mode programme

- CRX40 mode dialogue

Mode programme (CRX41)

Les lignes CA2 ou CB2 prennent letat du bit 3 du registre de controle correspondant

(CRA3 ou CRB3). Les lignes CX2 sont donc des sorties dont letat est modifie par

logiciel au mme titre que les ports A ou B programmes en sortie.

Mode dialogue (CRX40)

Dans ce mode, il est necessaire de programmer le port A en entree et le port B en

sortie. Le port A permet d`acquerir l`inIormation Iournie par le peripherique et le port B

permet au CPU de repondre.

AIin de rythmer les echanges :

- CA2 indique au peripherique que la donnee appliquee sur le port A a ete lue par le

CPU.

- CB2 indique au peripherique que le CPU vient d`ecrire une nouvelle donnee dans le

registre se sortie du port B.

- Le bit CRX3 deIinit le type de reponse des sorties CA2 et CB2.

CRX30 CX2 reste a l`etat actiI (0) jusqu`a ce que le peripherique ait repondu en

activant une entree de demande d`interruption (CA1 ou CB1).

- CRX31 reponse de type impulsion.

CX2 ne reste a l`etat actiI (0) que pendant une periode CPU quelque soit

la reponse du peripherique.

Contrle de CA2 en sortie (CRA51) en mode dialogue (CRA40)

C

R

A

5

C

R

A

4

C

R

A

3

CA2

Mis a 0

Mis a 1

53

1 0 0 Au Iront de

la 1ere

impulsion E qui

suit un cycle

CPU d`ecriture

dans ORA

Quand le drapeau

d`interruption

CRA7 est mis a 1

par action sur

l`entree CA1

1 0 1 Au Iront de

la 1ere

impulsion E qui

suit un cycle

CPU d`ecriture

dans ORA

Au premier de

E lorsque le PIA

n`est pas

selectionne par le

CPU

Contrle de CB2 en sortie (CRB51) en mode dialogue (CRB40)

C

R

B

5

C

R

B

4

C

R

B

3

CB2

Mis a 0

Mis a 1

1 0 0 Au Iront de

la 1ere

impulsion E qui

suit un cycle

CPU d`ecriture

dans ORB

Quand le drapeau

d`interruption

CRB7 est mis a 1

par action sur

l`entree CB1

1 0 1 Au Iront de

la 1ere

impulsion E qui

suit un cycle

CPU d`ecriture

dans ORB

Au 2eme de E

lorsque le PIA

n`est pas

selectionne par le

CPU

54

Programmation d'un PIA 821

- Charger le registre de commande par la valeur approprie. Ce chargement

s'effectue en principe une fois seulement au dbut du programme.

- Charger le registre de direction pour spcifier dans quelle direction on dsire utiliser

les lignes d'entre-sortie..

- A ce stade, la configuration est dfinie et il est donc prt tre utilis. On teste le

contenu du registre de commande pour dterminer l'tat du dispositif.

- Le CPU lit les donnes en provenance du dispositif.

On peut prsent rpter les phases 3 et 4 indfiniment.

-

55

Interface srie programmable : ACIA 85

L`ACIA est l`interIace serie asynchrone entre le 6809 et ses peripheriques (clavier serie,

imprimante serie, modem, terminal de visualisation, teletype, ...).

L`ACIA communique au p par l`intermediaire :

- du bus de donnees (8 bits),

- du bus d`adresse (4 lignes),

- du bus de contrle.

Les echanges avec la peripherie se Iont par :

- une ligne de transmission de donnees : TxData,

- une ligne de reception de donnees : RxData,

- 3 lignes de contrle paripherique/modem.

Figure n1

Mmoire

ACIA

6850

680X

Bus de

donnes

Bus

dadresse

Bus de

contrle

Transmission

Reception

Priphriques :

- imprimante

- Clavier

- Modem

- Teletvpe

- ..

Contrle

56

Structure interne de lACIA 6850

La structure interne de l`ACIA est donnee en Iigure n2. Le PIA comprend

essentiellement quatre registres dont deux a ecriture seule et deux a lecture seule :

Registre de contrle (CR : Controm Register)

Ce registre, accessible seulement en ecriture, contient les parametres de Ionctionnement

en transmission et en reception. On donnera par la suite une description complete de ces

possibilites.

Registre de transmission de donnes (1DR : 1ransmit Data Register)

Ce registre, accessible seulement en ecriture, contient le mot a emettre.

Registre de rception de donnes (RDR : Receive Data Register)

Ce registre, accessible seulement en lecture, reoit le mot en provenance de la

peripherie.

Registre d'tat (SR : Statut Register)

Ce registre, a lecture seule, contient le mot d`etat qui renseigne le p sur les operations

en cours.

TDR

CR

SR

RDR

Transmission

Reception

Controle

Horloge de transmission

Horloge de reception

IRQ

CS0

CS1

CS2

RS

D0-D7

R/W

E

TxD

RTS

CTS

DCD

RxD

57

Structure externe du LACIA 6850

Liaisons avec le microprocesseur

Bus de donnes D0-D7

Les lignes D0-D7 sont directement liees au bus de donnees du p . Elles permettent le

transIert de donnees entre le p et l`ACIA. Ces lignes sont dans l`etat haute

impedance` si elles ne sont pas utilisees.

Slection du botier CS0,CS1,CS2 (Chip Select)

Ces trois entrees permettent de selectionner le botier ACIA. Celui-ci est selectionne

si :

CS0,CS1,CS2 sont generalement des fonctions booleennes des entrees A

0

-A

15

.

Slection des registres RS (Register Select)

Cette ligne en liaison avec le signal R/W permet de selectionner l`un des quatre registres

internes de l`ACIA. Un niveau haut pour selectionner les registres de transmission ou de

reception et un niveau bas pour selectionner les registres de contrle ou d`etat.

Generalement RS0 est liee au Iil d`adresse A

0

. Le signal R/W est utilise avec le signal

RS pour selectionner, dans chaque paire, le registre a lecture seule ou le registre a

ecriture seule.

Signal de validation E

Ce signal permet la synchronisation des echanges. Cette entree correspond a la sortie E

du 6809.

0 1 1

2

1 0

. . . . = CS CS CS

58

Lecture-Ecriture R/W

Ce signal est produit par le p pour contrler le sens de transIert de donnees sur le bus

de donnees.

Demande d`interruption IRQ

Ccette sortie, si elle est reliee a IRQ ; FIRQ ou NMI du p, permet d`interrompre

l`execution d`un programme pour traiter un sous-programme speciIique au peripherique

ayant active IRQ. Le bit IRQ du registre d`etat, quand il est a un, indique que la sortie

IRQ est active.

Liaisons avec la priphrie

Lignes de transIert :

- TxD (ligne de transmission de donnees) : cette sortie assure la transmission des

donnees en serie.

- RxD (ligne de reception de donnees) : cette entree receptionne les donnees serie en

provenance de la peripherie.

Lignes de contrle d`un peripherique ou d`un modem

L`ACIA comprend plusieurs Ionctions qui permettent le contrle d`un peripherique ou

d`un modem. Ces Ionctions sont inhibition de l`emission (CTS : Clear To Send),

demande d`emission (RTS : Request To Send), perte de la porteuse de donnees (DCD :

Data Carrier Detect).

Demande d'mission R1S (Request 1o Send)

Cette sortie permet au p d`interroger le Modem (ou le peripherique) pour savoir s`il est

prt a recevoir les donnees transmises par l`ACIA. Le Modem repond generalement par

l`activation de l`entree CTS.

Inhibition de l'metteur C1S (Clear 1o Send)

Cette entree permet le contrle automatique de la Iin de transmission par un modem.

Non utilisee, elle doit tre au niveau bas.

59

Perte de la porteuse de donnes DCD (Data Carrier Detect)

Cette entree permet le contrle du recepteur de donnees par un modem. Elle est utilisee

par le Modem pour indiquer au p que les donnees reues sont Iausses a cause d`une

perte de la porteuse. Non utilisee, elle doit tre au niveau bas.

Lignes horloges :

- Txclk (horloge de transmission)

Cette entree sert pour rythmer la cadence de transmission. Les donnees sont transmises

sur le Iront descendant de cette horloge.

- Rxclk (horloge de reception)

Cette entree sert pour rythmer la cadence de reception. Les donnees sont prises en

compte sur le Iront montant de l`horloge.

60

CS0

CS1

/CS2

RS0

RS1

RS2

R/W

E

RESET

IRQB

D0-D7

PA0-PA7

PB0-PB7

CA1

CA2

CB1

CB2

IRQA

Ampli.

Bus de

Donnes

Registre

dentre

du bus

Slect.

de

Botier

Slect.

De

registres

Registre

de

Contrle A

(CRA)

Registre

de

Sortie A

(ORA)

Registre

de

Sortie B

(ORB)

Registre

de

Contrle B

(CRB)

Contrle

Dinterrup.

Port A

Registre de

Sens de

transfert

(DDRA)

Interface

Avec la

Priphrie

Port A

Interface

Avec la

Priphrie

Port B

Registre

de

Sens de

transfert

(DDRB)

Contrle

Dinterrup

.Port B

61

Fonctionnement de l'ACIA

Le diagramme Ionctionnel de l`ACIA (Iigure n3) nous montre le rle des diIIerents

registres accessibles a l`utilisateur.

a) 1ransmission

La sequence de transmission commence par la lecture du registre d`etat de l`ACIA soit

apres une interruption soit pendant une boucle de test. Un caractere peut tre ecrit dans

le registre de transmission si la lecture du registre d`etat indique que le registre de

transmission est vide (bit TDRE a 1). Le caractere est transIere dans un registre a

decalage puis il est transmis en serie, par la ligne TxD, precede par un bit START et

suivi de un ou deux bits STOP. Un bit de parite (paire ou impaire)peut tre

optionnellement ajoute au caractere et sera transmis entre le dernier bit de donnee et le

premier bit STOP. Apres l`ecriture du premier caractere dans le registre de transmission,

le registre d`etat peut tre lu a nouveau pour tester le bit TDRE, indiquant si le registre

de transmission est vide ou non, et l`etat courant du peripherique. Si le registre est vide,

un autre caractere peut tre ecrit mme si le premier caractere est en cours de

transmission (grce au double registre). Le second caractere sera automatiquement

transIere dans le registre a decalage, pour tre transmis, quand la transmission du

premier caractere sera termine.

b) Rception

Les donnees de la peripherie sont reues en serie par l`entree reception de

donnees (RxD). La sequence de reception commence par la lecture du registre d`etat de

l`ACIA pour tester si un caractere a ete reu. Si le registre de reception est plein (bit

RDRF a un), il peut tre lu par le p. Quand l`ACIA Ionctionne sur des mots de 8 bits

comprenant un bit de parite, le bit de parite n`est pas transIere dans le p ; ainsi seule la

donnee est lue par le p. Ceci Iacilite la programmation du p. La sequence continue

par une nouvelle lecture du registre d`etat pour determiner quand un nouveau caractere

sera disponible dans le registre de reception. Le recepteur a aussi un double registre de

sorte qu`un caractere peut tre lu dans le registre de donnees tandis qu`un autre est

transmis dans le registre a decalage. Cette sequence continue jusqu`a ce que tous les

caracteres soient reus.

62

Slection des registres internes

L`ACIA occupe 2 octets en memoire pour les registres internes. l`acces aux quatre

registres tient compte de l`etat du signal R/W. Le tableau suivant resume l`adressage des

registres internes de l`ACIA

B

u

s

C

P

U

A

1

5

L

o

g

i

q

u

e

.

.

.

D

e

A

1

D

e

c

o

d

a

g

e

A

0

R

/

W

A

C

I

A

C

S

0

C

S

1

C

S

2

R

S

0

R

/

W

A

d

r

e

s

s

e

s

C

R

1 1 0 0 0 A

d

r

.

R

e

g

i

S

R

1 1 0 0 1 A

d

r

.

63

s

t

r

e

s

T

D

R

1 1 0 1 0 A

d

r

.

1

R

D

R

1 1 0 1 1 A

d

r

.

1

1ableau n1 : Slection des registres internes

Les lignes A

2

-A

15

sont reliees a une logique de decodage qui determine l`adresse de

base de l`ACIA (Adr.).

CR/SR : Adr.

TDR/RDR : Adr.+1

Programmation de l'ACIA

La programmation se Iait par l`ecriture d`un mot de commande dans le registre de

commande apres un Master Reset` prealable qui se Iait en ecrivant 03 dans le registre

de commande.

64

a) Master Reset

La combinaison CR0.CR11.1 etant utilisee pour l`initialisation programmee du

registre de contrle (MASTER RESET). L`ACIA ne possede pas une broche RESET

permettant une initialisation hardware.

LDA #$03 ; Master Reset

STA CR

b) Ecriture du mot de commande dans le registre de commande

L`ACIA est utilise en emission et/ou en reception. Le mot de commande permet de

deIinir le nombre de bits utiles, le nombre de bits STOP, la presence ou l`absence d`un

contrle de parite ou imparite, la validation ou non d`un mode interruptible (IRQ), la

valeur du Iacteur du rythme. Le mot de commande est determine a partir du tableau de

la Iigure n.

Registre de contrle CR

C

R

7

C

R

6

C

R

5

C

R

4

C

R

3

C

R

2

C

R

1

C

R

0

Le registre de contrle de l'ACIA est un registre de 8 bits criture seule,

qui est slectionn quand RS et R/W. Ce registre contrle le

fonctionnement du rcepteur et du transmetteur, les autorisations

d'interruption et la sortie R1S de contrle du priphrique ou du Modem.

Bits de slection du rapport de division (CR et CR1)

Ces deux bits permettent d`indiquer le rapport de division, pour l`emetteur et le

recepteur, entre la Irequence d`horloge et la Irequence de transIert serie des donnees. De

plus, ces deux bits peuvent tre utilises pour l`initialisation programmee de l`ACIA.

Les fonctions de ces bits sont les suivantes :

C

R

1

C

R

0

Co

ntr

ole

en

65

tra

ns

mis

sio

n

et

en

rec

ept

ion

0 0 1/1

0 1 1/1

6

1 0 1/6

4

1 1 M

ast

er

Re

set

Bits de slection du format des mots (CR2,CR3 et CR4)

Ces trois bits determinent le Iormat du mot transmis (ou reu) : longueur du mot, parite,

nombre de bits STOP. Les Iormats possibles sont les suivants :

C

R

4

C

R

3

C

R

2

L

o

n

g

u

e

u

r

d

u

P

a

r

i

t

e

N

o

m

b

r

e

d

e

b

i

66

m

o

t

t

s

s

t

o

p

0 0 0 7

b

i

t

s

P

a

i

r

e

2

0 0 1 7

b

i

t

s

I

m

p

a

i

r

e

2

0 1 0 7

b

i

t

s

P

a

i

r

e

1

0 1 1 7

b

i

t

s

I

m

p

a

i

r

e

1

1 0 0 8

b

i

t

s

S

a

n

s

2

1 0 1 8 S 1

67

b

i

t

s

a

n

s

1 1 0 8

b

i

t

s

P

a

i

r

e

1

1 1 1 8

b

i

t

s

I

m

p

a

i

r

e

1

Bits de contrle du transmetteur (CR5 et CR)

Ces deux bits permettent le contrle des interruptions en transmission pouvant tre

generees par la condition registre de transmission vide, par la sortie RTS et par la

transmission d`un BREAK (niveau bas) sur la ligne de transmission serie. Les Ionctions

possibles sont les suivantes :

Controle en transmission C

R

6

C

R

5

RTS0, Interruptions du

transmetteur inhibees

0 0

RTS0, Interruptions du

transmetteur validees

0 1

RTS1, Interruptions du

transmetteur inhibees

1 0

RTS0, Interruptions du

transmetteur inhibees et

Emission d`un break sur la

ligne (niveau bas)

1 1

68

L`ACIA met automatiquement CR6.CR51.0 a la mise sous tension pour eviter l`envoi

d`inIormations aleatoires.

Bit d'autorisation des interruptions du rcepteur (CR7)

Les interruptions generees par le recepteur sont autorisees si Cr71 et sont masquees si

CR70 . Les interruptions du recepteur sont generees par les conditions suivantes :

registre de reception plain, une transition montante sur l`entree DCD.

C

o

n

t

r

o

l

e

e

n

r

e

c

e

p

t

i

o

n

C

R

7

I

n

t

e

r

r

u

0

69

p

t

i

o

n

s

d

u

r

e

c

e

p

t

e

u

r

m

a

s

q

u

e

e

s

I

n

t

e

r

r

u

p

t

i

o

n

1

70

s

d

u

r

e

c

e

p

t

e

u

r

v

a

l

i

d

e

e

s

Registre detat SR

Le registre d`etat (8 bits) permet de contrler en permanence le transIert des inIormations. Il indique les

etats du registre de transmission, du registre de reception et des erreurs logiques, ainsi que l`etat des

entrees CTS et DCD.

SR0 : RDRF (Receive Data Ragister Full : Registre de Reception des donnees plein)

Un test sur ce bit permet de connatre l`etat du registre de reception. Il indique (quand il est a 1) qu`une

donnee reue a ete transIeree dans le registre de reception RDRF. Quand il est a 0, ce bit indique que le

registre de reception ne contient pas de nouvelle donnee. La lecture du registre de reception par le p

reinitialise RDRF a 0.

SR1 : TDRE (Transmit Data Ragister Empty : Registre de Transmission des donnees vide)

71

Ce bit indique, quand il est a 1, que le contenu du registre de transmission a ete transIere dans le registre a