Professional Documents

Culture Documents

Design of PVT Tolerant Bandgap Reference Circuit For Low Noise and Low Current

Uploaded by

Manraj GujralOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design of PVT Tolerant Bandgap Reference Circuit For Low Noise and Low Current

Uploaded by

Manraj GujralCopyright:

Available Formats

UniversityofSouthampton

SchoolofElectronicsandComputerScience

DesignofPVTTolerantBandgapReferenceCircuitfor

LowNoiseandLowCurrent

By

ManrajSinghGujral

msg1g10

22

nd

September,2011

Projectsupervisor:Dr.PeterRWilson

SecondExaminer:Dr.KoushikMaharatna

Aprojectreportsubmittedfortheawardof

MasterofScienceinSystemonChip

ManrajSinghGujral msg1g10UniversityofSouthampton 2

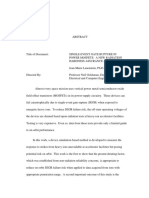

Abstract

With each new process technology, essentially driven by digital electronics, the transistor

sizesarebeingshrunktotheirlimitssothattheycanbepackedinmillionsinasmallsilicon

area. This increases the complexity for analogue circuits which are required to produce an

accurate output despite increased performancedegrading parameters, over a range of

conditions like temperature, voltage fluctuation and process errors. Therefore, with every

leap in process technology, more and more intelligent ways of implementing the analogue

andmixedsignalcircuitsarebeingsoughtafter.

Thisprojectdealswiththedesignofonethemostcommonblocksusedinalmostallsystem

onchipdesigns,aBandgapReferencecircuit.Areferencesignaloravoltagesourcewhichis

thefirstsignalgeneratedonachipthatandthencanbeusedforbiasing,generatingother

signalsacrossthechipetc.ThedesignfocusesontheNoiseperformanceanditseffectonthe

other systems connected to it. A detailed stepbystep approach is presented in this report

towards an ultra low noise performance. The Bandgap is tested for worst case industrial

Corners,islaidout,extractedandfinallyverifiedwithSchematicvs.Extractedchecks.

Acknowledgments

I would like to thank Dr Peter Wilson, my supervisor, for encouraging me to take on this

project.

Also,IwouldthankDrKeLiforofferingmehistimeandassistancewheneverIgotstuck.

SpecialthankstoMr.AjaibHussain,UKEngineeringManager,RakonUKLtd.,forproviding

meachancetoworkonthisprojectinRakonwithindustriallyacceptablespecificationsand

performancecriteria.

IwouldalsoliketothanktheDesignTeaminRakonUKLtd.,Mr.KevinAylward(PrincipalIC

Designer), Mr. Karl Ward (Principal Design Engineer), Mr. Ravi Ramakrishna (Sr. IC Design

Engineer) , Mr. Robbie Robinson (Sr. Layout Engineer) & Mr. Mark Broad (Sr. Layout

Engineer)fortheirconstantfeedbackandsupportthroughoutthisproject.

ManrajSinghGujral msg1g10UniversityofSouthampton 3

TableofContents

Abstract......................................................................................................................................2

Acknowledgments......................................................................................................................2

Chapter1:Introduction.............................................................................................................4

1.1ThesisStructure...............................................................................................................4

1.2BandgapPrinciple............................................................................................................5

1.3TemperatureCoefficients................................................................................................8

1.4NegativeTemperatureCoefficient..................................................................................8

1.5PositiveTemperatureCoefficient..................................................................................10

1.6TemperatureIndependence..........................................................................................11

Chapter2:BasicBuildingBlocks..............................................................................................15

2.1BasicAmplifier...............................................................................................................15

2.2CurrentMirror................................................................................................................17

2.3StartupCircuits...............................................................................................................19

Chapter3:BandgapModels....................................................................................................21

3.1Bandgap1......................................................................................................................21

3.2Bandgap2......................................................................................................................23

3.3Bandgap3......................................................................................................................25

Chapter4:CornerSimulationsforBandgap3........................................................................30

Chapter5:Layout&Extraction................................................................................................35

5.1Theory............................................................................................................................35

5.2Extraction.......................................................................................................................40

5.3CurrentSourcesfortheOutputStage...........................................................................42

Chapter6:Schematicvs.ExtractedBandgapSimulations(withuniversitycorners)..............48

Chapter7:Summary................................................................................................................52

SpecificationComplianceMatrix.........................................................................................52

Chapter8:NoiseAnalysis........................................................................................................53

8.1LDOPhaseNoise............................................................................................................57

8.2ControlSupplyPhaseNoise...........................................................................................60

8.3Experiment1:LowPassFilter.......................................................................................62

8.4LDOandControlSupplyPhaseNoiseRegions...............................................................63

Chapter9:Conclusion..............................................................................................................65

9.1ScopeofImprovement..................................................................................................65

References...............................................................................................................................66

ManrajSinghGujral msg1g10UniversityofSouthampton 4

Chapter1:Introduction

Allcircuitsandsystemsincorporateareferencesignalwhichsetsthefoundationofallother

signalstobegeneratedfromit.Sincethesereferencesareresponsibleforgeneratingallthe

biasinginagivenchipitisveryimportantthesesourcesareindependentofparameterslike

thevariationsinsupplyvoltage,temperaturefluctuationsandprocessvariations.Oneofthe

common techniques used is to have a Bandgap reference. As a starting guideline, a set of

specificationisprovidedisshowninthetable1below

Table1:BandgapSpecifications

Specification

Parameter Min

Nom

Max Units

Powersupply,Vcc

1.7 1.8 1.9 V

Temperature

40 27 85 C

BGRo/p,Vref

const. V

BGRo/pAccuracy

30m +30m V

BGRo/pRefCurrents

10 A

20 A

40 A

100 A

OutputImpedance(for10Ao/p) 1M

PSRR

40 dB

Noise(at10kHz)

100 nV/(Hz)

QuiescentCurrent,Idd(BGR)

100 A

Beforeweunderstandwhatthesenumbersmeanwewillfirstlookatthebasicprinciplesof

aBandGapandhowitcanbeusedtogenerateourreference.Theseareexplainedfrom

section1.2

1.1ThesisStructure

Chapter1providestheintroductiontoBandgap.Itdiscussesthebasicprinciplesandorigins

of temperature coefficients and how it can be used to make a Bandgap Reference voltage

source.

Chapter 2 marks the beginning of a design strategy exploring common building blocks that

wecouldplayaroundwithinananaloguecircuit.Thepropertiesofthesebuildingblocksare

seenindetailandhowtheycanbemodifiedtosuitspecificneeds.

ManrajSinghGujral msg1g10UniversityofSouthampton 5

Chapter 3 The bandgap models are then developed in this chapter. Each model is checked

andsimulatedtoseeifitcanbeimprovedanyfurther.Finallythechosenmodelissimulated

forworstcasecornersinChapter4.

Chapter 5 & 6 deal with the Layout and extraction of the selected bandgap schematic. A

detailed Layoutflow discussion is carried out in this section. After layout, DRC checks and

LVS the circuit is then extracted and a Schematic vs. Extracted bandgap simulation is

performed.AsummaryofalltheresultsarepresentedinChapter7.

TounderstandNoiseanditseffectsonthesystemwethenrunsimulationsonatestcircuit

providedbyRakon,inChapter8.ThistestcircuitisanactualpieceofcircuitryusedinRakon

systems. The noise profiles are therefore actual values seen in their systems and several

testsareconductedtoseehowitisdistributedacrossthesystem.

FinallyChapter9concludesthefindingsandpresentsfurtherscopeofimprovements

1.2BandgapPrinciple

Bandgap references are derived directly from the silicon, i.e., the potential between the

ValanceBandandtheConductionbandoftheSilicon.Hencetheyaretheonlytruebandgap

references.Thecurrentreferencesarederivedfromtheseabsolutevoltages.(1)

Figure1:Asimplifiedbanddiagramofasemiconductor.

An almost empty conduction band represents the electrons which have moved to a higher

energy level and can now conduct. The difference in the Energy in the electrons in the

Conduction band over the Valance Band (non conducting band) is seen as the Bandgap

energy. Valence band edge is shown as Ev (not electron volts). Conduction Band Edge is

shownasEc.TheenergyofanelectronoutsidethecrystalisE(vacuum)

ManrajSinghGujral msg1g10UniversityofSouthampton 6

Figure2:EnergyBandsforMetals,insulatorsandSemiconductor

This bandgap energy tends to decrease with the temperature because of the increased

interatomic spacing due to the thermal vibrations. The increase in spacing reduces the

potentialseenbytheelectronsandthereforetherelativegapbetweentheenergybandsis

alsoreduced.(2).ThatswhyweseeaCTATvoltageasshowninfigure3.

The experimental expression for the dependence between the Energy bandgap and

temperatureisfoundouttobe

E

g

(I) = E

g

(u) -

oI

2

I +[

Equation1(2)

WhereandarecalledthefittingparametersandE

g

(0)istheEnergyat0K.Thefitting

valuesarelistedbelowforGermanium,SiliconandGalliumArsenideinTable2

Table2:TableforfittingparametersforcalculatingtheEnergyBandgaps.(2)

Germanium Silicon GaAs

Eg(0)(eV) 0.7437 1.166 1.519

(meV/K) 0.477 0.473 0.541

(K) 235 636 204

And therefore if we run a temperature sweep on these materials we would get a result as

showninFigure3

ManrajSinghGujral msg1g10UniversityofSouthampton 7

Figure3:TemperatureandBandgapenergyrelationship(2)

How we make a CTAT voltage source into a temperature independednt voltage source will

bediscussedinthenextchapter.

From a circuit point of view, a reference voltage set all the other baising voltages in the

entire circuit. For example a reference voltage can be used in a Voltage regulator using a

feedbackloopwitharesistorratio.

Figure4:Vrefusedinavoltageregulator

SimilarilyaCurrentreferencecanalsobegeneratedfromaBandgapvoltage

Figure5:VrefusedinaCurrentsource(1)

Inthiscaseareferencevoltageisconvertedtoacurrentthrougharesistorandandopamp.

AsaresultitispossibletogeneratefurtherreferencesifwehaveaV

REF

thatstaystruetoits

name,i.e.,stableoveranentirerangeoftemperature.

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

0 500 1000 1500

E

n

e

r

g

y

B

a

n

d

g

a

p

(

e

V

)

Temperature (K)

GaAs

Si

Ge

ManrajSinghGujral msg1g10UniversityofSouthampton 8

1.S Tempeiatuie Coefficients

Many circuit related parameters and processes vary with temperature. It is therefore

interesting to see how the temperature independence is achieved. It is suggested if two

equal quantities of opposite temperature coefficients are added then the net result is nil. ,

i.e.,theresultcouldhaveazero(nearzero)temperaturecoefficient.

Concept being, if we have two voltages , V1 and V2 and they vary with temperature

opposite to each other , then we have a start. We can choose a multiplying factor (or a

scalingfactor),1and2,suchthattherateofchangeofthesevoltagescanbeequatedto

giveanetresultofsomethinglike

I

RLP

= o1I1 + o2I2

(3)

Suchthat

o1

oI

1

oI

+ o2

oI

2

oI

=

oI

RLP

oI

= u

I.e.

o1

oI

1

oI

= -o2

oI

2

oI

Equation2

Therefore we need to look for two such sources where, similar to equation 2, the

temperaturecoefficientsareopposite(andscaled)equaltooneanother.

1.4NegativeTemperatureCoefficient

A diode connected transistor has a currentvoltage relation quite accurately given by an

exponential. Usually, in a Pure CMOS process, forward biased diodes are avoided and the

designermighthavetoaskforspecialrequestfromthefabricationhouseifhe/sheintends

to use it. Unless specially made, diodes tend to pollute the substrate with forward biased

currents and manyatimes the model supplier will limit the forward biasing currents to a

maximum level with warnings (4). Therefore, if the same operation is achieved by a

transistorconnecteddiodethenitisadvisedtouseitinsteadofanactualdiode.

Figure6:Diodeconnectedtransistor.(3)

where,I

o

= I

S

c

v

BE

kT q

I

S

:saturationcurrentkTn

2

.

:mobilityoftheminorityCharge

carriers.

n:majoritychargecarrierconcentration

k:Boltzmannconst.

andkT/qisalsorepresentedasV

T

,earlyvoltage

ManrajSinghGujral msg1g10UniversityofSouthampton 9

IfwetakethiscurrentequationandrewriteitintheformofV

BE

,weget

I

BL

=

k1

q

ln(

I

c

I

S

),orI

BL

= I

1

ln(

I

c

I

S

)

Equation3

Takingthederivativeofequation3wefind,

oI

BL

oI

=

oI

1

oI

ln _

I

o

I

S

] -

I

1

I

S

oI

S

oI

Equation4

Equation 4 can be further proved to have a negative temperature coefficient or has a

Complementary To Absolute Temperature (CTAT) slope, by subsequent derivation, so we

performasimpletestinCadenceifthiscanbeprovedtrue.

In the circuit schematic shown in figure 7(a), an IBM 180nm BiCMOS library npnx bipolar

deviceisusedwhichisconnectedintheformofadiode.Thecurrentsource(I3)issupplying

25Awithapowersupplyof1.2V.Thiscircuitisthentestedoveratemperaturerangeof

45C to +125C. Figure 7 (b) shows the V

BE

voltage across the pn junction through this

temperaturerange.

(a) (b)

Figure7:(a)DiodeconnectedTransistorcircuit,(b)ItsV

BE

vs.Tcharacteristic

As can be seen by the figure 7 (a) & (b), the slope of the V

BE

, i.e., the Temperature

coefficientisnegative.Theprecisevaluecanbeseenfromthegraphtobe

oI

BL

oI

= -1.S4mvC.

Equation5

This seems to give us a fairly constant negative temperature coefficient slope over the

entire range of our operation. Although this looks like a linear slope, if this were plotted

over a long temperature it would appear to follow a second order slope, similar to a

parabola, but that is a second degree effect and for the purpose of this exercise we can

treatitasalinearslope.

ManrajSinghGujral msg1g10UniversityofSouthampton 10

Interestingly, even though the voltage across the diode connected transistors is CTAT, the

currentthroughitisaProportionaltoabsoluteTemperatureorPTAT.Thiscouldbefurther

discussed and analyzed. This is an interesting concept which can be looked into and is not

quiteapparentordiscussedinmanybooks.

1.5PositiveTemperatureCoefficient

It was found that if the two diode connected transistors are made to operate under

different current densities, then the difference in their base emitter voltage is a PTAT

voltage.(3)

VDD

nI I

Vbe

+

Q1 Q2

1:r

Figure8:PTATVoltagegeneration

Likewise,asmalltestcircuitismadesimilartofigure8withI=25A,n=10andTransistor

sizeQ2/Q1=1,i.e.,r=1.BasedontheEquationspresentedinfigure8,wecanexpect,

oAI

BL

oI

=

k

q

lnnr = u.u87 1u

-3

ln(1u 1) = . 232 mF

Equation6

AtemperaturesweeptestiscarriedouttocheckforvalidityofthePTATvoltagesource.

(a) (b)

Figure9:(a)DiodeconnectedTransistorscircuit,(b)ItsV

BE

vs.Tcharacteristic

In figure 9 a Positive temperature coefficient can be seen between V

BE

and Temp with

coefficientvaluebeing0.206mV/C,whichmatchesourestimationinEquation6.

I

BL

= I

BL1

- I

BL2

= I

1

ln

nI

I

S1

- I

1

ln

I

I

S2

= I

1

lnn

I

S2

I

S1

oAI

BL

oI

=

k

q

ln nr

Therefore,

ManrajSinghGujral msg1g10UniversityofSouthampton 11

FromthetwoanalysisofPositiveandNegativetemperaturecoefficientsitcanbeseenthat

both types are indeed possible. Therefore Equation 2 (page 8) seems possible and can be

implementedwithcorrectmagnitudesofthemultiplyingfactor1and2.

1.6TemperatureIndependence

WecannowcometoaconclusionthattherearetwotypesofTemperaturecoefficientswe

canplayaroundwith.Ifwecanfindawaytoaddthesetwovoltages,theoretically,wecan

obtainatemperatureindependentoutput.

Thereareanumberofwaysinwhichthiscanbeimplementedandalotofpapershavebeen

presented on this subject over theyears. Therefore, lets start with the basic concepts and

buildonitfurther

Consideracircuit,aspresentedbyWillyM.C.Sansen(1)

Figure10:aPTATvoltagecircuitgeneration

In this case assuming the currents in the two arms are the same, i.e., n = 1, but the

TransistorSizesaredifferentQ2/Q1=r,wecanderiveourPTATequationas

I

BL2

= I

BL1

+ I

R

So, I

R

= I

BL2

-I

BL1

= I

BL

Since v

BE2

= v

T

ln

I

C

I

S2

Therefore

I

BL

= v

T

ln

I

C

I

S2

- v

T

ln

I

C

I

S1

Hence,

I

BL

= v

T

ln

I

S2

I

S2

= v

T

ln i

Equation7

whereristheRatiooftheTransistorsize.

TakingthedifferentialwithrespecttotemperaturewecanseeourPTATequationas

ManrajSinghGujral msg1g10UniversityofSouthampton 12

oI

BL

oI

=

k

q

lnr

Equation8

NowononearmwehaveaCTATvoltage,whichistheV

BE

andontheotherarmwehavea

PTAT which is the V

BE

, if we add them together we can very easily get a Temperature

independentvoltage.

Similartothecircuitshowninfigure10,weemployacurrentmirror,Q3Q4,tomakesure

the currents in both the arms are the same. Moreover, we can add a ratio in that current

mirrorandthereforevarythecurrentinthesecondarmdependingonthescalingrequired

tomaintainanequalandoppositePTATandCTATslope.

Q1 Q2

1 : r

R1 Vbe

+

-

Q4 Q3

n : 1

R2 Vr2

+

-

Vref

+

-

Figure11:BasicBandgap

SincethecurrentsarenowntimeseachothertheV

BE

,inequation6,becomes

I

BL

= I

1

ln

nI

C

I

S2

- I

1

ln

I

C

I

S1

I

BL

= I

1

lnni

Equation9

ThereforetheCurrent,I

c

,inthearmissetbytheresister,R

1

as

I

C

=

I

BL

R

1

Equation10

Thisisthenmappedontothesecondarmbythecurrentmirrorwitharatioofn.Hencethe

voltageacrosstheresistor,R

2

isgivenby

v

R2

= R

2

n I

BL

R

1

Equation11

ThisisnothingbutaPTATvoltagescaledbyafactorof:n.R

2

/R

1.

i.e.,thereferencevoltagenow,shownasV

REF

becomes

v

RLP

= I

R2

+ I

BL

Equation12

ManrajSinghGujral msg1g10UniversityofSouthampton 13

So here, we have a PTAT and a CTAT voltage adding to give a reference voltage. Lets put

thistheoryintopractiseandbuildasmallcircuitthatshouldprovetheaboveconcepts.

WeselecttheTransistorsizeas1:4,thecurrentmirroras10:1andR1as50k.

First,ourV

BE

value,(Equation9)becomes

I

BL

= I

1

lnni = u.u26ln(1u 4)

I

BL

= 9Smv

Equation13

Therefore,Ic(Equation9)isgivenas

I

C

=

I

BL

R

1

=

u.u9S

Su 1u

3

I

C

= 2A Equation14

Figure12:BasicBandgapschematic

We mirror this current, to 20A and pass it through the resistance R2. R2 is assigned as

20kthereforethePTATvoltagegeneratedontheresistanceR2is

v

R2

= n.

R2

R1

vbe = 2 2uk

v

R2

= u.4v

Equation15

ManrajSinghGujral msg1g10UniversityofSouthampton 14

In figure13, we can look at the expected values of Voltages and currents. The currents are

shownindottedlineswithlegendsprintedalongside.

Figure13:BasicBandgapoutputwave

Here, among the crisscross of waveforms in figure 13, we can see the Actual temperature

insensitivevoltage(labelledVref)beinggenerated.Oncloserinspectionweseethatitisstill

droopingatlowertemperature.ThismeanswehavetoadjusttheslopesofPTATandCTAT

sothattheyexactlymatcheachotherinoppositedirection.

n.

R2

R1

Vbe:PTATVoltage

Vbe,CTAT

Vref:TemperatureIndependentVoltage

Ic2

Ic1

Vbe

ManrajSinghGujral msg1g10UniversityofSouthampton 15

Chapter2:BasicBuildingBlocks

Before we begin to construct the bandgap circuit, lets look at a few important building

blockswhicharewidelyusedinanalogueandmixedsignaldesign.Thesewillalsobeusedin

ourbandgapcircuit.

2.1BasicAmplifier

(a) (b)

Figure14:(a)BasicAmplifiercircuit(b)I

DS

vs.V

DS

curvewithvaryingV

GS

ForLinearRegion,whereV

DS

<V

GS

+V

T

,theSchichmanHodgesDraincurrentequationisgiven

by

I

S

=

p C

ox

w

2 nI

( I

uS

- I

1

-

I

S

2

)I

S

Equation16

ForSaturationRegion,whereV

DS

>V

GS

+V

T

,

I

S

=

p C

ox

w

2 nI

(I

uS

- I

1

)

2

(1 + zI

S

)

Equation17

Theterm1 + zI

S

representsthechannellengthmodulation.

C

OX

andnaretheProcessparameterfortheOxidelayerandthesubthresholdsloperesp.

W/Listhewidthoverlengthofthechannel

V

GS

, V

DS

, V

T

specify the GateSource Voltage, the DrainSource Voltage and the Threshold

voltagefortheMOSresp.

Equation16and17givesusthebasicstoperformhandcalculations.Furtheraccuracycanbe

gained if we include other effects such as the body effect, the vertical field mobility

degradationetc.

Linear Saturation

V

GS

+V

T

=V

DS

Ids

Vds

ManrajSinghGujral msg1g10UniversityofSouthampton 16

MOSdeviceshaveabehaviourpatternwithincreasingcurrentdensitieswithintheirchannel.

When a voltage is applied across the GateSource terminal and is gradually increased the

characteristicsofaMOSchangesfromWeakInversion,wherethedriftcurrentisverysmall

andthediffusioncurrentdominates,toStrongInversion,wherethechannelisnowformed

w.r.t. to the voltage and finally to Velocity Saturation, when the electrons in the channel

reach the maximum speed. This analysis is critical since it gives us an idea about the

maximumtransconductanceorgmofaMOSdevice.(4)

(a) (b)

Figure15:MOSCharacteristics(a)VariousregionsofInversion(b)Rateofchangeofgmw.r.tV

GS

During the point of velocity saturation the gm does not increase any further, but the current

increases linearly. Therefore, for analogue designers, this gives an idea of where the working

V

GS

ofthe MOSshouldbeset.Usuallyitisassignedjustbelowthevelocitysaturationpoint so

thatanychangesinthebiasdonotaffectthecurrentbudgetofthedesign.(1)

Inanaloguedesignitisadvisablenottousetheminimumpossiblechannellength(L)asperthe

technology. So It will be interesting to see how the gm of the transistor is affected by its W/L

parameters.

(a) (b)

Figure16:MOSCharacteristicsforgmvs.V

GS

(1)

Gm

becomes

constantin

velocity

saturation

Weak

Inversio

Strong

Inversion

Velocity

Saturation

L>>Lmin

L=Lmin

L>>Lmin

L=Lmin

ManrajSinghGujral msg1g10UniversityofSouthampton 17

(a)VaryingL,keepingW/Lconstant(b)VaryingonlyL,andkeepingWconstant

Fromfigure16itcanbeseenthattheInversionpointsforStrong,WeakandVelocitysaturation

can be manipulated by varying the parameters in W/L. This is an important concept when

designingacircuitinwhichMOSdevicesaresupposedtoturnonateitherlowvoltagesorhigh

voltagesdependingontheneed

Although, enough parameters can be analyzed for a MOS used as an Amplifier with its small

signal analysis, gain analysis etc, we will revisit the amplifier in next chapter when considering

designsforBandgaptopologies.

2.2CurrentMirror

In this topic we try and understand one of the critical building blocks in electronic design,

theCurrentmirrors.CurrentmirrorsarewidelyusedinbothAnalogueanddigitaldomains.

They are very useful when copying a current source across an IC and deriving multiple

currentreferencesfromjustoneidealsource.

FromEquation16weknowthatthecurrentequationofaMOS,insaturation,isgivenas

I

S

=

p C

ox

w

2 nI

(I

uS

- I

1

)

2

Equation18

Neglectingshortchanneleffects.

Where,C

OX

istechnologydependentparameter;nisthesubthresholdslope.

V

T

isthethresholdvoltage.

Therefore, the current is a function of Voltage at Gate w.r.t Source (Base w.r.t emitter in

Bipolar)i.e.,I

DS

=f(V

GS

).

This also means that, V

GS

= f

1

(I

DS

), which means, if a transistor is biased at I

DS

current it

generates a specific voltage V

GS

across it. Hence if this voltage, V

GS,

were to be applied at

thegateofanothertransistorwithsamefunctionf,wecanexpect

I

OUT

=ff

1

(I

DS

)=I

DS

Figure17:Diodeconnectedtransistorwithinversefunction,basiccurrentmirror

Asaresult,wecangetthesamecurrentattheoutputofanother,identicalMOSdevice.(3)

ManrajSinghGujral msg1g10UniversityofSouthampton 18

This concept can be further stretched to copying currents when W/L ratios are made

deliberately different. It is very simple in theory to perform current multiplication to just

aboutanynumber,butpracticallythatisnotthecase.

Figure18:Currentmirrorconceptextensiontocopyingcurrentsforreference

(a)SchematicdescriptionofCurrentcopying(b)PossibleLayoutsoffortheschematics

Current mirrors do give us the flexibility of generating our own current but an important

aspecttorememberisthatthisdevicehastobephysicallymadeonachip,likeeveryother

part of the circuit. Therefore, from a layout perspective a ratio of 1:2, or 1:8 is practical

whereasaratioof1:7.3or1:100mightnotbe practicalformatching.Wewillcomeacross

thisprobleminthechapter5inLayoutmatchingwhereweseehowtheseimpracticalratios

cangiverisetovariousproblems.

Sincethesecurrentmirrorareusedforcopyingareferencecurrentelsewhereinthecircuit,

these current sources are required to have high output impedance so that they can drive

largeloadsirrespectiveofthevoltagedropacrossit(aslongasitsinSaturationregion).

We attempt a small experiment where we use a standard current source like the ones

discussed above and plot their output characteristics. Then we use the same circuit and

implementacascadeontopofit.

(a) (b)

ManrajSinghGujral msg1g10UniversityofSouthampton 19

Figure19:CurrentMirrors(a)Simplecurrentmirror(b)CascodedcurrentMirror(BiasSetat1V)

Figure20:Outputcharacteristicsofthetwotypesofcurrentmirror.

Theoutputimpedanceofthecircuitisshowninfigure19.Wecanobserveperfigure20,we

canobservethattheoutputimpedanceofthedevicecanbeincreasedbyaddingacascode.

Thisisinlinewiththetheorythatoutputimpedanceofthecircuitshowninfigure19(a),

R

S

=

1

zI

S

Equation19

Isincreasedto,

R

0ut

= g

m2

R

S1

R

S2

Equation20

Whereg

m2

isthetransconductanceofthebiastransistor.

R

DS1

,R

DS2

aretheoutputresistanceofthetwooutputsideMOSrespectively.(4)

2.3StartupCircuits

AnothercriticalaspectinanICdesignistheuseofStartUpcircuit.Mostofthecircuitshave

two distinct stable points. One with zero current in the system and the other at a specific

desired bias point to which the system is actually designed. It is critical that no IC sent to

fabrication with a probability that it might not start. The start up circuits ensures that the

systemreachesitsdesiredoperatingpoint,always.Also,withoutstartupcircuits,softwares,

forexampleSpectre,mightnotsimulatethesystemproperlysinceitcanalwaysfindastable

solutionatzerocurrent.Tostressonthispointletusexamineatestcaseshowninfigure21

Voltage

C

u

r

r

e

n

t

Bipolar

curve

Bipolar +

resistor curve

Stable point 1

Stable point 2

cascoded

Simplecurrent

ManrajSinghGujral msg1g10UniversityofSouthampton 20

Figure21:Anexampleoftwostableoperatingpoints(5)

A bipolar device will have an exponential curve where as a Bipolar with a resistor in series

(or even a MOS device) will have a straight line characteristic (also shown in figure 15 (a)).

Thesetwocurveswillthereforeintersectattwodistinctpoints,oneat(0,0)andotherata

specifiedcurrentandvoltagevalue.

Startupcircuitsareusedtobringthesystemintoactivestatebysupplyinganinitialcurrent

during power ON that aids a self sustaining current to be generated in the main system.

Thesecircuitsaresodesignedthatafterstartingup,theyisolatethemselvesfromthemain

systemanddonotplayapartinitsgeneralfunctioning.

Figure22:StartupCircuitbasicprinciples

There are a number of ways to devise a start up circuit and there is no hardandfast rule.

Thereareseveralfactorsforadesignertoconsiderwhenmakingsuchacircuit,forexample:

Thestartupcircuitisrequiredtoeitherfeedthecurrentintothecircuit,ordrainthe

currentfromthecircuit(sinkit).Thesearethetwofundamentaltopologies.

When sourcing a current into the circuit the current should be fed into a part of

the main circuit that aids buildup of other circuit currents, i.e., to have a positive

feedback innature within the circuit. It is because of this positive feedback, we can

onlyprovideatinyamountofcurrentthatbuildsitselftothemaincircuitcurrent.

A feedback, or a sense, can be feed the status of the system back to the startup

circuit,forexampleavoltagesensethatcanswitchthestartupcircuitoff.

ThestartupcircuitinthisexercisethatIhaveusedusesaresistoracrosswhichavoltageis

developedthatpullsaPMOStransistoroff.Oneofthedrawbacksisthatitisatradeoff

betweenthesizeoftheresistorandtheareaofthecircuit.Sincethespecificationincludeda

currentbudget,Ihavemadetheresistorvalue(andhencethearea)high.

ManrajSinghGujral msg1g10UniversityofSouthampton 21

Chapter3:BandgapModels

There are a lot of papers on Bandgap designs dealing with low voltage, high PSRR, high

precision etc. There were several circuits attempted in order to reach the final circuit that

matchedthespecifications.Thesecircuitsarebrieflydiscussedwiththeirdesignstrategies.

3.1Bandgap1

Inthisdesign,amodularapproachwastakenwherethebandgapcircuitiscomprisedofthe

diode connected transistor and V

BE

, and an OpAmp to ensure that the voltage in the two

armsarethesame.AStartupCircuitisnotincludedatthispoint.

Figure23:aTypicalBandgapApproach.

Figure24:OutputVoltageperformanceoftheBandgap1Circuit.V

max

=17mV(approx)

ManrajSinghGujral msg1g10UniversityofSouthampton 22

(a) (b)

Figure25:OutputPerformance.

(a) OutputNoiseperformance1HzNoise=210.87v/Hz,10kKhzNoise=1HzNoise=2v/Hz

(b) PSSR,47dBat1Hzand10kHz

Table3:PerformancetableofBandgaps,withBandgap1

OutputAccuracy,

Vmax

Noise(1Hz) Noise(10kHz) PSRR

Specification 60mV NA 100nV/Hz 47dB

BandGap1 17mV 210.87v/Hz 2v/Hz 40dB

This circuit has an output voltage performance V

max

= 19mV which is fairly good when

comparedtoourspecifications(of+/30mV).TheoutputNoiseperformanceisjustaboutin

the range with minimum PSSR of about 45dB compared to 40dB in the specification. The

Noiseperformance,however,isextremelypoorat1Hzand10HzNoisebeing210.87v/Hz

and2v/Hzresp.WewouldliketohavenoiselevelsinrangeofseveralnV/Hz.

These high levels of Noise can be explained by looking at the OpAmp used in this circuit.

Thecircuitdiagramofthe2StageOpampusedinthiscircuitisshownbelowinfigure26

Figure26:A2StageOpAmpusedinbandgapcircuit.

ManrajSinghGujral msg1g10UniversityofSouthampton 23

Figure27:A2StageOpAmpOutputcharacteristics.PhaseMarginof74(approx)

ThiscircuitcontainsmanyMOSdevices.MOSisspeciallyknownforitsbad1/fNoisewhich

wasseeninfigure25,outputperformance.Therefore,thisleadsustoanewcircuitcanbe

implementedwithoutMOSdevices.

3.2Bandgap2

AnewBandgaptopologyisshownin,figure28.HereweuseasinglestageopAmpwithan

outputbuffertoseeifwecanreducethenoise.

Figure28:Circuitfor2

nd

Bandgapdesign

Figure29:OutputvoltageforBandgap2acrosstherangeoftemperature.V

max

=9mV(approx)

Bandgapoutput

OutputBuffer

ManrajSinghGujral msg1g10UniversityofSouthampton 24

(a) (b)

Figure30:OutputPerformance.

(a) OutputNoiseperformance1HzNoise=91.5V/Hz,10kKhzNoise=3.08V/Hz

(b) PSSR,47dBat1Hzand10kHz

Table4:PerformancetableofBandgaps,withBandgap1&2

Vsupply OutputAccuracy Noise(1Hz) Noise(10kHz) PSRR

Spec 1.8 60mV NA 100nV/Hz 45dB

BandGap1 1.5 17mV 210.87v/Hz 2v/Hz 40dB

BandGap2 1.8 9mV 91.5v/Hz 3.08V/Hz 47dB

We do get a much better noise performance with this topology, since the noise is almost

reducedmorethan50%oftheBandgap1Noise.Thatisasignificantimprovement.

TheOutputAccuracyalsohasincreasedconsiderablytoonly+/9mV.

Although this gives a marked improvement in the output, the output noise still remains

quitehigh.WehaveenoughmarginsintermsofBandgapvoltageoutputbuttheNoiseand

PSRRstillremainsanissue.

Thecircuitstillhasalotofscopeofimprovement.

ManrajSinghGujral msg1g10UniversityofSouthampton 25

Figure31:DiagramillustratingextraMOScomponents

WecanattempttoreducethenumberofMOSdevicesbyusingthesamecircuittopology

withoutthetailcurrentMOS.AlsowecanuseabipolardeviceinsteadoftheTN0MOSas

showninzoomedinviewoftheBandgap2circuitinfigure31.

3.3Bandgap3

Figure32:Circuitdiagramofbandgap3withstartupcircuit

Figure33:OutputvoltageforBandgap3acrosstherangeoftemperature.V

max

=5mV(approx)

ManrajSinghGujral msg1g10UniversityofSouthampton 26

(a) (b)

Figure34:OutputPerformance.

(a) OutputNoiseperformance1HzNoise=306nV/Hz,10kKhzNoise=109nV/Hz

(b) PSSR,83dBat1Hzand60dBat10kHz

Table5:PerformancetableofBandgapCircuits,withBandgap1,2&3

Vsupply

Output

Accuracy Noise(1Hz) Noise(10kHz) PSRR

Spec 1.8 60mV NA 100nV/Hz 45dB

BandGap1 1.5 17mV 210.87v/Hz 2v/Hz 40dB

BandGap2 1.8 9mV 91.5v/Hz 3.08V/Hz 47dB

BandGap3 1.8 5mV 306nV/Hz 109nV/Hz 83dB

The values coming out of this bandgap are much better in terms of Noise performance.

Industrially the Noise due to bandgap is in the range of several 10s of nV at 10kHz. This

circuit comes quite close to the industrial standards and serves as the base from which

furtherimprovementscanbemade.

This Bandgap was tweaked about and worked upon in various ways to get to these low

outputnoiselevels.FromthegivenlibraryofIBM7WL,allresistorsweretestedfortheleast

amountofnoiseattheoutput.

Table6:BandgapoutputNoisewithdifferenttypesofresistorsandtheirsheetresistance

ResistorType nV/Hz(at1Hz) SheetResistance/Sq

oprppcres 631 260

oprrpres 2751 1600

oppdres 431.9 105

opndres 438 72

nwrrpres 2751 1600

nwrppres 631 260

nwppcres 660 NA

k1res 437 61

ManrajSinghGujral msg1g10UniversityofSouthampton 27

Thereadingsintable6wereobtainedduringthedesignofthebandgapwhenIwaslooking

to lower the noise of the whole system. Hence the values are not as per the output

performanceshowninthefigure34.TheSheetresistancewasreferredfromtheIBMDesign

ManualfortheirIBM7WLprocess.(6)

Two parameters were considered, firstly, and with a higher priority, was to achieve a low

output noise by changing the type of resistor. It can be seen that the Noise at the output

ranges from a minimum of 431.9 nV/Hz to 2751 nV/Hz. That is roughly 8 mes apart.

Therefore before changing the circuit topology it was prudent to change the type of

resistancewhichwouldprovidethelowestresistance.

Secondly,withlowerpriority,thesizeofresistances.AscanbeseenfromTable6theNoise

due to k1res (metal resistor) is fairly low, but the sheet resistance is extremely low. That

wouldmeanaresistanceintherangeofseveralkisnotpracticalinthiscircuit.

Also,nwrrpestypeofresistorhavethehighestsheetresistance,i.e.,takingupleastspacein

the layout. But this has a very high output noise affect on the Bandgap when used as the

mainresistorswhichlieinthesignalpath,i.e.,R1orR2inEquation22.Inthestartupcircuit,

for Bandgap 3, the resistance value is in the range of M and it does not lie in the signal

path, i.e., not affecting the output noise. In this case, the resistance is then used as the

nwrrprestype.Thisenablesustohavethehighestresistanceintheminimumpossiblearea

withnoeffectonthenoise.

Itisinterestingtoseethenoisedistributioninsidethebandgap.

Table7:NoiseSummaryforBandgap3.

SpotNoiseSummary(inV^2/Hz)at1KHzSortedByNoiseContributors

TotalSummarizedNoise=1.04402e14

Device

Noise

Contribution %ofTotal

I0.RP0.rma 1.88E15 18.01

I0.RP0.rmb 1.88E15 18.01

I0.Q20.q 8.59E16 8.22

I0.Q19.q 8.36E16 8.01

I0.Q1.q 8.32E16 7.97

The highest noise contributor is the Resistance RP0 (in Cadence Schematic), or R3 in

Equation22.Anotheradjustmentwhichwasmadewastomakethisresistanceverythickin

size. I.e., the width of the resistance was set to 3m and the equivalent length of the

Resistance depending on its resistance value was set. We can see that 3m, serves the

purpose by being just big enough to have low 1/f noise and being small enough to have a

fairlylowcontributioninareawhenlayingout.

ManrajSinghGujral msg1g10UniversityofSouthampton 28

ThegeneralBandgapoutputisgivenbytheequation

I

RLP

= o1I1 + o2I2

Equation21

Which implies addition of a CTAT Voltage slope to a PTAT voltage slope to finally give an

outputwhichistemperatureindependent?

Inthisbandgapcircuittheoutputcanbewrittenas

I

RLP

= I

BL1

+ I

BL

_

R

2

R

3

+1 ]

Equation22

SincethetemperaturedependenceofV

BE1

,asgiveninEquation6,ifweassumenandrare

bothequalto1,then

oAI

BL

oI

=

oI

1

oI

= u.u87 mI

Equation23

Andfromequation5wecanseethatthe,

oI

BL

oI

= 1.S mI

Equation24

Thereforefromequation22and23,itcanbeseenthattheBandgap3ismadetoworkwith

1=1

V1=V

BE1

,whichformstheCTATpartoftheequation

2=(R2/R1+1)

and,V2=V

BE

,whichformsthePTATpartoftheequation

Thereforetomatchtheslopeofboththeseparts,weneedtoensure

oAI

BL

oI

o2 =

oI

BL

oI

X 1

Equation25

Expanding2=(R2/R1+1)intheaboveequation

oAI

BL

oI

_

R

2

R

S

+1 _ =

oI

BL

oI

X 1

Equation26

Equation 26 is now the foundation of our bandgap. This not only sets the slope of the V

REF

butalsoshowsushowtosetit.

Wecanadjusttheslopeintwoways.

1. VaryingResistorRatio,R1andR2,tomakesure(R2/R3+1)x0.087x10

3

=1.3x10

3

.

As seen in the previous section, one of major noise contributor is the resistance

itself.Thereforetosomeextent,wehavetoincreasetheresistancevaluebutthere

is a limit up to which it starts impacting on the noise. Therefore increasing the

resistancevaluemightnotservethepurpose.

ManrajSinghGujral msg1g10UniversityofSouthampton 29

2. Varying the AI

BL

to make

Av

BE

1

[

R

2

R

3

+1 =

v

BE

1

. Where

v

BE

1

=

v

T

1

lnr , r

beingtheratioofthebipolarsize.

Therearefurthertwowaysofperformingthis:

a. By varying the size ratio of transistor size, r. This also has its practical limits.

Similar to Figure 18, the diode connected transistors have to be matched

during layout. So in theory we might be able to increase the ratio r to any

valuewewant,howeverinpractisethereisonlyuptoacertainratioatwhich

we can ideally march. Some of the acceptable ratios are 1:8, 1:16, 1:32 and

1:64.Beyondthisitbecomesdifficulttomatch.

b. AnothertechniqueusedforultralowbandgapsisknownastheAI

BL

stacking

Figure35:BlockDiagramtoillustratetheV

BE

stacking(7)

To avoid large transistor ratio, r, the concept of V

BE

addition can be used. The circuit

shown in figure 35 uses this approach presented in a thesis report from Mr William T

Holman,whichhelpsloweringthenoisesincedependenceontheresistanceratioisreduced

considerably.Theauthorsimulatedthisconceptandmeasuredtheoutputnoiseinthelevel

of30nV/Hz(at10kHz)

ApatentonasimilarconceptwasfiledbySanderGierkink(8)

Thistechniquecouldbefurtherusedtoreducethenoisetoultralowlevelsinbandgap3

aswell.

ManrajSinghGujral msg1g10UniversityofSouthampton 30

Chapter4:CornerSimulationsforBandgap3

Bandgap3 circuit is now selected to be used for next stage, to perform the worst case

corner simulation. These corners are industry based actual samples from Rakon. The

followingpointsexplainthesetup.

1. Temperature:45to90C(Although45to125isalsosuccessfulforTypicalModel)

2. Supply Voltage , Vdc : 1.6V ,1 .8V, 2.0V (Vdc has been tested for 1.5V to 2.2V for a

TypicalCase)

3. Strong & Weak characteristics for the following Model files (Also simulated for the

Nominal/TypicalCorner):

a. Bip.scs:npnBipolardevices

b. Bipp.scs:pnpBipolardevices

c. Nmos.scs:NMOSdevices

d. Pmos.scs:PMOSdevices

e. Rescap.scs:AllResistancesandCapacitancesintheIBM7Wllibrary.

4. TotalNumberofCorners,therefore3(Vdc)x2(bip)x2(Bipp)x2x(Nmos)x2(Pmos)

X2(ResCap)+Nominal=97

5. SimulationType=3

Figure36:BandgapOutputVoltageacrossallCorners

ManrajSinghGujral msg1g10UniversityofSouthampton 31

Table8VValuesacrossallcorners

DeviationfromMean

V(negative) V(Positive)

BestCorner 5.73m 0

Max.PositiveDeviationCorner 20.5m 9.68m

Max.NegativeDeviationCorner 14.8 3mV

WorstVamongCorners |V/2| 53mV

General Industrial standard before trimming the output is 5% of absolute value. Our

Bandgap supplies a Raw voltage of 1.18V therefore a range of +/ 60 mV. We have a

deviationof+/53mVfromthemeanforworstcasecorners

Anyfurtheraccuracycanbeimplementedbyaddingtrimmingcircuitstothebandgap.

Figure37:OutputNoiseoftheBandgap(measuredatVrefinfigure1)

Table9NoiseValuesacrossallcorners

AcrossAll96Corners

MinNoise TypicalNoise MaxNoise units

at1Hz 142 305.9 1385 nV/Hz

at10kHz 92 101 114 nV/Hz

ManrajSinghGujral msg1g10UniversityofSouthampton 32

Figure38:PSRR

Table10PSRRValuesacrossallcornersat1Hz

Max Typical Min units

121.7 83 76 dB

Figure39:TheBandgapstartsworkingatabout1.3V.thecornersimulationsweretestedfor1.5V

ManrajSinghGujral msg1g10UniversityofSouthampton 33

Figure40:CurrentOutputfromBandgap

Figure41:BGROutputCurrentscorners

ThisDesignwastransferredfromthecurrentRakonmachinetotheUniversitysystemanda

samplerunwasperformedwiththeUniversityModelsfortt,sf,ssat1.6V,1.8Vand2.0V

(i.e.,atotalof9corners).TheUniversitywaveisshowninFigure42below.

ManrajSinghGujral msg1g10UniversityofSouthampton 34

Figure42:BGROutputCurrentsforuniversitycorners

Vacrossallcorners,forworstcase=5.9mV.

ManrajSinghGujral msg1g10UniversityofSouthampton 35

Chapter5:Layout&Extraction

5.1Theory

AfterwefixedaschematicdesignthenextstepistoLayitout.Inthisexercisewecontinue

to use the tools by Cadence IC design Suite, and have used Cadence Layout XL. The Layout

techniques which have been listed below are techniques based on this specific layout and

eachcircuitwillhaveitsownprioritieswhenlayingitout.

1. IntheSchematicofanyDesigntherewillbePMOSesandNMOSesclosertotheVDD

and GND/VSS. A good tip to begin layout will be to move the PMOSes up and NMOSes

down.

Figure43Basiclayouttechniquesattempted

2. InthisexerciseinitialroutingwasdoneasperthestandardpracticeofM1andMetal

3inVerticalandMetal2andMetal4inHorizontal,butlatermodifiedtoreducetheuseof

Metal 3 in the layout, thereby reducing the effective cost of fabrication. Although this is a

verysmalldesign,ithighlightstheuseofdesignerschoiceinordertohavethesamelayout

indifferentways.

Alltheelementssupposedto

beconnectedtoVDD

Alltheelementssupposedto

beconnectedtovss

DiodeConnectedTransistorsina3x3

matrix

ManrajSinghGujral msg1g10UniversityofSouthampton 36

Figure44:RoutingusingMetal3inRevision1ofLayout

Figure45:RoutingreducedtoMetal2inRevision2ofLayout

Metal3(Vertical)

Metal2(Horizontal)

M3M2Taps

Metal1(0.75mWide)

Metal1(Horizontal)

Metal1(0.35mWide)

NoTaps

Metal2(Vertical)

ManrajSinghGujral msg1g10UniversityofSouthampton 37

Figure46:RoutingusingMetal3inRevision1ofLayout,2

nd

Example

Figure47:RoutingusingMetal2inRevision2ofLayout,2

nd

Example

This has enabled us to reduce a metal layer without increasing the area of the layout,

however one has to be careful while attempting to do this since it can cause routing

problemslaterintheLayoutstageormightincreasethemetaltracklengthstoachievethe

sameconnection.Thereforeitcomesdowntodesignersjudgement.

3. The MIM Capacitor (metalinsulatormetal) is relatively small for the same

capacitance,thereforeisabigadvantageiflookingforasmallerfootprint.

M1M3Taps

Metal3(Vertical)

M1M2Taps

Metal2(Vertical)

ManrajSinghGujral msg1g10UniversityofSouthampton 38

(a)

(b)

Figure48:Layouts(a)with1pFMIMCapacitor,and(b)with1pFvncapcapacitor.

Thereforeusingthisseemsamuchbetteroption,withoutdegradingtheperformance.

4. Mimhk type capacitors, unlike regular capacitor are formed on the top layers in

theprocess.

MIMCapacitor

vncapCapacitor

ManrajSinghGujral msg1g10UniversityofSouthampton 39

(a)

(b)

Figure49:1pFCapacitorusedinthedesign(a)asacomponent(b)splitupindifferentlayers

This means that the space beneath the capacitors can be used to place the component.

Therefore this is the second advantage with this type of capacitor, that components using

uptoM3canbeplacedunderneathit,therebysavingarea.

Since this component uses the top two layers in a process, this also changes the wiring

scheme. Unlike conventional capacitor, this is not formed with polygateoxidenWell but is

formed at the top level metals. Also the two terminal are supposed to be pulled from the

samehighestlayer,topreventdielectricbreakdown(9)

LAYER:E1

(dwg)

LAYER:MT(dwg)

ManrajSinghGujral msg1g10UniversityofSouthampton 40

Figure50AtestcircuittobeusedforMIMLayout

Figure51LayoutforatestcircuittobeusedforMIMLayout

Figure46and47explaintheconceptofwiringtoMIMcapacitorwithasamplecircuit.

5.2Extraction

The bandgap was extracted and cleared for all the DRC, LVS and Floating Gate and NWell

Errors. The following figures shows the full laid out circuit and additional features

incorporatedtoclearallthedesignrules.

MTtoE1VIAbeforeconnecting

toVSSPin

M1toE1(ThroughM2M3M4

MTlayers)VIAforconnectingto

thetopPlateoftheCapacitor

ManrajSinghGujral msg1g10UniversityofSouthampton 41

Figure52ExtractedviewoftheBandgap3.Sizeof100x131m

2

.

NWELL

Protective

Diode

Connection

VDD

Figure53NWELLProtection

NWELL

P Substrate

VDD

Reversed Biased

Diode

VSS

Figure54NWELLProtectionSchematic

ManrajSinghGujral msg1g10UniversityofSouthampton 42

P-Substrate

Taps

Polysilicon

Gate

Protection

Figure55GateProtection

Size of the cell could further be reduced by about 5% to 10% with proper laying out of

components.

5.3CurrentSourcesfortheOutputStage

1. Ideally,thecurrentscomingoutofthecurrentmirrorsarepreciseandDrainsource

voltage independent. As the design moves towards more practical models these

nonIdealeffectsstarttocreepinanddependingontheOutputNetsvoltage(andits

swings)theoutputcurrentderivedmightnotbeaspertheoreticalcalculations.

Figure56OutputStagecurrentsourcesfortheBandgapReference

BandgapVoltage

ManrajSinghGujral msg1g10UniversityofSouthampton 43

2. Infigure11,wecanseetheoutputsarelabelledas:

a. vdd_10u

b. vdd_20u

c. vdd_40u

d. vdd_100u

These outputs were tested for constant V

DD

conditions. Depending on the usage of

thesecurrentreferences,e.g.:aTailCurrentbiasforanOpAmp,oranoutputStage

Bias, etc., the desired accuracy willchange and also the Voltage across these nMOS

devices will vary. Therefore these circuit level changes can either be acknowledged

andtherequiredamountofaccuracyintheoutputcurrentcanbeimplemented,or

lessstringentaccuracylevelscanbeaccepted.

3. Possiblewaystoimprovetheaccuracy:

a. Oneoftheconventionalwayswouldbetoprovideahighoutputimpedance

forthesecurrentmirrors.Eitherbyacascodeorusinganenhancementtype

MOS.

b. AddingextraresistorontheSource.

4. To finish the trial within the given time frame a considered decision was taken to

make changes in the Width of the Transistors , and leave out the other options

enumeratedinPoint3above.Inordertomatchtheoutputcurrents,parameterized

simulationsofwidthwereruntofindouttheapproximatewidthsthatwouldsupply

the best output current over the entire Temperature range. The result is we have

Widthratiosas:

a. W0:W1=2:2

b. W0:W2=2:3.9

c. W0:W3=2:7.64

d. W0:W4=2:18.9

Where W0, W1, W2, W3 and W4 are the corresponding widths of the

TransistorsTN0,TN1,TN2,TN3,andTN4infigure1.

5. This meant that the conventional matching in the Interlocking Fingered way, as

showninFigure12andFigure13wouldntwork.

Figure57ConventionalInterfingeredmatchingasDDCABCDD.

TransistorsA(TN0)andB(TN1)areofthesamesize.

ManrajSinghGujral msg1g10UniversityofSouthampton 44

Figure58:ZoomedinviewbetweenTN2TN0highlightingtheerrorsduetonotches.

TransistorsA(TN0)andB(TN1)areofthesamesize.ScaleshowninMicrons

6. InconventionalmatchingthiswouldnotbeaproblemsincetheTransistorssizesare

anintegralmultipleofeachotherandsuchnotchesarethereforeavoided.

7. Since I had already made the schematic without realizing the Layout issues, I can

either make the Widths Integral multiples, for example W0:W4 = 2:20 instead of

2:18.9,ortrytolaythemcompromisingtheeffectivematching.

8. I am currently working on a slightly unconventional Layout. Since the Lengths of all

thetransistorsaresame,Iplantostackthemverticallyinsteadofhorizontally.

Figure59TransistorsStackedontheirGates,insteadofDrainandSources

Poly Poly

RX

RX

SinceTransistorLengthsareconstant.They have

beenstackedvertically

Metal1

(Commo

nDRAIN

Or

SOURCE

)

ManrajSinghGujral msg1g10UniversityofSouthampton 45

TheMatchingtechniqueforthisdesignisdescribedbelow,werewehave5setoftransistors

tomatch.Figure60and61presentsthematchingdiagrams

Figure60PresentTransistorsMatchingrepresentation,AandA0representthesameW/LTransistor

A

B

C

C

D

D

D

D

D

A0

B

C

C

D

D

D

D

D

Dummy

Dummy

Dummy

Dummy

Dummy

Dummy

Figure61AnotherMatchingschemethatcanbeused,AandA0representthesameW/LTransistor

Using the same concept as in figure 60 we stack the transistors on top of each other and

connect the same transistor with their respective Vdds. A zoomed in version of the

matchingusedinthisexerciseisshownbelowinfigure62

ManrajSinghGujral msg1g10UniversityofSouthampton 46

Figure62TransistorsStackedontheirGates,insteadofDrainandSources

TheoveralllayoutofboththeCurrentsourcesandtheBandGapareshownbelowinfigure

63.

(a) (b)

Figure63:(a)LayoutforCurrentSources17mX81m,(b)placedalongsideBandgapReference

CommonGate

CommonSourceConnection,

VSS

VRef

Vdd_10u

Vdd_20u

Vdd_40u

ManrajSinghGujral msg1g10UniversityofSouthampton 47

ThelayoutoftheOutputcurrentsources,Figure63(a),ismadelengthwisealsobecauseit

can easily be stacked next to the main bandgap reference circuit. Although a much tighter

packing of these two structures was possible, it was not attempted to go beyond this

currentone.Sincetheareaisnotamajorconcerninthisexercisemoreemphasiswasgiven

totheMatchingandoverallaccuracythanthesize.

The size of the Output current sources comes out to be 17m X 81m, and the size of the

Bandgapcircuitisabout131mX100m.

We will check these extracted models for their accuracy in the next chapter.

ManrajSinghGujral msg1g10UniversityofSouthampton 48

Chapter6:Schematicvs.ExtractedBandgapSimulations(withuniversitycorners)

ThefollowingfiguresshowthetestsconductedforSchematicvs.Extractedbandgapcircuitsandcomparetheoutputtoseeitstillmatchesthe

specifications.TheTestsetupisshownbelowinfigure64

Figure64:Schematicvs.ExtractedCircuit

Bandgapreference

Schematic

Bandgapreference

Extracted

CurrentSources

Schematic

CurrentSources

Extracted

Voltagesource(vdc_out)sweeptotest

theoutputImpedenceofthe10A

currentsourcesonboththeschematic

andExtractedcircuit

ManrajSinghGujral msg1g10UniversityofSouthampton 49

Figure65OutputVoltagefrom45to90C,withVDDvaryingfrom1.6Vto2.1V

ThemaximumVout(acrossallwaveforms=5.9mV)

Figure66PSSRWavefrom1Hzto10GHz.

Min76.8dB,Max=125dB

ManrajSinghGujral msg1g10UniversityofSouthampton 50

Figure67OutputNoiseWave

Noiseat10kHz=101.9V,Noiseat1Hz=308.53Hz

Figure68QuiescentCurrent

ManrajSinghGujral msg1g10UniversityofSouthampton 51

Figure69OutputCurrentsforSimulatedandExtractedcircuits.

Table11OutputCurrentResults(UnitsinA)

(at25C)

100A

Source

40A

Source

20A

Source

10A

Source

Simulated 101.81 40.1 19.97 10.041

Extracted 94.78 38.3 19.57 10.041

Figure70:OutputImpedanceforSimulatedandExtractedcircuits.WorstCase2.5M

ManrajSinghGujral msg1g10UniversityofSouthampton 52

Chapter7:Summary

SpecificationComplianceMatrix

Table12SpecificationComplianceMatrix

Specification

Simulation (Rakon

Corners,96No.s)

Extracted (University Corners,

9No.s)

Parameter Min Nom Max Min Nom Max Min Nom Max Units

Power

supply,Vdd 1.7 1.8 1.9 1.6 1.8 2.0 1.6 1.8 2.0 V

Temperature 40 27 85 45 27 90 45 27 90 C

BGR o/p,

Vref Const. 1.18 1.18 V

BGR o/p

Accuracy 30m +30m

30m

+58m 5.8mV

0mV

V

BGR o/p Ref

Currents 10 10.04 10.04 A

(at25C) 20 19.97 19.57 A

40 40.1 38.3 A

100 101.8 94.78 A

Output

Impedance

(for 10A

o/p Ref

Current) 1M 2.5M 2.5M

PSRR 40 75 83 99 76.8 77 125 dB

Noise (at

1Hz) N.A 142 309 1380 308.5 nV/(Hz)

Noise (at

10kHz) 100 92 101 114 101.9 nV/(Hz)

Quiescent

Current, Idd

(BGR) 100 66 56.5 A

ManrajSinghGujral msg1g10UniversityofSouthampton 53

Chapter8:NoiseAnalysis

A Noise producing elements pass on the noise to connected elements. The final output

noiseofasystemcanbeaffectedeitherbycertaintypesofnoiseprofiles,fromcertaintypes

of elements, or a noise producing element can affect the final system noise at particular

frequencies.

AtypicalconnectionofaBGRassociatedcircuitisshowninfigure71.

Figure71:TypicalNoiseProducingElementsinanexamplesystem

Thepowersupplynoisecanbeexpectedtohaveaneffectonthefinaloscillatornoise.Since

theoscillatorisconnectedtomultipleunits,suchastheCrystalitself,theControlsupplyto

adjust the frequency of operation, and the LDO output the effect of the oscillator noise

mightbedifferentfromdifferentsources.

In this exercise we examine the effects of different noise sources on our main output.

Similartotheschemeshownfigure71,wewilluseacircuitequivalentinaschematiceditor.

ThesearetheactualcircuitsprovidedbyRakonUKLtd.andthesimulationswerecarriedout

tounderstandthenoiseflowthroughtheirsystem.InthiscasetheBandgapwasassumedto

beanIdealVoltagesource,i.e.,withnoNoise,andtheremainingcircuitwastested.

The purpose of the test was to analyze the circuit with different noise producing elements

andhowitaffectsthefinaloutputnoise.

Figure 72 shows the circuit under test where we use the Industrial LDO, Oscillator and its

oscillatorcontrolcircuit.

ThistestbenchisprearrangedsothattheoutputfrequencyoftheOscillator=26MHz.

ManrajSinghGujral msg1g10UniversityofSouthampton 54

Figure72Noiseanalysiscircuit

Vcontrol

ManrajSinghGujral msg1g10UniversityofSouthampton 55

1. Asatool:InCadenceaNoisecanbesimulatedby

a. Either placing noisy elements , such as a Resistor (for Flat band

Noise/ThermalNoise)

b. ByplacingMOSdevicestoadd1/fnoiseetc.

c. UploadingaNoiseprofile.txtfilecanbeaddedontoanidealvoltagesource

2. In the Initial test conducted Analogue library Sources were used to give us an

estimateoftheperformanceofsysteminanIdealcase.Thisresultcanthenbeused

tocomparetheresultsobtainedwithactualNoisyelements.

(a) (b)

Figure73(a)OutputPhaseNoiseoftheOscillatorand(b)PeriodicsteadystateoftheOscillatoroutput.

a. HeretheNoiseat1Hz=62.4dBc

b. Noiseat10kHz=147dBc

[dBcistheNoisew.r.ttothecarrierfrequency]

ManrajSinghGujral msg1g10UniversityofSouthampton 56

V

control

is the input to the Oscillator Tuning Circuit shown in figure 72, which is responsible

forsettingtheoscillatoroperatingfrequency.KeepingallothersourcesIdeal,aNoiseprofile

was added on top of V

control

and the Phase Noise at the output of the Oscillator was

measured.

Figure74PhaseNoiseduetheadditionofatypicalNoiseprofile(/ravi/noise.txt

1

)onVcontrol.

A difference of 5.18 dBs can be seen at 1 Hz frequency, in figure 74. This noise affects the

lowerfrequency(1/f)regionofthenoiseslope.

SimilarlyatestforV

LDO

wasperformed,keepingeverythiselseIdealaddedtoseetheNoise

attheOscillatoroutput

Figure75:PhaseNoiseduetheadditionofatypicalNoiseprofile(/ravi/noisel.txt

2

)onLDOOutput(fig72).

1

noise.txtfilewasanactualnoiseprofileforControlsuppliedbyMrRavi,ICDesignEngineerinRakon

2

noisel.txtfilewasanactualnoiseprofileforLDOsuppliedbyMrRavi,ICDesignEngineerinRakon

OutputNoisedue

tonoiseinLDO

OutputNoisedueto

noiseintheControl

Supply

OutputNoise

performanceof

theOscillatordue

toIdealVoltage

Sources

ManrajSinghGujral msg1g10UniversityofSouthampton 57

InthiscasetheNoiseaffectsthehigherfrequenciesregionoftheNoiseslope.Adifference

ofalmost2dBisobservedbetweentheIdealcaseandtheNoiseadditionatabout300kHz.

At this instance we are interested in finding out the region of slope at which the deviation

startsduetoLDONoiseandduetoControlNoise.

8.1LDOPhaseNoise

A series of simulation runs were carried out to see the affect of additional LDO Noise over

IdealSourceandcorrespondingfrequencybeyondwhichtheeffectswerepronounced.

The typical Noise profile file for the LDO, noisel.txt was modified to have a range of noise

values. The values of Noise were changed so that the tests could be performed with

increasingseverityofnoiseas:

IdealCase,Noise,10xNoise,100xNoiseand1000xNoise.

Asweepofthiswascarriedouttoseetheaffectoftheseontheoutputperformance.

Figure76:PhaseNoiseprofilesattheOutputoftheOscillator.EachwaveisrepresentedbytheNoiseX

<value>inthesamecorrespondingorder.

This output performance was then analysed to see at what frequencies the deviation is

maximum.TheNoisywaveformswereeachsubtractedfromtheidealwaveformtoseetheir

differencesw.r.tfrequency.

ManrajSinghGujral msg1g10UniversityofSouthampton 58

Figure77:StandardoutputPhaseNoisefordifferentprofiles,andthedifferenceofeachwavefromtheideal

one.

As can be seen from waveforms in Figure 77, the Effect of LDO Noise reaches a peak just

before 10

4

Hz and reaches a second peak just after 10

5

Hz. These waves are the levels of

Noiseovertheidealperformance.

It can also be seen that the affect of LDO noise starts impacting as soon as 10

2

Hz. At this

pointthereisasharpriseinitsvalueuntilitreachesthefirstpeak.

Anothersetofwaveformsisplottedwhichshowstherateofchangeofnoisew.r.ttheideal

curve in figure 78. This helps us identify the place from where the noise starts to rise and

howfast.

Figure78:a2xNoiseand10xNosewavedifferentialofnoise(differencefromtheIdeal)wave.

It can be seen that the peak occurs between 10

2

and 10

3

Hz. After which, although the

absoluteerrorremains,itstartstodecelerateandafter10

4

Hzbecomesalmostconstant.

ManrajSinghGujral msg1g10UniversityofSouthampton 59

Figure79::AsummaryofoutputphasenoiseperformancefordifferentLDOinputnoiselevels.

ManrajSinghGujral msg1g10UniversityofSouthampton 60

8.2ControlSupplyPhaseNoise

Similarly Control Supply Phase Noise was added onto an ideal system to observe the

Oscillatoroutputnoise.

Thelevelsofnoiseaddedcanbeseeninthewaveformsbelowinfigure80.SimilartoLDO

PhaseNoiseAnalysis,adifferenceofOutputNoiseperformancefordifferentControlSupply

noisevs.theIdealcasewereplottedtoobservetherelativemagnitudes.

Hereagain,theNoisywaveformswereeachsubtractedfromtheidealwaveformtoseethe

differencebetweenw.r.tfrequency.

Figure80:(top)OscillatorOutputPhasenoisefordifferentlevelsofnoiseatcontrolsupply.

(bottom)Differencebetweenoutputnoisewavesw.r.tIdealwave

In this case, we can see that the Phase Noise on Control Supply affects the lower

frequenciesmore.Thedifferencestartsappearingat1Hznoise.

Thisdifferencethenpeaksbetween10

2

and10

3

Hzandbegintodroptoalmost0atabout

10

5

Hz.

Herealso,wecanseetherateatwhichthedifferenceoccurs,infigure82

Thesummaryof

waveforms.

ManrajSinghGujral msg1g10UniversityofSouthampton 61

Figure81:AsummaryofoutputphasenoiseperformancefordifferentCtrlinputnoiselevels.

ManrajSinghGujral msg1g10UniversityofSouthampton 62

From figure 81 it can be observed that the rate of change of Noise is maximum at lower

frequenciesandtherateofchangebecomesalmostconstantbeyondafew100Hz.

8.3Experiment1:LowPassFilter

Asmallexperimentwascarriedoutbasedonthefindingsoffigure13totryandreducethe

outputnoisefromLDObypassingitthroughalowpassfilter.Thehighestrateatwhichthe

errorstartstopickupliesatverylowoffsetfrequencies,intheregionof10Hz.

Ideal Voltage

Source

Oscillator

Ctrl Supply

Oscillator Output + noise

+

filter

Figure82:anexperimentalsetupbyaddingafilterinfrontoftheCtrlsupplynoise

Now since the control supply voltage source, with its specific Noise Profile, affects at low

offset frequencies, a Low Pass filter, for these low frequencies were added to see if the

noisecanbefurtherremoved.

Figure83:WaveformsforOutputPhaseNoiseoftheOscillatorwithLowPassfilterattheinputCtrlSupplyline

Although the noise is pulled closer to the Ideal curve, the value of capacitance and

resistanceinvolvedincreasedquitesignificantly.Thecapacitancevalues,markedincircles,

increasetoveryhighvaluesinscalesofnF.

IdealNoiseProfileof

theOscillator

NoiseProfilewithouta

Filter

ManrajSinghGujral msg1g10UniversityofSouthampton 63

8.4LDOandControlSupplyPhaseNoiseRegions

Atthispointanothersetoftestswereperformedtoseeatwhichfrequencies(orarangeof

frequencies) the effect of LDO Noise and Control supply noise begins to impact the

OscillatorOutputPhaseNoise.

IfwegetanideaatwhatrangeoffrequenciesbelowcertainlevelonlyControlsupplyNoise

affects more , and above a certain frequency LDO Noise Starts to dominate we can adjust

thenoiseperformanceoftheseunitsaccordingly,togiveanoverallOscillatorOutputnoise

whichiscontrollable.

Figure84:OscillatorO/PPhaseNoisewavesforCtrlvoltagesourcenoisefromIdealto1000Timesitsstdnoise

profile&LDOSourceNoisefromIdealto1000TimesthestdnoiseProfile.

Inthisbunchofwaves,wehavethecontrolsupplynoiseaffectingatlowerfrequencies,and

LDO supply noise affecting at higher frequencies. We intend to find out the tipping point

wherethedominanceofCtrlSupplyendsandLDOnoisebeings.

ForthiswesubtractthenoiseduetoCtrlSupplyfromthenoiseduetoLDOsupplyandsee

thedifference.

ManrajSinghGujral msg1g10UniversityofSouthampton 64

Figure85:OutputPhaseNoisedominancebetweenCtrlSupplyandLDOsupply.

From figure 85 a clear point on frequency scale can be seen between 30kHz and 40kHz

where the Noise due to Ctrl Supply and LDO becomes almost equal, and hence their

differencebecomeszero.

ItcanbeinferredthatiftheOscillatoroutputNoiseistobetargetedforloweroffset

frequenciesthentheadjustmentsinControlsupplywillhaveahigherimpact.Similarly,if

thetargetisathigheroffsetfrequenciesbeyond30kHzthentheLDOcircuitwillhavea

higherimpact.

CtrlSupply

Dominance

LDOsupply

dominance

ManrajSinghGujral msg1g10UniversityofSouthampton 65

Chapter9:Conclusion

Athorough descriptionofbandgap principleswerediscussedandcriticalcomponentsused

inanalogueandmixedsignaldesignswerelookat.Severalimportanttestswerecarriedout

to understand the parameters in these building blocks and how these could be tailored to

meet a designers needs. The results of these tests were used to design a Bandgap circuit

whichwentthroughadesigncyclekeepingtherequiredspecificationinmind.

A low Noise Bandgap circuit was developed and simulated for stringent Industrial Corners,

supplied by Rakon UK Ltd., as well as University specified corners for the same IBM7WL

process.Thelowestnoiselevelsachievedwereintherangeof100nV/Hzandtheaccuracy

matchedthespecifications.AdetailedcompliancematrixisshowninChapter7,Table12.

9.1ScopeofImprovement

Although the Bandgap reaches the target specification in terms of Noise

Performance which is industrially acceptable, it can be lowered even further by using

VBE

Techniques. V

BE

stacking theory explains the concept in making a bandgap relying less on

theResistancesandusingthepropertyofBipolar,whicharelownoisedevices,toattainthe

sameReferencevoltage.

This concept is also presented in a Thesis by Mr William T Holman (7) on which several

patentshavealsobeenfiled,forexampleSanderGierkinkPatent(8).

TheoutputperformanceofaBandgapisusuallyacceptedifitperformsatanoutput

of+/5%ofreferenceVoltage.This5%deviationisthenadjustedthroughtrimmingcircuits.

Usually in the topology that has been presented in Bandgap3, section 3.3 in Figure 32,

thesetrimmingcircuitswouldbeappliedtotheresistancevaluessoastoenablethetaped

out chip to have control over output voltage. These resistance values can be adjusted to

finally allow a very high degree of accuracy even in the worst case corner. Also trimming

circuitscanbeusedtoregulatetheoutputsupply.(10)

These features on top of a low noise bandgap circuit can provide a low noise, highly

accurate,userspecificvoltagereference.

The Output Resistance of the Current Mirrors at the output stage of the Bandgap,

Chapter 5.3 Figure 56, can be further increased by using Cascode as shown in Chapter 2.2

Figure 19 and Figure 20. That would need a Bias Circuitry to go along with it. Although a

CascodewouldmeanaheadroomproblemswithminimumV

DD

.Thiscanbeworkedaround

withlowvoltagecascadesandalsobecauseweseeaheadroomofabout0.3Vasshownin

theChapter4:CornerSimulationsforBandgap2,Figure39.

During Layout, although Common centroid techniques were used to minimize the

mismatch,Dummystructureswerenotplacedduetotimeconstraint.Consideringweneed

very high matching in this Bandgap it is advisable to implement the dummy structures.

ManrajSinghGujral msg1g10UniversityofSouthampton 66

Section5.3,Figure61and62,explainssomeoftheseconceptsbutwerenotimplementedin

thisdesign.

Thesearesomeoftheobviousscopesofimprovementswhichcanbeimplementedtothis

circuit.

References

1.Sansen,Willy.Bandgapandcurrentreferencecircuits.[bookauth.]WillyM.C.Sansen.AnalogDesign

Essentials.CatholicUniversity,LeuvenBelgium:Springer,2006.

2.Zenhbroeck,B.Van.Chapter2:SemiconductorFundamentals.PrinciplesofSemiconductorDevices.s.l.:

DepartmentofElectrical,computerandEnergyEngineering,UniversityofColoradoatBoulder,2011.

3.BehzadRazavi,DesignofAnalogCMOSIntegratedCircuits,Chapter11BandgapReferences.s.l.:TATA

McGrawHill,2002.

4.IBMCorporation.BiCMOS7WLModelReferenceGuide.2011,Vol.V1.8.1.0,11.4.Page183.

5.RedmanWhite,Prof.W.Analogue&MixedSignalCMOSDesign.s.l.:Dept.ofElectronicsandComputer

Science,UniversityofSouthampton,2011.

6.Aylward,Kevin.LowArea,LowPowerStartupCircuit.AnalogueDesign,KevinAylward,B.Sc.,.[Online]

October2006.http://www.kevinaylward.co.uk/ee/zeropowerstartup/zeropowerstartup.html.

7.IBMCorporation.IBMDesignManual.ES#70P3341BiCMOS7WLDesignManual.25January2011.

8.Holman,WilliamTimothy.ALowNoiseCMOSVoltageReference.GeorgiaInstituteofTechnology,USA.

1994.p.176.

9.Gierkink,Sander.LowNoiseBandgap.US007242240B2USA,10July2007.UnitedStatesPatent.

10.IBMCorporation.BiCMOS7WLTrainingManual.2007,Vol.Revision6.2,p.309.Page52.

11.MartinezBrito,J.P.Bampi,S.Klimach,H.Kimach,A4BitsTrimmedCMOSBandgapReferencewithan

ImprovedMatchingModelingDesign..June2007,IEEEInternationalSymposiumonCircuitsandSystems,2007

(ISCAS2007),pp.19111914.

You might also like

- LM117 Voltage RegulatorDocument26 pagesLM117 Voltage Regulatore_bahamondesNo ratings yet

- Noise Sources of MOSFETDocument11 pagesNoise Sources of MOSFETDerunNo ratings yet

- Learn Swift by Examples Beginner LevelDocument331 pagesLearn Swift by Examples Beginner LevelletaronsonNo ratings yet

- U2U 2018 India - ConfirmationDocument8 pagesU2U 2018 India - ConfirmationAjay Kumar MattupalliNo ratings yet

- An32f PDFDocument12 pagesAn32f PDFPaulo MonteiroNo ratings yet

- Ec8353electronicdevicesandcircuitsunit2 180711152109Document126 pagesEc8353electronicdevicesandcircuitsunit2 180711152109dhivyaNo ratings yet

- Solar Battery Charger CircuitDocument4 pagesSolar Battery Charger Circuittim schroderNo ratings yet

- AnalogProduct 28022013Document67 pagesAnalogProduct 28022013bbas6825No ratings yet

- Electrical Overstress (EOS): Devices, Circuits and SystemsFrom EverandElectrical Overstress (EOS): Devices, Circuits and SystemsNo ratings yet

- Ece Ade Manual 500 CopiesDocument79 pagesEce Ade Manual 500 CopiesRajkumarNo ratings yet

- Digital Phase Selector: A Mini-Project Report Submitted in Partial Fulfillment Requirements For The Award ofDocument53 pagesDigital Phase Selector: A Mini-Project Report Submitted in Partial Fulfillment Requirements For The Award ofdondbNo ratings yet

- Abp Dynamics Multiple Choice 2016-02-24Document10 pagesAbp Dynamics Multiple Choice 2016-02-24artsidartsyNo ratings yet

- TestYantra CapabilitiesDocument27 pagesTestYantra CapabilitiesChris Majestic IT ServicesNo ratings yet

- Adv CKT Technique Using GmIdDocument35 pagesAdv CKT Technique Using GmIdnarashimarajaNo ratings yet

- Integrated CircuitsDocument108 pagesIntegrated CircuitsECEHOD SECNo ratings yet

- Milliken Thesis Ldo Differentiator PDFDocument106 pagesMilliken Thesis Ldo Differentiator PDFkijiji userNo ratings yet

- Fabrication Organic Solar CellsDocument48 pagesFabrication Organic Solar CellsSwaroop RNo ratings yet

- Advanced Technologies For Next Generation Integrated CircuitsDocument321 pagesAdvanced Technologies For Next Generation Integrated CircuitsIEC2020034No ratings yet

- Analog & Digital ElectronicsDocument18 pagesAnalog & Digital ElectronicsJoyee ChakrabortyNo ratings yet

- Solar Charged e VehicleDocument39 pagesSolar Charged e VehicleBig Fan Of YouNo ratings yet

- Yagi-Uda Antenna Design and Radiation PatternsDocument30 pagesYagi-Uda Antenna Design and Radiation PatternsA_DarkoNo ratings yet

- Design of A Low Voltage Low Drop Out LDO Voltage Cmos RegulatorDocument6 pagesDesign of A Low Voltage Low Drop Out LDO Voltage Cmos Regulatorsantosh kumar gangalaNo ratings yet

- Department of Electrical and Systems Engineering: MOSFET Amplifier Mini ProjectDocument7 pagesDepartment of Electrical and Systems Engineering: MOSFET Amplifier Mini ProjectsadfaNo ratings yet

- Bandgap 2009Document27 pagesBandgap 2009jjloksNo ratings yet