Professional Documents

Culture Documents

Logic Gates

Uploaded by

Mahavira Desai0 ratings0% found this document useful (0 votes)

45 views99 pagesFor BCA Students

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentFor BCA Students

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

45 views99 pagesLogic Gates

Uploaded by

Mahavira DesaiFor BCA Students

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 99

Physical States for Bits

Black Box Representations

Truth Tables

Basic Logic Gates

NAND and NOR gates

Sum of Products Circuits

Timing Diagrams

Logic Levels for CMOS

The concept of voltagecontrolled resistance

nMOS transistor

pMOS transistor

Now we put together nMOS and pMOS transistors to create an inverter

Switch Model for CMOS inverter

Logical operation of CMOS inverter

Explanation of 2-input CMOS NAND gate

Switch Model for NAND realized in CMOS

Explanation of CMOS NOR

CMOS NAND with 3 inputs

Example of realization of large NAND gates in CMOS

Buffers realized in CMOS

AND gate in CMOS

AND-OR-INVERT gate in CMOS

AND-OR-INVERT gate in CMOS

CMOS OR-AND-INVERT

CMOS OR-AND-INVERT

Data Sheets and how to use them

Test Circuits and Waveforms

Input-Output Characteristics

Logic Levels and Noise Margins for CMOS logic family

Resistive Models of Inverters

Resistive model for CMOS LOW output with resistive load

Resistive modelRepresentations for CMOS HIGH output Black Box with resistive load

Circuit defintions to calculate currents

Output loading specifications

Estimating sink and source currents

CMOS inverters with nonideal input voltages

CMOS Black inverter Box Representations with load and nonideal 1.5 voltage input

CMOS Black inverter Box Representations with load and nonideal 3.5 voltage input

What to do with non-used inputs?

Transition times

How to analyze transition times for CMOS output?

Model of HIGH-to-LOW transition

Fall time

Model of a CMOS Low-to-High Transition

Rise time for a LOW-to-HIGH transition of a CMOS Output

Propagation Delays for a CMOS inverter

Worst-Case Timing using logic-level boundary points

Ground bounce in an IC with eight inverters and one ground pin

CMOS transition gate

Two-input multiplexer using CMOS transmission gates

Schmitt-Trigger Inverter

Operation with slowly changing inputs

CMOS three-state buffers

Open-Drain CMOS NAND

Open-Drain CMOS NAND gate driving a load

Rising and Falling transitions of an open-drain CMOS output

Driving a LED with an opendrain output

Driving a LED with standard CMOS output

Eight Open-Drain Outputs driving a bus

Wired-AND function on three open-drain NAND-gate outputs

Two CMOS outputs trying to maintain opposite values on the same line

Four open-drain outputs driving two inputs in Black Box Representations the LOW state

Four open-drain outputs driving two inputs in the HIGH state

Input and output levels for CMOS devices using a 5V supply

Transfer characteristics of HC and HCT circuits

Speed and power characteristics of CMOS families operating at 5V

Input specifications for CMOS families with VCC between 4.5 V and 5.5V

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

ECL 2-input OR/NOR

Problems for quizzes

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

Black Box Representations

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Lic ProjectDocument80 pagesLic ProjectMahavira DesaiNo ratings yet

- LLB Entrance paper on legal awarenessDocument11 pagesLLB Entrance paper on legal awarenessMahavira Desai30% (10)

- All Full Form Related To ComputerDocument2 pagesAll Full Form Related To ComputerMahavira DesaiNo ratings yet

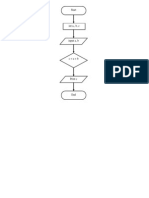

- Flow ChartDocument1 pageFlow ChartMahavira DesaiNo ratings yet

- DOS Commands Guide: Internal, External & OtherDocument12 pagesDOS Commands Guide: Internal, External & OtherMahavira DesaiNo ratings yet

- Comprensive ProjectDocument42 pagesComprensive ProjectMahavira DesaiNo ratings yet

- The Communication Process DefinedDocument18 pagesThe Communication Process DefinedCrissa Marcelo MarianoNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Lecture08 BJT BasicsDocument9 pagesLecture08 BJT BasicsJeanpierreNo ratings yet

- 1985 Siliconix MOSPOWER Applications PDFDocument512 pages1985 Siliconix MOSPOWER Applications PDFGabrielitoNo ratings yet

- SOI-based Devices and Technologies For High Voltage ICsDocument8 pagesSOI-based Devices and Technologies For High Voltage ICssaurabh kumarNo ratings yet

- Chapter 4-TransistorsDocument13 pagesChapter 4-TransistorsMian NomanNo ratings yet

- Program Arduino Lab ELDA 2Document13 pagesProgram Arduino Lab ELDA 2Oups GamingNo ratings yet

- LT-SPICE NMOS Characterization & 180nm Technology InstallationDocument3 pagesLT-SPICE NMOS Characterization & 180nm Technology InstallationvickyNo ratings yet

- EEPROMDocument97 pagesEEPROMMoises PedrazaNo ratings yet

- Mask Design LayoutDocument1 pageMask Design Layoutapi-121385755No ratings yet

- DMT 231 Analogue Electronics: Introduction To Field Effect TransistorsDocument28 pagesDMT 231 Analogue Electronics: Introduction To Field Effect TransistorsAmriNo ratings yet

- Silicon On InsulatorDocument6 pagesSilicon On InsulatorShivam VishnoiNo ratings yet

- Apporva EDKCON2022Document4 pagesApporva EDKCON2022Sonam RewariNo ratings yet

- MOS Rabaey PDFDocument32 pagesMOS Rabaey PDFalamgirNo ratings yet

- Afc 1563Document10 pagesAfc 1563Eugene FlexNo ratings yet

- Active Microwave DevicesDocument17 pagesActive Microwave Deviceswarke abayNo ratings yet

- Electronics_2Document26 pagesElectronics_2okuwobiNo ratings yet

- TPO 610 MosfetDocument4 pagesTPO 610 MosfetCalinhosBaoNo ratings yet

- Realization of Logic Gates Using DTL, TTL, ECL, Etc: Experiment No. 13Document5 pagesRealization of Logic Gates Using DTL, TTL, ECL, Etc: Experiment No. 13Sruthi ReddyNo ratings yet

- EE560 MOS Theory P202Document40 pagesEE560 MOS Theory P202sachin rajputNo ratings yet

- 1988 SGS-Thomson Power Bipolar Transistors Databook 1edDocument1,208 pages1988 SGS-Thomson Power Bipolar Transistors Databook 1edFulanoNo ratings yet

- Unit 5 NotesDocument9 pagesUnit 5 NotesShashikant PandeyNo ratings yet

- MOSFET Digital Circuits and NMOS Logic GatesDocument50 pagesMOSFET Digital Circuits and NMOS Logic Gatesvlsijp100% (1)

- List of Transistors and Diodes AvailableDocument6 pagesList of Transistors and Diodes AvailableCatra Chris SandyNo ratings yet

- Lecture6,7-Logic Design - Transistors To Gates-FinalDocument46 pagesLecture6,7-Logic Design - Transistors To Gates-FinalattarshahriarNo ratings yet

- EHB322E Digital Electronic Circuits Midterm Ii: 1) Consider A Boolean Function 8k 24kDocument3 pagesEHB322E Digital Electronic Circuits Midterm Ii: 1) Consider A Boolean Function 8k 24kfurkan çelikNo ratings yet

- FetDocument31 pagesFetNehaPatelNo ratings yet

- KF3N50FZDocument6 pagesKF3N50FZnow2moreNo ratings yet

- Predictive Model For HCI (Beta Version) : Exp Exp) (+ 2) 2 (Document1 pagePredictive Model For HCI (Beta Version) : Exp Exp) (+ 2) 2 (Gurinder Pal SinghNo ratings yet

- W/L Ratio and Its Effect on Delay and Power in CMOS CircuitsDocument20 pagesW/L Ratio and Its Effect on Delay and Power in CMOS Circuitsdipankar_nath07No ratings yet

- Lecture8 MOS TransistorDocument21 pagesLecture8 MOS TransistorKartika MunirNo ratings yet

- AE - 1.7 MOSFET Circuits - DC Biasing, AC Coupling and Small-Signal Analysis of AmplifiersDocument65 pagesAE - 1.7 MOSFET Circuits - DC Biasing, AC Coupling and Small-Signal Analysis of AmplifiersjayanthiNo ratings yet